Устройство для умножения 12n-разрядных двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

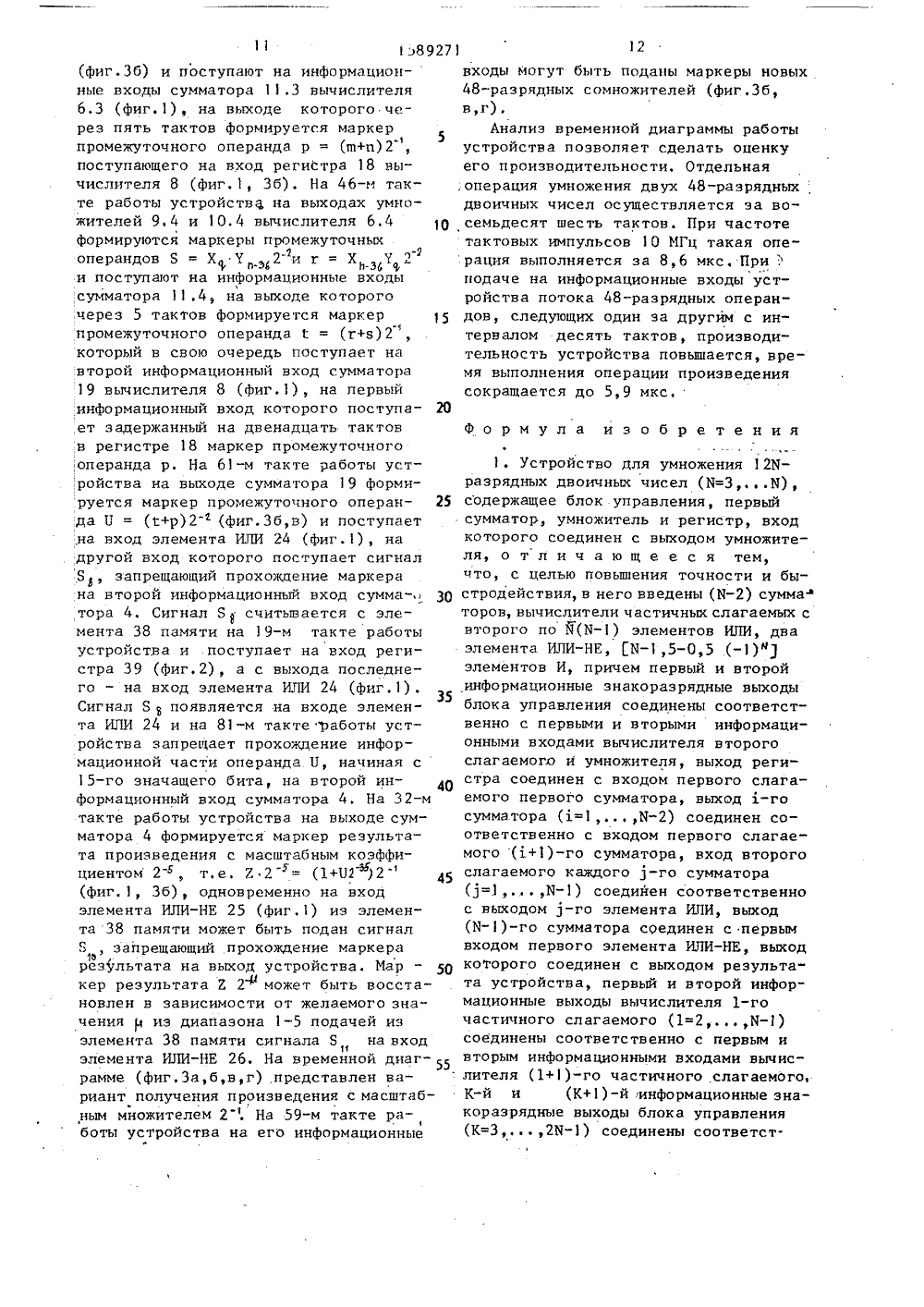

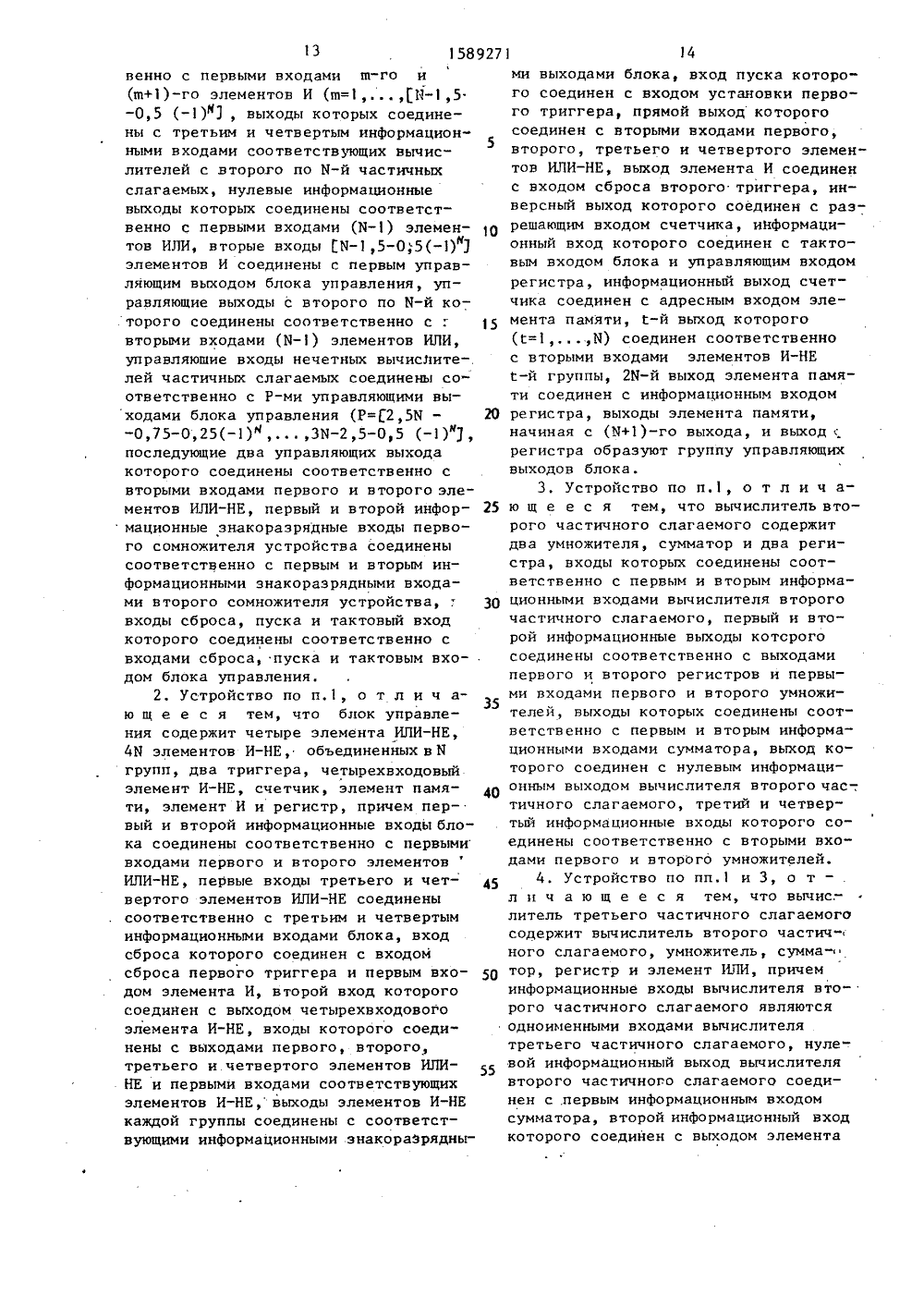

4539271 1 От Ют оа оо 7 т 10 т Фт бдти Гв УИО й 5(кЯй1 589271 РРО Фиг, Зг Составитель Е.МурзинаТехред Л,Сердюкова . Корректор О,Ципле Редактор А.Маковская Заказ 2541 Тираж 5 б 5 ПодписнреВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1011589271 Входные операнды Х и У в двоичной, гут быть представлены в виде: энакоразрядн.ой системе счисления моМ,Х ,ХХ, Х23 " 4 Ю1=1и,Э, 4," Е1Очевидно, что эти операнды могутбыть преобразованы следующим образом: Х 7 где Х;, У 1 принимают значения (1, О,М " 3,4,И; п 12,1. 2Х=,Х,Х Х 00.,00Х,2 Х;2 4-п 2 йХ.2 2 ",) Х.2 = 2 Х 1:1 1900ОХ ХХ 4,0004й-) 14 24 Зб 2 ,.: Х 2 = 2 , Х.2= 2 ХЬ ., 1 ь Х( 2,000ОХХХ 00 1., "-Х;2 = 2Х.2 2 Х 21 , 1 4 11+ 2 х 2 х Фп Йп определяющее точный 2 И-разрядный результат. Ограничиваясь членом, содер- ф.12 55 жащим сомножитель 2 , можно сформировать (0+1)п-раэрядный результат, .как минимум (11,5 Я - 1,5) разрядов которого - точные. Действительно, величина первого отбрасываемого члена не превышает величины 2 л". 2( )= 2 ("Яф 1) поэто)му подсуммирование его к принятому (Я+1)и-разрядному результату произведения может начаться не раньше, чем,-п -1 -Злпо аналогии - 1( = У+ 2 Х 1 + 2 Х + 2У + 42 УЗл й1где Х , У - 1 2-раэрядные операнды тели нетрудно получить выражение дляЙп Идля всех значений Н, 40 Е из произведенияПредставляя таким образом сомножиЕ Х У = Хпл + 2 (Хпгп + 1) + 2 "(Хп+ Х гп + Хз У) ++(2)Ограничиваясь членом, содержащим множитель 2 , получим 60-разрядный результат, сорок четыре разряда которого - точные,На фиг. представлена функциональная схема устройства (для И=4); на фиг,2 - функциональная схема блока управления; на фиг,За, Зб, Зв, Зг - временная диаграмма работы устройства. 55 5 158927 с (11,5 Я + 0,5)-го разряда основной суммы, а учитывая, что при суммировании старшими разрядами вперед (в знакоразрядной системе счисления) пере 5 нос единицы в сторону старших разрядов возможен не более чем на два разряда, получим приведенное выше выражение, определяющее гарантированное количество .точных разрядов в произведении, Последнее обстоятельство определяет также отсутствие влияния на принятый результат младших отбрасываемых членов произведения (1).Анализируя выражение (1), можно 15 определить, что для аппаратной реализации произведения с принятой выше точностью двух 1 2 М-разрядных операндов при условии максимально возможного распараллеливания вычислительного 20 процесса требуется 0,5 М(И+1) 1 2-разрядных умножителей и 0,5 И(И+1)-11 сумматоров неограниченной разрядности, Микропроцессор К 1815 ВФЗ содержит один такой умножитель и один незави симый от умножителя сумматор неорганической разрядности, поэтому количество потребных корпусов микропроцессорных СВИС для реализации предлагаемого устройства определяется выра жением 0,5 Н(0+1), причем один сумматорь не задействованный в реализации (1), используется как независимый вычислитель, сохраняя таким образом функциональную. аналогию с прототипомДля определенности положим, что устройство оперирует 48-разрядными слонами, т.е, 0=4, Принимая и = 12, ш = 2 п, р = Зп, О = 4 п, запишем алгоритм вычисления произведения сорока- , 40 восьмиразрядных операндов: 1 6Устройство для умножения энакораэрядной системы счисления (фиг,1) содержит умножитель 1 (двенадцатиразрядный для последовательных энакоразрядных кодов), сумматоры 2-4 (неограниченной разрядности для последовательных знакораэрядных кодов), регистр 5 (семираэрядный последовательного сдвига знакораэрядного кода),вычислители 6,1 -6,4 второго частичного слагаемого, вычислитель 7 третьего частичного слагаемого, вычисли"тель 8 четвертого частичного слагаемого. Вычислители 6,1 -6.4 содержатумножители 9.1 -9.4 и 1 0.1 -1 0.4 (12 разрядные для последовательных знакоразрядных кодов), сумматоры 11.111.4 (неограниченной разрядности дляпоследовательных знакоразрядных кодов), регистры 12.1-12.4 и 13.1-13.4(последовательного сдвига на двенадцать тактов для знакораэрядных кодов)Вычислитель 7 содержит вычислитель 6, 2, умножитель 14 (1 2-разрядныйдля последовательных знакоразрядныхкодов), регис тр 1 5 (последовательного сдвига на восемнадцать тактов дляэнакоразрядных кодов), сумматор 16(неограниченной разрядности для пос-,ледовательных знакоразрядных кодов)и элемент ИЛИ 17. Вычислитель 8 содержит вычислители 6.3 и 6.4, регистр18 (последовательного сдвига на две надцать тактов для последовательныхзнакоразрядных кодов) и сумматор 19(неограниченной разрядности для последовательных знакоразрядных кодов),Устройство содержит также два элемента И 20 и 21, три элемента ИЛИ 22-24два элемента ИЛИ-НЕ 25, 26 и блок 27управления.Блок управления (фиг.2) содержитчетыре элемента ИЛИ-НЕ 28.1-28.4, четыре группы элементов И-НЕ 29.1-29,4,30.1 -30,4, 31.1 -31,4, 32,1 -32.4, четырехразрядный элемент И-НЕ 33, элемент И 34, триггеры 35, 36, счетчик37, элемент 38 памяти, регистр 39(последовательного сдвига на сороктри такта).Блок управления предназначен дляочистки (обнуления) устройства после подачи электропитания, для образования кодов частных сомножителей Х , пфУпф,Х, У ь для ввода и эалрещения управляющих маркеров (запятых)у промежуточных кодов, возникающих впроцессе вычисления произведения, сог1589271 ласно временной диаграмме работы устройства (фиг.З а,б,в,г). Управляющие сигналы Б -Б, хранятся в элементе 38 памяти и устанавливаются согласно адресам, формируемым счетчиком 37Временная диаграмма (фиг.3 а,б,с, г) представляет изображения в общем виде двоичных знакоразрядных кодов формирующихся на выходах умножителей и сумматоров устройства, и иллюстрирует процесс преобразования информации. Следует иметв в виду, что двоичный знакоразрядный код физически реализован как два прямых двоичных кода, передающихся синхронно по раздвоенной информационной шине. Положительная часть двоичного числа передается по положительному каналу информационной шины и обозначена (фиг.2) Х 7, Х 20И 1,отрицательная - по отрицательному каналу шины и обозначена Х, 7, Х; ,.Устройство для умножения 48-разрядных двоичных чисел работает следующим образом, 25После подачи на устройство электропитания и тактовых импульсов (ТИ) по сигналу "Сброс" (фиг,2) триггеры 35, 36 устанавливаются в "1", при этом сигнал с прямого выхода триггера 36 запрещает прохождение сигналов через элементы ИЛИ-НЕ 281-28.4, а сигнал с инверсного выхода триггера 35 поступает на разрешающий вход счетчика 37, который через несколько35 ТИ достигает нулевого значения и формирует сигнал переноса Ркоторый возвращает триггер 35 в исходное состояние и запрещает счет счетчику 37, Таким образом в элементе 38 памяти ус танавливается первоначальный адрес. После прохождения 86 ТИ устройство обнуляется и на него может быть подан сигнал "Пуск", который сбрасывает триггер 36 и разрешает прохождение сигналов через элементы ИЛИ-НЕ 27.1-27.4, определяя готовность устройства к работе.При появлении на входе элементов ИЛИ-НЕ 28.1-28.4 первого (управляюще 50 го) бита информации - маркера триггер 35 устанавливается в положение "1" и запускает счетчик 37, формирующий адреса управляющих сигналов Б-Б записанных в элементе 38 памяти. По ну 55 левому адресу записан, сигнал Б (фиг,За), который подается иа входы элементов И-НЕ 29,1-29.4 (фиг,2) и разрешает прохождение на входные информационные шины умножителя 1 (фиг.1 12-разрядных операндов Х, У,. Умно- жители 1, 91-9,4, 10.1-10.4 и 14 и сумматоры 2, 3, 4, 11.1-11.4, 16 и 19 функционируют в режиме автоматического масштабирования, т.е. выполняют операции вида 2 = (Х У)2 , С =(А+В)2 " или С = (А+В)2-. Таким образом, на 10-м такте работы устройства на выходе умножителя 1 (фиг.1) формируется маркер промежуточного операнда а = Х.У .2 (фиг.За), пос. тупающего в регистр 5 (фиг1). На .12-м такте из элемента 38 памяти на входы элементов И 20, 21 поступает сигнал Б (фиг,1, За), а на выходе элементов И 20, 21 формируется маркер операндов Х, У . На 13-м такте действие сигнала Б прекращается и1на выходах элементов И-НЕ 29,1-29.4 устанавливаются нулевые уровни информационных сигналов, одновременно из элемента 38 памяти на входы элементов И-НЕ 30.1-30.4 поступает сигнал Б (фиг.2, За), разрешающий прохождение на входные информационные шины умножителей 9.1 и 1 О, вычислителя 6.1 1 2-разрядных операндов Х и У соответственно, при этом на вторые входы умножителей 9.1 и 10.1 поступают задержанные на дванадцать тактов в регистрах 12.1 и 13.1 операнды Х . и У. Через десять тактов относительно Бна выходах умножителей 9.1 и 10.1 формируются маркеры промежуточных операндов С =. Х У2 иВ = Х-2ш л и ь 6 х У, 2 соответственно (фиг.1, За), которые поступают на информационные входы сумматора 11,1, на выходе. которого через пять тактов формируется маркер промежуточного операнда Й =(Ь + с)2 1 (фиг.За). На 25-м такте работы устройства действие сигнала Б прекращается и на выходах элементов И-НЕ 30.1-30,4 устанавливаются информационные нули; одновременно из элемента 38 памяти (фиг.2) на входы элементов И-НЕ 31.1-31,4 поступает сигнал Б , разрешающий прохождение в вычислитель 7 на вторые информационные входы умножителей 9,.2 и 10,2 вычислителя 6,2 12-разрядных операндов Х, У, при этом на первые входы умножителей 9.2 и 10,2 поступают задержанные на двадцать четыре такта в регистрах 12.1, 12,2 и 13.1, 13.2 операнды Х и У , На 17-м такте рабойты устройства на первый информацион 9,158927 ный вход сумматора 2 поступает маркер операнда а, задержанного на, семь тактов в регистре 5. На втором информационном входе сумматора 2 элементом ИЛИ 22 поддерживается информационный нуль. Начиная с 18-го такта, сумматор 2 осуществляет суммирование операнда а с нулевыми старшими разрядами операнда й (фиг,1, За), учитывающими множитель 2-Р согласно алгоритму (2) . На 27-м такте работы одновременно с формированием маркера операнда й на выходе сумматора 11.1 из элементов 38 памяти (фиг.2) на вход элемента ИЛИ 22 поступает сигнал Яд, запрещающий прохождение маркера операнда Й на второй информационный вход сумматора 2 и пропускающий без преобразования информационную часть операнда. 20 На 22-м такте на выходе сумматора 2 формируется маркер промежуточного операнда е = (а+62 ")Т, который пос-. тупает на первый информационный вход сумматора 3 (фиг,1, За, 6). Сформиро ванные на 12-м такте работы устройства двумя элементами И 20, 21 маркеры и операнды Х , У поступают также на информационные входы умножителя 14 вычислителя 7 (фиг.1), на выходе которого через десять тактов формируется маркер промежуточного операнда Г = Х У 2 , который поступает на вход регистра 15. На 34-м такте работы устройства на выходах умножителей 9.2 и 10,2 формируются маркеры промежуточных операндов Ь = ХУ 1, 2 и Ч = ХУР 2 соответственно (фиг.36), ко",орые поступают на информационные входы сумматоРа 11,2 (фиг.1), 40 на выходе которого через пять тактов формируется маркер промежуточного операнда д = (с+В)2(фиг.36), который в свою очередь поступает на первый информационный вход сумматора 16 вычислителя 7 (фиг,1). На второй информационный вход этого сумматора поступает задержанный на восемнадцать тактов промежуточный операнд й, причем маркер этого операнда запрещается элементом ИЛИ 17 по сигналу Я, приходящему иэ элемента 38 памяти (фиг.2), на 40-м такте работы устройства, На 44-м такте на выходе сумматора 16 формируется маркер промежуточного операнда 1 = (Е 2+ 1)2 (фиг.36) и поступает на вход элемента ИЛИ 23, одновременно на второй вход элемента ИЛИ 23 поступает сигнал Я.Р 1 10из элемента 38 памяти (фиг2), котоРый запрещает прохождение маркера операнда Е на второй информационный вход сумматора 3 (фиг,1, Зб), но пропускает информационную часть операнда 1 с, Элементы ИЛИ 22-24 идентичны один другому и функционируют одинаково, Сумматор 3, начиная с 23-го такта работы устройства, осуществляет сумми" рование операнда е с нулевыми старшими разрядами операнда 1 с, учитывающими множитель 2" в алгоритме (2), а после прихода сиагнала Б, к операнду е подсуммируется информационная часть операнда Е, причем так, чтобы первый значащий бит операнда Е сложился с двадцать четвертым битом опе-. ранда е (фиг.36). На 27-м такте работы устройства на выходе сумматора 3 формируется маркер промежуточного операнда 1 щ (е+Ы 212 -, который поступает на первый информационный вход сумматора 4 (фиг,1), который, начиная с 28-го такта работы устройства, будет осуществлять суммирование операнда 1 с нулевыми старшими разрядами операнда Б, учитывающими множитель 2 з в алгоритме (2), На 37- м такте работы устройства действие сигнала Б з прекращается и на выходах элементов И-НЕ 31.1-31,4 устанавливаются информационные нули; одновременно из элемента 38 памяти (фиг.2) на входы элементов И-НЕ 32,1-32.4 поступает сигнал Б, разрешающий прохожде-, ние в вычислитель 8 на вторые информационные входы умножителей 9.4 и 10.4 вычислителя 6,4 1 2-разрядных операндов Х , У, при этом на первые информационные входы умножителей 9.4, 10,4 поступают задержанные на тридцать шесть тактов в регистрах 12.1, 12.2, 12,4 и 13.1, 13.2, 13.4 операнды Х и У с управляющим битом (маркером). На 24-м такте работы устройства в вычислитель 8 на первые информационные входы умножителей 9.3, 10,3 поступает маркер операндов Х, У, задержанных на двенадцать тактов в регистрах 1 2.3 и 13.3 (фиг.1). На 25-м такте на вторые информационные входы умножителей 9.3 и 1 О.3 поступают первые информационные биты операндов Х УР. Через десять тактов после прихода маркеров на входы умножителей 9.3 и 10.3 на их выходах формируются маркеЯ ры промежуточных операндов и = Х У 2Р в-н и ш = Х У Р 2 соответственно11э 89271 (Фиг.Зб) и поступают на информационные входы сумматора 11.3 вычислителя 6.3 (фиг.1), на выходе которого через пять тактов формируется маркер промежуточного операнда р = (ш+п)2 поступающего на вход регистра 18 вычислителя 8 (фиг,1, Зб). На 46-и такте работы устройства на выходах умножителей 94 и 1 0.4 вычислителя 6.4 формируются маркеры промежуточных операндов Б = Х Уэ 2 и г = ХэУ 2 и поступают на йнформационные входы сумматора 11,4, на выходе которого через 5 тактов формируется маркер 5 промежуточного операнда 1: = (г+з)2 который в свою очередь поступает на второй информационный вход сумматора 19 вычислителя 8 (Фиг.1), на первый информационный вход которого поступа ет задержанный на двенадцать тактов в регистре 18 маркер промежуточного операнда р. На 61 -м такте работы устройства на выходе сумматора 19 формируется маркер промежуточного операн да 11 = (с+р)2(фиг,Зб,в) и поступает ,на вход элемента ИЛИ 24 (фиг.1), на другой вход которого поступает сигнал Б, запрещающий прохождение маркера на второй информационный вход сумма-30 тора 4. Сигнал Бсчитывается с элемента 38 памяти на 19-м такте работы устройства и поступает на вход регистра 39 (Фиг,2), а с выхода последнего - на вход элемента ИЛИ 24 (фиг,1) . Сигнал Бпоявляется на входе элемента ИЛИ 24 и на 81 -м такте работы устройства запрещает прохождение информационной части операнда Б, начиная с15-го значащего бита, на второй ин формационный вход сумматора 4. На 32-м такте работы устройства на выходе сумматора 4 Формируется маркер результата произведения с масштабным коэффициентом 2 ь т.е. Е2 = (1+И )2 (фиг.1, Зб), одновременно на вход элемента ИЛИ-НЕ 25 (фиг,1) из элемента 38 памяти может быть подан сигнал Б , запрещающий прохождение маркера 1 ь,результата на выход устройства. Мар - 50 кер результата Е 2 ф может быть восстановлен в зависимости от желаемого значения р из диапазона 1-5 подачей из элемента 38 памяти сигнала Б на входи элемента ИЛИ-НЕ 26. На временной диаг рамме (фиг,За,б,в,г),представлен вариант получения произведения с масштабным множителем 2 . На 59-м такте работы устройства на его информационные 12входы могут быть поданы маркеры новых 48-разрядных сомножителей (фиг.Зб, в,г).Анализ временной диаграммы работы устройства позволяет сделать оценку его производительности, Отдельная операция умножения двух 48-разрядныхдвоичных чисел осуществляется за восемьдесят шесть тактов. При частоте тактовых импульсов 1 0 МГц такая операция выполняется за 8,6 мкс, Приподаче на информационные входы устройства потока 48-разрядных операндов, следующих один за другим с интервалом десять тактов, производительность устройства повышается, время выполнения операции произведения сокращается до 5,9 мкс.Формула изобретения1. Устройство для умножения 12 Я- разрядных двоичных чисел (И=З,.Ф.И), содержащее блок управления, первый сумматор, умножитель и регистр, вход которого соединен с выходом умножителя, о т л и ч а ю щ е е с я тем, что, с целью повьш 1 ения точности и быстродействия, в него введены (И) сумма торов, вычислители частичных слагаемых с второго по Й(И-) элементов ИЛИ, два элемента. ИЛИ-НЕ, Н,5-0,5 .(-1)элементов И, причем первый и второй информационные знакоразрядные выходы блока управления соединены соответственно с первыми и вторыми информационными входами вычислителя второго слагаемого и умножителя, выход регистра соединен с входом первого слагаемого первого сумматора, выход -го сумматора (1 1 И) соединен соответственно с входом первого слагаемого (+1)-го сумматора, вход второго слагаемого каждого 3-го сумматора Ц=.1И) соединен соответственно с выходом З-го элемента ИЛИ, выход (11-)-го сумматора соединен с первым входом первого элемента ИЛИ-НЕ, выход которого соединен с выходом результата устройства, первый и второй информационные выходы вычислителя 1-го частичного слагаемого (1=20-1) соединены соответственно с первым и вторым информационными входами вычислителя (1+)-го частичного слагаемого, К-й и (К+1)-й информационные знакоразрядные выходы блока управления (К=З,2 И) соединены соответст 13 158927145 50 55 венно с первыми входами щ-го и (а+1)-го элементов И (в=11-1,5. -0,5 (-1)ф 3, выходы которых соединены с третьим и четвертым информационными входами соответствующих вычислителей с второго по И-й частичных слагаемых, нулевые информационные выходы которых соединены соответственно с первыми входами (И-) элементов ИЛИ, вторые входы ГМ,5-0;5(-1) 3 элементов И соединены с первым управляющим выходом блока управления, управляющие выходы с второго по Н-й которого соединены соответственно с ." вторыми входами (И) элементов ИЛИ, управляюшие входы нечетных вычислите-. лей частичных слагаемых соединены соответственно с Р-ми управляющими выходами блока управления (Р=2,5 М -0,75-0,25( - 1)н ,31 Я,5-0 5 ( 1)и последующие два управляющих выхода которого соединены соответственно с вторыми входами первого и второго элементов ИЛИ-НЕ, первый и второй информационные знакоразрядные входы первого сомножителя устройства соединены соответственно с первым и вторым информационными знакоразрядными входами второго сомножителя устройства, входы сброса, пуска и тактовый вход которого соединены соответственно с входами сброса, пуска и тактовым входом блока управления.2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок управления содержит четыре элемента ИЛИ-НЕ, 40 элементов И-НЕ, объединенных в Н групп, два триггера, четырехвходовый элемент И-НЕ, счетчик, элемент памяти, элемент И и регистр, причем первый и второй информационные входы блока соединены соответственно с первыми входами первого и второго элементов ИЛИ-НЕ, первые входы третьего и четвертого элементов ИЛИ-НЕ соединены соответственно с третьим и четвертым информационными входами блока, вход сброса которого соединен с входом сброса первого триггера и первым входом элемента И, второй вход которого соединен с выходом четырехвходового элемента И-НЕ, входы которого соединены с выходами первого, второго, третьего и.четвертого элементов ИЛИНЕ и первыми входами соответствующих элементов И-НЕ, выходы элементов И-НЕ каждой группы соединены с соответствующими информационными знакоразрядньг. 10 15 20 25 30 35 40 ми выходами блока, вход пуска которого соединен с входом установки первого триггера, прямой выход которого соединен с вторыми входами первого, второго, третьего и четвертого элементов ИЛИ-НЕ, выход элемента И соединен с входом сброса второго триггера, инверсный выход которого соединен с разрешающим входом счетчика, информационный вход которого соединен с тактовым входом блока и управляющим входом регистра, информационный выход счетчика соединен с адресным входом элемента памяти, Е-й выход которого (1=1И) соединен соответственно с вторыми входами элементов И-НЕ е-й группы, 2 М-й выход элемента памяти соединен с информационным входом регистра, выходы элемента памяти, начиная с (И+1)-го выхода, и выход с. регистра образуют группу управляющих выходов блока.3. Устройство по п.1, о т л и ч аю щ е е с я тем, что вычислитель второго частичного слагаемого содержит два умножителя, сумматор и два регистра, входы которых соединены соответственно с первым и вторым информационными входами вычислителя второго частичного слагаемого, первый и второй информационные выходы которого соединены соответственно с выходами первого и второго регистров и первыми входами первого и второго умножителей, выходы которых соединены соответственно с первым и вторым информационными входами сумматора, выход которого соединен с нулевым информационным выходом вычислителя второго час-, тичного слагаемого, третий и четвертый информационные входы которого соединены соответственно с вторыми входами первого и второго умножителей. 4. Устройство по пп.1 и 3, о т -л и ч а ю щ е е с я тем, что вычис; литель третьего частичного слагаемого содержит вычислитель второго частичного слагаемого, умножитель, сумма- тор, регистр и элемент ИЛИ, причем информационные входы вычислителя второго частичного слагаемого являются одноименными входами вычислителятретьего частичного слагаемого, нулевой информационный выход вычислителя второго частичного слагаемого соединен с первым информационным входомсумматора, второй информационный вход которого соединен с выходом элемента158927ИЛИ, первый вход которого соединен с выходом регистра, выход которого соединен с выходом умножителя, первый и второй входы которого соединены соот 5 ветственно с пятым и шестым информационными входами вычислителя третьего частичного слагаемого, первый и второй информационные выходы вычислителя второго частичного слагаемого являО ются первым и вторым информационными Эходами вычислителя третьего частичного слагаемого, нулевой информационный выход которого соединен с выходом сумматора, второй вход элемента ИЛИ 15 соединен с (2 И+1)-м управляющим выходом блока управления.5, Устройство по пп.1 и 3, о т . - и и ч а ю щ е е с я тем, что вычислитель четвертого частичного слагаемого содержит два вычислителя второго частичного слагаемого, регистр и сумматор, выход которого соединен с нулевым информационным выходом вычислителя четвертого частичного слагаемого, информационные входы вычислителя второго частичного слагаемого и первый и второй информационные выходы вычислителя третьего частичного слагаемого соединены соответственно 30 с одноименными информационными входами первого и второго вычислителей второго частичного слагаемого вычислителя четвертого частичного слагаемого, нулевые выходы первого и второго вы- З 5 числителей второго частичного слагаемого соединены соответственно с входом регнстра.и первым информационным входом сумматора, второй информацион 1 16ный вход которого соединен с выходом регистра. 6. Устройство по п,1, о т л и ч а-, ю щ е е с я тем, что вычислитель . Н-го частичного слагаемого содержит вычислитель Р-го частичного слагаемого (где Р - меньшее иэ двух равноотстоящих от 0,5 М - четное натуральное число), вычислитель (И-р)-го частич" ного слагаемого, сумматор и регистр последовательного сдвига на 6 тактов энакораэрядного кода, причем информационные входы и выходы, кроме нулевого, вычислителя (И-р) -го частичного слагаемого являются одноименными информационными входами и выходами вычислителя Н-го частичного слагаемого, управляющий вход которого (при нечетном И) является последующим эа управ" ляющйм входом вычислителя (Н)-го частичного слагаемого, информационные входы вычислителя М-го частичного слагаемого с 2(Н-р)+1)-го по 2 Н-й являются соответственно первым и вторым информационными входами вычислителя р-го .частичного слагаемого, нулевой информационный выход вычислителя (Б-р)-го частичного слагаемого соединен с входом регистра, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с нулевым информационным входом вычислителя р-го частичного слагаемого, а выход сумматора является нулевым информационным выходом вычислителя Ю-го частичного слагаемого.

СмотретьЗаявка

4609470, 24.10.1988

ОСОБОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО "ПАРСЕК" ПРИ ТОЛЬЯТТИНСКОМ ПОЛИТЕХНИЧЕСКОМ ИНСТИТУТЕ

ЕВСТИФЕЕВ СЕРГЕЙ ГЕЛИЕВИЧ, КУРАКИН ДМИТРИЙ СТЕПАНОВИЧ, ЛУЦЕНКО ВАЛЕНТИН НИКОЛАЕВИЧ, СОКОЛОВ ВЛАДИМИР ВИКТОРОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: 12n-разрядных, двоичных, умножения, чисел

Опубликовано: 30.08.1990

Код ссылки

<a href="https://patents.su/14-1589271-ustrojjstvo-dlya-umnozheniya-12n-razryadnykh-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения 12n-разрядных двоичных чисел</a>

Предыдущий патент: Устройство для суммирования двух чисел с плавающей запятой

Следующий патент: Устройство для вычисления модуля комплексного числа

Случайный патент: Установка для хранения метаболически активных продуктов