Микропрограммное устройство управления (его варианты)

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

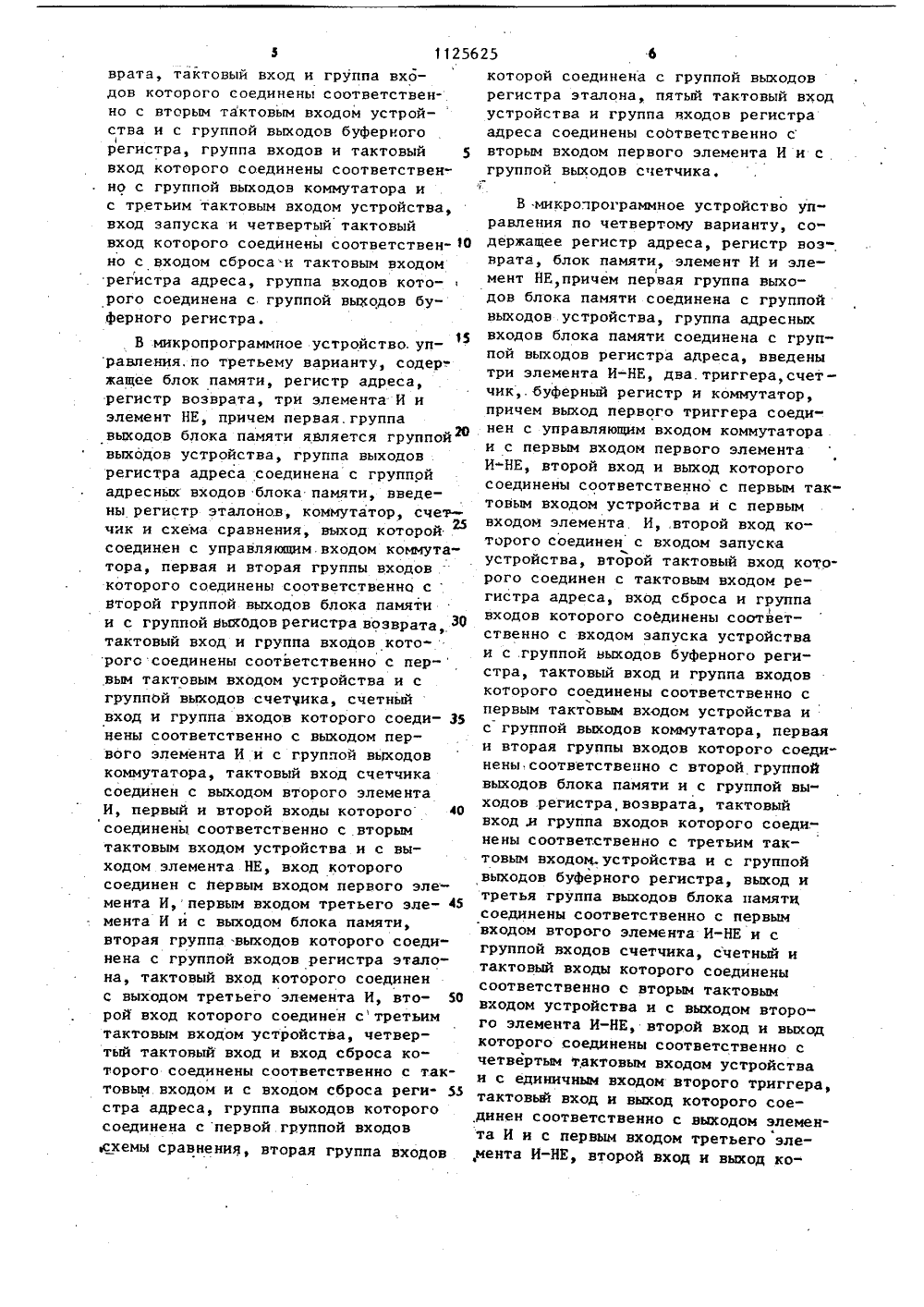

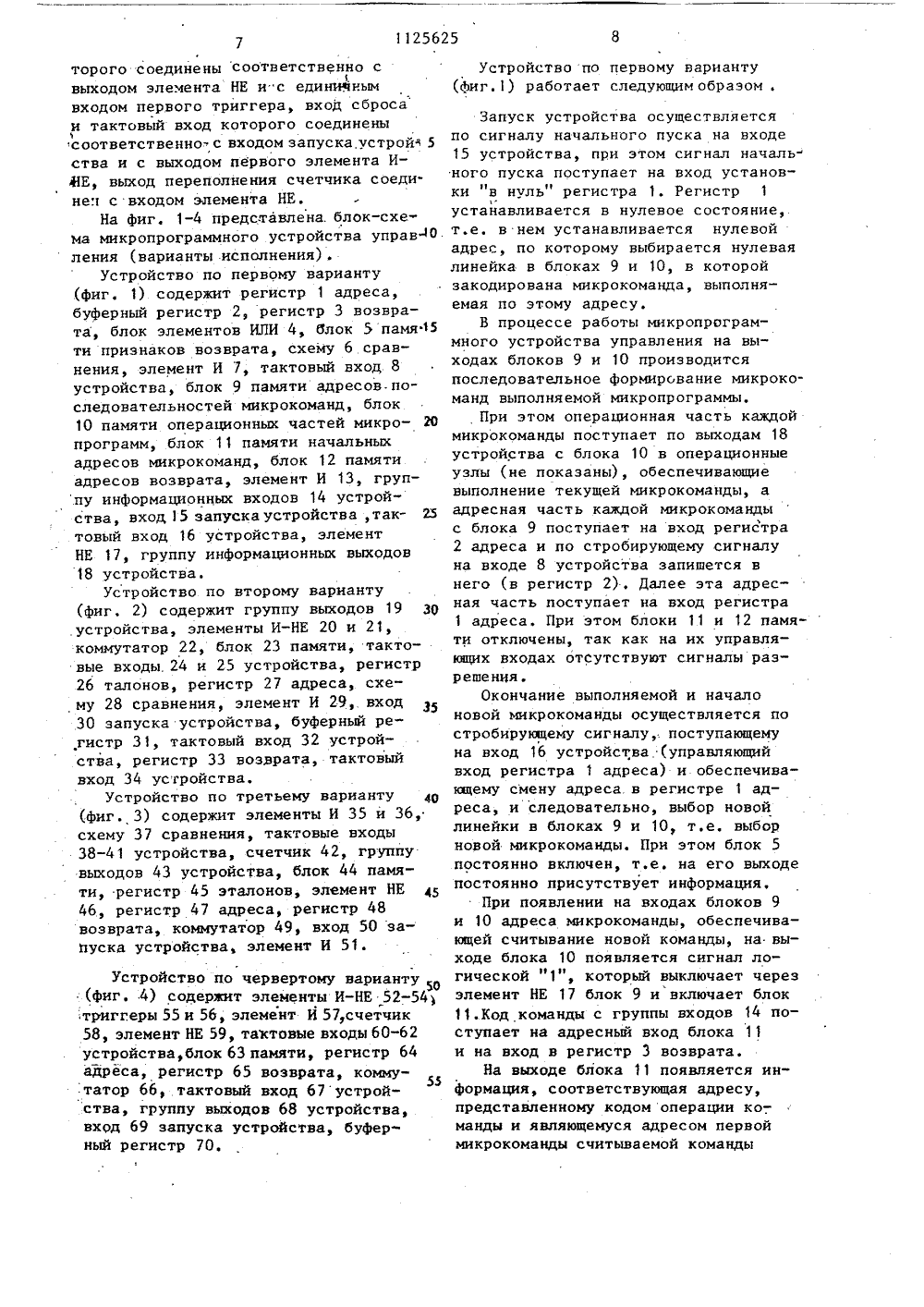

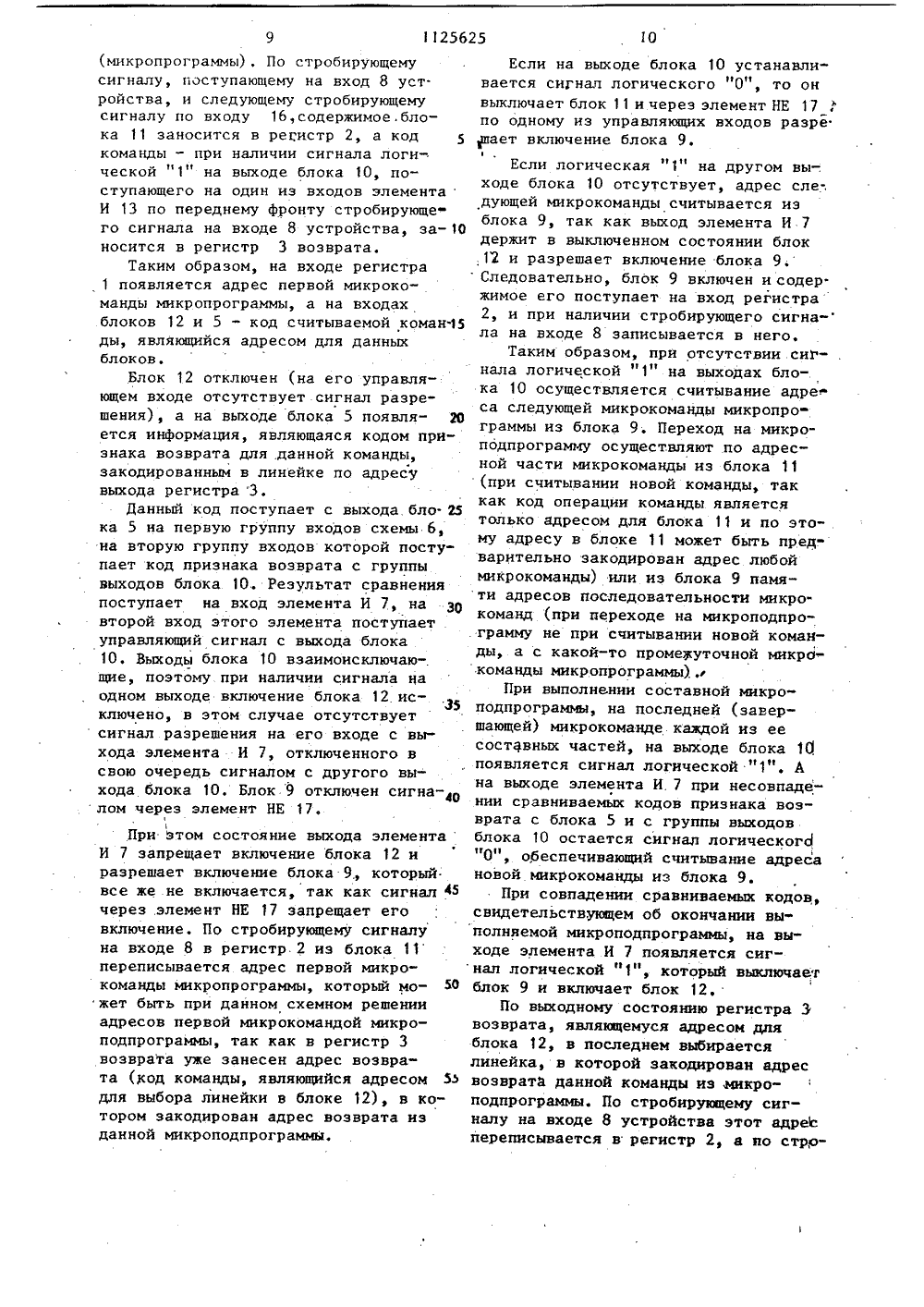

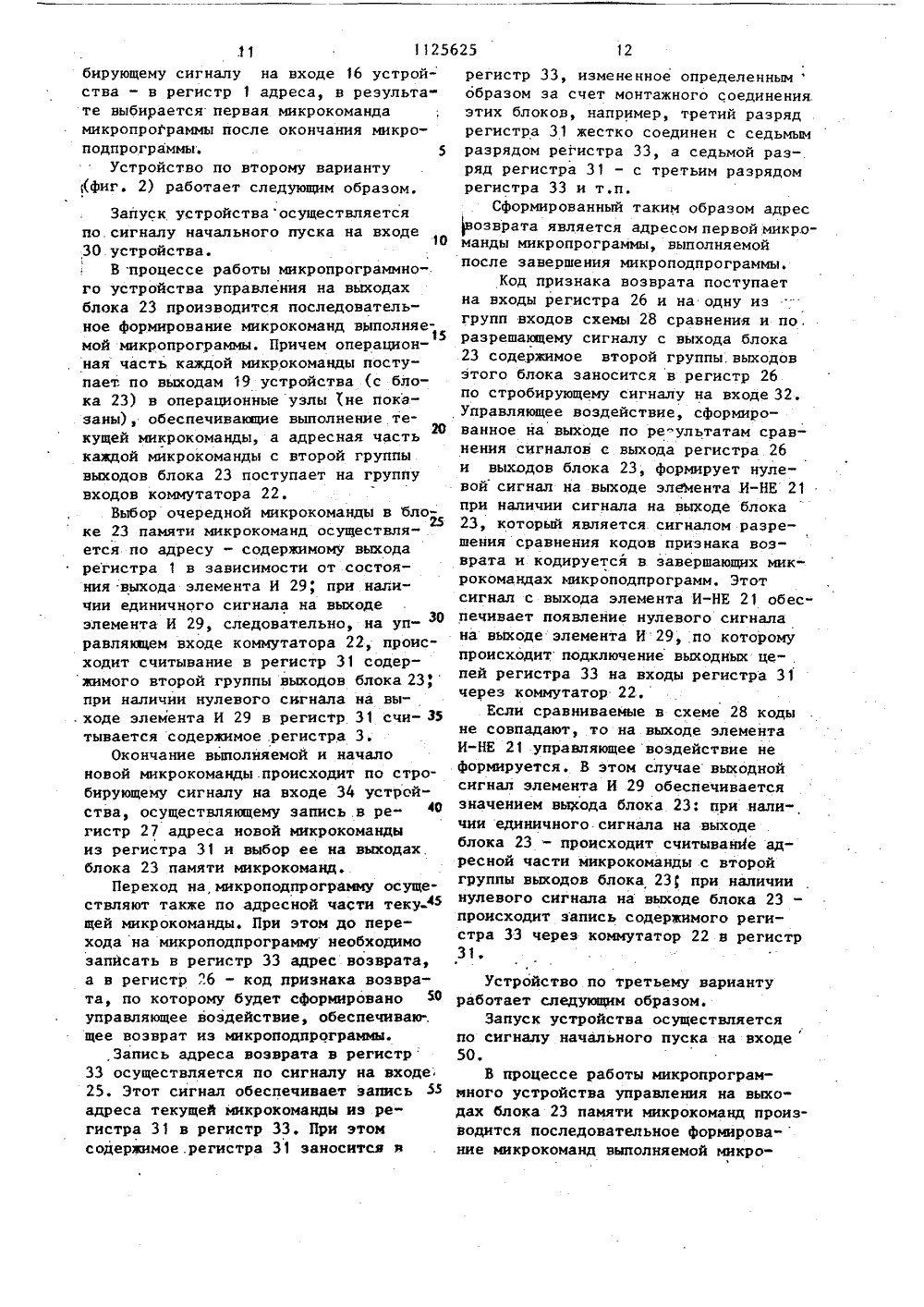

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК ОЮ О)(21 (22 46 кимо .В,М ьков,в,н ьство ССС1976.тво СССР1982 ОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ ОПИСАНИЕ АВТОРСКОМУ СВИДЕТЕЛЬС(54) 161 КРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ (ЕГО ВАРИАНТЫ),57) 1. Микропрограммное устройствоуправления, содержащее блок памятиоперационных частей микропрограмм,.регистр адреса, регистр возврата,блок памяти адресов возврата, дваэлемента И, элемент НЕ, причем первая группа выходов блока памяти операционных частей микропрограмм является группой информационных выходовустройства, группа выходов регистраадреса соединена с группой адресныхвходов блока памяти операционных частей микропрограмм, группа выходов регистра возврата соединена с группойадресных входов блока памяти адресоввозврата, о т л и ч а ю щ е е с ятем, что, с целью расширения области применения устройства эа счетобеспечения возможности работы егос составными микроподпрограммами, внего введены блок памяти адресов последовательностей микрокоманд, буферный регистр, блок элементов ИЛИ, блокпамяти начальных адресов микрокоианд схема сравнения и блок памяти признаков возврата, причем вход запуска устройства соединен с входом сброса регистра адреса, тактовый вход которого соединен с первым тактовым входом устройства, группа выходов регистра адреса соединена с группой адресн 1 ых входов блока памяти адресов последовательностей микрокоманде, первый, второй входы управления чтенйем которого соединены соответственно с выходом элемента П с входом чтения цлока памяти адресов возврата и с выходом первого элемента И, первый и второй входы которого соединены соответственно с первым выходом блока памяти операционных частей микропро 1 грамм и с выходом схемы сравнения, первая и вторая группы входов которой соединены соответственно со второй группой выходов блока памяти опе- а рационных частей микропрограмм и с . группой выходов блока памяти признаков возврата, группа адресных входов которого соединена с группой выходов регистра возврата, группа входов и тактовый вход которого. соединены соответственно с группой информационных входов устрбйства и с выходом второго элемента И, второй выход блока памяти операционных частей микропрограммсоединен с входом. элемента НЕ, с входои управления чтением блока пямяти начальных адресов иикрокоианд ф и с первым входом второго элемента И, второй вход которого соединен с тактовым входом буферного регистра и вторыи тактовым входои устройства, группа информационных входов которого соединена с группой адресных входов блока памяти начальных адресов иикро15 112 микропрограммы до перехода на микро- подпрограмму, но удобнее его формировать на той микрокоманде, на которой осуществляется переход на микро- подпрограмму (так сделано в .предла гаемом устройстве), так как в этом случае число, определяющее код признака возврата (т.еколичество микро- команд до момента окончания микро- подпрограммы), равно количеству мик рокоманд микроподпрограммы минус единица (т.е. нет необходимости учитыаать количество микрокоманд от той микрокоманды, на которой сформирован код признака возврата, до завершающей 15 микрокоманды микроподпрограммы),При этом до перехода на микроподпрограмму необходимо записать в ре-. гистр 65 адрес возврата. Запись адреса возврата в регистр 65 осуществля ется по управляющему сигналу на входе 62, обеспечивающему запись адреса текущей микрокоманды из регистра 70 в регистр 65. При этом содержимоерегистра 70 заносится в регистр 65 возврата, измененное определенным образом за счет монтажного соединения этих блоков, например третий разряд регистра 70 адреса жестко соединен с седьмым разрядом регистра 65, ЗО а седьмой разряд регистра 70 - с третьим разрядом регистра 65 и т.п.Сформированный таким образом адрес возврата является адресом первой микрокоманды микропрограммы, выполняемой после завершения микроподпрограм"мые По сигналу начального пуска (по входу 69 устройства) в регистр 64 установится адрес начальной микро команды, по которому в блоке 63 выбирается определенная микрокоманда, Триггер 56 устанавливается сигналом начального пуска на одном из его входов (через элемент И 57) в исходное 45 состояние, которое запрещает прохождение сигнала с выхода элемента НЕ 59 на выход элемента И-НЕ 53, при этом триггер .55 устанавливается сигналом начального пуска по входу 69 также ЬО в исходное, состояние, при котором на его выходе, а следовательно, на управляющем входе коммутатора 66, устанавливается нулевой сигнал. При этом формирование адреса следующей микро команды происходит по адресной части микрокоманды с блока 63. Этот адрес через коммутатор бб записывается по 5625 16сигналу на входе 60 в регистр 70. Итак, на выходе блока 63 появляется(так предварительно закодировано вблоке 63) единичный сигнал . Этот сигнал означает необходимость записи кода признака возврата в счетчик 58,По переднему фронту сигнала на входе 67 на выходе элемента 52 появляется нулевой сигнал, обеспечивающий запись в счетчик 58 содержимого. второй группы выходов блока 63.По заднему фронту сигнала на входе 67 на выходе триггера 56 появляется единичный сигнал, разрешающий прохождение сигнала с выхода счетчика 58 через элемент НЕ 59 и элемент И-НЕ 53на вход триггера 55, После записи кода признака возврата в счетчик 58состояние в последнем с приходом очередкого сигнала по входу "-1" уменьшается на единицу на каждой микрокоманде. При достижении теперь всчетчике 58 нулевого состояния привыборе предпоследней микрокомандымикроподпрограммы и появлении следующего сигнала на входе 6 1 (вход "-1"счетчика 58) - переход на последнююмикрокоманду микроподпрограммы - навыходе счетчика 58 появляется нулевой сигнал. Инвертированный этот сигнал поступает на второй вход элемента И-НЕ 53, на первом входе которого присутствует единичный сигналс выхода триггера 56. На выходе элемента И-НЕ 53 появляется нулевойсигнал, длительность которого равнадлительности стробирующего сигналапо входу 6 1 устройства .Нулевой сигнал с выхода элементаИ-НЕ 53 устанавливает триггер 55 всостояние, при котором на его выходе появляется единичный сйгнал, аследовательно, и на управляющем входекоммутатора 66 также. появляется единичный сигнал, по которому через коммутатор 66 содержимое регистра 65 посигналу 60 записывается в регистр 70.Это содержимое регистра 65, занесенное в него до перехода на микроподпрограмму, является адресом микрокоманды, выполняемой первой после завершения микроподпрограммы, и заносится оно в регистр 70 на завершающей микрокоманде микроподпрограммы. До выполнения завершающей микро- команды микроподпрограммы и поступлении очередного сигнала на вход 6 1 устройства, обеспечивающего считываПрименение изобретения позволяетрасширить область его применения. 12562518ние адреса возврата иэ регистра 70на его выходе), а задним фРонтомв регистр 64, на выходе элемента этот сигнал приводит в исходное соИ-НЕ 54 появляется нулевой сигнал, стояние (нулевой сигнал на выходе)длительность которого равна длитель- триггер 55.ности сигнала на входе 60 устройства. 5Этот сигнал приводит триггер 56 висходное состояние (нулевой сигнал1125625 одписноПатент " 4 Редактор А, Шишкина Заказ 8541/37 ВНИИПИ Гос по делам 113035, Моск11256команд, группы выходов блоков памяти начальных адресов микрокомаид, адресов возврата и адресов последовательностей микрокоманд соединены соответ-, ственно с первой, второй и третьей группами входов блока элементов ИЛИ, группа выходов которого соединена с группой входов буферного регистра, группа выходов которого соединена с группой входов регистра адреса.2, Микропрограммное устройство управления, содержащее регистр адреса, регистр возврата, блок памяти и элемент И, причем группа выходов регистра адреса соединена с группой адресных входов блока памяти, первая группа вьгодов которого является группой выходов устройства, о т л и- ч а ю щ е е с я тем, что, с целью расширения области .прииенения устройства за счет обеспечения возможности работы его с составными иикроподпрограммами, оно содержит коммутатор, буферный регистр, регистр эталона, схему сравнения и два элемента И-НЕ, причем первый и второй входы элемента И соединены соответственно с первым выходом блока памяти и с выходом первого элемента И-НЕ, первый, второй входы которого соединены соответственно с вторым выходом блока памяти и с выходом схемы сравнения, первая и вторая группы входов которой соединены соответственно с второй группой . выходов блока памяти и с группой выФодов регистра эталона, группа входов и тактовый вход которого соединены соответственно с второй группой выходов блока памяти и с выходои второго элемента И-НЕ, первый и второй входы которого соединены соответствен. но с первым тактовым входом устройства и с третьим выходом блока памяти, четвертый выход которого соединен с первой группой входов коммутатора, управляющий вход и вторая группа входов которого соединены соответственно с выходаии элемента И и с , группой выходов регистра возврата,тактовый вход и группа входов которого соответственно с, вторым тактовым входом устройства и с группой выходов буферного регистра, группа входов и тактовый вход которого соединены соответственно с группой выходов коммутатора и с третьим тактовым входом устройства, вход запуска и четвертый тактовый вход которого 25соединены соответственно с входомсброса и тактовым входом регистра адреса, группа входов которого соединена с группой выходов буферного регистра. 3. Микропрограммное устройство управления, содержащее блок памяти, регистр адреса, регистр возврата, три элемента И и элемент НЕ, причем первая группа выходов блока памяти является группой выходов устройства, группа выходов регистра адреса соединена с группой адресных входов блока памяти, о т л и ч а ю щ е е с я тем, что, с целью расширения области приме.- нения устройства путем обеспечения возможности работы егосоставными микроподпрограммами, в него введены регистр эталонов, коммутатор, счетчик и схема сравнения, выход которой соединен с управляющим входом коммутатора, первая и вторая группы входов которого соединены соответственно с второй группой выходов блока памяти и с группой выходов регистра возврата, тактовый вход и группа входов которого соединены соответственно с первым тактовым входом устройства и с группой выходов счетчика, счетный вход и группа входов которого соединены соответственно с выходом первого элемента И и с группой выходов коммутатора, тактовый вход счетчика соединен с выходом второго элемента И, первый и второй входы которого соединены соответственно с вторым тактовым входом устройства ,и с выходом элемента НЕ, вход которого соединен с первым входом первого элемента И, первым,входои третьего элемента И и с выходом блока памяти, вторая группа выходов которого соединена с группой входов регистра эталонов, тактовый вход которого соединен с выходом третьего элемента И, второй вход которого соединен с третьим тактовым входом устройства, четвертый тактовый вход и вход сброса которого соединены соответственно с тактовым входом и с входом сброса регистра адреса, группа выходов которого соединена с первой группой входов схемы сравнения, вторая группа входов которой соединена е группой выходов регистра эталонов, пятый тактовый вход устройства и ,группа входов регистра адреса соеди- ,нены соответственно с вторым входом25625 11 первого элемента И и с группой выхо" дов счетчика.4. Микропрограммное устройство уп-. равления, содержащее регистр адреса, регистр возврата, блок памяти, элемент И и элемент НЕ, причем первая группа выходов блока памяти соединена с группой выходов устройства, группа адресных входов блока памяти соединена с группой выходов регистра адреса, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет обеспечения возможности работы его с составными микропрограммами, в него введены три элемента И-НЕ, два триггера, счетчик, буферный регистр и коммутатор, причем выход первого триггера соединен с управляющим входом коммутатора и с первым входом первого элемента И-НЕ, второй вход и выход которого соединены соответственно с первым тактовым входом устройства и с первым входом элемента И, второй вход которого соединен с входом запуска устройства, второй тактовый вход которого соединен с тактовым входом регистра адреса, вход сброса и группа входов которого соединены соответственно с входом запуска устройства и с группой выходов буферного регистра, тактовый вход и группа входов которого соединены соответственно с первым тактовым входом устройства и с группой выходовкоммутатора, первая и вторая группывходов которого соединены соответственно с второй группой выходов бло .ка памяти и с группой выходов регистра возврата, тактовый вход и группа входов которого соединены соответственно с третьим тактовым входомустройства и с группой выходов буферного регистра, выход и третья группавыходов блока памяти соединены соответственно с первым входом второгоэлемента И-НЕ и с группой входов счетчика, счетный и тактовый входы которого соединены соответственно с вто-.рым тактовым входом устройства и с выходом второго элемента И-НЕ, второйвход и выход которого соединены соответственно с четвертым тактовымвходом устройства и с единичным входом второго триггера, тактовый входи выход которого соединены соответственно с выходом элемента И и с первым входом третьего элемента И-НЕ,второй вход и выход которого соединены соответственно с выходом элемента НЕ и с единичным входом первоготриггера, вход сброса и тактовый входкоторого соединены соответственно с1входом запуска устройства и с выходом первого элемента И-НЕ, выходпереполнения счетчика соединен с вхо- .дом элемента НЕ, Изобретение относится к вычислительной технике и может быть использовано в устройствах управления.Известно устройство микропрограммного управления, содержащее блок 5 памяти микрокоманд, регистр микро- команд, дешифратор кода микрокоманд и дешифратор кода ветвления, блок управления 1 .Наиболее близким к изобретению 10 по технической сущности и достигаемому результату является микропрограммное устройство управления содерУ жащее блок памяти микропрограмм, два регистра адреса, блок проверки усло вий, элемент НЕ, регистр микрокоманд и блок памяти адресов возврата,причем первая группа входов блокапроверки условий соединена с группойвходов устройства, группа выходов которого соединена с первой группойвыходов блока памяти микропрограмм,первая, вторая группы адресных входов и вторая группа выходов, которогосоединены соответственно с группамивыходов первого, второго регистровадреса и с второй группой входов блока проверки условий, выходы которогосоединены с группой входов регистрамикрокоманд, тактовый вход и группавыходов которого соединены соответственно с выходом блока памяти микропрограмм и с группой адресных входов блока памяти адресов возврата,группа выходов которого соединена с группой входов первого регистра адреса 2Недостатком известного устройства является невозможность его работы с составными микроподпрограммами.Цель изобретения - расширение области применения устройства за счет обеспечения возможности его работы с составными микроподпрограммами. 10 Поставленная цель достигается тем, что в микропрограммное устройство управления содержащее блок памяти операционных частей микропрограмм, регистр адреса, регистр возврата, блок памяти15 адресов возврата, два элемента И, элемент НЕ, причем первая группа выходов .блока памяти операционных частей микропрограмм является группой информационных выходов устройства, группа20 выходов регистра адреса соединена с группой адресных входов блока памяти операционных частей микропрограмм, группа выходов регистра возврата сое 25 динена с группой адресных входов .блока памяти адресов возврата, введены блок памяти адресов последовательностей микрокоманд, буферный регистр, блок элементов ИЛИ, блок памяти начальных адресов микрокоманд, схема сравнения и блок памяти признаков возврата, причем вход запуска устройства соединен с входом сброса регистра адреса, тактовый вход которого соединен с первым тактовым входом устройства, 35 группа выходов регистра адреса соединена с .группой адресных входов блока памяти адресов последовательностей микрокоманд, первый, второй входы управления чтением которого соедине- ф ны соответственно с выходом элемента НЕ, с входом чтения блока памяти адресов возврата и с выходом первого элемента И, первый, второй входы которого соединены соответственно с пер 45 вым выходом блока памяти операционных частей микропрограмм и с выходом схемы сравнения, первая, вторая группы входов которой соединены соответственно с второй группой выходов блока па 50 мяти операционных частей микропро" грамм и с,группой выходов блока памяти признаков возврата, группа адрес,ных входов которого соединена с группой выходов регистра возврата, группа 55 входов и тактовый вход которого соединены соответственно с группой информационных входов устрбйства и с выхоцом второго элемента И, второй выход блока памяти операционных частеймикропрограмм соединен с входом элемента НЕ, с входом управления чтением блока памяти начальных адресов микрокомард и с первым входом второгоэлемента И, второй вход которого соединен с тактовым входом буферногорегистра и вторым тактовым входомустройства, группа информационныхвходов которого соединена с группойадресных входов блока памяти начальных адресов микрокоманд, группы выходов блоков, памяти начальных адресовмикрокоманд, адресов возврата и адресов последовательностей микрокоманд1соединены соответственно с первой,второй и третьей группа:я входов блока элементов ИЛИ, группа выходов которого соединена с группой входов буферного регистра, группа выходов которого соединена с группой входов регистра адреса,В микропрограммное устройство управления по второму варианту, содержащее регистр адреса, регистр возврата, блок памяти и элемент И, причем группа выходов регистра адреса соединена с группой адресных входов блока памяти, первая группа выходов которого является группой выходов устройства, введены коммутатор, буферный регистр, регистр этадонар схема сравнения и два элемента И-НЕ, причем первый, второй входы элемента И соединены соответственно с первым выходом блока памяти и с выходом первого элемента И-НЕ, первый, второй входы которого соединены соответственно с вторым выходом. блока памяти и с выходом схемы, сравнения, первая, вторая группы входов которой соединены соответственно с второй группой выходов блока памяти и с группой выходов регистра эталона, группа входов и тактовый вход которого соединены соответственно с второй группой выходов блока памяти и с выходом второго элемента И-НЕ, первый, второй входы которого соединены соответственно с первым тактовым входом устройства и с третьим выходом блока памяти, четвертый выход которого соединен с первой группой входов коммутатора, управляющий вход и вторая группа входов которого соединены соответственно с выходами элемента И и с группой выходов регистра воз"1125625врата, тактовый вход и группа входов которого соединены соответственно с вторым тактовым входом устройства и с группой выходов буферного регистра, группа входов и тактовый 5 вход которого соединены соответственно с группой выходов коммутатора и с третьим тактовым входом устройства, вход запуска и четвертый тактовый вход которого соединены соответствен но с входом сброса и тактовым входом регистра адреса, группа входов которого соединена с группой выходов буферного регистра.В микропрограммное устройство. уп 15 равления. по третьему варианту, содержащее блок памяти, регистр адреса, регистр возврата, три элемента. И и элемент НЕ, причем первая, группа выходов блока памяти является группой выходов устройства, группа выходов регистра адреса соединена с группой адресных входов блока памяти, введены регистр эталонов, коммутатор, счетчик и схема сравнения, выход которой . соединен с управляющим входом коммутатора, первая и вторая группы входов которого соединены соответственно свторой группой выходов блока памяти и с группой выходов регистра возврата, З 0 тактовый вход и группа входов которого соединены соответственно с пер-,вым тактовым входом устройства и с группой выходов счетчика, счетный вход и группа входов которого соеди иены соответственно с выходом первого элемента И и с групчоч выходов коммутатора, тактовый вход счетчика соединен с выходом второго элемента И, первый и второй входы которого 40 соединены соответственно с вторым тактовым входом устройства и с выходом элемента НЕ, вход которого соединен с первым входом первого элемента И,первым входом третьего эле мента И и с выходом блока памяти, вторая группа .выходов которого соединена с группой входов регистра эталона, тактовый вход которого соединен с выходом третьего элемента И, вто рой вход которого соединен стретьим тактовым входом устройства, четвертый тактовый вход и вход сброса которого соединены соответственно с тактовым входом и с входом сброса реги стра адреса, группа выходов которого соединена с первой группой входовсхемы сравнения, вторая группа входов которой соединена с группой выходоврегистра эталона, пятый тактовый входустройства и группа входов регистраадреса соединены соответственно свторым входом первого элемента И и сгруппой выходов счетчика.3 В микропрограммное устройство управления по четвертому варианту, содержащее регистр адреса, регистр возврата, блок памяти, элемент И и элемент НЕ,причем первая группа выходов блока памяти соединена с группой выходов устройства, группа адресных входов блока памяти соединена с группой выходов регистра адреса, введены три элемента И-НЕ, два.триггера, счетчик,. буферный регистр и коммутатор, причем выход первого триггера соединен с управляющим входом коммутатора и с первым входом первого элемента И-НЕ, второй вход и выход которого соединены соответственно с первым тактовым входом устройства и с первым входом элемента Ивторой вход которого соединен с входом запуска устройства, второй тактовый вход которого соединен с тактовым входом регистра адреса, вход сброса и группа входов которого соединены соответственно с входом запуска устройства и с .группой выходов буферного регистра, тактовый вход и группа входов которого соединены соответственно с первым тактовым входом устройства и с группой выходов коммутатора, первая и вторая группы входов которого соеди" иены соответственно с второй группой выходов блока памяти и с группой выходов, регистра, возврата, тактовый вход и группа входов которого соеди. - нены соответственно с третьим тактовым входом устройства и с группой выходов буферного регистра, выход и третья группа выходов блока памяти соединены соответственно с первым входом второго элемента И-НЕ и с группой входов счетчика, счетный и тактовый входы которого соединены соответственно е вторым тактовым входом устройства и с выходом второго элемента И-НЕ, второй вход и выход которого соединены соответственно с четвертым тактовым входом устройства и с единичным входом второго триггера, тактовый вход и выход которого соединен соответственно с выходом элемента И и с первым входом третьего эле,мента И-НЕ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и"с единичным входом первого триггера, вход сброса и тактовый вход которого соединены соответственно- с входом запуска.устрой 5 ства и с выходом первого элемента ИНЕ, выход переполнения счетчика соединен с входом элемента НЕ.На фиг. 1-4 представлена. блок-схема микропрограммного устройства управО ления (варианты исполнения).Устройство по первому варианту (фиг. 1) содержит регистр 1 адреса, буферный регистр 2, регистр 3 возврата, блок элементов ИЛИ 4, блок 5 памя 15 ти признаков возврата, схему б сравнения, элемент И 7, тактовый вход 8 устройства, блок 9 памяти адресов.последовательностей микрокоманд, блок 10 памяти операционных частей микро программ, блок 1 1 памяти начальных адресов микрокоманд, блок 12 памяти адресов возврата, элемент И 13, группу информационных входов 14 устройства, вход 15 запуска устройства,так товый вход 16 устройства, элемент НЕ 17, группу информационных выходов 18 устройства.Устройство по второму варианту (фиг, 2) содержит группу выходов 19 ЗО .устройства, элементы И-НЕ 20 и 21, коммутатор 22, блок 23 памяти, тактовые входы 24 и 25 устройства, регистр 26 талонов, регистр 27 адреса, схему 28 сравнения, элемент И 29, вход 30 запуска устройства, буферный регистр 3 1, тактовый вход 32 устройства, регистр 33 возврата, тактовый вход 34 устройства.Устройство по третьему варианту (фиг. 3) содержит элементы И 35 и 36, схему 37 сравнения, тактовые входы 38-41 устройства, счетчик 42, группу выходов 43 устройства, блок 44 памяти, регистр 45 эталонов, элемент НЕ 46, регистр 47 адреса, регистр 48 возврата, коммутатор 49, вход 50 запуска устройства, элемент И 51.Устройство по червертому варианту о(фиг. 4) содержит элементы И-НЕ 52-54триггеры 55 и 56, элемент И 57,счетчик 58, элемент НЕ 59, тактовые входы 60-62 устройства, блок 63 памяти, регистр 64адреса, регистр 65 возврата, комму 55татор 66, тактовый вход 67 устройства, группу выходов 68 устройства, вход 69 запуска устройства, буферный регистр 70. Устройство по первому варианту(Лиг,1) работает следующим образом, Запуск устройства осуществляется по сигналу начального пуска на входе 15 устройства, при этом сигнал началь ного пуска поступает на вход установки "в нуль" регистра 1. Регистр 1 устанавливается в нулевое состояние,. т.е. в нем устанавливается нулевой адрес, по которому выбирается нулевая линейка в блоках 9 и 10, в которой закодирована микрокоманда, выполняемая по этому адресу.В процессе работы микропрограммного устройства управления на выходах блоков 9 и 10 производится последовательное формирование микрокоманд выполняемой микропрограммы.При этом операционная часть каждой микрокоманды поступает по выходам 18 устройства с блока 10 в операционные узлы (не показаны), обеспечивающие выполнение текущей микрокоманды, а адресная часть каждой микрокоманды с блока 9 поступает на вход регистра 2 адреса и по стробирующему сигналу на входе 8 устройства запишется в него (в регистр 2), Далее эта адресная часть поступает на вход регистра 1 адреса. При этом блоки 11 и 12 памяти отключены, так как на их управляющих входах отсутствуют сигналы разрешения.Окончание выполняемой и начало новой микрокоманды осуществляется по стробирующему сигналу,. поступающему на вход 16 устройства.(управляющий вход регистра 1 адреса) и обеспечивающему смену адреса в регистре 1 адреса, и следовательно, выбор новой линейки в блоках 9 и 10, т.е. выбор новой микрокоманды, При этом блок 5 постоянно включен, т.е. на его выходе постоянно присутствует информация.При появлении на входах блоков 9 и 10 адреса микрокоманды, обеспечивающеи считывание новой команды, на выходе блока 10 появляется сигнал логической "1", который выключает через элемент НЕ 17 блок 9 и включает блок 11.Код команды с группы входов 14 поступает на адресный вход блока 11 и на вход в регистр 3 возврата.На выходе блока 11 появляется ин" формация, соответствующая адресу, представленному кодом операции команды и являющемуся адресом первой микрокоманды считываемой команды( кропрограммы) . По стробирующемусигналу, поступающему на вход 8 уст.ройства, и следующему стробирующемусигналу по входу 16,содержимое.блока 11 заносится в регистр 2, а кодкоманды - при наличии сигнала логической " 1" на выходе блока 10, поступающего на один из входов элементаИ 13 по переднему фронту стробирующего сигнала на входе 8 устройства, заносится в регистр 3 возврата.Таким образом, на входе регистра1 появляется адрес первой микрокоманды микропрограммы, а на входахблоков 12 и 5 - код считываемой коман 15ды, являющийся адресом для данныхблоков.Блок 12 отключен (на его управляющем входе отсутствует сигнал разрешения), а на выходе блока 5 появляется информация, являющаяся кодом признака возврата для данной команды,закодированным в линейке по адресувыхода регистра 3.Данный код поступает с выхода.бло. 25ка 5 иа первую группу входов схемы 6,иа вторую группу входов которой поступает код признака возврата с группывыходов блока 1 О Результат сравненияпоступает на вход элемента И 7, на З 0второй вход этого элемента поступаетуправляющий сигнал с выхода блока10. Выходы блока 10 взаимоисключающие, поэтому при наличии сигнала наодном выходе включение блока 12.исключено, в этом случае отсутствуетсигнал разрешения на его входе с выхода элемента И 7, отключенного всвою очередь сигналом с другого выхода блока 10. Блок 9 отключен сигна лом через элемент НЕ 17,При этом состояние выхода элементаИ 7 запрещает включение блока 12 иразрешает включение блока 9, которыйвсе же не включается, так как сигнал 45через .элемент НЕ 17 запрещает еговключение, По стробирующему сигналуна входе 8 в регистр. 2 из блока 11переписывается адрес первой микрокоманды микропрограммы, который может быть при данном схемном решенииадресов первой микрокомандой микроподпрограммы, так как в регистр 3возврата уже занесен адрес возврата Ьод команды, являющийся адресом 55для выбора линейки в блоке 12), в котором закодирован адрес возврата изданной микроподпрограммы. Если на выходе блока 10 устанавливается сигнал логического "0", то он выключает блок 11 и через элемент НЕ 17 по одному из управляющих входов разре знает включение блока 9.1Если логическая " 1" на другом вы-. ходе блока 10 отсутствует, адрес сле; дующей микрокоманды считывается из блока 9, так как выход элемента И 7 держит в выключенном состоянии блок .12 и разрешает включение блока 9. Следовательно, блок 9 включен и содер. жимое его поступает на вход регистра 2, и при наличии стробирующего сигна- ла на входе 8 записывается в него.Таким образом, при отсутствии сигнала логической " 1" на выходах блока 10 осуществляется считывание адре са следующей микрокоманды микропрограммы из блока 9. Переход на микро" подпрограмму осуществляют по адресной части микрокоманды из блока 11 (при считывании новой команды, так как код операции команды является только адресом для блока 11 и по этому адресу в блоке 11 может быть пред" варительно закодирован адрес любой микрокоманды) или из блока 9 памяти адресов последовательности микро- команд (при переходе на микроподпрограмму не при считывании новой команды, а с какой-то промежуточной микро- команды микропрограммы)При выполнении составной микро- подпрограммы, на последней (завершающей) микрокоманде каждой из ее составных частей, на выходе блока 1 О появляется сигнал логической "1". А на выходе элемента И. 7 при несовпаде- нии сравниваемых кодов признака возврата с блока 5 и с группы выходов блока 10 остается сигнал логическогд ИО, обеспечивающий считывание адреса новой микрокоманды из блока 9.При совпадении сравниваемых кодов, свидетельствующем об окончании выполняемой микроподпрограммы, на выходе элемента И 7 появляется сигнал логической "1", который выключает блок 9 и включает блок 12.По выходному состоянию регистра 3 возврата, являющемуся адресом для блока 12, в последнем выбирается линейка, в которой закодирован адрес возврата данной команды из микро- подпрограммы. По стробирующему сигналу на входе 8 устройства этот адреЬ переписывается в регистр 2, а но стробирующему сигналу на входе 16 устрой"ства - в регистр 1 адреса, в реэульта"те выбирается первая микрокомандамикропрограммы после окончания микроподпрограммы.Устройство по второму варианту(фиг. 2) работает следующим образом.Запуск устройства осуществляетсяпо сигналу начального пуска на входе30 устройства.В процессе работы микропрограммного устройства управления на выходахблока 23 производится последовательное формирование микрокоманд выполняе 5мой микропрограммы. Причем операционная часть каждой микрокоманды поступает, по выходам 19 устройства (с блока 23) в операционные узлы не показаны), обеспечивающие выполнение те 20кущей микрокоманды, а адресная частькаждой микрокоманды с второй группывыходов блока 23 поступает на группувходов коммутатора 22.Выбор очередной микрокоманды в блоке 23 памяти микрокоманд осуществляется по адресу - содержимому выходарегистра 1 в зависимости от состояния выхода элемента И 29; при наличии единичного сигнала на выходеэлемента И 29, следовательно, на уп 30равлякщем входе коммутатора 22, происходит считывание в регистр 31 содержимого второй группы выходов блока 23 фпри наличии нулевого сигнала на вы.ходе элемента И 29 в регистр 31 считывается содержимое .регистра 3.Окончание выполняемой и началоновой микрокоманды .происходит по стробирующему сигналу на входе 34 устройства, осуществляющему запись в ре"гистр 27 адреса новой микрокомандыиз регистра 31 и выбор ее на выходах.блока 23 памяти микрокоманд,Переход на,микроподпрограмму осуществляют также по адресной части теку щей микрокоманды. При этом до перехода на микроподпрограмму необходимозапйсать в регистр 33 адрес возврата,а в регистр ,".6 - код признака возврата, по которому будет сформировано 50управляющее воздействие, обеспечивающее возврат из микроподпрограммы.Запись адреса возврата в регистр33 осуществляется по сигналу на входе25. Этот сигнал обеспечивает запись 55адреса текущей микрокоманды из ре"гистра 31 в регистр 33. При этомсодержимое. регистра 31 заносится в регистр 33, измененное определеннымобразом за счет монтажного соединения. этих блоков, например, третий разряд регистра 31 жестко соединен с седьмым разрядом регистра 33, а седьмой раз-. ряд регистра 3 1 - с третьим разрядом регистра 33 и т.п.Сформированный таким образом адрес возврата является адресом первой микроманды микропрограммы, выполняемой после завершения микроподпрограммы.Код признака возврата поступает на входы регистра 26 и на одну из групп входов схемы 28 сравнения и по, разрешающему сигналу с выхода блока 23 содержимое второй группы. выходов этого блока заносится в регистр 26 по стробирующему сигналу на входе 32. Управляющее воздействие, сформированное на выходе по ре"ультатам сравнения сигналов с выхода регистра 26 и выходов блока 23, формирует нулевой сигнал на выходе элемента И-НЕ 21 при наличии сигнала на выходе блока 23, который является сигналом разрешения сравнения кодов признака возврата и кодируется в завершающих микрокомандах микроподпрограмм. Этот сигнал с выхода элемента И-НЕ 21 обеспечивает появление нулевого сигналана выходе элемента И 29, по которомупроисходит подключение выходных цепей регистра 33 на входы регистра 3 1через коммутатор 22Если сравниваемые в схеме 28 кодыне совпадают, то на выходе элементаИ-НЕ 21 управляющее воздействие неформируется, В этом случае выходной сигнал элемента И 29 обеспечивается значением выхода блока 23: при наличии единичного сигнала на выходе блока 23 - происходит считывание адресной части микрокоманды с второй группы выходов блока 23 при наличии нулевого сигнала на выходе блока 23 - происходит запись содержимого регистра 33 через коммутатор 22 в регистр 31. Устройство по третьему варианту работает следующим образом.Запуск устройства осуществляется по сигналу начального пуска на входе 50.В процессе работы микропрограммного устройства управления на выходах блока 23 памяти микрокоманд производится последовательное формирова"ние микрокоманд выполняемой микро1125625 13 10 программы. Причем операционная частькаждой микрокоманды поступает по выходам 43 в операционные узлы (не показаны), обеспечивающие выполнениетекущей микрокоманды, а адреснаячасть каждой микрокоманды с второйгруппы выходов блока 44 поступаетна входы регистра 45 эталона и коммутатора 49. При этом на правляющий вход коммутатора 49 поступаетсигнал с выхода схемы 37. При наличии первого нулевого сигнала на выходе схемы 37 формирование адреса следующей микрокоманды осуществляется .по адресной части блока 44: содержимое второй группы выхода блока 44 параллельно записывается через коммутатор 22 в счетчик 42 по сигналу на входе 38 при наличии нулевого сиг,нала на выходе блока 44.Окончание выполняемой микрокоманды и начало новой .происходит по стробирующему сигналу на входе 40, По этому сигналу осуществляется запись в регистр 47 адреса новой микрокоманды из счетчика 42 и выбор ее на выходах блока 44.Переход на микроподпрограмму осуществляют также по адресной части текущей микрокоманды. При этом до30 перехода на микроподпрограмму необходимо сформировать адрес возврата, а в регистр 45 записать адрес завершающей микрокоманды микроподпрограммы.Запись адреса возврата в регистр З 5 48 осуществляется по управляющему сигналу на входе 41. Этот сигнал обеспечивает запись адреса текущей микрокоманды из счетчика 42 в регистр 48. При этом содержимое счетчика 42 заносится в регистр 48, измененное определенным образом за счет монтажного соединения этих блоков, например третий разряд счетчика 42 жестко соединен с. седьмым разрядом регистра 45 48, а седьмой разряд счетчика 42 - с третьим разрядом регистра 48 и т.п,Сформированный таким образом адрес возврата является адресом первой микрокоманды, выполняемой после за вершения микроподпрограммы.В момент записи адреса завершающей микрокоманды в регистр 45 на вы- ходе блока 44 присутствует единичный сигнал (предварительно закодировано), который запрещает параллельную запись в счетчик 42, сигнал с выхода блока 44 инвертируется на элементе НЕ 46 1и поступает на один из входов элемента И 35 как запрещающий сигнал,поэтому по сигналу на входе 38 устройства запись по группе входов счетчика 42 запрещается, а по входу Ъ 1"этого счетчика содержимое в нем увеличивается на единицу, таким .образом формируется в этом варианте адрес следующей микрокоманды микропрограммЫ.По стробирующему сигналу на входе 39 устройства, поступающему на один .из входов элемента И 36, и единичному сигналу на втором .входе элемента И 36 с выхода блока 44 содержимое второй группы блока 44 заносится в регистр 45 и представляет собой адрес завер-, шающей микрокоманды микроподпрограмьМПосле записи адреса завершающей микрокоманды в регистр 45 эталона происходит сравнение на каждой микрокоманде содержимого выходов регистра 45 и содержимого выходов регистра 47. При несовпадении сравниваемых кодов переход на следующую микрокоманду осуществляется по адресной части микрокоманды с выхода блока 44. При совпадении сравниваемых кодов в счетчик 42 заносится содержимое регистра 48. При этом осуществляется возврат из иикроподпрограммы, т.е. переход на первую микрокоманду после завершения микроподпрограммы.Устройство по четвертому варианту (фиг. 4) работает следующим образом.Запуск устройства осуществляется по сигналу начального пуска по входу 69.В процессе работы микропрограммного устройства управления на выходах блока 63 производится последователь. ное формирование микрокоманд выполняемой микропрограммы. Причем опера ционная часть каждой микрокоманды поступает по выходам 68 в операцион. ные узлы (не показаны), обеспечивающие выполнение текущей микрокоманды микропрограммы, а адресная часть каждой микрокоманды с второй группы выходов блока 63 поступает на первую группу входов коммутатора 66. Код признака возврата поступает с второй группы выходов блока 63 из группы входов счетчика 58. При этом на вход "-1" счетчика 58 по входу 61 /устройства постоянно поступают стро" бирующие сигналы. Код признака возврата может бытьсформирован на любой микрокоманде.

СмотретьЗаявка

3624293, 15.07.1983

ПРЕДПРИЯТИЕ ПЯ А-1736

ВЕЛЕНЬКО ЮРИЙ ДМИТРИЕВИЧ, ЕКИМОВА ВАЛЕНТИНА ИВАНОВНА, КАТАШЕВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, КОЛЯКО ИГОРЬ НИКОЛАЕВИЧ, МАЛЬКОВ ЕВГЕНИЙ ВЛАДИМИРОВИЧ, МИХАЦКИЙ АЛЬБЕРТ ТИМОФЕЕВИЧ, ПАНГА АЙВАР ВИЛФРИДОВИЧ, ПЕТРАКОВ ВЛАДИМИР НИКОЛАЕВИЧ, ТАРАСОВ ВЛАДИМИР ГРИГОРЬЕВИЧ, ЦВЕТКОВ ЯН ЯНОВИЧ, ЦЕЙТЛИН ГЕННАДИЙ НАУМОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: варианты, его, микропрограммное

Опубликовано: 23.11.1984

Код ссылки

<a href="https://patents.su/14-1125625-mikroprogrammnoe-ustrojjstvo-upravleniya-ego-varianty.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления (его варианты)</a>

Предыдущий патент: Генератор случайного процесса (его варианты)

Следующий патент: Устройство для управления обслуживанием запросов

Случайный патент: Закалочная среда