Система выравнивания сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

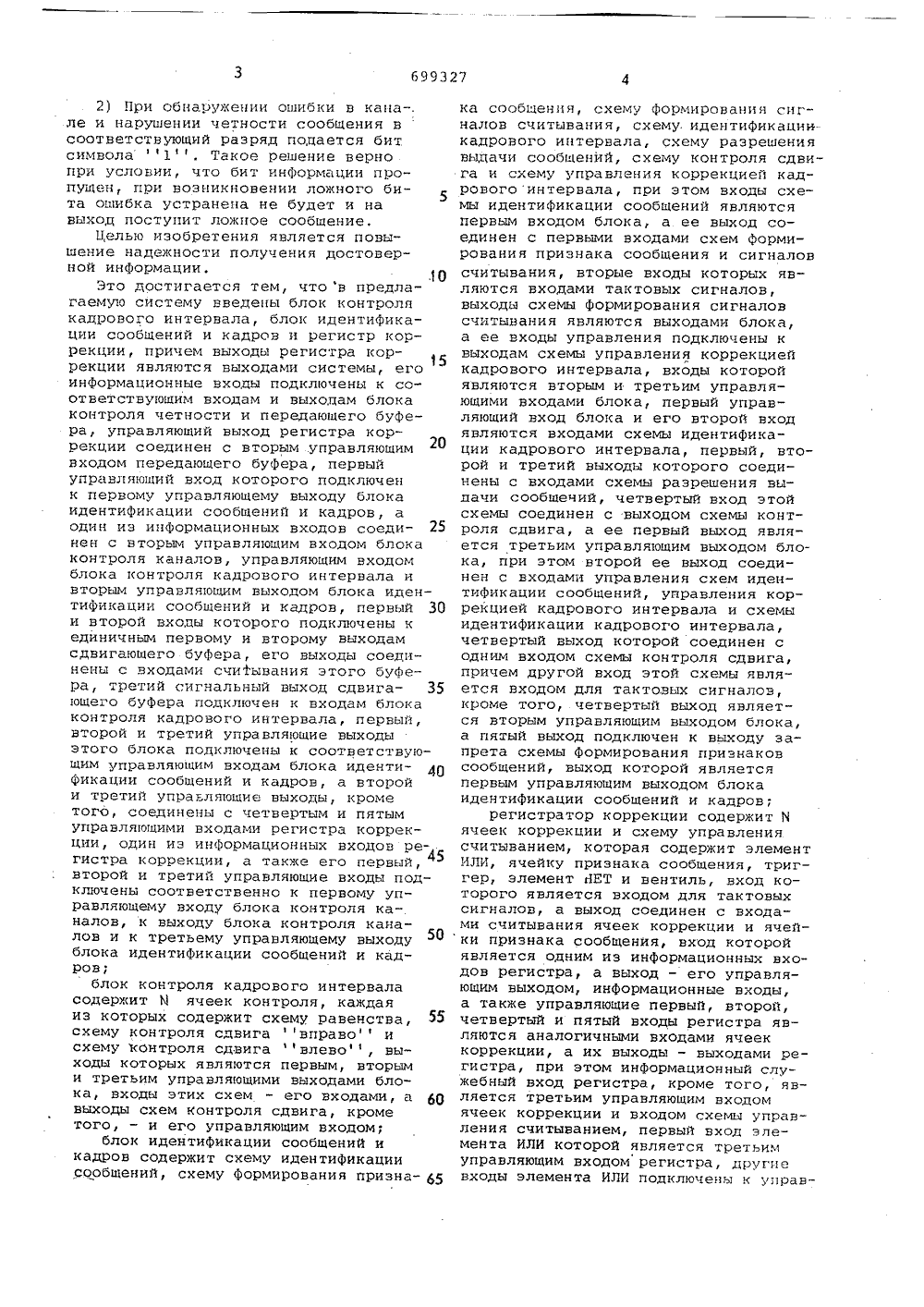

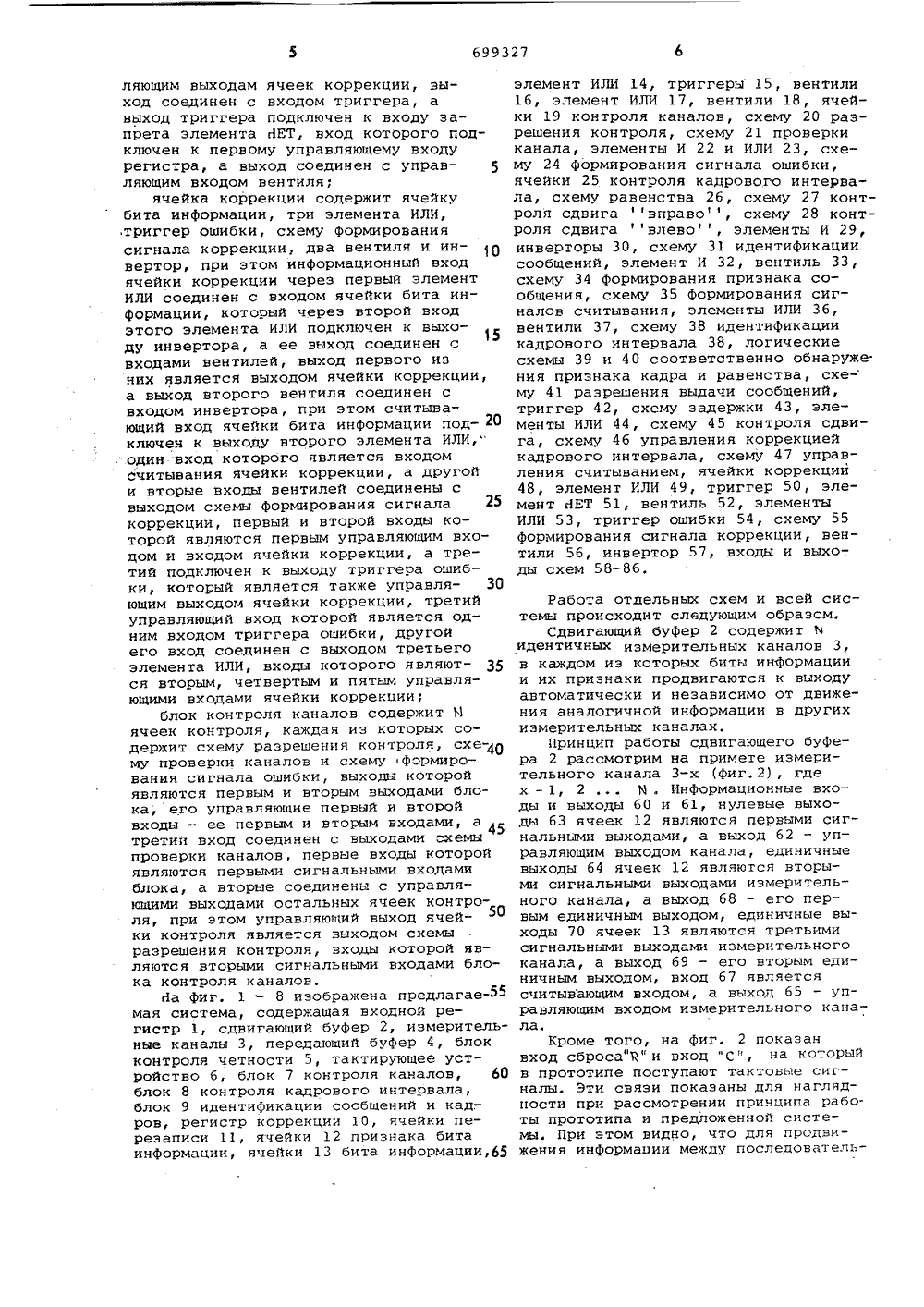

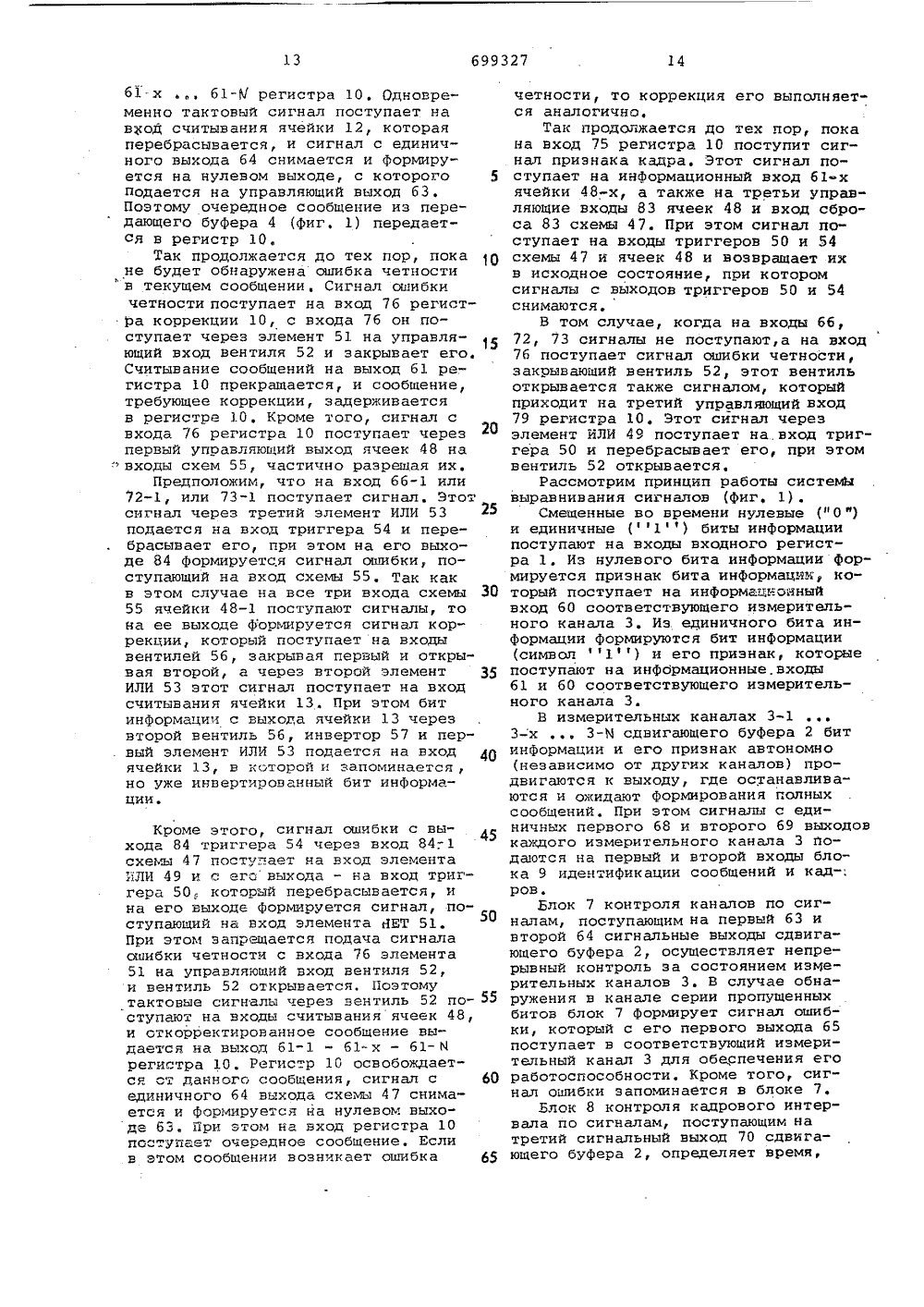

Союз Советских Социалистических Республик(51)м. Кл. с присоединением заявки Ио 6 01 0 5/247 Государственный ком нтет СССР ао делам нзобретеннй н открытнй(71) Заявители 54) СИСТЕМА ВЫРАВНИВАНИЯ СИГНАЛОВ Изобретение относится к устройствам для выравнивания сигналов, появляющихся в нескольких информационных потоках, и может быть использовано в качестве буФера при считывании параллельно поступающей информации, записанной с высокой плотностью на магнитных носителях.Известно считывающее корректирующее устройство для цифровой информации с сокращенным временем считывания информации 1.Недостаток такого устройства заключается в том, что считанный бит информации должен ожидать остальные биты данного сообщения, поступающие на вход устройства с некоторым смещением во времени, что снижает плотность записи параллельной информации на магнитный носитель.Наиболее близкой к изобретению по технической сущности является система выравнивания сигналов, содержащая последовательно подключенные входной регистр, сдвигающий буфер, содержащий Й измерительных каналов и передающий буфер, а также блок контроля четности, тактирующее устройство, выходы которого соединены с синхронизирующими и считывающими входами соответствующих элементов, и блокконтроля каналов, входы которого подключены к первому и второму сигнальным выходам сдвигающего буфера, а еговыход подключен к управляющему входу этого буФера 2.Недостатками этой системы являют О ся:1) Цепи контроля обнаруживают только серии пропущенных битов, ложныебиты и единичные сбои при таком контроле не обнаруживаются. Это объясняется тем, что при заполнении информацией одного из каналов проверяютсяостальные каналы и, если обнаруживается канал, в котором нет ни одногобита информации, тогда Формируетсясигнал ошибки в данном канале. В том случае, когда в канале по. явился ложный бит или вместо двухбитов имеется один, сигнал ошибки не Формируется, так как такое состояние цепями контроля не раэлича" ется. Поэтому такие сообщения не корректируются и ошибочный бит некоторое время присутствует в измерительном канале.699327 20 50 ния Вторые Входы кстсрых являются входами тактовых сигналов, выходы схемы формирования сигналов считывания являются выходами блока, а ее входы управления подключены к выходам схемы управления коррекцией кацрового интервала, входы которой яв ляются вторым и третьим управляющими входами блока, первый управляющий вход блока и его второй вход являют-. ся входами схемы идентификации кадрового интервала, первый, второй и тре 1 О тий выходы которой соединены с аналсгичными входами схемы разрешения выдачи сообщений, четвертый вход этойсхемы соединен с выходом схемы контроля сдвига, а ее первый выход является третьим управляющим выходсм блока, при этом второй ее выход соединен с входами управления схем идентификации сообщений, управления коррекциейкадрового интервала и схемы идентификации кадрового интервала, четвертый выход которой соединен с одним входом схемы контроля сдвига, причемдругой вход этой схемы является входом,цля тактовых сигналов, кроме того, четвертый выход является вторымуправляющим выходом блока, а пятыйвыход поцключен к входу запрета схемы формирования признаков сообщений,выход которой является первым управляющим выходом блока идентификациисообщений и кадров,4, Система по и, 1, о т л и ч а -ю щ а я с я тем, что регистр коррекции содержит й ячеек коррекции и схему управления считыванием, котораясодержит элемент ИЛИ, ячейку признака сообщения, триггер,. элемент ЛЕТ и вентиль, вход котсоогс является вхсдом для тактовых сигналов, а выходсоединен с входами считывания ячееккоррекции и ячейки признака сообщения, вход которой является одним изинформационных входов регистра, авыход - его управлжощим входом, информационные входы, а также управляющие первый, второйчетвертый ипятый входы регистра являются аналогичными входами ячеек коррекции,а их выходы - выходами регистра, при этом информационный служебный входрегистра, кроме того, является третьим управляющим входом ячеек коррекции и входом схемь 1 управления считыванием, первый вхсц элемента ИЛИ ксторой является третьим управляющимвходом регистра, другие входы элемента ИЛИ подключены к управляющим выходам ячеек коррекции, выход соединен с входом триггера, а выход триггера подключен к входу запрета эле" 6 Омента НЕТ, вход которого подключен к первому управляющему входу регистра, а выход соединен с управляющимвходом вентиля,5, Система по п. 4, о т л и ч аю щ а я с я тем, что ячейка коррекции содержит ячейку бита информации,три элемента ИЛИ, триггер ошибки,схему формирования сигнала коррекции,два вентиля и инвертор, при этом информационный вход ячейки коррекциичерез первый элемент ИЛИ соединен свходом ячейки бита информации, который через второй вход этого элементаИЛИ подключен к выходу инвертора, аее выход соединен с входами вентилей,выход первого из них является выходом ячейки коррекции, а выход второго вентиля соединен с входом инвертора, при этом считывающий вход ячейкибита информации подключен к выходувторого элемента ИЛИ, один вход которого является входом считывания ячейки коррекции, а другой и вторые входы вентилей соединены с выходом схемы формирования сигнала коррекции,первый и второй входы которой являются первым управляющим входом и входом ячейки коррекции, а третий подключен к выходу триггера ошибки, которыйявляется также управляющим выходомячейки коррекции, третий управляющийвход которой является одним входомтриггера ошибки, другой его вход соединен с выходом третьего элементаИЛИ, входы которого являются вторым,четвертым и пятым управляющими входами ячейки коррекции.6. Система по п. 1, о т л и ч аю щ а я с я тем, что блок контроляканалов содержит М ячеек контроля,каждая из которых содержит схему разрешения контроля, схему проверки каналов и схему формирования сигналаошибки, выходы которой являются первым и вторым выходами блока, его управляющие первый и второй входы -ее первым и вторым входаьпл, а третийвход соединен с выходами схемы проверки каналов, первые входы которой являются первыми сигнальными вхоцамиблока, а вторые соединены с управляющими выходами остальных ячеек контроля, при этом управляющий выход ячеекконтроля является выходом схемы разрешения контроля, входы которой являются вторыми сигнальными входами блока контроля каналов. Источники информации,принятые вс внимание при экспертизе1. Патент США Р 3164774,кл. 328-61, 1968,2, Патент СШЛ Р 3509531,кл. 340-146.1, 1970 (прототип).2) При обнаружении ошибки в кана-.ле и нарушении четности сообщения всоответствующий разряд поцается битсимвола 1. Такое решение вернопри условии, что бит информации пропущен, при возникновении ложного бита ошибка устранена не будет и навыход поступит ложное сообщение,Целью изобретения является повышение надежности получения достоверной информации, 10Это достигается тем, что в предлагаемую систему введены блок контролякадрового интервала, блок идентификации сообщений и кадров и регистр коррекции, причем выходы регистра коррекции являются выходами системы, егоинформационные вхоцы подключены к соответствующим входам и выхоцам блокаконтроля четности и передающего буфера, управляющий выход регистра коррекции соединен с вторым .управляющимвходом передающего буфера, первыйуправляющий вход которого подключенк первому управляющему выходу блокаидентификации сообщений и кадров, аодин из информационных входов соединен с вторым управляющим входом блокаконтроля каналов, управляющим входомблока контроля кадрового интервала ивторым управляющим выходом блока идентификации сообщений и кадров, первый 30и второй входы которого подключены кединичным первому и второму выходамсдвигаюшего буфера, его выходы соединены с входами считывания этого буфера, третий сигнальный выход сдвигающего буфера подключен к входам блокаконтроля кадрового интервала, первый,второй и третий управляющие выходыэтого блока подключены к соответствующим управляющим входам блока идентификации сообщений и кадров, а второйи третий управляющие выходы, крометого, соединены с четвертым и пятымуправляющими входами регистра коррекции, один из информационных входов регистра коррекции, а также его первый,второй и третий управляющие входы подключены соответственно к первому управляющему входу блока контроля каналов, к выходу блока контроля каналов и к третьему управляющему выходублока идентификации сообщений и кадров;блок контроля кадрового интерваласодержит Й ячеек контроля, каждаяиз которых содержит схему равенства, Ысхему контроля сдвига вправо исхему контроля сдвига влево, выходы которых являются первым, вторыми третьим управляющими выходами блока, входы этих схем - его входами, а 6 Овыходы схем контроля сдвига, крометого, - и его управляющим входом;блок идентификации сообщений икадров содержит схему идентификациисообщений, схему формирования призна ка сообщения, схему формирования сигналов считывания, схему идентификациикадрового интервала, схему разрешениявыдачи сообщений, схему контроля сдвига и схему управления коррекцией кадровогоинтервала, при этом входы схемы идентификации сообщений являются первым входом блока, а ее выход соединен с первыми входами схем формирования признака сообщения и сигналовсчитывания, вторые входы которых являются входами тактовых сигналов, выходы схемы формирования сигналов считывания являются выходами блока, а ее входы управления подключены к выходам схемы управления коррекцией кадрового интервала, входы которой являются вторым и третьим управляющими входами блока, первый управляющий вход блока и его второй вход являются входами схемы идентификации кадрового интервала, первый, второй и третий выходы которого соединены с входами схемы разрешения выдачи сообщений, четвертый вход этой схемы соединен с выходом схемы контроля сдвига, а ее первый выход является третьим управляющим выходом блока, при этом второй ее выход соединен с входами управления схем идентификации сообщений, управления коррекцией кадрового интервала и схемы идентификации кадрового интервала, четвертый вьход которой соединен с одним входом схемы контроля сдвига, причем другой вход этой схемы является входом для тактовых сигналов, кроме того, четвертый выход является вторым управляющим выходом блока, а пятый выход подключен к выходу запрета схемы формирования признаков сообщений, выход которой является первым управляющим выходом блока идентификации сообщений и кадров;регистратор коррекции содержит й ячеек коррекции и схему управлениясчитыванием, которая содержит элементИЛИ, ячейку признака сообщения, триггер, элемент НЕТ и вентиль, вход которого является входом для тактовых сигналов, а выход соединен с входами считывания ячеек коррекции и ячейки признака сообщения, вход которой является одним из информационных входов регистра, а выход - его управляющим выходом, информационные входы, а также управляющие первый, второй, четвертый и пятый входы регистра являются аналогичными входами ячеек коррекции, а их выходы - выходами регистра, при этом информационный служебный вход регистра, кроме того, является третьим управляющим входом ячеек коррекции и входом схемы управления считыванием, первый вход элемента ИЛИ которой является третьим управляющим входом регистра, другиевходы элемента ИЛИ подключены к уиранляющим выходам ячеек коррекции, выход соединен с входом триггера, а выход триггера подключен к входу запрета элемента ЛЕТ, вход которого подключен к первому управляющему входу регистра, а выход соединен с управляющим входом вентиля;ячейка коррекции содержит ячейку бита информации, три элемента ИЛИ, .триггер ошибки, схему формирования сигнала коррекции, два вентиля и инвертор, при этом информационный вход ячейки коррекции через первый элемент ИЛИ соединен с входом ячейки бита инФормации, который через второй вход этого элемента ИЛИ подключен к выходу инвертора, а ее выход соединен с входами вентилей, выход первого из них является выходом ячейки коррекции, а выход второго вентиля соединен с входом инвертора, при этом считывающий вход ячейки бита информации под ключен к выходу второго элемента ИЛИ, один вход которого является входом Считывания ячейки коррекции, а другой и вторые входы вентилей соединены с выходом схемы формирования сигнала 25 коррекции, первый и второй входы которой являются первым управляющим входом и входом ячейки коррекции, а третий подключен к выходу триггера ошибки, который является также управля- ЗО ющим выходом ячейки коррекции, третий управляющий вход которой является одним входом триггера ошибки, другой его вход соединен с выходом третьего элемента ИЛИ, входы которого являют ся вторым, четвертым и пятым управляющими входами ячейки коррекции;блок контроля каналов содержит Я ячеек контроля, каждая из которых содержит схему разрешения контроля, схе 40 му проверки каналов и схему формирования сигнала ошибки, выходы которой являются первым и вторым выходами блока, его управляющие первый и второй входы - ее первым и вторым входами, а 45 третий вход соединен с выходами схемы проверки каналов, первые входы которой являются первыми сигнальными входами блока, а вторые соединены с управляющими выходами остальных ячеек контроля, при этом управляющий выход ячейки контроля является выходом схемы разрешения контроля, входы которой являются вторыми сигнальными входами блока контроля каналов.йа фиг. 1 - 8 изображена предлагаемая система, содержащая входной регистр 1, сдвигающий буфер 2, измерительные каналы 3, передающий буфер 4, блок контроля четности 5, тактирующее устройство б, блок 7 контроля каналов, 60 блок 8 контроля кадрового интервала, блок 9 идентификации сообщений и кад. - ров, регистр коррекции 10, ячейки перезаписи 11, ячейки 12 признака бита информации, ячейки 13 бита инФормации,65 элемент ИЛИ 14, триггеры 15, вентили 16, элемент ИЛИ 17, вентили 18, ячейки 19 контроля каналов, схему 20 разрешения контроля, схему 21 проверки канала, элементы И 22 и ИЛИ 23, схему 24 формирования сигнала ошибки, ячейки 25 контроля кадрового интервала, схему равенства 26, схему 27 контроля сдвига вправо, схему 28 контроля сдвига влево, элементы И 29, инверторы 30, схему 31 идентификации сообщений, элемент И 32, вентиль 33, схему 34 формирования признака сообщения, схему 35 формирования сигналов считывания, элементы ИЛИ 36, вентили 37, схему 38 идентификации кадрового интервала 38, логическиесхемы 39 и 40 соответственно обнаруже.ния признака кадра и равенства, схе-му 41 разрешения выдачи сообщений,триггер 42, схему задержки 43, элементы ИЛИ 44, схему 45 контроля сдвига, схему 46 управления коррекцией кадрового интервала, схему 47 управления считыванием, ячейки коррекции 48, элемент ИЛИ 49, триггер 50, элемент НЕТ 51, вентиль 52, элементы ИЛИ 53, триггер ошибки 54, схему 55 формирования сигнала коррекции, вентили 56, инвертор 57, входы и выходы схем 58-86,Работа отдельных схем и всей системы происходит следующим образом,Сдвигающий буфер 2 содержит йидентичных измерительных каналов 3,в каждом из которых биты информациии их признаки продвигаются к выходуавтоматически и независимо от движения аналогичной информации в другихизмерительных каналах,Принцип работы сдвигающего буфера 2 рассмотрим на примете измерительного канала 3-х (фиг.2), гдех = 1, 2И . Информационные входы и выходы 60 и 61, нулевые выходы 63 ячеек 12 являются первыми сигнальными выходами, а выход 62 - управляющим выходом канала, единичныевыходы 64 ячеек 12 являются вторыми сигнальными выходами измерительного канала, а выход 68 - его первым единичным выходом, единичные выходы 70 ячеек 13 являются третьимисигнальными выходами измерительногоканала, а выход 69 - его вторым единичным выходом, вход 67 являетсясчитывающим входом, а выход 65 - управляющим входом измерительного канала.Кроме того, на фиг. 2 показанвход сброса"Ч" и вход "Сц, на которыйв прототипе поступают тактовые сигналы, Эти связи показаны для наглядности прирассмотрении принципа работы прототипа и предложенной системы. При этом видно, что для продвижения информации между последовательно соединенными парами ячеек 12 и 33 тактовые сигналы не требуются.На входь: поступают сигналы сброса и через элемент ИЛИ 14 они обнуляют триггеры 15.Бит информации, символ 0 или 1, поступает на вход 61 триггера 15 ячейки 13, При этом символ "0 никаких изменений не производит, а символ 1 перебрасывает триггер 15, и на его единственном выхо)О де 70 формируется сигнал (потенциал). Одновременно бит признака информации, символ 1, поступает на. вход 60 триггера 15 ячейки 12, который перебрасывается. При этом сигнал с нуле- ного выхоца 63 снимается и формируется на его единичном 64 выходе, Этот сигнал поступает на один вход ячейки перезаписи 11, и, если при этом следующая пара ячеек 12 и 13 свободна, то с нулевого выхода 63 ячейки 2 О 12 этой пары на второй вход ячейки 11 также поступает сигнал. В этом случае на. выходе ячейки 11 формируется сигнал перезаписи, который поступает на входы вентилей 16, при этом бит 25 информации и его признак переписываются в следующую пару ячеек 12 и 13, Одновременно сигнал с выхода ячейки 11 через элемент ИЛИ 14 поступает на входы триггеров 15 ячеек 12 и 13 дан- ЗО ной пары и обнуляет их. При этом снимается сигнал с выхода 70 ячейки 13, если он был, а также с выхода 64 ячейки 12 и формируется на ее выходе 63, что свидетельствует о готовности дан ной пары ячеек 12 и 13 к приему очередной информации.Выходная пара ячеек 12 и 13 в каждом измерительном канале 3 своей ячейки перезаписи не имеет, поэтому инфор-)О мация из таких ячеек передается на выход буфера 2 считывающими сигналами поступающими на вход 67.В том случае, когда в канале 3 обнаружена серия пропущенных битов информации, на вход 65 поступает сиг 45 нал ошибки, который через элемент ИЛИ 17 поступает на вход ячейки 12 выходной пары, обеспечивая перебростриггера в этой ячейке и формирование сигнала на единичном выходе 68 данно О го канала 3.Функциональные связи, поясняющиепринцип работы передающего буфера 4показаны на фиг. 3, где ячейки перезаписи 11 собраны по схеме И на три 55входа ячейки 12 идентичны ячейкампризнака бита информации. Также показаны информационные входы и выходы61, 74, 75 и 60, при этом для удобства пояснения принципа работы системы 6 О вход 74 назван информационным служебным входом, а выход 75 - информационным служебным выходом, так как на вход74 поступают и на выход 75 выдаются признаки кадров, в остальном этот ка" 65 нал (вентиль ) 8 и последовательно соединенные ячейки 13) аналогичен остальным каналам буфера 4, Кроме того, имеются нулевые 63 и единичные 64 выходы ячеек 12, синхронизирующий входТИ и управляющий вход 77.биты информации, соответствующиеодному сообщению, поступают на первые входы 61 вентилей 18, на. вторые входы этих вентилей 18 и вход 77 ячейки 12 подается признак сообщения. При этом биты информации записываются в ячейках 13, а бит признака сообщения в ячейке 12. Признак начала кадра поступает на вход 74 и запоминается в ячейке 13.При поступлении признака сообщения в ячейку 12 с ее нулевого выхода 63 снимается сигнал и формируется на ее единичном выходе 64. Этот сигнал поступает на вход ячейки 11. Если следующий регистр свободен, то с его нулевого выхода 63 на другой вход ячейки 11 также поступает сигнал, Поэтому в момент поступления на третий вход ячейки 11 тактового (синхронизирующего) сигнала на ее выходе Формируется сигнал перезаписи, который переписывает сообщение и его признак из ячеек 13 и 12 данного регистра в аналогичные ячейки следующего регистра. При этом ячейки 12 и 13 данного регистра возвращаюся в исходное состояние, при котором на выходе 63 ячейки 12 формируется сигнал готовности регистра к приему следующего сообщения.блок 7 контроля каналов содержит аналогичных ячеек контроля. Функциональные связи, поясняющие принцип работы блока, показаны на фиг. 4, гдеизображены ячейки 19-1, 19-х 19-Мконтроля каналов, третий управляющий вход и выход 78, второй 74 и первый 75 управляющие входы, первый 65 и второй 66 выходы ячеек 19 и блока 7. Кроме того, на фиг. 4 показаны сдвигающий буфер 2 и измерительные каналы 3-1, З-х З-Н.Допустим, что канал 3-х заполненбитами информации до заданного уровня,- тогда на вторых сигнальных выходах 64-х имеются сигналы, которые поступают на входы схемы 20. Этот сигнал поступает на третьи управляющие входы 78-х ячеек 19-1 и 19- М, которые проверяют состояние измерительных каналов 3-1 и З-М. Предположим, что канал 3-1 заполнен информацией, а на выходе 78- 1 формируется сигнал, поступающий ча вход 78-1 ячейки 19-х. Этот сигнал через элемент ИЛИ 23 подается на вход элемента И 22, разрешая проверку измерительного канала 3-х. Если при этом на остальные входы элемента И 3 поступают сигналы с первого сигнально 699327 10го выхода 63 канала З-х, что является признаком отсутствия битов информации в этом канале, то на выходеэлемента И 22 формируется сигнал, который поступает на третий вход схемы 24 формирования сигнала ошибки.йа первый выход 65 ячейки 19-х в этомслучае поступает сигнал ошибки,который поступает на управляющий вход65-х канала 3-х. Кроме того, сигнал .ошибки заполняется в схеме 24 ячей.ки 19-х.При поступлении на первый управляющий вход 75 признака текущего кадра, сигнализирующего о начале анализа и коррекции сообщений данного кадра, сигнал ошибки выдается на выходбб-х ячейки 19-х,При поступлении на второй управляющий вход 74 блока 7 признака начала следующего кадра. сигнал ошибки снимается с выхода 65-х. Сигнал ошибки для,следующего кадра, при необходимости,формируется заново, так как анализсостояний измерительных каналов 3осуществляется непрерывно,Ьлок 8 контроля кадрового интервала содержит Й ячеек контроля кадровых интервалов в каждом измерительном канале. Принцип работы блока 8рассмотрим на примере одной ячейкиконтроля, функциональные связи кото- ЭОрой приведены на фиг. 5, где изображены ячейки 25-х контроля кадровогоинтервала в канале З-х, первый 71,второй 72, третий 73 управляющие выходы, управляющий вход 74 и входы 70. 35В табл. 1 Фиг. 8 показан примерный код 110011 кадрового интервала,который следует в каждом измерительном канале 3 одновременно. Такой коддостаточен для реализации сдвига 40вправо и влево на два такта(два бита информации в канале). Присдвиге вправо выполняется операция перемещения бита инФормации вправо в данном канале. При сдвиге влево выполняется операция сдвига вправо бита информации во всех каналах 3,кроме данного.В табл. 2 фиг. 8 приведены три примера, поясняющие принцип анализа кадрового интервала, Символом Х обозначены неизвестные символы, поступающиев кадровый интервал из предшествующего или последующего сообщений.П р и м е р 1. Допустим, что кодкадрового интервала соответствует заданному, тогда на входы 70-1, 70-2 и70-5, 70-6 поступают сигналы, а навходы 70-3 и 70-4 они не поступают.В этом случае на выходе 7-1 формируется сигнал равенства, так как входы 70 - 3 и 70-4 соединены с входамиэлемента И 29 через инвертор 30.П р и м е р 2. Предположим, что вканале 3-х появился ложный бит инфор. мации при передаче сообщений данно го кадра. Он смещает кадровый интервал влево. Поэтому на входе 70-3 появляется сигнал, а на входе 70-5 егонет. В этом случае на управляющем выходе 72 формируется сигнал сдвигавправо. Иа выходе 71 схемы 26 сигнала в этом случае не будет.П р и м е р 3. Допустим, что вканале 3-х потерян бит информации,когда кадровый интервал смещаетсявправо. Иа выходе 71 схемы 26 сигнала в этом случае не будет. При этомна выходе 70-2 сигнала нет, а на выходе 70-4 он есть. Поэтому на выходе 73 формируется сигнал сдвига влево,Следует заметить, что схемы 27 и 28.разрешаются только в моменты, когдана входах элементов И 29 этих схемимеется сигнал признака кадра, поступающий на управляющий вход 74 ячеек 25 блока 8.Функциональные связи, поясняющиепринцип работы блока 9 идентификациисообщений и кадров, приведены на фиг,б, где показаны первые 66-1 68-йи вторые 69-1 69-У входы блока,первые 71-1 71-Н, вторые 72-172-й и третьи 73-1 73-М управляющие входы, синхронизирующий вход ТИ,на который подаются тактовые сигналы,первый 77, второй 74 и третий 79 управляющие выходы, выходы 67-1, 67-267- й блока, на которые поступают сигналы считывания,Схема 31 анализирует сигналы, поступающие на ее входы 68 в 1. 68-М,и при обнаружении сигналов на всехвходах на выходе элемента И 32 формируется сигнал, который через вентиль33, если он открыт, поступает на входсхемы 34, а также через элементы ИЛИ36 на первые входы вентилей 37. Поэтому при подаче на вторые входы этихэлементов тактового сигнала на выходах 67-1, 67-2 67-М блока формируются сигналы считывания, а на выходе 77 - сигнал признака сообщения,Схема 38 анализирует сигналы, поступающие на ее входы 69-1,. 69- Ми 71-1, 71-Ч, и при обнаружении заданного числа, например ь из Й сигналов на входах 69-1 69 - М , на выходе 80 схемы 39 Формируется сигналпредполагаемого начала кадрового интервала. Этот сигнал через третийвыход 80 схемы 38 поступает на входы схемы 43 и триггера 42, которыйперебрасывается, при этом снимаетсясигнал с выхода 82 схемы 41, и выдача сообщений запреЩается, так какзакрывается Вентиль 33 схемь 1 31. Одновременно снимается сигнал запрета суправляющего входа схемы 46, а такжесигнал с управляющего входа схемы 38.Если это был ложный признак кадрового.интервала, то задержанный сигнал свыхода схемы 43 через первый элементИЛИ 44 поступает на другой вход триггера 42, который возвращается в исходное состояние, и на выходе 82 фор-мируется сигнал.В том случае, когда логическаясхема равенства 40 обнаруживает и 5сигналов из М , поступающих на еевходы 71-1 71 - й , то формируетсясигнал, подтверждающий наличие кадрового интервала в сдвигающем буфере 2 (фиг. 1, 2, 5). Этот сигнал свыхода 86 поступает на вход схемы;39 и через второй выход схемы 38 навход схемы 43, которая сбрасывает задержанный сигнал. Схема 39 в этомслучае Формирует сигнал признака кадра, который через четвертый выходсхемы 38 поступает на второй управляющий выход 74 блока 9 (фиг, 1), а также на вход схемы 45, разрешая контрольсдвига.Одновременно сигнал формируетсяи на выходе 85 схемы 39, который через пятый выход схемы 38 поступаетна вход схемы 34, запрещая формирование признаков сообщения,Если при этом на все входы 71-171- Мсхемы равенства 40 поступаютсигналы равенства (фиг, 5), то на еевыходе 84 Формируется сигнал, который через первый выход схемы 38 поступает на первый вход второго элемента ИЛИ 44,Н том случае, когда обнаруженосмещение кадрового интервала в какомлибо из каналов 3 (на фиг. 1, 2, 5)за счет появления ложного бита или 35в результате пропуска действительныхбитов информации, тогда на выходе 81схемы 40 сигнал не формируется. Однако в этом случае поступает сигнал наодин из входов 72-172 - М схемы 46, 40При этом на соответствующем ее выходе Формируется сигнал,Допустим, что сигнал поступает навыход 72-1 схемы 46, Этот сигнал через элемент ИЛИ 36 схемы 35 подается на вход вентиля 37. Поэтому очередной тактовый сигнал, поступающийна вторые входы вентилей 37, сформирует на выходе 67-1 блока 9 считывающий сигнал. При этом выполняется опе рация сдвига вправо на один бит инФормации в канале 3-1 (фиг. 1, 2, 5).Одновременно тактовый сигнал поступает на вход схемы 45, которая контролирует такты сдвига.При Формировании сигнала на выходе 73-1 схемы 46 он через элементыИЛИ 36.поступает на входы всех вентилей 37, кроме данного, Поэтому очередной тактовый сигнал поступает через открытые вентили 37 на выходы67-2 67-Н блока 9. При этом выполняется операция сдвига влево битов информации во всех каналах 3-2,З-И, кроме данного 3-1 (фиг, 1, 2,5), 65 После обработки заданного количества тактов сдвига на выходе схемы 45 формируется сигнал, поступающий на второй вход второго элемента ИЛИ 44, С выхода второго элемента ИЛИ 44 сигнал поступает на третий управляющий выход 79 блока, а также через первый элемент ИЛИ 44 - на вход триггера 42 и возвращает его в исходное состояние, При этом на выходе 82 схемы 41 формируется сигнал, который поступает на входы управления схем 46 и 38, схема 46 запрещается, а с выхода 74 схемы 38 снимается сигнал признака кадраКроме того, сигнал с выхода 82 подается на управляющий вход вентиля 33 и открывает его. Поэтому схема 31 по результатам анализа сигналов, поступающих на входы 68-1.,68-М, одновременно открывает все вентили 37, и тактовые сигналы подаются на выходы 67"1, 67-2 67-й, обеспечивая считывание полных слов кадрового интервала из каналов 3 сдвигающего буфера 2 (фиг. 1). однако при этом схема 34 остается закрытой сигналом, поступающим с выхода 85 схемы 38, поэтому на выходе 77 признаки таких сообщений не Формируются, а зто означает, что они в передающий буфер 4 не передаются (Фиг, 3), Сигнал на выходе 85 схемы 39 снимается после того, когда на ее входы 69-1.69-Н перестанут поступать слова, соответствующие коду кадрового интервала. После этого блок 9 обеспечивает формирование и передачу полных сообщений нового кадра.функциональные связи, поясняющие принцип работы регистра коррекции 10, приведены на фиг. 7, где показаны управляющие входы первый 76, второй 66-166-х66-й, третий 79, четвертый и пятый 72-172 х72-М и 73-1 73-х73-Ч соответственно, информационные входы 60, 61-1 75 61-М, вход считывания ТИ, а также управляющий выход 63 и выходы 61-161 х61" М.Биты информации текущего сообщения поступают на входы 61 регистра10, При этом бит информации черезпервый элемент ИЛИ 53 поступает навход ячейки 13 и запоминается в ней,5 ит признака сообщения подается навход 60 ячейки 12 и запоминается вней, при этом снимается сигнал с выхода 63 и формируется на единичномвыходе 64 схемы 47, с выхода которойон поступает на входы схем 55 ячеек48,Тактовые сигналы через вентиль 52,если он открыт, подаются на считывающие входы ячеек 48 и через вторыеэлементы ИЛИ 53 на входы считыванияячеек 13. При этом биты информации,хранящиеся в них, через первый вентиль 56 поступают на выход 61-1бО 61.х61-М регистра 10, Одновременно тактовый сигнал поступает навход считывания ячейки 12, котораяперебрасывается, и сигнал с единичного выхода 64 снимается и формируется на нулевом выходе, с которого 5подается на управляющий выход 63.Поэтому очередное сообщение из передающего буфера 4 (фиг, 1) передается в регистр 10.Так продолжается до тех пор, покане будет обнаружена ошибка четностив текущем сообщении, Сигнал ошибкичетности поступает на вход 76 регистра коррекции 10, с входа 76 он поступает через элемент 51 на управляюший вход вентиля 52 и закрывает его.Считывание сообщений на выход 61 регистра 10 прекращается, и сообщение,требующее коррекции, задерживаетсяв регистре 10, Кроме того, сигнал свхода 76 регистра 10 постугает черезпервый управляющий выход ячеек 48 на" входы схем 55, частично разрешая их,Предположим, что на вход 66-1 или72-1, или 73-1 поступает сигнал, Этотсигнал через третий элемент ИЛИ 53подается на вход триггера 54 и перебрасывает его, при этом на его выходе 84 формируется сигнал ошибки, поступающий на вход схемы 55, Так какв этом случае на все три входа схемы 3055 ячейки 48-1 поступают сигналы, тона ее выходе формируется сигнал коррекции, который поступает на входывентилей 56, закрывая первый и откры"вая второй, а через второй элементИЛИ 53 этот сигнал поступает на входсчитывания ячейки 13, При этом битинформации с выхода ячейки 13 черезвторой вентиль 56, инвертор 57 и пер. вый элемент ИЛИ 53 подается на входячейки 13, в которой и запоминается,но уже инвертированный бит информации,Кроме этого, сигнал ошчбки с выхода 84 триггера 54 через вход 84.-1 схем 47 постуает на вход элемента ИЛИ 49 и с его выхода - на вход триггера 50, который перебрасывается, и на его выходе формируется сигнал, поступающий на вход элемента ЛЕТ 51.При этом запрещается подача сигнала ошибки четностч с входа 76 элемента 51 на управляющий вход вентиля 52, и вентиль 52 открывается. Поэтому тактовые сигналы через вентиль 52 по ступают на входы считывания ячеек 48, и откорректированное сообщение выдается на выход 61"1 - 61-х - 61- й регистра 10. Регис=р 10 освобождается ст данного сообщения, сигнал с единичного 64 выхода схемы 47 снимается и формируется на нулевом выходе 63, При этом на вход регистра 10 поступает очередное сообшение. Если в этом сообщении возникает ошибка 65 четности, то коррекция его выполняется аналогично.Так продолжается до тех пор, покана вход 75 регистра 10 поступит сигнал признака кадра. Этот сигнал поступает на информационный вход 61-хячейки 48-х, а также на третьи управ"ляюшие входы 83 ячеек 48 и вход сброса 83 схемы 47 При этом сигнал поступает на входы триггеров 50 и 54схемы 47 и ячеек 48 и возвращает ихв исходное состояние, при которомсигналы с выходов триггеров 50 и 54снимаются,В том случае, когда на входы бб,72, 73 сигналы не поступают,а на вход76 поступает сигнал ошибки четности,закрываюший вентиль 52, этот вентильоткрывается также сигналом, которыйприходит на третий управляющий вход79 регистра 10. Этот сигнал черезэлемент ИЛИ 49 поступает на.вход триггера 50 и перебрасывает его, при этомвентиль 52 открывается.Рассмотрим принцип работы системМвыравнивания сигналов (фиг, 1).Смещенные во времени нулевые ("0 ")и единичные (1) биты информациипоступают на входы входного регистра 1, Из нулевого бита информации формируется признак бита информации, который поступает на информационныйвход 60 соответствующего измерительного канала 3, Из единичного бита информации формируются бит информации(символ 1) и его признак, которыепоступают на инфбрмационные.входы61 и 60 соответствующего измерительного канала 3.В измерительных каналах 3-13-х3-й сдвигаюшего буфера 2 битинформации и его признак автономно(независимо от других каналов) продвигаются к выходу, где останавливаются и ожидают Формирования голныхсообщений, При этом сигналы с единичных первого 68 и второго 69 выходовкаждого измерительного канала 3 подаются на первый и второй входы блока 9 идентификации сообщений и кад-;ров.Блок 7 контроля каналов по сигналам, поступающим на первый 63 ивторой 64 сигнальные выходы сдвигаюшего буфера 2, осуществляет непрерывный контроль за состоянием измерительных каналов 3. В случае обнаружения в канале серии пропущенныхбитов блок 7 формирует сигнал ошибки, который с его первого выхода 65поступает в соответствующий измерительный канал 3 для обеспечения егоработоспособности, Кроме того, сигнал ошибки запоминается в блоке 7,Блок 8 контроля кадрового интервала по сигналам, поступающим натретий сигнальный выход 70 сдвигаюшего буфера 2, определяет время, 699327 16когда в буфере 2 находится кадровый (разделительный) интервал. Сигналы о наличии или отсутствии кадрового интервала непрерывно поступают с первого управляющего выходаблока 8 на соответствующий вход блока 9.Блок 9 идентификации сообщенийи кадров по сигналам, поступающимна его первый вход 68, определяетналичие на выходе сдвигающего буфера 2 полного сообщения и формируетв этом случае сигналы считывания,поступающие с его выхода на входы 67всех измерительных каналов 3, Поэтому полные сообщения поступают на информационные входы 61 передающего буфера 4. Оцновременно на первый управляющий вход буфера 4 с выхода 77 блока 9 поступает признак сообщения,Тактовые сигналы, поступающие с выхода тактирующего устройства б, обеспечивают продвижение таких .сообщений и их признаков на выход передающего буфера 4, Если корректирующийрегистр 10 свободен, то на второйуправляющий вход 63 передающего буфера 4 поступает сигнал, поэтому сообщение из буфера 4 поступает на информационные входы 60 61 и 75 регистра 10, а также на входы блока 5контроля четности. Признак текущего 30кадра следует в составе первого сообщения этого кадра, кроме того, поступает с информационного служебного выхода 75 и на первый управляющийвход блока 7, на втором выходе 66 которого формируется сигнал ошибки всоответствующем измерительном кана -ле 3, если оц был при передаче сообщений данного кадра.Этот сигналподается на второй управляющий вход 4 Орегистра 10,Если на первый управляющий вход76,регистра 10 не поступает сигналошибки четности, то сигналы считывания с выхода тактирующего устройства 45б считывают сообщение из регистра 10на выход 61 системы. При этом на еговыходе 63 формируется сигнал готовности регистра 10 к приему очередного сообщения. Этот сигнал поступаетна второй управляющий вход буфера 4,При этом очередной тактовый сигнал,поступающий с выхода тактирующегоустройства б на вход буфера 4, переписывает из буфера 4 в регистр 10очередное сообщение, а блок 5 осуществляет контроль четности этогосообщения и формирует на ьыходе 76соответствующий сигнал.Допустим, что на вход 76 регистра 10 подается сигнал ошибки четности, тогда регистр 10 с учетом ошиб-ки в измерительном канале, котораяподается на его вход 66, осуществляет коррекцию бита информации в соответствующем разряде данного со общения. После этого откорректированное сообщение поступает на выход 61 системы,В том случае, когда на второй управляющий вход 66 регистра 10 сигнал ошибки в канале не подается, а на первый управляющий вход 76 поступает сигнал ошибки четности, выдача сообщений на выход 61 системы приостанавливается и сообщение, требующее коррекции, остается в регистре 10. При этом вход 63 передающего буФера 4 сигнал не подается и текущие сообщения данного кадра накапливаются в буфере 4. Блок 9 идентификации сообщений икадров по сигналам, поступающим свторых единичных выходов 69 измерительных каналов 3, а также с выхода 71блока 8, определяет момент, когдакадровый интервал поступает на выходсдвигающего буфера 2. При этом передача сообщений из буфера 2 в буфер 4приостанавливается и на втором управляющем выходе 74 блока 9 формируетсясигнал признака очередного кадра, который подается на второй управляощийвход блока 7 и снимает сигнал ошибки с его первого выхода 65, если онбыл, а также признак кадра поступаетна информационный служебный вход передающего буфера, где он запоминаетсядо поступления на его вход первогосообщения этого кадра. С этим сообщением признаккадра продвигается навыход передающего буфера 4,Кроме того, с выхода 74 блока 9признак кадра поступает на управляющий вход блока 8, разрешая формирование на втором 72 и третьем 73 управляющих выходах сигнала ошибки кадрового интервала, т.е. наличие ложных или единичных пропущенных битовинформации в сообщениях данного кадра, которые приводят к смещению кадрового интервала в соответствующихизмерительных каналах 3 (табл, 1 и 2),Эти сигналы с выходов 72 и 73 блока8 поступают на регистр 10, который сучетом ошибки четности корректируеттекущие сообщения данного кадра, после чего такие сообщения поступаютна выход 61 системы.Одновременно эти сигналы подаютсяна второй 72 и третий 73 управляющиевходы блока 9, который осуществляеткоррекцию кадрового интервала путемФормирования считывающих сигналовна соответствующих выходах 67-х (х -1, 2 М). При этом кадровые интервалы в соответствующих измерительныхканалах 3-х смещаются вправо иливлево. После коррекции кадровогоинтервала или их равенства заданному коду с выхода 74 блока 9 снимаетсясигнал признака кадра, и выходы 72 и73 блока 8 закрываю.ся,а блок 9 опре 17 699327Формула изобретения 451. Система выравнивая,я сигналов,содержащая пос:-,:. дов ат-.-:;.ь":.о подключен 50 60 деляет полные сообщения и считывают их на выход 61 сдвигаюшего буфера 2.Однако в течение коррекции кадрового интервала и считывания слов кадрового интервала на выходе 77 блока 9 признаки сообщений не формируются. Поэтому такие слова в передающий буфер 4 не поступают.После окончания коррекции кадрового,интервала на третьем управляющем выходе 79 блока 9 формируется сигнал, поступающий на третий управляющий вход регистра 10. Этот сигнал разрешает выдачу сообщений на выход 61 системы даже в том случае, когда нет сигналов ошибки ни в каналах, ни в кадровом интервале и сообщение не может быть откорректировано, хотя на вход 76 поступает сигнал ошибки четности, Такая выдача сообщений будет продолжаться д поступления на вход 75 регистра 10 признака следующего кадра.В случае переполнения какого-либо из измерительных каналов 3 на выходе 62 этого канала формируется сигнал, Этот сигнал можно использовать для управления скоростью считывания информации с магнитного носителя и подачи сообщений на вход регистра 1,Таким образом, предложенная систе. ма обеспечивает коррекцию не только серий пропущенных битов информации, но также и коррекцию сообщений при возникновении в измерительных каналах единичных пропусков или ложных битов. Кроме того, она обеспечивает периодический контроль (по окончанию кадра сообщений) измерительных каналов и их освобождение от ошибочных битов информации появляющихся в таких каналах. Э о повышает надежность получения достоверной информации,;ь:е входной регистр. сдвигающий буфер, содержащий М измерительных каналов и передающий буфер, а такжеблок контроля четности, тактирующееустройство, выходы которого соединены с синхронизируюшим;: и считывающими входами соответсвуюших элементов, и блок контроля к:; в :плов, вхотыкоторого подключены к и-рвому и второму сигнальным выходам сдвигающегобуфера, а его выход подключен к управляющему входу этого буфера, о тл и ч а ю ш а я с я т.-";, что, с целью повышения надежности получениядостоверной информации, в нее введены блок контроля кадровсго интервала, блок идентификации сообщений икадров и регистр коррекции, причемвыходы регистра коррекции являются 10 15 20 25 ЗО 35 40 выходами систеьж, его информационные входы подключены к соответствующим входам и выходам блока контроля четности и передающего буфера, управлпоший выход регистра коррекции соединен с вторым управляющим входом передающего буфера, первый управляющий вход которого подключен к первому управляющему выходу блока идентификации сообщений и кадров, а один из информационных входов соединен с вторым управляющим входом блока контроля каналов, входом блока контроля кадрового интервала и вторым управляющим выходом блока идентификации сообщений и кадров, первый и второй входы которого подключены к единичным первому и второму выходам сдвигающего буфера, еговыходы соединены с входами считыванияэтого буфера, третий сигнальный выход сдвигающего буфера подключен квходам блока контроля кадрового интервала, первый, второй и третий управляющией выходы этого блока подключены к соответствующим управляющимвходам блока идентификации сОобщенийи кадров, а второй и третий управляющие выходы, кроме того, соединены счетвертым и пятым управляющими входами регистра коррекции, один из информационных входов регистра коррекции, а также его первый, второй итретий управляющие входы подключенысоответственно к первому управляющему входу блока контроля каналов, квыходу блока контроля четности, квторому выходу блока контроля каналови к третьему управляющему выходу блока идентификации сообщений и кадров,2, Система по п. 1, о т л и ч а -ю ш а я с я тем, что блок контролякадрового интервала имеет Н ячеекконтроля, каждая из которых содержитсхему равенства, схему контроля сдвига вправо и схему контроля сдвига влево, выходы которых являются первым, вторым и третьим управляющими выходами блока, входы этих схем -его входами, а входы схем контролясдвига, кроме того, - и его управляющим входом,3 Система по п, 1, о т л и ч а ю ш а я с я тем, что блок идентификации сообщений и кадров содержит схему идентификации сообщений, схему формирования признака сообщений, схему форьирования сигналов считывания, схему идентификации кадрового интервала, схему разрешения выдачи сообщений, схему контроля сдвига и схему управления коррекцией кадрового интервала, при этом входы схемы идентификации сообщений являются первым входом блока, а ее выход соединен с первыми входами схем формирования признака сообщений и сигналов считыва

СмотретьЗаявка

2536871, 20.10.1977

ВСЕСОЮЗНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ЛЕСОВОДСТВА И МЕХАНИЗМА ЛЕСНОГО ХОЗЯЙСТВА, НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ АВТОМАТИЗИРОВАННЫХ СИСТЕМ ПЛАНИРОВАНИЯ И УПРАВЛЕНИЯ В СТРОИТЕЛЬСТВЕ

СКРИПКО ВЛАДИМИР АБРАМОВИЧ, СОФИНСКИЙ ЛЕОНИД ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G01D 5/247

Метки: выравнивания, сигналов

Опубликовано: 25.11.1979

Код ссылки

<a href="https://patents.su/13-699327-sistema-vyravnivaniya-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Система выравнивания сигналов</a>

Предыдущий патент: Устройство для контроля наличия металла на рольганге прокатного стана

Следующий патент: Отсчетно-измерительное устройство для металлорежущих станков

Случайный патент: Способ конвертирования медных и медно-никелевых штейнов