Устройство для ввода в микроэвм дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

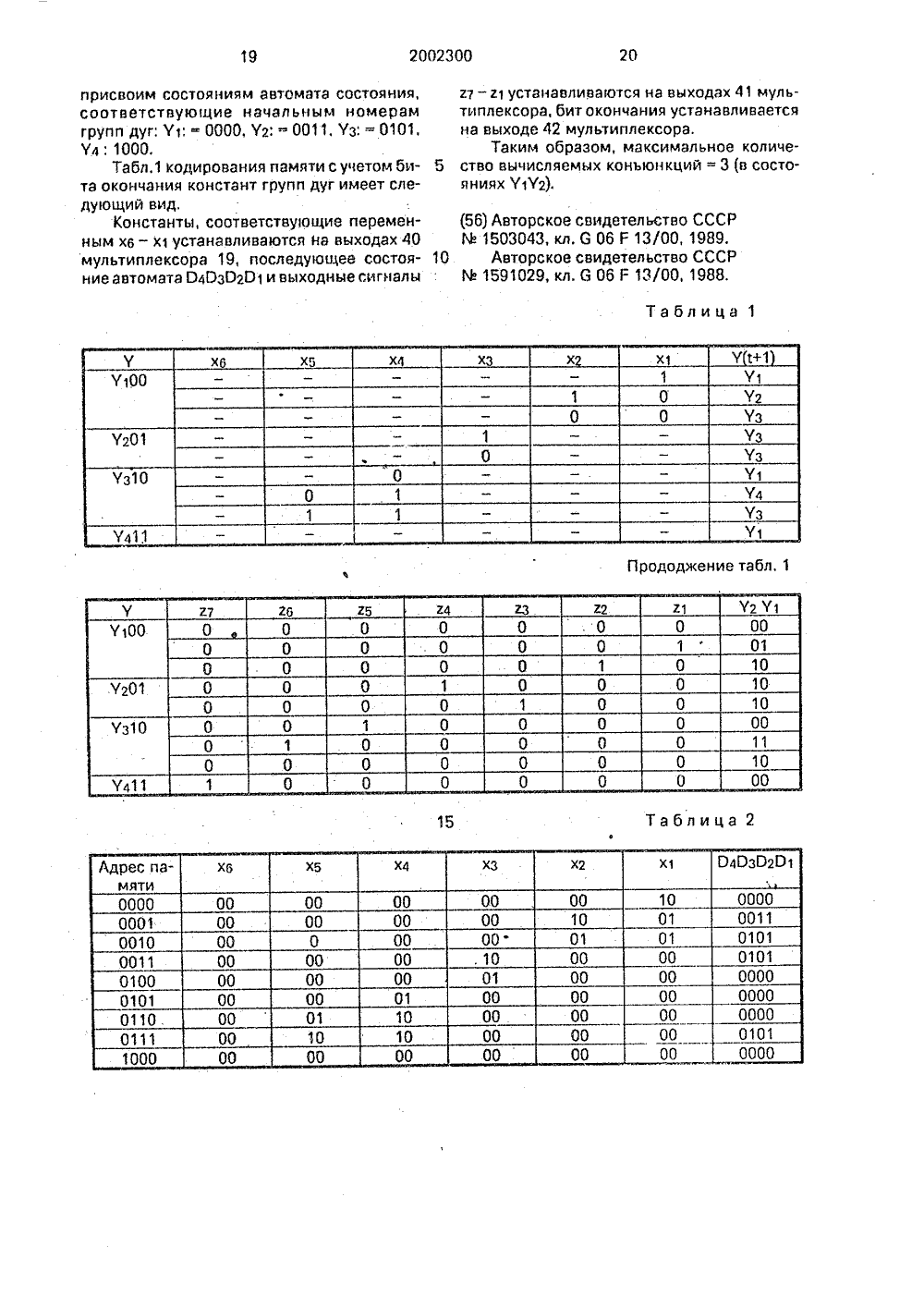

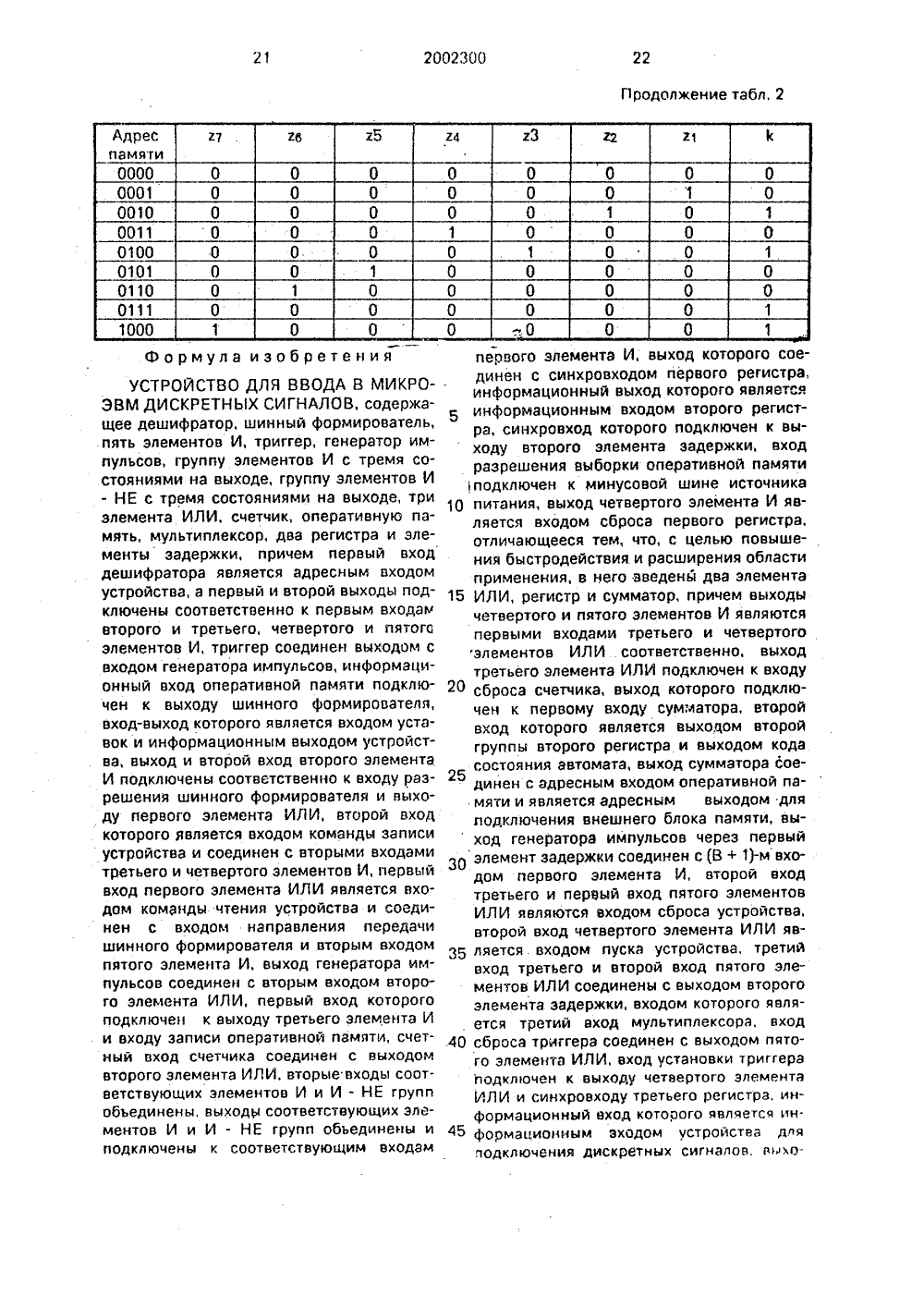

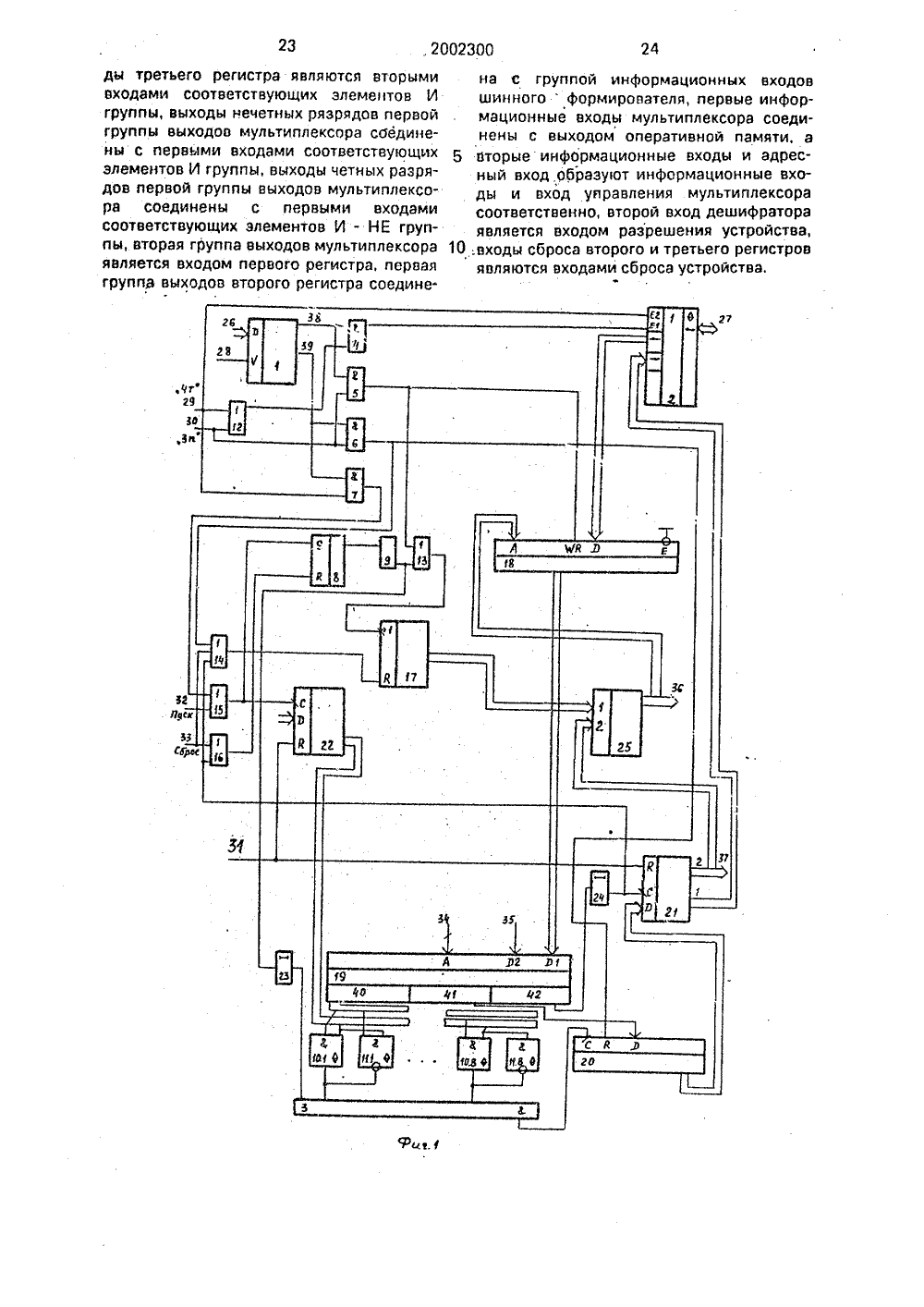

ПЫЛАНИЕ ИЗОБРЕТЕ 1 С ПАТЕРУ Комитет Российской Федерации по патентам и товарным знакам(64) УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМДИСКРЕТНЫХ СИГНАЛОВ(Я) 60 б Г 1300 для программно-аппаратной реализации поспедовательностных автоматов. Цель изобретения - повышение быстродействия устройства и расширение области его применения. Устройство содержит дешифратор, шинный формирователь, элементы И, триггер, генератор импульсов, группу из В элементов И с тремя состояниями на выходе, где В - разрядность входного дискретного сигнала, группу из В элементов И - НЕ с тремя состояниями на выходе, элементы ИЛИ, счетчик оперативную память. мультиплексор, регистры, элементы задержки, сумматор,входы адреса, 2 табл, 2 ил.2002300 20 Таблица 1 Прододжение табл. 1 Таблица 2 присвоим состояниям автомата состояния, соответствующие начальным номерам групп дур; У 1, " 0000, У 2:0011, Уз: = 0101, У 4; 1000,Табл,1 кодирования памяти с учетом бита окончания констант групп дуг имеет следующий вид,Константы, соответствующие переменным х 6 - х 1 устанавливаются на выходах 40 мультиплексора 19, последующее состояние автомата О 10 з 0201 и выходные сигналы г 7 - г 1 устанавливаются на выходах 41 мультиплексора, бит окончания устанавливается на выходе 42 мультиплексора.Таким образом, максимальное количе ство вычисляемых коньюнкций = 3 (в состояниях У 1 У 2).(56) Авторское свидетельство СССР ЬЬ 1503043, кл. 0 06 Е 13/00, 1989.10 Авторское свидетельство СССР % 1591029, кл. 8 06 Г 13/00, 1988.2002300 Продолжение табл, 2 Формула изобретения УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ, содержащее дешифратор, шинный формирователь, пять элементов И, триггер, генератор импульсов, группу элементов И с тремя состояниями на выходе, группу элементов И - НЕ с тремя состояниями на выходе, три элемента ИЛИ, счетчик, оперативную память, мультиплексор, два регистра и элементы задержки, причем первый вход дешифратора является адресным входом устройства, а первый и второй выходы подключены соответственно к первым входам второго и третьего, четвертого и пятога элементов И, триггер соединен выходом с входом генератора импульсов, информационный вход оперативной памяти подключен к выходу шинного формирователя, вход-выход которого является входом уставок и информационным выходом устройства, выход и второй вход второго элемента И подключены соответственно к входу разрешения шинного формирователя и выходу первого элемента ИЛИ, второй вход которого является входом команды записи устройства и соединен с вторыми входами третьего и четвертого элементов И, первый вход первого элемента ИЛИ является входом команды чтения устройства и соединен с входом направления передачи шинного формирователя и вторым входом пятого элемента И, выход генератора импульсов соединен с вторым входом второго элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И и входу записи оперативной памяти, счетный вход счетчика соединен с выходом второго элемента ИЛИ, вторые входы соответствующих элементов И и И - НЕ групп объединены, выходы соответствующих элементов И и И - НЕ групп обьединены и подключены к соответствующим входам первого элемента И, выход которого соединен с синхровходом первого регистра, информационный выход которого является информационным входом второго регистра, синхровход которого подключен к выходу второго элемента задержки, вход разрешения выборки оперативной памяти 1 подключен к минусовой шине источника 10 питания, выход четвертого элемента И является входом сброса первого регистра, отличающееся тем, что, с целью повышения быстродействия и расширения области применения, в него.введенй два элемента 15 ИЛИ, регистр и сумматор, причем выходычетвертого и пятого элементов И являются первыми входами третьего и четвертого элементов ИЛИ соответственно, выход третьего элемента ИЛИ подключен к входу 20 сброса счетчика, выход которого подключен к первому входу сумматора, второй вход которого является выходом второй группы второго регистра и выходом кода состояния автомата, выход сумматора соединен с адресным входом оперативной памяти и является адресным выходом для подключения внешнего блока памяти, вы ход генератора импульсов через первый 0 элемент задержки соединен с (В+ 1)-м входом первого элемента И, второй вход третьего и первый вход пятого элементов ИЛИ являются входом сброса устройства, второй вход четвертого элемента ИЛИ яв ляется. входом пуска устройства, третийвход третьего и второй вход пятого элементов ИЛИ соединены с выходом второго элемента задержки, входом которого является третий вход мультиплексора, вход .40 сброса триггера соединен с выходом пятого элемента ИЛИ, вход установки триггера подключен к выходу четвертого элемента ИЛИ и синхровходу третьего регистра. информационный вход котооого является ин формационным входом устройства дляподключения дискретных сигналов. аыоды третьего регистра являются вторыми входами соответствующих элементов И группы, выходы нечетных рязрядов первой группы выходов мультиплексора соединены с первыми входами соответствующих элементов И группы, выходы четных разрядов первой группы выходов мультиплексора соединены с первыми входами соответствующих элементов И - НЕ группы, вторая группа выходов мультиплексора является входом первого регистра, первая группа выходов второго регистра соединена с группой информационных входов шинногоформирователя, первые информационные входы мультиплексора соединены с выходом оперативной памяти, а Б вторые инфбрмационные входы и адресный вход Образуют информационные входы и вход управления мультиплексора соответственно, второй вход дешифратора является входом разрешения устройства, 10 .входы сброса второго и третьего регистровявляются входами сброса устройства.2002300 Составитель С.Тарин Техред М,Моргентал КорректорВ,Петраш дактор чикова Тираж Подписное НПО "Поиск" Роспатента113035, Москва, Ж, Раушскав наб., 4/Б,аказ 317 оизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина;Изобретение относится к вычислительной технике, в частности к устройствам сопряжения "интеллектуальных" датчиков, и может быть использовано для ирограммггоаппаратной реализации последавательностных автоматов.Известно устройство, содержащее дешифратор адреса, пять элементов И, два элемента ИЛИ, шинный формирователь, группу элементов И с тремя состояниями на выходе, группу элементов И-НЕ с тремя со. стояниями на выходе, оперативнуго память, два триггера, генератор импульсов и счетчик.Недостатками такого устройства являются ниэкге быстродействие и узкая область ггрименения.Наиболее близким по технической сущности к предлагаемому является устройство, содержащее дешифратор, шиггный формирователь, пять элементов И,-гоуппу элементов И, генератор импульсов, группу элементов И с тремя состояниями на выходе, группу элементов И-НЕ с тремя состояниями гга выходе, три элемента ИЛИ, оперативную память термав и выходов, группу блоков оперативной памяти предикатов, два счетчика, груггпу мультиплексоров, два регистра, триггер, два элемента задержки, группу элементов ИЛИ, причем вход дешифратора подключен к входу устройства длл подключения шины адреса мик- роЭВМ, первьгй выход дешифратора соедгинен с первыми входами второго и третьего элементов И, выход второго элемента И соединен с входам выборки шинного Формирователя, вход задания направления передачи коараго и первый вход первого элемента ИЛИ соединены с входом устройства для подклгоченил команды ввода микроЭВМ, выход первого, элемента ИЛИ соединен с вторым входом второго элемента И, вторые входы перво"о элемента ИЛИ, третьего и четвертого элементов И соединены с входом устройства для подключеггия команды вывода микро- ЭВМ, вход-выход шинного Формирователя соединен с входам-выходом устройства для подключения к первым входам четвертого и пятого элементов И, второй вход которого подключен к входу устройства для подклгочения команды ввода микроЭВМ, выход пятого элемента И подклгоцегг к входу установки триггера, выход триггера подклгачен к входу генератора, выход которого подключен к второму входу второго элемента ИЛИ и к (В+1)-у входу первого элемента И, где В - число элементов гз группах элементов И и И-НЕ с тремя состояниями на выходах, выход третьего элемента И подключен30 40 к псрвому входу второго элемента ИЛИ и к входу записи оперативной памяти, выход второго элемента ИЛИ подключен к счетному входу счетчика, информационные выходы которого подключены к адреснымвходам оперативной памяти, выход переполнения счетчика подключен к входу элемента задержки, выход которого подключен к входу сброса триггера, вход разрешения выборки оперативной памяти подключен к минусовой шине источника питания, выходы шинного формирователя подключены кинформационным входам оперативной памяти, нечетный выход первой группьг выходов оперативной памяти подключен кпервому входу соответствующего элемента И группы с тремя состояниями на выходе, четный ьы ад группы выходов оперативной памлти иодклгочен к первому входу соответствующего элемег а И - НЕ группы с тремя состояниями на выход; выходы К-го элемента И группы с тремя с;.гстояниями на выходе и К-го элемента И - НЕ гр;.гпы с тремя састояггиями на выходе соединены с К-м входом первого элемента И (К=1,Р), в ход четвертого элемента И подклгочен к входу сброса первого регистра, О-й выход(0=1,С)группы выходов дешифратара подключен к второму входу О-га элемента И группы, где С - число элементов И группы, число элементов ИЛИ группы, муль.гиплексорав и блоков оперативной памяти предикатов, первые входы элементов И группы подключены к входу устройства для подключения команды вывода чгкраЭВМ, выходы элементов И группы асаф;ключены к соответствующим входам треть";.о элемента ИЛИ и к вторым входам соотвегсгвугощих элементов ИЛИ группы, первый иггчерсггые входы элементов ИЛИ группы паг лючены к выходу третьего элемента ИЛИ, акже подключенному к входам загиси блоков оперативной памяти предикатав группьг, к гдресггьгм входам мультиплексоров группы и к счетному 45 входу второго счетчика, выха;г которогоподключены к вторым группам ин ггармзционных,входов мультиплексооов группы, первые группы информационных входов которых являютсл соответствующими иггфор мационньгми входами Групыинформационных входов устройства, выходы мультиплексоров группы подклгачены к адресным входам саотв тствующих блоков операгипной памяти предикатов группы, 55 входы разрешения выборки которых подключены к выходам саотггетствуюгцих элементов ИЛИ группы, ниформационг ье входы блоков оперативггай памяти предикагав г рупггы цодклгэгг(г.г к псовому разрлду выходов гциггггага:,-:лл, "г:,лл. ггг,1 ггоп 2002300мационные выходы блоков оперативной памяти предикатов группы подключены к второй подгруппе объединенных вторых входоо элементов И группы с тремя состояниями на выходе и элементов И-НЕ группы с тремя состояниями на выходе, первая подгруппа обьединенных вторых нходоо которых является информационными входами устройства для подключения дискретных сигналов, а третья подгруппа объединенных вторых входоо подключена к информационным выходам второго регистра, второй выход оператинной памяти подключен к (В+2)-у входу первого элемента И, нторая группа информационных выходов оперативной памяти подключена к входам установки первого регистра, первая группа информационных выходов которого подключена к входам шинного формирователя, вторая группа информационных выходов первого регистра подключена к информационным входам второго регистра, выход первого элемента И подключен к входу синхронизации первого регистра первый выход оперативной памяти подключен к входу второго элемента задержки, выход которого подключен к входу синхронизации второго регистра.Недостатками прототипа являются низкое быстродействие и узкая область применения. Эти недостатки объясняются следующими обстоятельствами. Технические средства протОтипа ориентированы на последовательное вычисление всех коньюнкций булевых функций, описывающих поведение автомата, Однако в каждом из состояний последовательностного автомата имеет смысл лишь вычисление конъюнкций, помещающих исходящие дуги из соответствующей вершины, для определения выходных сигналов и последующего состояния автомата. Кроме того, прототип ориентирооан на работу лишь о составе микропроцессорной системы и его использование в простых контроллерах сопряжено со сложностью формирования сигналов записи констант, пуска и сброса, Все это снижает быстродействие прототипа и сужает область его применения,Целью изобретения является повышение быстродействия устройства и расширение области его применения.Цель достигается тем, что н устройства для ввода н микроЭВМ дискретных сигналов, содержащее дешифратор, шинный формирователь, пять элементов И, триггер, генератор импульсов, группу элементов И с тремя состояниями на выходе, группу элементов И - НЕ с тремя состояниями на выходе, три элемента ИЛИ, счетчик,оперативную память, мультиплексор, два регистра и два элемента задержки, причем первый вход дешифратора является адрес. ным входом устройства, а первый и второй 5 выходы подключены соответственно к первым входам второго и третьего, четвертого и пятого элементов И, триггер соединен с входом генератора импульсов, информационный вход оперативной памяти подключен 10 к выходу шинного формирователя, вход-выход которого является входом уставок и информационным выходом устройства, выход и второй вход второго элемента И подключенысоответственно к входу разрешения 15 шинного формирователя и выходу первогоэлемента ИЛИ, второй вход которого является входом команды записи устройства и соединен с вторыми входами третьего и четвертого элементов И, первый вход первого 20 элемента ИЛИ является входом командычтения устройства и соединен с входом направления передачи шинного формирователя и вторым входом пятого элемента И.выход генератора импульсов соединен с 25 вторым входом второго элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И и входу записи оперативной памяти, счетный вход счетчика соединен с выходом второго элемента ИЛИ, 30 вторые входы соответствующих элементовИ и И-НЕ групп объединены, выходы соответствующих элементов И и И - НЕ групп объединены и подключены к соответствующим входам первого элемента И, выход ко торого соединен с синхровходом первогорегистра, информационный вход которого является информационным входом второго регистра, синхровход которого подключен к выходу второго элемента задержки, вход 40 разрешения выборки оперативной памятиподключен к минусовой шине источника питания, выход четвертого элемента И является входом сброса первого регистра, введены доа элемента ИЛИ; регистр и сум матор, при этом выходы четвертого и пятогоэлементов И являются первыми входами третьего и четвертого элементов ИЛИ соответственно, выход третьего элемента ИЛИ подключен к входу сброса счетчика, выход 50 которого подключен к первому входу сумматора, второй гход которого является выходом второй группы второго регистра и выходом кода состояния автомата, выход сумматора соединен с адресным входом 55 оперативной памяти и является адреснымвыходом для подключения внешнего блока памяти, выход генератора импульсов через первый элемент задержки соединен с (В)- м входом первого элемента И, второй вход третьего и первый вход пятого элементовИЛИ являются входом сброса устройства, второй охаДчетвертога элемРнта ИЛИ является входом пуска устройства, третий вход третьего и второй вход пятого элементов ИЛИ соединены с выходом второго элемента задержки, охадом которого является третий вход мультиплексора, вход сброса триггера соединен с выходом пятого элемента ИЛИ, вход установки триггера подключен к выходу четвертого элемента ИЛИ и синхровходу третьего регистра, информационный вход которого является информационным входом устройства для подклОчения дискретньх сигналов, выходы третьего регистра являОтся вторыми входами саатоетствуОщих элементов И группы, выхадь нечетных разрядов первой группы выходов мультиплексора соединены с первыми входами соответствующих элементов И группы, вьходы четных разрядов ггервой группы выходов мультиплексора соединены с первыми входами соответствующих элементов И - НЕ группы, вторая группа выходов мультиплексора является входом первого регистра, первая групга выходов второго регистра соединсна с группой информационных вхадао шинного формирователя, первые информационные входы мультиплексора соединены с оыхадОл опе; ративнай памяти, э вторые информационные входы и адресный вход образуют информационные входы и вход управления мультиплексора соответственно, второй вход дешифратора является входом разрешения устройсва, входы сброса второго и третьего регистров явля,отся входами сброса устройства,Сущность изобретения заключается о повышении быстродействия и расширении области применения гутем введения дисциглины адаптивной адресации констант, Суть введенной дисциплины заключается в адресации блока памяти не только состоянием счетчика констант, но и сигналами состояний реализуемого автомата, причем адрес конкретной константы определяется как сумма кодов состояния счетчика констант и текущего состояния автомата, и в обеспечении возможности подключения онешега блока памяти и инициирования вычислений дополнительными входами.Введение четвертого элемента ИЛИ и соответствующих ему соязей позволяет инициировать вычисления при использовании устройства без внешней микроЭВМ для реализации введенной дисциплины. Введение пятого элемента ИЛИ и соответствующих ему связей позволяет подготавливать устройство к вычислению либо путем предоариельного обнуления сигналом сброса 5 10 15 20 25 30 35 40 45 50 55 как микропроцессорной системы, так и при использовании устройства без микроЭВМ для реализации введенной дисциплины, либо сигналом окончания массива подконстант. Введение третьего регистра и соответствующих ему связей позволяет фиксировать значение входного вектора перед началом вычисления во введенной дисциплине, Введение сумматора и соотоетстоующих ему связей позволяет реализовать адаптивную адресацию констант путем суммирования кода состояния автомата, который определяется как начальный адрес подконстант даннога состояния автомата, и кода номера константы в подмассиое оо введенной дисциплине, Введение новых связей для мультиплексора позволяет подключать внешний блок памяти при использовании устройства без микроЭВМ для реализации введенной дисциплины. Введение новых связей для дешифратора позволяет сократить количество выводов микросхемы предлагаемого устройства (при реализации в виде БИС) за счет использования внешних дешифраторов для реализации введенной дисциплины,На фиг,1 изображена функциональная схема устройства для овода в микроЭВМ дискретных сигналов; нэ фиг.2 - граф автомата для примера конкретного выполнения.Устройство (фиг.1) содержит дешифратор 1, шинный формирователь 2, элементы И 37, триггер 8, генератор 9 импульсов, группу элементов И 10.1,10.В с тремя состояниями на выходе, где В - разрядность входного дискретного сигнала, группу элементов И - НЕ 11.111.В с тремя состояниями на выходе, элементы ИЛИ 1216, счетчик 17, оперативнуо память 18, мультиплексор 19, регистры 2022, элементы 23, 24 задержки, сумматор 25, входы 26 адреса, входы-выходы 27 Данных, вход 28 разрешения, входы чтения 29 и записи 30, информационные входы 31 устройства, вход 32 пуска и вход 33 сброса устройства, вход 34 управления мультиглексорам 19, информационные входы 35 мультиплексора 19, адресные выходы 36 для подключения внешнего блока памяти, выход 37 кода состояния автомата, выходы 38, 39 дешифратора 1 1 л выходы 40.42 мультиплексора 19.Первый вход дешифратара 1 является адресным входом 26 устройства, а первый 38 и второй 39 выходы подключены соответственна к первым входам второго 4, третьего 5 и четвертого 6, пятого 7 элементов И, Триггер 8 соединен выходам с входом генератора 9 импульсов, Информационный вход апРративнай пэмя, .. л 1 й нн к выходу ВИННОО фОРМИ,",Л, - .,: .: ;чал ка.торого является входом 27 данных и информационным выходом устройства. Выход и второй вход второго элемента И 4 подключены соответственно к входу разрешения шинного формирователя 2 и выходу первого элемента ИЛИ 12, второй вход которого является входом 30 команды записи устройства и соединен с вторыми входами третьего 5 и четвертого 6 элементов И. Первый вход первого элемента ИЛИ 12 является входом 29 команды чтения устройства и соединен с входом направления передачи шинного формирователя 2 и вторым входом пятого элемента И 7. Выход генератора 9 импульсов соединен с вторым входом второго элемента ИЛИ 13, первый вход которого подключен к выходу третьего элемента И 5 и входу записи оперативной памяти 18, Счетный вход счетчика 17 соединен с выходом второго элемента ИЛИ 13, Вторые входы соответствующих элементов И 10 и И - НЕ 11 групп объединены. Выходы соответствующих элементов И 10 и И - НЕ 11 групп объединены и подключены к соответствующим входам первого элемента И 3, выход которого соединен с синхровходом первого регистра 20, Информационный выход последнего является информационным входом второго регистра 21, синхровходы которого подключены к выходу второго элемента 24 задержки. Вход разрешения выборки оперативной памяти 18 подключен к минусовой шине источника питания, Выход четвертого элемента И 6 является входом сброса первого регистра 20. Выходы четвертого 6 и пятого 7 элементов И являются первыми входами третьего 14 и четвертого 15 элементов ИЛИ соответственно. Выход третьего элемента ИЛИ 14 подключен к входу сброса счетчика 17, выход которого подключен к первому входу сумматора 25, второй вход которого является выходом второй группы второго регистра 21 и выходом 37 кода состояния автомата. Выход сумматора 25 соединен с адресным входом оперативной памяти 18 и является адресным выходом 36 для подключения внешнего блока памяти. Выход генератора 9 импульсов .через первый элемент 23 задержки соединен с (В+1)-м входом первого элемента И 3. Второйвход третьего 14 и первый вход пятого 16 элементов ИЛИ являются входом 33 сброса устройства. Второй вход четвертого элемента ИЛИ 15 является входом 32 пуска устройства, Третий вход третьего 14 и второй вход пятого 16 элементов ИЛИ соединены с выходом второго элемента 24 задержки, входом которого является третий выход 42 мультиплексора 19. Вход сброса триггера 8 соединен с выходом пятого элемента ИЛИ 16. Вход установки триггера 8подключен к выходу четвертого элементаИЛИ 15 и синхровходу третьего регистра 22,. информационный вход которого является5 информационным входом 31 устройства дляподключения дискретных си;чалов. Выходытретьего регистра 22 являются вторыми входами соответствующих элементов И 10группы. Выходы нечетных разрядов первой10 группы выходов 40 мультиплексора 19 соединены с первыми входами соответствующих элементов И 10 группы. Выходы четныхразрядов первой группы выходов 40 мультиплекжра 19 соединены с первыми входами15 соответствующих элементов И-НЕ 11 группы, Вторая группа выходов 41 мультиплексора 19 является входом первого регистра20. Первая группа выходов второго регистра21 соединена с группой информационных20 входов шинного формирователя 2. Первыеинформационные входы мультиплексора 19соединены с выходом оперативной памяти18, а вторые информационные входы и адресный вход образуют информационные25 входы 35 и вход 34 управления мультиплексора. Второй вход дешифратора 1 являетсявходом 28 разрешения устройства, входысброса регистров 21,22 являются входом 33устройства.30 Дешифратор 1 предназначен для дешифрации адреса, выставленного на входах26. Дешифратор формирует сигналы 38 управления элементами И 4, 5 сигналы 39 управления элементами И 6, 7 и может быть35 реализован, например, на стандартных интегральных микросхемах 155 ИДЗ, причемдля согласования с функциональной схемойв этом случае сигнал с входа 28 подключается через инвертор,40 Шинный формирователь 2 предназначен для усиления по мощности сигналов навходах-выходах 27, обеспечения двунаправленной передачи информации на них, а также для перевода своего входа-выхода в45 состояние высокого импеданса при неактивизации первого входа разрешения для отключения устройства от входов-выходов 27.При возбужденном первом входе разрешения потенциал на втором входе разрешения50 шинного Формирователя 2 определяет направление передачи (при возбужденных. обоих входах разрешения информация передается с выходов регистра 21 на входывыходы 27, т.е. идет ввод в микроЭВМ).55 Шинный формирователь 2 может быть реализован, например, на стандартных интегральных микросхемах 589 АП 16, при этомдля согласования с функциональной схемойнеобходимы инверторы к входам разрешения.13 счетчиком 17 и страбиравания элемента 45И 3 при считывании тнформации из мультиплексора 19. енера ор 9 может быть реализован, например, на стандартной интегральной микросхеме 155 ЛАЗ, резисторе, конденсаторе,Гругпа элементов И 10 с тремя состояниями на выходе предназначена для идеитификации прямого (неинверсированного) ЗНЗЧЕНИЙ ПЕРЕМЕННЫХ В КОНЪЮНКТИВНОМтерме, При этом активирован вход управления соответствующих элементов И 10. В противном случае выход элемента И находится в высокоимпедансном состоянии и невлияет на работу саответствуощих элементов И - НЕ 11, Группа элементов И с тремя Г 1 ервый элемент И 3 предназначен для формирования значения коньюнктивного терма по значению выходов каждой пары элементов И 10-И-НЕ 11 по страбу генератора 9, Когда выходы обоих элементов в паре находятся в высакаимподансном са- СТОЯНИИ, ЭТО ВОСПРИНИМаЕТСЯ СООТВЕТ- стлуОщим входом элемента И 3 как в ТТЛ-логике логической 1". Второй элемент И 4 предназначен для управления первым входом разрешения (входом выборки) шинного формирователя 2. Выход элемента И 4 возбуждается в том случае, если акти вированы выход 38 дешифратора 1 и вьход элемента ИЛИ 12,1 ротий элемент И 5 предназначен для управления входом записи оперативной памяти 18 и через элемент ИЛИ 13 счетнымвходом счетчика 17 в том случао, если актиВираван выход 38 дешифратора 1 и вход 30 управления устройства.Четвертый элемент И 6 предназначен дпя управления входом сброса счет ика 17 па окончании вьчислоний втам случае, ослиактивираван выход 39 дешифратараи вход 30 управления устоойства,Пятьй элемент И 7 предназначен для управх(ения Входам установки триггера 8 в там слуЯо., если ахиврован ВыхОд 39 дешифратораи вход 29 устройства.Триггер 8 предназначен для управления генератором 9 и устанавливается сигналами с выхода элемента И 7 или входа 32 пуска, а обнуляется игналам с входа 33 сброса или с третьего выхода 42 мультиплексора 19 после задержки на элементе 24 и может быть реализован, например, а стаДартных интегральных микросхемах 155 ТМ 2, причем для согласования с функциональной схемой входы сброса и установки подключаются через инвертары,Генора гор 9 предназначен Для управления по счетному входу через элемент ИЛИ 10 152030 35 40 состояниями на выходе может быть реализована, например, на стандартных интегральных микросхемах 589 АП 16, причем для согласования с функциональной схемой оба входа разрешения объединяются и подключаются через инвертор к соответствующему выходу 40 мультиплексора 19.Группа элементов И-НЕ 11 с тремя состояниями на выходе предназначена дпя идентификации инверсного значения переменной в конъюнктивном терме, При этом активизирован вход управления соответствующих элементов И-НЕ 11. В противном случае выход элемента И - НЕ находится в высокоимпедансном состоянии и не влияет на работу соответствуОщих элементов И 10. Группа элементов И - НЕ с тремя состояниями на выходе может быть реализована, например, на стандартных интегральных микросхемах 589 АП 16 с инверсией входных сигналов,Первый элемент ИЛИ 12 предназначен для управления элементом И 4 в том случае, если активирован один из входов 29 и 30 управления устройства. Второй элемент ИЛИ предназначен для управления счетным Входом счетчика 17 сигналами либо с генератора 9 чтение из памяти 18), либо с выхода элемента И 5 (запись в память 18). Третий элемент ИЛИ 14 предназначен дляуправления сбросом счетчика 17 сигналами либо с выхода элемента И 6, либо с входа 33сброса, либо с выхода 42 мультиплексора 19 после задержки на элементе 24. Четвертый элемент ИЛИ 15 предназначен для управления входом установки триггера 8 либо с выхода элемента И 7, либо с входа 32 управления. Пятый элемент ИЛИ 16 предназначен для управления сбросом триггера 8 сигналами либо с входа 33 сброса, либо свыхода 42 мультиплексора 19 после задержки на элементе 2 Ч,Счетчик 17 предназначен для адресации констант при записи или считывании информации и может быть реализован, например, на стандартных интегральных микросхемах 155 ИЕ 7, Счетный вход счетчика 17 управляется выходам элемента ИЛИ 13. Емкость счетчика достаточна для адресации массива констант, соответствующих состоянию автомата с максимальным количествам конъюнкций, определяющих возможные переходы автомата,Оперативная память 18 предназначенадля записи, хранения и выдачи кодов настройки в мультиплексор 19 и элементы И 10, И-НЕ 11, Вариант программирования оперативной памяти 18 представлен в примере конкретного выполнения вы ислений,Оперативная память 18 программируетсямикроЭВМ и может быть реализована, например, на стандэртных интегральных микросхемах 541 РУ 2.Мультиплексор 19 предназначен для подключения к выходу данных оперативной памяти 18 либо оыходоо данных внешней памяти с входов 35 о том случае, еслл на вход 34 подана логическая "1" (внешняя память о этом случае адресуется выходами 36). Нечетные выходы 40 группы выходов подключены к входам управления соответствующих элементов И 10 с тремя состояниями нл выходе для подключения их к соответствующему разряду выхода регистра 22, поступающего на информационные входы элементов И 10 группы, если переменная, сопоставляемая с ним, входит в коньюнктивный терм булевой функции без инверсии и отключения о противном случае. Четные вцходы 40 группы выходов подключены к входам управления соответствующих элементов И-НЕ 11 группы с тремя состояниями на выходе для подключения их к соответствующему разряду выхода регистра 22, если переменная, сопоставляемая с ним, входит в коньонкгионый терм булевой функции с иноерсией, и отключения их в протиином случае. Информация на группе выходов 41 имеет единицы о разрядах, соответствующих номерам булевых функций, включающих вычисляемый (соответствующий) коньюнктивный терм, Информация на выходе 42 раона единице в том случае, если соответствующий коньюнктивный терм (код коньюнктионого терма) последний, и нул,о в противном случае. Мультиплексор 19 может быть реализован, например, на стандартных интегральных микросхемах 155 Ы 1, причем для согласования с функциональной схемой входы синхронизации. микросхем подключаются к минусовой шине источника питания, к которой также подключаются и адресные входы с весами 2, 4, 8, а выходы микросхем иноертируются,Первый регистр 20 предназначен длч записи с накоплением в него, хранения и выдачи информации об обобщенном выходном слове с выходов 41 мультиплексора 19, .Обобщенное выходное слово состоит из выходного слова и информации о последующем внутреннем состоянии, Информация о регистр 20 записывается стробом, формируемым на выходе элемента И 3. Первый регистр 20 накапливает "единицы" в трех разрядах, которым соответствуют булавы функции, равные единицам, при оыцислении соотоетстоуюших коньюнктивнык тер" моо и определении, что онив свою очередь, равны единице, и может быть реализован, например. на стандартных интегральныхмикросхемах 533 ТР 1 с элементами И-НЕ по всем входам установки, стробируемыми по вторым входам.Второй регистр 21 предназначен для записи, хранения и выдачи информации о последующем внутреннем состоянии и выходных сигналов с выхода первого регистра 20 по стробу на выходе элемента 24 задержки. Второй регистр представляет собой память отработки алгоритма устройства и может быть реализован, например, на стандартных интегральных микросхемах 155 ИР 13.Третий регистр 22 предназначен для записи,хранения и выдачи входного дискретного сигнала, поступающего на вход 31 устройства и может быть реализован, например, на интегральных микросхемах 155 ИР 13. Информация входного сигнала с входов 31 записывается в регистр 22 по сиг 20 налу "ноль" с выхода элемента ИЛИ 15.Первый элемент 23 задержки предназначен для задержки стробирующего импульса на вход элемента И 3 для ожидания завершения переходных процессов при эаР 5 писи информации в регистр 22 (по сигналу пуска вычислений). Второй элемент 24 задержки предназначен ря задержки сигнала с выхода 42 мультиплексора 19 с целью ожидания завершения переходных процес 30 сов в элементах И 10 и И - НЕ 11 и окончания записи; если таковая будет, в регистр 20.Сумматор 25 предназначен для формирования адреса памяти 18 путем суммирования текущего состояния автомата с 35 выхода регистра 21 и сигналов с выхода счетчика 17. Сумматор 25 может быть реализован, например, на стандартных интеграл ьн ых микросхемах 531 ИМ 4.Вход 26 адреса предназначен для под 45 50 55 устройства предназначен для приема импульса пуска при использовании устройства без внешней ЭВМ в качестве отдельного локального контроллера, Вход 33 сброса устройства предназначен для приведения в нулевое (исходное) состояние триггера 8,ключения шины адреса (или ее части) внешней микроЭВМ, Входы-выходы данных 27 предназначены для подключения шины данных внешней микроЭВМ. Вход 28 разрешения предназначен для управления дешифратором 1 адресов устройств ввода- ввода внешней микроЭВМ. Первый вход 29 управления "чтение" предназначен для подключения команды ввода внешней микро- ЭВМ. Второй вход 30 управления "запись" предназначен для подключения команды вывода внешней микроЭВМ. Информационные входы 31 предназначены для подключениявходных сигналов. Вход 32 пуска5 10 15 20 ф+1) =- Гх(0, уЯ; чсчетчика 17, регистров 21,22 перед началом работы. Вход 34 предназкачен для управления мультиплексором 19 в том случае, если необходимо использование внешней памяти констант ПЗУ ППЗУ), в этом случае на вход 34 подается логическая "1", Информационный вход 35 мультиплексора 19 предназначен для подключения выхода данных внешнего блока памяти. Адресные выходы 36 предназначены для подключения к входам адреса внешнего блока памяти, Выход 37 кода состояния предназначен для осуществления контроля работы устройства, например, внешней микроЭВМ.Устройство для ввода в микроЭВМ дискретных сигналов работает следующим образом,Режим настройки.Перед началом работы на вход 33 устройства подается сигнал, переводящий в исходное (нулевое) состояние триггер 8 и счетчик 17 через элементы ИЛИ 16 и 14 соответственно, а также регистры 21, 22. Регистр 20 также переводится в исходное нулевое) состояние. Вйешняя микроЭВМ,подключенная к устройству по входам 26 адреса, входам-выходам 27 и входам 29, 30 управления, обращается к нему как к порту вывода с фиксированным адресом. Активируется вход 30 управления "запись", а на выходах 26 выставляется адрес, что приводит к возбуждению выход 38 дешифратора 1 и элемента ИЛИ 12. Поэтому активируется выход элемента И 4, подключающий шинный формирователь 2 по первому входу управления по входам-выходам 27, Так как второй вход управления шинного формирователя 2 неактивирован (отсутствует сигнал "чтение" на выходе 29), го он подключается в режиме передачи информации с входов выходов 27 на входы данных оперативной памяти 18, Оперативная память имеет постоянно активированный вход управления выборкой он инверсный и подключен к минусовой шине источника питания), поэтому выход элемента И 5, активировэнный выходом 38 дешифратора 1 и входом 30 управления, переводит ее в режим записи по входу записи. Поскольку счетчик 17 и регистр 21 в исходном положении обнулены по цепям сброса, то на входах адреса оперативной памяти 18 выставлен адрес нулевой ячейки. Таким образом, в оперативную память 18 записывается первое слово информации, имеющее три поля. Первое поле соответствует группе выходов 40 мультиплексора 19 - эта информация кодирует коньюнктивные термы аналогично прототипу и управляет группами элементов И 10, И-НЕ 11, Второе поле соответствует группе выходов 41 и представляет собой информацию обобщенного выходного сигнала э+в, где гп - количество выходных сигналов; з =1 пт 1 о 92 М, где М - количество состояний автомата, причем единицы в соответствующих позициях означают, что при равенстве единиц данного коньюнктивного терма булевы функции, комера которых равны этим позициям, равны единице. Третье поле (один разряд, выход 42) состоит из одного бита, который равен единице в том случае, если соответствующий конъюнктивный терм и обобщенный выходной сигкал последние. По заднему фронту сигнала на выходе элемента И .5 через элемент ИЛИ 13 изменяет свое состояние счетчик 17, и его выходные сигналы адресуют очередную (первую) ячейку опера- тинной памяти 18, При очередных обращениях к устройству и активировании входа 30 в оперативную память 18 аналогично записывается второе слово информации, Далее устройство работает аналогично, в оперативную память 18 записывается массив слов информации, описанных выше, причем последнее слово информации в подмассивах, соответствующих состояниям автомата, помечаетсяединицей в разряде, соответствующем выходу 42, а в незадействованные ячейки записываются нули в соответствующем разряде.Таким образом, настройка устройства - запись констант в оперативную память 18 аналогична прототипу,Режим реализации дисциплины адаптивной адресации констант,В этом режим реализуется заданное автоматное отображение автомат Мили) Ф) = Чх у(Вгде х 1) - вектор входных сигналов (входы 31);у(т) - вектор текущего состояния автомата выходы 37);ф+1) - вектор последующего состояния автомата часть выходов 41);ф) - вектор выходных сигналов часть выходов 41).Инициирование вычислений может быть произведено программно внешней микроЭВМ(при этом аналогично прототипу возбуждаются входы 28, 29, вход 26 приводит к возбуждению выход 39 дешифратора 1, возбуждается выход элемента И 7, через элемент ИЛИ 15 устанавливается триггер 8) либо внешним стробом по входу 32, Генератор 9 начинает генерировать последовательность импульсов, по переднему фронту10 20 30 которых с некоторой задержкой, определлемой элементом 23, страбируется элемент И 3, вычисляющий значение конъюнкции ат входного сигнала х, записанного передним фронтом импульса с выхода элемента ИЛИ 15 в регистр 22 с входов 31. Если вычисляемая конъюнкция покрывает входной сигнал, то выходы всех элементов И 10.1 - 10,В, И-НЕ 11.1 - 11,В, настроенные константой с выхода 40 мультиплексора 19, (аналагично прототипу) находятсл в состоянии логической "1" и на выходе элемента И 3 возникает импульс(павторяющий строб генератора 9), записывающий в регистр 20 обобщенный выходной сигнал у(с+1) г(1) с выходов 41 мультиплексора 19 (второе поле выходов памяти 18 - первое поле - константа) либо значения булевых функций,. описывающих этот обобщенный выходной сигнал (аналагично прототипу). При этом, так как регистр 20 имеет входы, происходит "накопление" единичных значений указанных функций,По заднему фронту импульса генератора 9 изменяется состояние счетчика 17, адресующего следующую константу. Адрес константы формируется в сумматоре 25 выходных сигналов счетчика 17 и регистра 21, Выходные сигналы сумматора поступают на входы адреса оперативной памяти 18 и на выходы 36 устройства, например, для контроля или для адресации внешнего блока памяти (при необходимости). С задерккой, необходимой для завершения переходных процессов в сумматоре 25 и памяти 18, через элемент 23 задержки стробируетсл элемент И 3, и процесс прадолжаетсл до тех пар, пока на выходе 42 не появится признак окончания констант, соответствующих данному состоянию (в описанном случае .начальному); через элемент ИЛИ 16 обнуляется триггер 8, через элемент ИЛИ 14 - счетчик 17. Тогда с задержкой, определяемой элементам 24, задержки и необходимой для завершения вычислений последней конъюнкции, в регистр 21 переписываетсл значение вычисленных функций у(1+1) г(1) из регистра 20. Выходные сигналы г(1) с первой группы выходов регистра 21 поступают на входы шинного фармиравателл 2 и вводятся в микроЭВМ при исполнении ею команды ввода: возбуждаются входы 29, 28, вход Е 2 шинного формирователя 2, выход элемента ИЛИ 12, выход 38, выход элемента И 4, вход Е 1 шинного фармирователл 2 и инфармация с входов шинного формирователя поступает на входы-выходы 27 и далее о микро Э В М. Си гнал ы текущего состояния поступают на выходы 37(например, для контроля) и на вторую группу входов сумматора, подготавливая вычисления в очередном состоянии по очередной команде микроЭВМ,Для использования внешнего блока па. мяти на вход 34 подается логическая "1", квходам адреса внешнего блока подключаются выходы 36 устройства, а выходы данных внешнего блока памяти подключены квходам 35 и через мультиплексор 19 на еговыходы 40 (константы), 41 (выходные слова),42 (бит окончания констант состояния), Этопозволяет использовать устройство в качестве отдельного контроллера (микропрограммного автомата) для различных целейуправления при записи констант во внеш 5 нее постоянное запоминающее устройство.Адаптивная адресация повышает быстродействие, так как исключает необходимость вычисления всех конъюнкций,вычисляются только конъюнкции, соответствующие данному состоянию,С выхода элемента И 6 происходит программное обнуление регистра 20 и счетчика17 и подготовка устройства к последующимвычислениям.5 Рассмотрим пример конкретного выполнения.Допустим, что необходимо реализоватьграф автомата, изображенный на фиг.2,Имеется четыре состояния У 1, У 2, Уз, У 4,шесть входных сигналов Х 5-Х 1. В таком случае обобщенная табл.1 переходов-выходовимеет следующий вид.При обычном кодировании У 1:=00;У 2:=01; Уз=10; У 4;-11 и автомат описывается следующей системой булевых функцйй:1 2 . 3 401= У 2 У х 2 х 1 Ч У 2 У 1 Ч У 2 У 1 У У 2 Ух 5 Х 4 Ч,5ч У 2 У 1 х 5 х 46 702 = У 2 У 1 х 2 х ЧУ 2 У 1 х 5 х 4;8 9г 1 = У 2 У 1 х 2 х 1 Ч У 2 У 1 Ю10г 2 У 2 У 1 х 2 х 1111гз = У 2 у ХЭВИ12г 4 = Уг УХЗ13г 5 У 2 У 1 Х 414гб угу 1 Х 5-Х 4,15г 7 - угу. Итак, имеются 15 конъюнкций, В прототипе необходимо в каждом цикле вычислений определять значения всех 15 конъюнкций. Пронумеруем дуги граФа и

СмотретьЗаявка

5019327, 26.12.1991

Тюрин Сергей Феофентович, Назин Владимир Иванович, Суханов Александр Владимирович, Гусейнов Акир Пегриз-оглы, Шор Олег Анатольевич, Жолкевский Андрей Геннадьевич

МПК / Метки

МПК: G06F 13/00

Метки: ввода, дискретных, микроэвм, сигналов

Опубликовано: 30.10.1993

Код ссылки

<a href="https://patents.su/13-2002300-ustrojjstvo-dlya-vvoda-v-mikroehvm-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода в микроэвм дискретных сигналов</a>

Предыдущий патент: Устройство для отладки программ

Следующий патент: Устройство для определения показателей надежности объектов

Случайный патент: Устройство для бесконтактного перемешивания