Устройство для ввода в микроэвм дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1594554

Автор: Тюрин

Текст

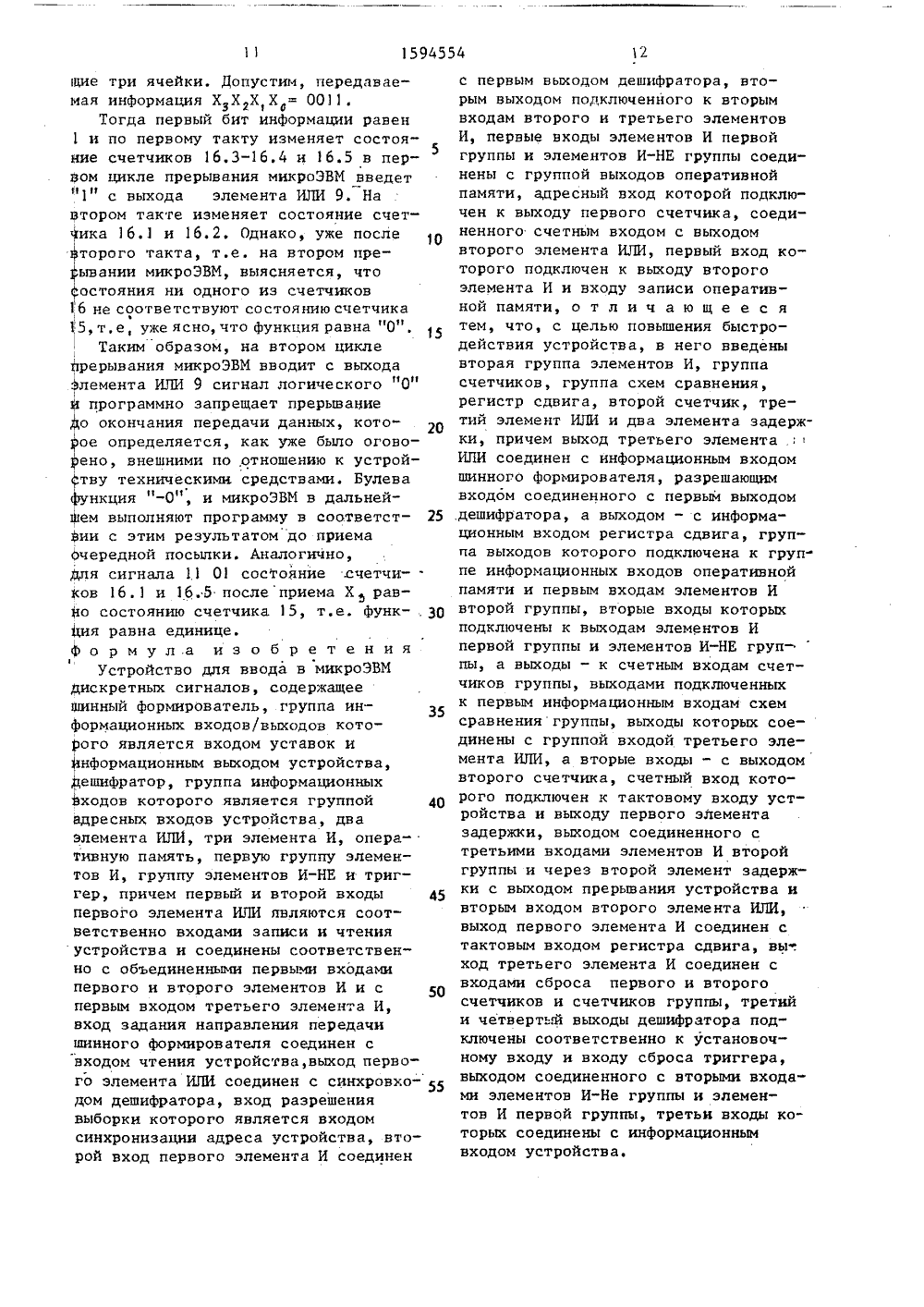

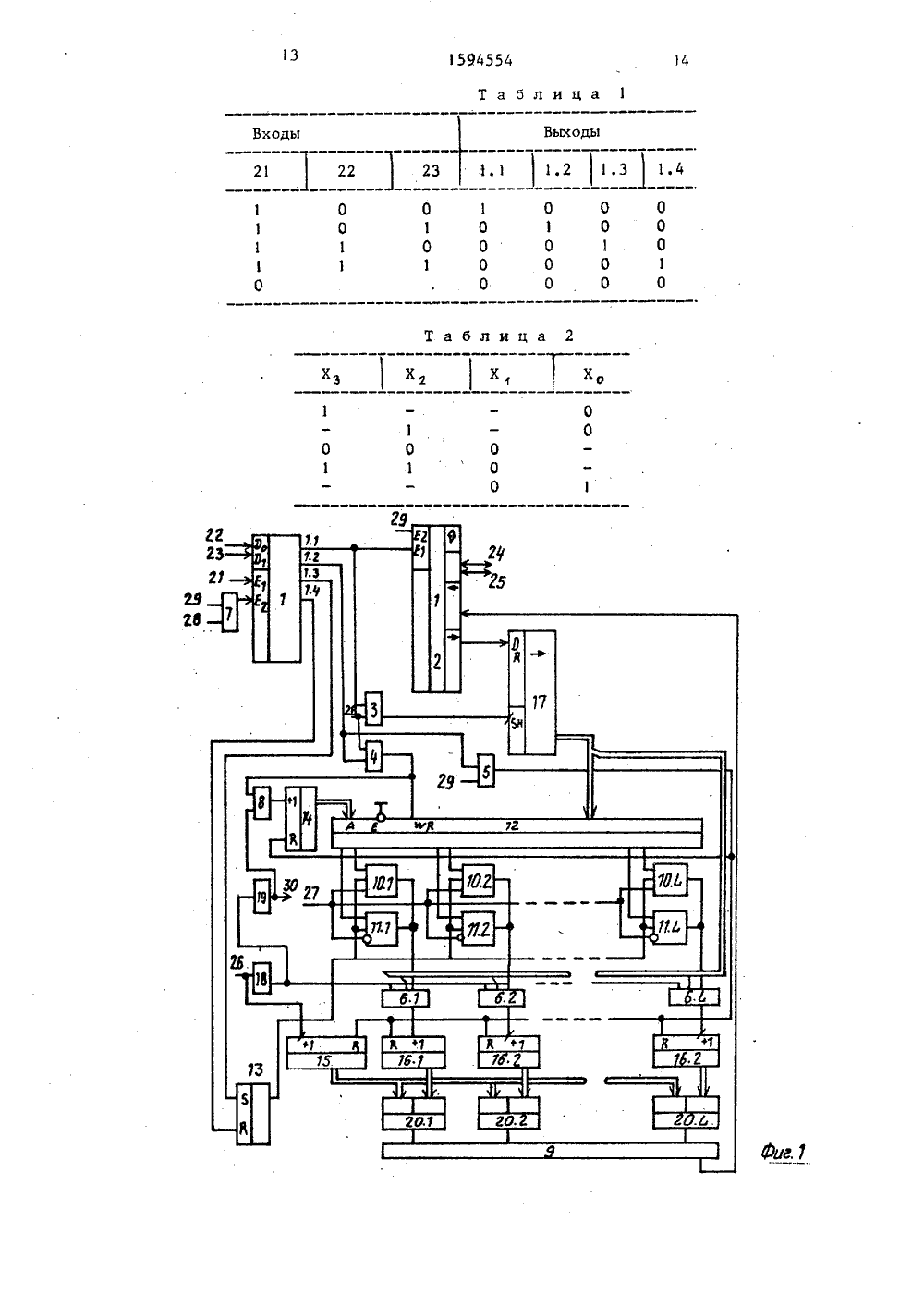

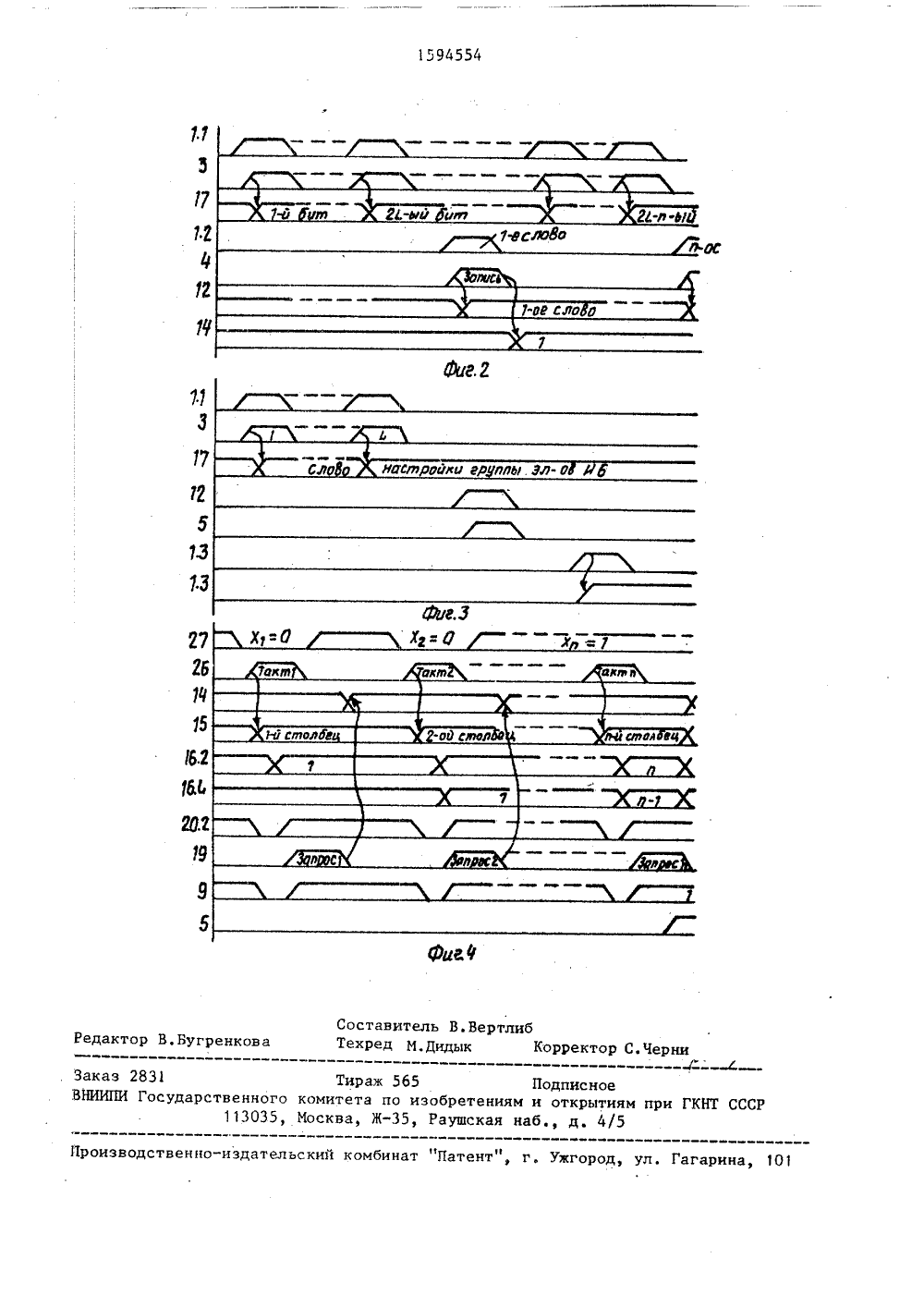

ты устройства в режиме настройкигруппы элементов И; на фиг 4 - временная диаграмма работы устройствав режиме реализации дисциплиныстолбцового маскирования дискретныхсигналов битового интерфейса,Устройство содержит дешифратор 1,шинный формирователь 2, элементыИ 3-5, элементы И 6 группы, элементы ИЛИ 7-9, элементы И 10.группы,элементы И-НЕ 11, оперативную память 12, триггер 3, счетчики 14 и15, счетчики 16 группы, регистр17, элементы 18 и 19 задержки, схемы 20 сравнения, управляющий вход21 выборки дешифратора, адресныевходы 22 и 23, входы/выходы 24 и 25данных, тактовый вход 26, информационный вход 27, синхрониэирующиевходы 28 и 29 вывода и ввода, выход30 прерывания.Дешифратор 1 предназначен длядешифрации адреса, причем логика егоработы описывается таблицей истинности (табл.1).Шинный формирователь 2 предназначен для усиления по мощности сигналовна входах/выходах 24 и 25 устройства при активизации его первого входа 30разрешения (входа выборки), а такжедля перевода своих входов/выходов ввысокоимпедансное состояние в противном случае.Режим работы шинного формирователя2 определяется уровнем сигнала наего втором входе разрешения, Если:.;цэтот вход активирован (и соответственно активирован первый вход), тошинный формирователь 2 подключенв режиме Чтение - режиме ввода инИ И 40формации со своего входа на входы/выходы 24, Если же второй вход разрешения неактивирован, то шинный формирователь 2 подключен в режиме "Запись - режиме вывода информации с1 т45входов/выходов, например, входа/выхода 25, Таким образам второй входразрешения является входом направления передачи.Элемент И 3 предназначен для фор 50мирования управляющего сигнала сдвига дпя регистра 17 в том случае,если активируется первый выход дешифратора .1 при активировании входа 28.55Элемент И 4 предназначен для формирования сигнала записи в оперативную память 12 и инкремента счетчика14 в том случае, если активируется второй выход дешифратора 1.при активировании входа 28.Элемент И 5 предназначен для формирования сигнала сброса счетчиков 14-16.Группа элементов И 6 предназначена для управления счетными входами счетчиков 16, если имеется тактовый сигнал с выхода элемента 18 задержки, с соответствующих разрядов части информационных выходов регистра 17 поступают логические единицы и с выходов соответствующих пар элементов И 10 и И-НЕ 11.Элемент ИЛИ 8 предназначен дпя управления счетным входом счетчика 14 либо тактовыми импульсами .с выхода элемента 19 задержки, либо сигналами с выхода элемента И 4.Элемент ИЛИ 9 предназначен для формирования значения вычисляемой булевой функции и передачи его на вход шинного формирователя 2. Если по окон- . чании вычислений (по последнему тактовому импульсу на входе 26) на выходе хотя бы одной из схем 20 сравнения установлена логическая единица, то значение булевой функции равно единице. Если же на каком-то такте на выходе всех схем 20 сравнения устанавливаются логические нули, то на выходе элемента ИЛИ 9 также устанавливается "0" - значение функции равно "0" и дальнейшие вычисления не нужны.Элементы И 10 имеют три состояния на выходе без инверсии и предназначены для идентификации прямых значений переменных в каждом столбце интервальной таблицы истинности булевой функции, где количество столбцов соответствует разрядности входного сигнала, а количество строк - количеству конъюнкций, При этом каждый выход памяти 12 активизирует выход одного из элементов 10, В противном случае выходы элементов И О находятся в высокоимпедансном состоянии и не влияют на работу элементов 11.Элементы И-НЕ 1 имеют состояния на выходе и предназначены для идентификации инверсных значений переменных в каждом столбце интервальной таблицы истинности. При этом выходы памяти 12 активизируют выходы элементов 11 В противном случае, выходы элементов И 1 находятся в высокоимпедансном состоянии и не влия 5 159ют на рабту соответствующих элементов И 10,Оперативная память 12 предназначена для записи, хранения и выдачикодов настройки элементов И 10 иИ-НЕ 11 .Триггер 13 предназначен для управления элементами И 10 и И-НЕ 11,т,е, для блокирования их выходов воизбежание конфликтных ситуаций на ихвыходах после включения питания, когда информация в оперативной памяти12 не определена. При включении пйтания триггер 13 обнуляется по цепям,не указанным на фиг.1, при этомвыходы всех элементов И 10 и И-НЕ 1находятся в высокоимпедансном состоянии. Триггер 3 устанавливается приактивировании выхода 1.3 дешифратора1, а также может обнуляться при активировании выхода 14 дешифратора 1.Счетчик 14 предназначен для адресации оперативной памяти 12 при записи либо при считывании информациисигналами с выхода элемента ИЛИ 8.Счетчик 15 предназначен дляуправления схемами 20 сравнения,причем изменение состояния счетчика15 происходит по переднему фронтутактового сигнала на входе 26,т.е, счетчик 15 является счетчикомстолбцов интервальной таблицы истинности исследуемой булевой функции.Счетчик 16 предназначены дляподсчета совпадений входного битаинформации с элементами столбцовО- -(" - " - тильда, безразличное состояние входного сигнала)1 41В случае таких совпадений повсем столбцам количество единиц всоответствующем счетчике 16 записано столько же, сколько в счетчике15. Изменение состояния счетчиков16 происходит по сигналам с выходовсоответствующих элементов И 6.Регистр 17 предназначен для приема при сдвиге вправо информации настройки устройства, хранения и выдачи ее на входы данных оперативнойпамяти 12, выдачи старших разрядовна входы элементов И 6.Элемент 18 задержки предназначендля задержки тактового сигнала свхода 26 для Формирования строба элементов И 6.после завершения переходных процессов в элементах И 10 и 4554 6И-НЕ 11, обу;.ловленных обработкойвходного бита с входа 27.Элемент 1 9 задержки предназначен 5для формирования запроса прерываниямикроЭВМ на выходе 30, а также дляуправления элементом ИЛИ 8 послетого, как закончатся переходные процессы по обработке очередного битаинФормации и установится сигнал навыходе элемента ИЛИ 9.Схемы 20 сравнения предназначеныдля сравнения информации на выходах15соответствующих счетчиков 16 и выходе счетчика 15, На выходах схем 20сравнения возникают сигналы логической единицы в случае сравнения этойинформации,20 Если в течение всех и тактов навыходе соответствующей схемы 20 сравнения формируется сигнал логическойединицы, исключая периоды изменениясостояния одноименного счетчика 1625 после того, как вначале изменяетсясостояние счетчика 15, то значениебулевой функции по данной конъюнкцииравноУправляющий вход выборки дешифратора 2 предназначен дляподключениявыхода строба адреса внешней мик.роЭВМ.Входы 22 и 23 адреса предназначены для подключения двух разрядов35. шины адреса внешней микроЭВМ.Входы/выходы 24 и 25 данных предназначены для подключения двух разрядов шины данных внешней микроЭВМ,Тактовый вход 26 предназначен40 для подключения тактового сигнала,сопровождающего передаваемый по входу 27 бит информации.Информационный вход 27 предназначен для подключения информационного45 сигнала - бита информации, передаваемого последовательным кодом.Вход.28 "Запись" предназначен дляподключения выхода сигнала выводавнешней микроЭВМ.Вход 29 "Чтение" предназначендля подключения выхода сигнала вводавнешней микроЭВМ.Устройство работает следующимобразом.55После подачи питания триггер 13и счетчик 14 устанавливаются в нулевое состояние. Нулевым сигналом навыходе триггера 13 выходы всех эле 1594554ментов И О и элементов И-НЕ 11 переведены в высокоимпедансное состоя- . ние во избежание конфликтов на выходах одноименных пар, так как информация на выходах оперативной памяти 12 еще не определена.МикроЭВМ обращается к дешифратору 21 как к порту вывода с фиксированным адресом, Активируются входы 28 (" Запись" ) и 21, вследствие чего активируется выход элемента ИЛИ и первый выход дешифратора 1, включая шинный формирователь 2, в режим записи, Бит данных, например, с5 входа/выхода 25 поступает на информационный вход регистра 17 т Передним фронтом импульса на выходе элемента И 3 информация записывается в регистр 17 (Фиг1 и 2) в младший разряд, В дальнейшем при очередных обращениях микроЭВМ в режиме записи в регистр 17 записывается 2 Ь бит инфор- мации (Ь - максимальная длина обрабатываемых интервальных таблиц бу левых Функций) со сдвигом вправо. Проведя 21. циклов записи в регистр 17, микроЭВМ обращается к устройству в режиме "Запись", причем сочетание адресных сигналов на входах 22 и 23 таково, что активируется второй выход дешифратора 1, поэтому активируется выход элемента И 4, в оперативную память 12 записывается первое слово информации из регистра 17. Задним фронтом импульса записи на выходе элемента И 4 через элемент ИЛИ 8 увеличивается содержимое счетчика 14, который адресует очередную, первую (после нулевой) ячейку оперативной 40 памяти 2. В дальнейшем аналогично вышеописанному в оперативную память 12 записывается и слов (где и разрядность булевой функции информации после записи в регистр 17 соответствующих 2 Ь бит информации), В.заключение после записи в и ячеек оперативной памяти 12 информационных слов в регистр 1 (Фиг. и 3) записывается еще одно слово, разрядностью 50 1 дпя управления элементами И 6, на часть которых подаются нули в том случае, если длина обрабатываемой таблицы истинности булевой функции меньше максимальной: в противном случае на все элементы И 6 подаются единицы.Затем микроЭВМ обращается к устройству в режиме ввода из него(" Чтение" ). При этом активируются входы 21 и 29, а сочетание адресных сигналов на входах 22 и 23 такового, что активируется второй выход дешифратора 1, Поэтому активируется выход элемента И 5, в результате чего обнуляются счетчики 14-16. Теперь счетчик 14 адресует нулевую ячейку оперативной памяти 2, в которой записана информация, кодирующая первый столбец таблицы истинности реализуе-. мой булевой функции. Далее микроЭВМ обращается к устройству в режиме И 11Запись , при этом активируется третий выход дешифратораи устанавливается триггер 13, снимающий блокировку с элементов И 10, И-НЕ,11. Для актнвирования третьего выхода дешифратора 1 микроЭВМ может также обращаться к устройству в режиме11Чтение , в любом случае имеет значение лишь соответствующие сигналы на входах 22 и 23, причем при возбужде-. нии выходов дешифратора 1 шинный формирователь 2 отключен от входов/выходов 24 и 25.Таким образом, устройство готово к работе. В оперативную память 12 записана информация, кодирующая и столбцов реализуемой интервальной таблицы истинности. Смысл этой информации следующий: если в столбце таблицы истинности в К-й позиции имеется "0", то М-я пара элементов И 10, И-НЕ 11 коммутирует на выход инверсное значение сигнала на входе 27, если имеется "1", то сигнал на входе 27 коммутируется на выход в прямом значении. Если в данной позиции имеется("тильда"), то выходы обоих элементов И 10,. И-НЕ 11 находятся в высокоимпедансном состоянии, что воспринимается соответствующим элементом И 6 как в ТТЛ-логике - логической "1". Счетчики 14 и 15, группа счетчиков 16 обнулены. Триггер 13 установлен.Режим реализации дисциплино"столбцового маскирования.В этом режиме на информационный вход 27 последовательно поступают биты информации, сопровождаемые тактовыми сигналами по входу 26 (фиг.1, 4). При этом по переднему фронту тактового сигнала изменяется состояние счетчика 15, подсчитывающего такты, или что то же самое, количество анализируемых столбцов интервальной20 таблицы истинности булевой функции.На выходах пар элементов И 10, И-НЕ 11устанавливаются единицы, если соответствующая позиция столбца габлицыистинности соответствует входному5биту; при несоответствии устанавливается ноль. Эта информация поступаетна соответствующие входы элементовИ 6, причем они воспринимают выходыпар неиспользуемых элементов И,И-НЕ 10, 11, а также выходы пар элементов в позициях, соответствующих("тильда") как в ТТЛ-логике -логической единицей. После этоготактовый импульс с выхода элемента18 задержки стробирует элементы И 6,на выходах которых появляются сигналы логической единицы, если совпа дение в соответствующей позициистолбца произошло, либо в этойпозиции записаны "-" ("тильда"). Еслисовпадения не произошло, или еслиданные разряди не используются,то на выходах соответствующих элементов И 6 устанавливаются логическиенули. Поэтому в соответствующие активированным элементам И 6 счетчики16 записьваются единицы, .Выходные сигналы счетчиков 16 сравниваются с выходными сигналами счетчика 15. Выхо. ды схем 20 сравнения активируются втом случае, если в соответствующемразряде столбца таблицы истинностипроизошло совпадение с входной информацией, либо в соответствующем,разряде стобца имеется "-" ("тнлвда")Таким образом, в случае несовпадения хотя бы в:одном столбце, выходсоответствующей схемы 20 сравнения 40не возбудится, и наоборот, он возбудится только при совпадениях и/или"-" во всех и столбцах.Очевидно, что если на каком-тотакте не активирован выход ни одной 45из схем сравнения, то в данном столбце нет совпадений и дальнейшеее вычисление функции теряет смысл - одно"значно она будет равна "0".Сигнал на выходе элемента 19 задержки формируется после завершенияпереходньж процессов по обработкепервого столбца интервальной таблицы истинности первым битом информации и вызывает прерывание микроЭВМпо входу ЭО. Причем длительностьсигнала прерывания (тактового импульса и интервалов между ними) такова,что микроЭВМ успевает перейти на под программу прерывания и ввестисигнал с выхода элемента ИЛИ 9, Подсчет количества прерываний производится программно, Задним фронтомимпульса на выходе элемента 19 задержки через элемент ИЛИ 8 изменяется состояние счетчика 14,МикроЭВМ обращается к устройствукак к порту ввода с фиксированнымадресом так, что активируется выход1.1 дешифратора 1, а шинный формирователь 2, второй вход разрешения которого активируется входом 29, подключается в режиме чтения сигналовна выходе элемента ИЛИ 9.Следовательно, вычисляемая булевафункция равна "1" в том случае, еслив течение и тактов считывания информации из устройства по сигналам прерывания микроЭВМ зафиксирует и единицы на выходе элемента ИЛИ 9. Приобнаружении первого нуля на выходеэлемента ИЛИ 9 дальнейшее сканирование прекращается, прерывания запрещаются программными методами и функция считается равной нулю. МикроЭВМможет обнулять триггер 13 путемобращения к устройству, как было описано вьппе. Например, для контроляфункционирования активируется четвертый выход дешифратора 1. Для обеспечения очередных вычислений аналогично вьппеописанному обнуляются счетчики 14-16 снимается блокировка, т.е,устанавливается триггер 13.В дальнейшем устройство работаетаналогично, причем иницированне микроЭВМ на начало связи производитсявнешними по отношению устройствасредствами, например некоторым устройством выделения маркера и концапередачи. Для обработки дискретнойинформации в соответствие с другойинтервальной таблицей истинности производится перенастройка устройствааналогично вышеописанному.Рассмотрим пример конкретноговычисления булевой функции от последовательно передаваемой информацние.Пусть задана булева функции,интервальная таблица истинностикоторой представлена в табл.2. Для кодирования первого столбца (Х ) в оперативную память 12 записывается слово 10 10 ОО 00 01. Аналогично записьвается информация в следую-.40 цие три ячейки. Допустим, передаваемая информация ХХХ,Х 0011.Тогда первый бит информации равен1 и по первому такту изменяет состояние счетчиков 16.3-16.4 и 16.5 в пер 5вом цикле прерывания микроЭВМ введет"1" с выхода элемента ИЛИ 9. Навтором такте изменяет состояние счетчика 16.1 и 16.2, Однако, уже послевторого такта, т.е. на втором преывании микроЭВМ, выясняется, чтоостояния ни одного из счетчиков16 не соответствуют состоянию счетчика1,5, т, е, уже ясно, что функция Равна "0".Таким образом, на втором циклепрерывания микроЭВМ вводит с выходаЭлемента ИЛИ 9 сигнал логического "0"й программно запрещает прерываниедо окончания передачи данных, которое определяется, как уже было оговорено, внешними по,отношению к устройству техническими средствами. Булевафункция "-0", и микроЭВМ в дальнейшем выполняют программу в соответствии с этим результатом до приемаОчередной посылки. Аналогично,дпя сигнала 11 01 состояние счетчи- .ков 16.1 и 16.5 послеприема Х э равно состоянию счетчика 15, т.е. функ- З 0Йия равна единице.Формула изобретенияУстройство для ввода в микроЭВМдискретных сигналов, содержащеешинный формирователь группа ин З 5формационных входов/выходов котоРого является входом уставок иинформационным выходом устройства,дешифратор, группа информационныхвходов которого является группойадресных входов устройства, дваэлемента ИЛИ, трн элемента И, опера. -тивную память, первую группу элемен. -тов И, группу элементов И-НЕ и триггер, причем первый и второй входы 45первого элемента ИЛИ являются соответственно входами записи и чтенияустройства и соединены соответственно с объединенными первыми входамипервого и второго элементов И и с 50первым входом третьего элемента И,вход задания направления передачишинного формирователя соединен свходом чтения устройства, выход первого элемента ИЛИ соединен с синхровходом дешифратора, вход разрешениявыборки которого является входомсинхронизации адреса устройства, второй вход первого элемента И соединен с первым выходом дешифратора, вторым выходом подключенного к вторымвходам второго и третьего элементовИ, первые входы элементов И первойгруппы и элементов И-НЕ группы соединены с группой выходов оперативнойпамяти, адресный вход которой подключен к выходу первого счетчика, соединенного счетным входом с выходомвторого элемента ИЛИ, первый вход которого подключен к выходу второгоэлемента И и входу записи оперативной памяти, о т л и ч а ю щ е е с ятем, что, с целью повышения быстродействия устройства, в него введенывторая группа элементов И, группасчетчиков, группа схем сравнения,регистр сдвига, второй счетчик, третий элемент ИЛИ и два элемента задержки, причем выход третьего элементаИЛИ соединен с информационным входомшинного формирователя, разрешающимвходом соединенного с первым выходомдешифратора, а выходом - с информационным входом регистра сдвига, группа выходов которого подключена к группе информационных входов оперативнойпамяти и первым входам элементов Ивторой группы, вторые входы которыхподключены к выходам элементов Ипервой группы и элементов И-НЕ группы, а выходы - к счетным входам счетчиков группы, выходами подключенныхк первым информационным входам схемсравнения группы, выходы которых соединены с группой входой третьего элемента ИЛИ, а вторые входы - с выходомвторого счетчика, счетный вход которого подключен к тактовому входу устройства и выходу первого элементазадержки, выходом соединенного стретьими входами элементов И второйгруппы и через второй элемент задержки с выходом прерывания устройства ивторым входом второго элемента ИЛИ,выход первого элемента И соединен стактовым входом регистра сдвига, вы .ход третьего элемента И соединен свходами сброса первого и второгосчетчиков и счетчиков группы, третийи четвертый выходы дешифратора подключены соответственно к установочному входу и входу сброса триггера,выходом соединенного с вторыми входами элементов И-Не группы и элементов И первой группы, третьи входы которых соединены с информационнымвходом устройства..г Составитель В. ВертлиТехред М.дидык едакто угренков а Черни оррек Заказ 2831ВНИИПИ Госуда и ГКНТ ССС Производственно-издательский комбинат "Патент", г. Ужгор Гагарина, 1 О 71 35 13 13 27 26 19 16 1 Тираж 565 Подписное венного комитета по изобретениям и открытия 113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

4607145, 17.11.1988

ПЕРМСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА В. И. ЧУЙКОВА

ТЮРИН СЕРГЕЙ ФЕОФЕНТОВИЧ

МПК / Метки

МПК: G06F 13/00

Метки: ввода, дискретных, микроэвм, сигналов

Опубликовано: 23.09.1990

Код ссылки

<a href="https://patents.su/8-1594554-ustrojjstvo-dlya-vvoda-v-mikroehvm-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода в микроэвм дискретных сигналов</a>

Предыдущий патент: Устройство для сопряжения эвм с внешним абонентом

Следующий патент: Устройство для сопряжения двух электронно-вычислительных машин

Случайный патент: Устройство для окраски изделий типа тел вращения