Устройство магнитной записи сигналов цифровой информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1157566

Авторы: Закржевский, Клюкина, Соловьев, Чуманов

Текст

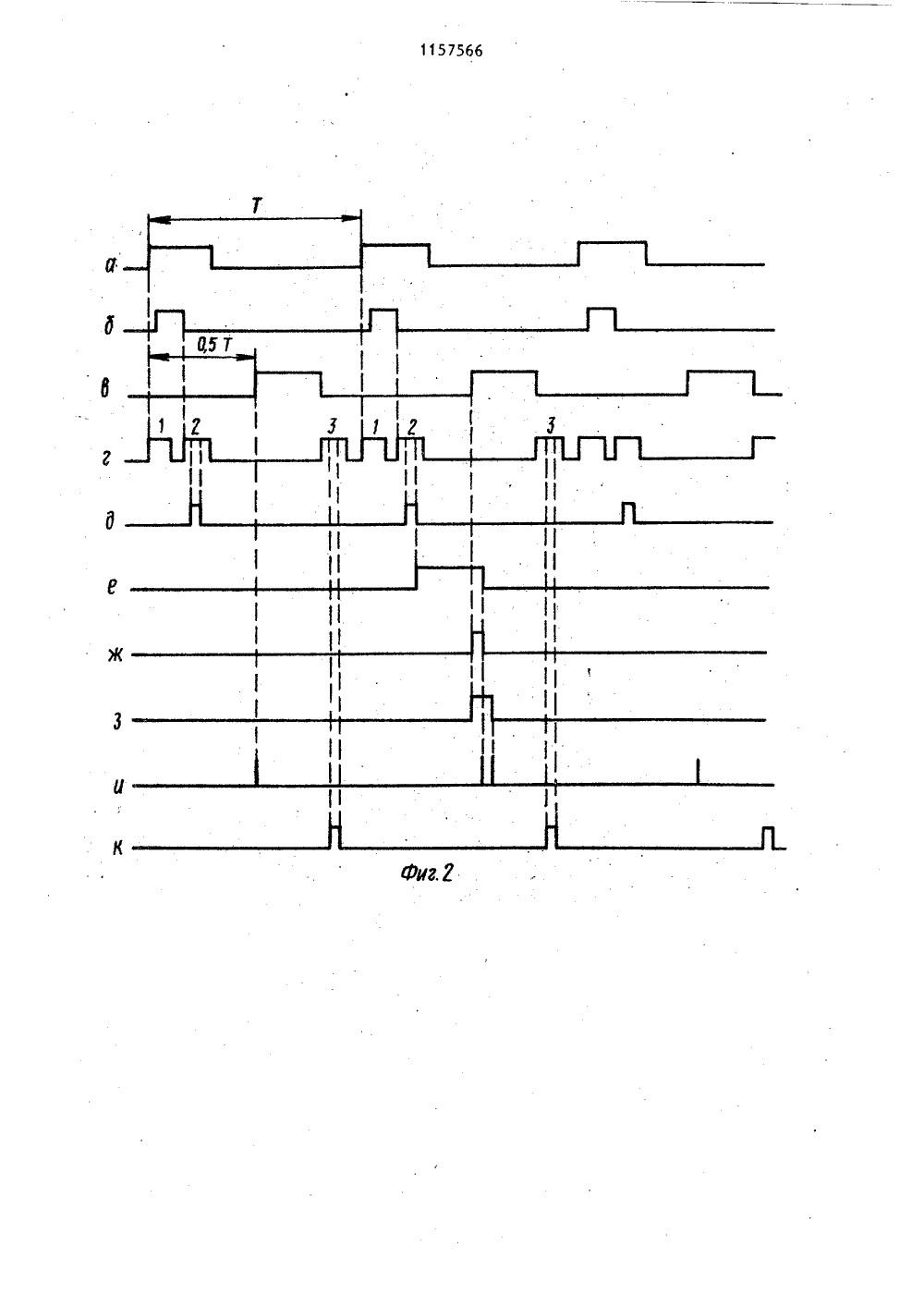

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 11 В 5/09 0 НИЕ ИЗ ЕТЕНИЯ У Ав 21) 3678209/24-1022) 26.12.8346) 23.05.85. Вюл.72) В.С. Соловьев,(53) 5 (56) 1 В 8860 4,852 (08 Авторско 2, кл. С вторское 37, кл. С 3/04, 198 2.В 1037СО 6 Р ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ СКОМУ СВИДЕТЕЛЬС(54) (57) УСТРОЙСТВО МАГНИТНОЙ ЗАПИСИСИГНАЛОВ ЦИФРОВОЙ ИНФОРМАЦИИ, содержащее входные шины информационныхсигналов в параллельном коде, входную шину сннхроимпульсов, буферныйблок записи, регистр памяти, блокконтроля, преобразователь сигналовпараллельного кода в последовательный, соединенный информационным выходом и входом управления последовательного вывода информации соответственнр с информационным и тактовым входами блока магнитной записи,и генератор сигналов опорной частоты,о т л и ч а ю щ е е с я тем, что, сцелью повышения достоверности записицифровой информации, буферный блокзаписи содержит блоки оперативнойпамяти, а в устройство введеныэлемент ИЛИ, переключатель адресов,дешифратор первого адреса, переключатель блоков оперативной памяти, первый и второй дешифраторы номеровблоков оперативной памяти, блокключей, блок сравнения, первый ивторой элементы И, счетчик ошибок,формирователь импульсов переключения дЯО 1157566 А блоков оперативкой памяти и формирователь управляющих последовательностей импульсов, первым входом соединенный с входной шиной синхроимпульсов, вторым входом - с первым входомформирователя импульсов переключения блоков оперативной памяти и свыходом генератора сигналов опорнойчастоты, а первым выходом - с входами управления записью-считываниемблоков оперативной памяти, вторым и .третьим выходами соответственно свходами управления последовательнымвыводом и параллельньи вводомсигналов информации преобразователяпараллельного кода в последовательный, четвертым выходом соединенныйс входом стробирования блока контроля, пятьж выходом - с первым вхо"дом первого элемента И, с сигнальньи.входом переключателя адресов и свторьи входом формирователя импульсов переключения блоков оперативной памяти, а шестым выходом - с входом стробирования первого дешифратора номербв блоков оперативнойпамяти, выходы которого подключенык входам сигнала разрешения соответствующих блоков оперативной памяти, при этом входные шины информационных сигналов в параллельномкоде соединены с первой группойинформационных входов блока контроля и с информационньии входамиблоков оперативной памяти, выходыкоторых через элемент ИЛИ соединеныс информационньии входами преобразователя сигналов параллельного кодав последовательный, а также с второй группой информационных входовработы этого блока оперативной памяти сигнал на выходе блока 27сравнения отсутствует.Когда на выходах переключателя20 адресов опять имеется адреспервой ячейки памяти, то это означает, что запись информации вовсе ячейки памяти данного блокаоперативной памяти завершилась.Начинается поочередная запись входных информационных параллельныхкодов последовательно во всей ячейке памяти следующего блока оперативной памяти,Если же после очередного контрольного считывания из данногоблока оперативной памяти, счетчик17 ошибок насчитывает заданноечисло (например,32) импульсов ошибок, т.е. блок 11 контроля во время работы данного блока оперативной памяти зафиксировал 32 ячейкипамяти, дающие сбои информации,навыходе счетчика 17 ошибок устанавливается сигнал (фиг.2 й) до прихода, сдвинутого синхроимпульса,а в момент прихода этого синхроимпульса Формируется сигнал (фиг:2 а)на выходе элемента И 18, которыйпоступает на установочный входпереключателя 20 адресов и устанавливает его в нулевое состояние.Сигнал с выхода элемента И 18поступает также на управляющий входблока 25 ключей. Но время действияэтого сигнала, сигнал с выхода дешифратора 24, соответствующего номеруданного, отказавшего блока оперативной памяти, поступает через соответствующий замкнутый ключ насоответствующий вход регистра 26памяти и записывается в нем, Такимобразом, регистр 26 памяти запоминает номер отказавшего блока оперативной памяти на время дальнейшей работы устройства.Поскольку выходным сигналом элемента И 18 включен первый адрес,то сформированный формирователем 28первый импульс проходит через элемент И 19 и переключает в следующеесостояние переключатель 22 блоковоперативной памяти. Переключатель22 при этом задает номер следующегоблока оперативной памяти, Пустьблок этой оперативной памяти также оказывается неисправньг, Информация об этом хранится в регистре 26 памяти.При этом формируется сигнал (Фиг.2 р) на выходе блока 27 сравнения, так как сигнал на одном иэ входов его второй группы входов, .соответствующем номеру включенного, числящегося неисправным, блока оперативной памяти, совпадает с сигналом соответствующего входа первой группы входов блока сравнения, поступающего с соответствующего номеру включенного неисправного блока оперативной памяти выхода дешифратора 24.При наличии сигнала на выходе блока 27 сравнения, формирователь 28 импульсов переключения блоков оперативной памяти формирует еще один импульс (Фиг,2 к), который вторично переключает переключатель 22 блоков оперативной памяти, тем самым задается номер следующего работоспособного блока оперативной памяти, который в регистре 26 памяти не хранится.После чего сигнал (фиг.2 и) на выходе блока сравнения снимается и работа устройства продолжается с ячейками памяти данного исправного блока оперативной памяти.Таким образом, осуществляется обход ранее зафиксированного неисправным блока оперативной памяти в случае обнаружения отказа предыдущего ему блока оперативной памяти, а также каждый раз в случае обычной смены предыдущего ему исправного блока оперативной памяти,Технико-экономическая эффективность предлагаемого устройства состоит в повышении верности результата записи цифровой информации (в результате замены буферного блока записи-воспроизведения, выполненного в виде аппарата магнитной записи, на буферный блок, выполненный на основе блоков оперативной памяти с использованием микросхем), а также в повышении надежности, уменьшении габаритов, массы и потребляемой мощности, по сравнению с известными устройствами "Волна" и ц Н1157566 ФО блока контроля, выход которого соединен через счетчик ошибок с вторьм входом первого элемента И выходом связанного с управляющим входом блока ключей и с входом установки в первое состояние переключателя адресов, выходы которого соответственно соединены с адреснымивходами блоков оперативной памятии с входами дешифратора первого адреса, выходом соединенного с первьмвходом второго элемента И,к выходу которого подключены вход установки в "О" счетчика ошибок к входпереключателя блоков оперативной 1Изобретение относится к приборо- . строению, а именно к технике магнитной записи, и может быть использовано в автоматизированных системах магнитной регистрации информации телеметрии с целью сокращения объема записываемых цифровых данных путем осуществления выборочной записи отдельных, представляющих для эксперимента интерес, фрагментов непрерывно поступающей информации с обеспечением при этом записи определенного количества данных, предшествующих началу записываемого фрагмента. ИИзвестно устройство для магнитной записи сигналов цифровой инфор" мации, .содержащее буферный блок записи-воспроизведения, регистр памяти, преобразователь параллельного кода в 2 последовательный, соедийенный информационньм выходом и входом управления последовательньм выводом информации соответственно с информационкьм и тактовьм входаии основного д блока магнитной записи, и генератор сигнала опорной частоты 111.Недостатки этого устройства заключаются в его относительно больших габаритах, массе и потребляемой им электроэнергии, а также в низкой надежности работы его и в не очень высокой достоверности записи с его помощью цифровой информации, так памяти, выходами подключенного к первому и к второму дешифраторам номеров блоков оперативной памятиУ причем выхбды второго дешифратора соединены с первой группой входов блока сравнения и через блок ключей с входами регистра памяти, выходами связанного с второй группой входов блока сравнения, выход котоФрого подключен к третьему входу формирователя импульсов переключения блоков оперативной памяти, выходом соединенного с вторым входом второго элемента И. 2как в качестве буферного блока записи-воспроизведения применен, аппарат магнитной записи с кольцевьм лентопротяжньм механизмом.Достоверность передачи цифровой информации таким буферньм блоком записи-воспроизведения значительно снижается иэ-за выпадений сигнала воспроизведения с магнитной ленты,рабочий отрезок которой многократно реверсируется, т.е. подвергаетсясильному износу в кольцевом лентопротяжном механизме в течение длительного времени. Кроме того, буферный блок записи-воспроизведения,выполненный на основе аппарата иагнитной записи, вносит значительные временные искажения в передаваемый им цифровой сигнал, что также ухудшает достоверность последующей выборочной перезаписи информации на основной блок магнитной записи и требует применения специальной системы коррекции временных ошибок, усложняющей устройство.Наиболее близким к изобретению по технической сущности является устройство магнитной записи сигналов цифровой информации, содержащее шины ввода информационных сигналов в параллельном коде, входную шину синхроимаульсов, буферный блок записи"воспроизведения, регистр памяти, блок контроля, преобразовательпреобразователя параллельного кода впоследовательньпг, четвертым выходом соедиггенньгй с входом стробирования блока контроля, пятым выходомс первым входом первого элемента И,с сигнальньк входом переключателяадресов и с вторым входом формирователя импульсов переключения блоковоперативной памяти, а шестымвыходом - с входом стробирования первого дешифратора номеров блоков оперативной памяти, выходы которогоподключены к входам сигнала разрешения соответствующих блоков опера-тивной памяти, при этом входные шиныинформационных сигналов в параллельном коде соединены с первой группойинформационных входов блока контроляи с информационными входами блоков оперативной памяти, выходы которых через элемент ИЛИ соединеныс информационными входами преобразователя сигналов параллельногокода в последовательньп, а такжес второй группой информационных входов блока контроля, выход которогосоединен через счетчик ошибок свторым входом первого элемента И,выходом связанного с управляющим вхо"дом блока ключей и с входом установки в первое состояние переключа,/ (,теля адресов, выходы которого соответственно соединены с адреснымивходами блоков оперативной памятии с входами дешифратора первого адреса, выходом соединенного с первымвходом второго элемента И, к выходу которого подключены вход установггки в О счетчика ошибок и входпереключателя блоков оперативнойпамяти , выходами подключенного кпервому и к второму дешифратор амномеров блоков оперативной памятипричем выходы второго дешифраторасоединены с первой группой входовблока сравнения и через блок ключейс входами регистра памяти, выходамисвязанного с второй группой входовблока сравнения , выход .которогоподключен к третьему входу формирователя импульсов переключения блоков оперативной памяти , выходомсоединенного с вторым входом второго элемента И .Ыа фиг . 1 . изображена структурнаясхема предлагаемого устройства , нафиг . 2 - временные диаграммы , поясняю"щие работу предлагаемого устройства з 11 г 7.гг 16сигналов параллельного кода в последовательный, соединенный информационным выходом и входом управленияпоследовательного вывода информации соответственно с информационньми тактовььг входами основного блокамагнитной записи, и генератор сигналов опорной частоты 2,Недостатками известного устройства являются невысокая верность записи с его помощью цифровой информации, а также относительно болвшиегабариты, масса и потребление электроэнергии.Цель изобретения - повышение 5достоверности записи цифровой информации.Поставленная цель достигаетсятем, что в устройстве магнитнойзаписи сигналов цифровой информации, 20содержащем входные шины информационных сигналов в параллельном коде,входную шину синхроимпульсов, буферный блок записи, регистр памяти,блок контроля, преобразователь сигналов параллельного кода в последовательный, соединенный информационным выходом и входом управления последовательного вывода информациисоответственно с информационным итактовым входами блока магнитнойзаписи, и генератор сигналов опорной частоты, буферный блок записисодержит блоки оперативной памяти,а в устройство введены элемент ИЛИф 35переключатель адресов, дешифраторпервого адреса, переключатель блоков оперативной памяти, первый ивторой дешифраторы номеров блоковоперативной памяти, блок ключейэ 40блок сравнения, первый и второйэлементы И, счетчик ошибок, формирователь импульсов переключенияблоков оперативной памяти и формирователь управляющих последователькостей импульсов, первым входомсоединенный с входной шиной синхроимпульсов, вторым входом - с первым входом формирователя импульсовпереключения блоков оперативной50памяти и с выходом генератора сигналов опорной частоты, а первым выходом - с входами управления записью-считыванием блоков оперативнойпамяти, вторым и третьим выходамисоответственно входами управленияпоследовательным выводом и параллельным вводом сигналов информации1157566 3 15 36 .ЗФ 33 ной памяти. эз выход соединен с управляющим входом наиг.З - в развернутом виде формирователь управляющих последовательностей импульсов; на фиг.4 - з развернутом виде Формирователь импуль" сов переключения блоков оперативной памятиПредлагаемое устройство (фиг. 1) содержит входные шины 1 информационных сигналов в параллельном коде, блоки 2-9 оперативной памяти, образующие совместно буферный блок записи устройства (не выделен),эле," мент ИЛИ 10, блок 11 контроля, преобразователь 12 параллельного кода в последовательный.,блок 13 магнитной записи, входную шину 14 синхро" импульсов, формирователь 15 управляю щих последовательностей импульсов, генератор 16 сигнала опорной частоты, счетчик 17 ошибок, первый 18 и второй 19 элементы И, переключатель 20 адресов, дешифратор 21 первого адреса, переключатель 22 блоковоперативной памяти, первый 23 и второй 24 дешифраторы немеров бло ков оперативкой памяти, блок 25 ключей, регистр 26 памяти, блок 27 сравнения и Формирователь 28 кмпуль сов переключения блоков оперативной памяти, Кроме того, в устройстве имеется входная шина 29 сигнала начальной установки в "0" регистра 26 памяти.формирователь 15 управляющих последовательностей иинулъсов (Фиг.З) содержит делитель 30 частоты, первый 31, второй 32, третий 33 и четвертый 34 элементы задержки, первый 35, второй Зб, третий 37 и четвертый 38,однозибраторы, первый 39 и втврой 40 кнверторы, элемент И 41 и элемент ИЛИ 42.Формирователь 28 импульсов переключения блоков оперативной памяти (фи 1,4) содержит блок. 43 выделения Фронта иипулъсоз, первый 44 и второй 45 счетчики импульсов, элемент ИЛИ-НЕ 46, первый 47 и второй ;48 триггеры, инвертор 49 и первый 50, второй 51 к третий 52 элементы И.Входные шины 1 инфориарионных сигкалоз з параллельном коде соединены с икфориационньии входами каждого блока 2-9 оперативной памяти, которые могут быть вы олкены, например, нв интегральных микросхемах и с первой группой информационных входов блока 11 контроля, Вьмодыкаждого блока оперативной памятисоединены с входами элемента ИЛИ 1 О,выходы которого соединены с информационнции входаии преобразователя12 параллельного кода в последовательный и с второй группой информвционньм входов блока 11 контроля. Выход преобразователя 12параллельного кода в последовательный соединен с информационным входои блока 13 магнитной записи.Входная шина 14 синхроимпульсовсоединена с первьщ зходои формирователя 15 управляющих последовательностей импульсов, второй вход которого соединен с выходом генератора 16 сигналов опорной частотыи с первым входом формирователя 28импульсов переключения блоков оперативной памяти. Формирователь 15управляющих последовательностей импульсов первым выходом соединен свходом управления записью-считцванием каждого блока 2-9 оперативнойпамяти, вторым выходом - с входомуправления последователъньак выводоминформации преобразователя 12 параллелъного кода в последовательныйи с тактовым входом блока 13 магниткой. записи, третьим выходом - свходом управления параллельньивводои информации преобразователя12 параллельного кода воследователъный, четвертьи выходом - свходом стробирования блока 11 контроля, пятью выходои " с первьи входом элемента И 18, с сигнальньмвходом переключателя 20 адресов и с вторым входом формирователя 28 импулъсов переключения блоков оперативной памяти, а шестым выходом - с входом стробирования дешифратора 23 номеров блоков оперативВыход блока 11 контроля соединен со счеткьи входом счетчика 17 ошибок, выход которого соединен с вторЫй входом элемента И 18, в его блока 25 ключей и с установочным в10" входом переключателя 20 адресов, выходами соответственно соединенного с адресньии входами каждого блока оперативной памяти и с входами дешифратора 21 первого адреса, выходом связанного с первьи входом элемента И 19, выход ко 1 орогосоединен с установочньм в "0" входом счетчика 17 ошибок и с входом переключателя 22 блоков оперативной памяти. Выходы этого переключателя соединены с входами первого 23 и второго 24 дешифратора номеров блоков оперативной памяти, выходы второго дешифратора 24 соединены с сигнальными входами блока 25 ключей и с первой группой входов блока 27 сравнения.Выходы блока 25 ключей соединены с сигнальными входами регистра 26 памяти, выходы которого соединены с второй группой входов блока 27 сравнения. Входная шина 29 соединена с установочным в "О" входом регистра 26 памяти. Выход блока 27 сравнения соединен с третьим входом формирователя 28 импульсов переключения блоков оперативной памяти, выход которого соединен с вторым входом элемента И 19, Каждый выход первого дешифратора 23 номеров блоков оперативной памяти соединен с входом сигнала разрешения соответствующего блока 2-9 оперативной памяти.Первый вход формирователя 15 соединенный с входной шиной 14 синхроимпульсов, соединен с входом элемента 31 задержки,с входом элемента И.41 и с установочным в "0" входом делителя 30 частоты, выполненного на основе счетчика, Второй вход формирователя 15, соединенный с выходом генератора 16 сигнала опорной частоты, соединен с сигнальньк (счетным) входом делителя 30 частоты. Выход элемента 31 задержки соединен с входом одновибратора 35, выход которого соединен с, входом инвертора 39 и с первым выходом (выход импульсов записи) форГирователя 15, соединенньи с вхоом управления записью-считываникаждого блока оперативной памяти. Выход делителя 30 частоты соединен с вторич выходом (выход тактового сигнала поспедовательной записи информации в блоке 13 магнитной записи) формирователя 15, соединенньи с входом управления последова-, тельньи выводом информации преобразователя 12 параллельного кода в . последовательный и.с тактовым входои блока 13 магнитной записи. Выход инвертора 39 соединен с вторьи входом элемента И 41 и с входомэлемента 33 задержки.Выход элемента 32 зацержки соединен с входом инвертора 40, выход э которого соединен с первым входомэлемента ИЛИ 42 и с входом элемента 34 задержки. Выход последнегосоединен с входом одновибратора 38,выход которого соединен с третьим 1 О выходом (выход импульсов считыванияс задержкой) формирователя 15, соединенным с входом управления параллельным вводом информации преобразователя 12 параллельного кода 15 в последовательный. Выход элемента 33 задержки соединен с входомодновибратора 37, выходом соединенного с четвертым выходом (выходимпульсов контрольного считывания) В формирователя 15, который соединенс входом стробирования блока 11контроля. Выход элемента 32 задержкисоединен также с пятым выходом(выход сдвинутых синхроимпульсов) 23 формирователя 15, соединенньи свторым входом формирователя 28 импульсов переключения блоков оперативной памяти, с первым входомэлемента И 18 и с сигнально входом фр переключателя 20 адресов. Выходэлемента И 41 соединен с вторымвходом элемента ИЛИ 42, выход которого соединен с входом одновибратора 36. Выход последнего соединенс шестым выходом (выход импульсовразрешения) формирователя 15, соединенным с входом стробирования дешифратора 23 номеров блоков оперативной памяти.Первый вход формирователя 28,соединенный с выходом генератора 16сигнала опорной частоты, соединенсо счетным входом счетчика 44 импульсов, Второй вход формирова теля 28, соединенный с пятью выходом формирователя 15 управляющих.последовательностей импульсов соеди.Энен с входом блока 43 выделенияфронта импульсов, выход которого ЗЕ соединен с установочным в "0" входомсчетчика 44 импульсов и с единичнымустановочным входом триггера 47.Выход первого разряда счетчика 44импульсов соединен с первым входом у элемента И 50 и с первым входом элемента И 51. Выход второго разряда.счетчика 44 импульсов соединен свторьм входом элемента И 50 и с вхо- .дом инвертора 49, выход которого соединен с вторым входом элемениа И 51. Выход элемента И 50 соеди" нен с инверсным счетным входом счетчика 45 импульсов и с первым вхо дом элемента И 52, Выход последнего соединен с первым входом элемен" та ИЛИ-НЕ 46, выход которого соединен с нулевым установочным входом триггера 47, а его выход соединен с 1 вторым входом элемента И 52, выход которого соединен с выходом формирователя 28 и с единичным установочным входом триггера 48. Второй вход элемента ИЛИ-НЕ 46 соединен с третьим 1 з входом формирователя 28, соединенным с выходом блока 27 сравнения. Инверсный выход триггера 48 соединен с третьк входом элемента ИЛИ-НЕ 46 и с установочным в "О" входом счет чика 45 импульсов, выход третьего разряда которого соединен с С-входом триггера 48. 0-вход триггера 48 соединен с шиной потенциала логического "0". ИБлоки оперативкой памяти могут быть выполнены, например, на интегральных микросхемах, представляющих собой статические оперативные запоминающие устройства определенной ем кости (в зависимости от типа используемых микросхем), образующие ячейки памяти.Для получения необходимой задержки передачи (считывания) информацион-щ нык сигналов буферным блоком записи в предлагаемом устройстве используются "несколько последовательно работающих идентичных блоков оперативной памяти, например восемь блоков 2-9. Реэуль- . р тирующее время. задержки считывания информационных сигналов получается при этом равным произведению дли тельности интервала следования сиихроимпульсов входных параллельных ,р кодов на число ячеек памяти одного блока оперативной памяти и ка коли" чество этих блоков.Элемент ИЛИ 10 могут представ-лять собой (например) монтажное ЗФ (проводное) ИЛИ.Предлагаемое устройство работает следующим образом.На вторую шину 14 поступают синхроимпульсы:(фиг.2 а), сопровож- .у дающие поступающие на входные ши.ны 1 в параллельном коде информационные сигналы, В течение длительности каждого синхроимпульсана информационных входах всех блоков 2-9 оперативной. памяти и напервой группе информационных входовблока 11 контроля присутствуют сигналы.(значения разрядов) соответствующего входного информационногопараллельного кода.Входные информационные сигналыв параллельном коде поочередно,с интервалом следования синхроимпульсов, записываются последовательно сначала в ячейки памяти первого блока 2 оперативной памяти,затем второго блока 3 и т.д. допоследнего, восьмого блока 9 оперативной памяти включительно, послезаполнения которого запись вновьначинает производиться последовательно в ячейки памяти первогоблока 2 оперативной памяти, затеи,1 второго 3 блока оперативной памятии т.д. При этом в момент записипредыдущее содержимое этой ячейкипамяти автоматически стирается. Таким образом, после заполнения всехвосьми блоков оперативной памятив них содержится запись массива информации, поступившей в течениеопределенного времени тому назад(предыстория).Считаиная с задержкой из блоковпамяти, информация формируется .на выходе преобразователя 12 изпараллельного кода в последователъньй, который подается на информационный вход блока 13 магнитнойзаписи.Окончательная запись информациив устройстве производится блоком13 магнитной записи. Когда возникает необходимость (например, в случае возникновения отклонения одногоиз параметров контролируемогообьекта за допустимые пределы) восуществлении с данного момента времени записи информации, то по команде внешней системы блок 13 магнитной записи переводится в рабо-.чий режим записи информации, приэтом на его магнитную ленту вначалезаписано определенное количестводанных, предшествующих началу записываемого интересующего нас сообщения, хранящихся в блоках оперативной памяти,Поочередное переключение ячеек памяти в каждом блоке 2-9 опе12 задержки информации незначительносокращается, в частности, на 1/8,что допустимо с учетом сохранениявысокой достоверности передачи ин"З формации блоками оперативной паиятина запись в блок 13 магнитной записи.К контролю Функционированияблоков оперативной памяти имеют от ношение, кроме блока 11 контроля,следующие узлы.Счетчик 17 ошибок обнуляется вмомент включения нулевого адреса,т.е. в начале работы каждого блока 15 оперативной памяти, и подсчитываетколичество сбойных ячеек памяти одного блока оперативной памяти.Элемент И 18 синхронизируетпрохождение выходного сигнала счетф чика 17 ошибок на установочный впервое (нулевое) состояние входпереключателя 20 адресов со сдвинутыми сннхроимпульсами.Дешифратор 24 номеров блоков ЙЗ оперативной памяти и блок 25 ключейобеспечивают запись в регистр 26памяти номера отказавшего блокаоперативной памяти.При наличии сигнала на выходе 39 блока 27 сравнения, сравнивающегохранимый в регистре 26 памяти номеротказавшего блока оперативной памяти с номером включенного блока опе-ративной памяти, формирователь 28выдает еще один импульс для переключения устройства на работу соследующим блокок оперативной памяти.В результате этой операции исключается кз работы устройства отказавший р блок оперативной памяти.формирователь 15 управляющихпоследовательностей иипульсов управляет работой, всех уздоз и блоковпредлагаемого устройства. ,р В каждом интервале времени междуфронтамк двух соседних входныхсинхроимпулъсов,поступающих з устройство по шине 14, последовательново времени в устройстве осуществляю у ются следующие операции.Запись соответствующего данному:синхроимпульсу входного инфориационного параллельного кода в ячейку памяти, соответствующую установленному в предыдущем интервале следования синхроимпульсов, адресу,блока оперативной памяти, соответствующего,номеру заданному в данное1157566ративной памяти осуществляетсяс помощью переключателя 20 адресов,который последовательно Формируетна своих выходах параллельные двоичные коды адресов: от нулевого адреса и до адреса последней ячейкипамяти, Циклы формирования кодоввсех адресов непрерывно повторяютсяСигналы адресного кода поступаютс выходом переключателя 20 адресовна адресные входы каждого блока 2-9оперативной. памяти.Поочередное переключение блоков2-9 оперативной памяти осуществляется с помощью переключателя 22блоков оперативной памяти, выходныесигналы параллельного двоичногокода которого дешифрируются стробируемым дешифратором 23 номеров блоков оперативной памяти, Каждый выход дешифратора 23 соединен с входом сигнала разрешения соответствующего блока оперативной памяти.Сигнал на выходе дешифратора 23,соответствующем номеру работающегов данное время блока оперативнойпамяти, появляется только в отрезки времени определяемые сигналом,поступающим на вход стробированиядешкфратора 23 (фиг.20 .В формировании входного сигналадля переключателя 22 блоков оперативной памяти участвуют дешифратор 21 первого адреса, формирователь 28 импульсов переключенияблоков оперативной памяти и элемент И 19, пропускающий выходныеимпульсы формирователя 28которыйзапускается каждый раз при сиенеадреса, только при включении перво- .го (нулевого адреса).При большом количестве элементов (разрядов) памяти существуетвероятность отказа отдельных элементов. Поэтому буферный блок записив предлагаемом устройстве разбит наряд отдельных блоков 2-9 оперативной памяти работа каждого из которых непрерывно контролируется блоком 11 контроля. Если обнаружкваетсячто в данном блоке оперативной памяти количество ячеек памяти со сбойными разрядами (с разрядами памяти,искажающими информацию) превышаетдопустимое значение (равное, напри-мер 32), то этот блок оперативнойпамяти исключается из дальнейшейработы устройства. При этом времявремя переключателем 22 блоков оперативной памяти (эта операция выполняется в первой половине длительности сннхроимпульса). Контроль" ное считывание в параллельном коде только что записанных информационных сигналов из этой ячейки памяти для контроля ее состояния (эта операция производится во второй половине длительности синхронмпульса). Смена адресов ячейки памяти (эта операция выполняется в середине интервала между синхроимпульсами), Формирование сигнала о неисправности данного блока оперативной памяти в случае, если достоверность записи информации в этот блок стала ниже допустимой (эта операция по времени производится сразу же после смены адреса), Включение следующего блока оперативной памяти в случаях, если после очередной смены адреса был установлен нулевой адрес или если был сформирован сиг-, нал об отказе данного блока оперативной памяти (эта операция производится с небольшой задержкой после смены адреса). Поиск следующего исправного блока оперативной памяти (так называемый обход неисправного блока оперативной памяти. Считывание информационных сигналов из ячейки памяти, соответствующей новому адресу, т,е. считывание информации с задержкой для последующей записи ее (при необходимости) в блоке 13 магнитной записи (эта операция выполняется после завершения поиска следующего исправного блока оперативной памяти и до прихода фронта следующего синхроимпульса) .При выполнении оперативной записи, контрольного считывания и считывания с задержкой на шестом выходе формирователя 15 управляющих последовательностей импульсов формируются импульсы включения (фиг.2), которые поступают через дешифратор 23 номеров блоков оперативной памяти на вход сигнала разрешения, соответствующего заданному переключателе 1 ч 22 номеру блока оперативной памяти, и включают его на соответ.ствующее время.Для осуществления записи каждого очередного входного информационного параллельного кода в ячейку памяти, соответствующую установленному в данный момент адресу, на первомвыходе формирователя управляющихпоследовательностей импульсов 15формируются с частотой синхроимпулвсон импульсы записи (фиг,23),которые по времени расположены внутри первой полонины длительностисинхроимпульсов. Во время каждогоиэ этих импульсон, поступающих навходы управления записью-считываниемблоков 2-9 оперативной памяти, осуществляется запись информационногопараллельного кода в соответствующуюячейку памяти. Одновременно с импульсом записи на вход сигнала разрешения блока оперативной памяти,номер которого в двоичном кодеустановлен в данный момент на выходах переключателя 22 блоков оперативной памяти, поступает первыйимпульс включения с соответствующего выхода дешифратора 23 номеровблоков оперативной памяти. Сигнална стробирующем входе дешифратора23 и, следовательно, на любом выходе этого дешифратора показан нафиг,21.,После окончания импульсов записиблоки оперативной памяти находятсяв режиме считывания (низкий уровеньсигнала, фиг,28).На четвертом выходе формирователя 15 управляющих последовательностей импульсов формируются с частотой синхроимпульсов импульсы кон-. трольного считывания (фиг.59), которые поступают на вход стробированияблока 11 контроля. Каждый импульсконтрольного считывания по временинаходится внутри второго импульса стробирования дешифратора 23, расположенного во второй половине длительности синхроимцульса (фиг,2) .Во время действия импульса контрольного считывания на входе стробирования блока 11 контроля,на его первой группе информационныхвходов еще присутствуют данные входные информационные сигналы,.а навторую группу информационных входовблока контроля поступают толькочто записанные эти информационныесигналы с выходов включенного вданное время блока оперативной памя. ти.В блоке 11 контроля при этом осуществляется поразрядное суммирование по модулю два входных информационных сигналов и сигналов, записанных в ячейке памяти блока опе. ративной памяти.Если один нз символов входногопараллельного кода оказывается , Эзаписанным в блоке оперативной памяти неправильно, то сумма помодулю два этого входного символаи соответствующего ему считанногоошибочного символа не равна нулю., 1 ОВ этом случае сигналы с выхода соответствующего сумматора по модулюдва стробируются импульсом контрольного считывания и поступаютна выход блока 11 контроля. 13Выходные импульсы блока 11 контроля подсчитываются счетчиком 17ошибокмодуль счета которого равен,например, 32. Счетчик 17 ошибоксбрасывается в нулевое состояние ЗОкаждый раз при установке нулевогоадреса, т.е. в начале цикла работыкаждого блока 2-9 оперативной памяти.В середине интервала между входными синхроимпульсами, на пятом выходе фформирователя 15 управляющих последовательностей импульсов формируетсясигнал (фиг.2), представляющий собой сдвинутые на иолпериода синхроимпульсы. От переднего фронта каждо ЗОго сдвинутого синхроимпулъса переключается переключатель 20 адресови запускается Формирователь 28 импульсов переключения блоков оперативной памяти (фиг.2) . ИПри отсутствии. сигнала на выходеблока 27 сравнения формирователь 28выдает один импульс (первый импульс, фиг,2 ф,Выходной сигнал (импульс) форми Фрователя 28 иоступает на вход переключателя 22 блоков оперативной памя.ти и на установочный в нулевое состояние вход счетчика 17 ошибок черезэлемент И 19, которЮ управляется 4выходным сигналом дешифратора 21гервого адреса.Следовательно, переключение вследующее состояние переключателяблоков оперативной памяти и сброс 9в нулевое состояние счетчика 17ошибок производится только привключении первого (нулевого) адреса, т.е. при смене блоков оперативной памяти. 33В промежутке времени . междусдвинутыю сиихроеатулъсом, а именномежду окончанием формирования вы 1157566 16ходкого импульса (импульсов) формирователем 28 импульсов переключенияблоков оперативной памяти и фронтомследующего входного синхроимпульса,на шестом выходе формирователя 15управляющих последовательностей импульсов формируется третий импульсстробирования дешифратора 23 номеров блоков оперативной памяти, этотимпульс поступает через дешифратор23 на вход сигнала разрешения, соответствующего выходному коду переключателя 22 данного блока оперативнойпамяти 2-9, который включается дляобеспечения операции считывания сзадержкой.Импульсы считывания с задержкойформируются по времени внутри дпительности третьего импульса стро.".бирования девифратора 23 на третьемвыходе формирователя 15 управляющихпоследовательностей импульсов. Им",пульс считывания с задержкой осуществляет считывание информационныхсигналов ячейки памяти, адрес которой перед этим установлен фронтом сдвинутого синхроимпульса,путем параллельной перезаписиэтих сигналов в преобразователь 12параллельного кода в последовательный. Считанная при этом информацияпредставляет собой предысторию пове.дення данного параметра, так какона записана в эту ячейку определенное время тому назад.После прихода фронта следующеговходного синхроимпулъса повторяются операция записи пришедшего одновременно с этим синхроимпульсомвходного информационного параллельного кода в ячейку памяти, задер"жанные информационные сигналы которой перед этим считаны, и операцияконтрольного считывания.После прихода фронта сдвинутогосинхроимпулъса включается адресследующей ячейки памяти и черезнекоторое время из этой ячейки памяти производится считывание задер.жанной информации для последующей(при необходимости) последовательнойзаписи ее в блоке 13 магнитной записи и т.д.Если же ячейки памяти данногоблока оперативной памяти оказываются исправными или число отказавшихего ячеек памяти не превышает заданного значения,то за время цикла

СмотретьЗаявка

3678209, 26.12.1983

ПРЕДПРИЯТИЕ ПЯ А-7162

СОЛОВЬЕВ ВИКТОР СЕРАФИМОВИЧ, ЧУМАНОВ ИГОРЬ ВАСИЛЬЕВИЧ, КЛЮКИНА ГАЛИНА ГЕОРГИЕВНА, ЗАКРЖЕВСКИЙ СЕРГЕЙ ТАДЕУШЕВИЧ

МПК / Метки

МПК: G11B 5/09

Метки: записи, информации, магнитной, сигналов, цифровой

Опубликовано: 23.05.1985

Код ссылки

<a href="https://patents.su/13-1157566-ustrojjstvo-magnitnojj-zapisi-signalov-cifrovojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство магнитной записи сигналов цифровой информации</a>

Предыдущий патент: Способ магнитной записи цифровой информации

Следующий патент: Устройство воспроизведения сигналов магнитной записи

Случайный патент: Устройство для обслуживания разноприоритетных групп заявок