Микропроцессорная система для программного управления технологическими процессами

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

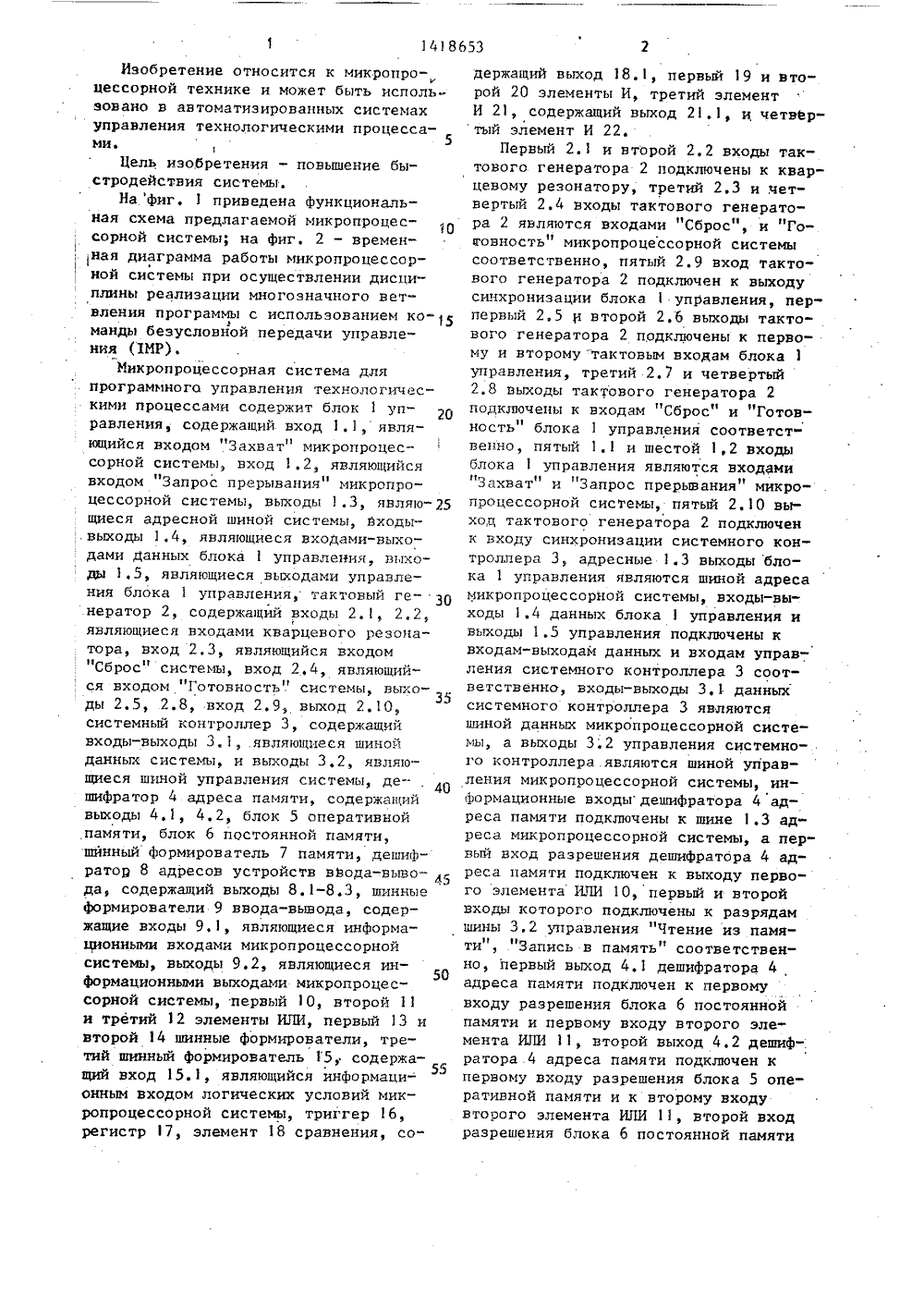

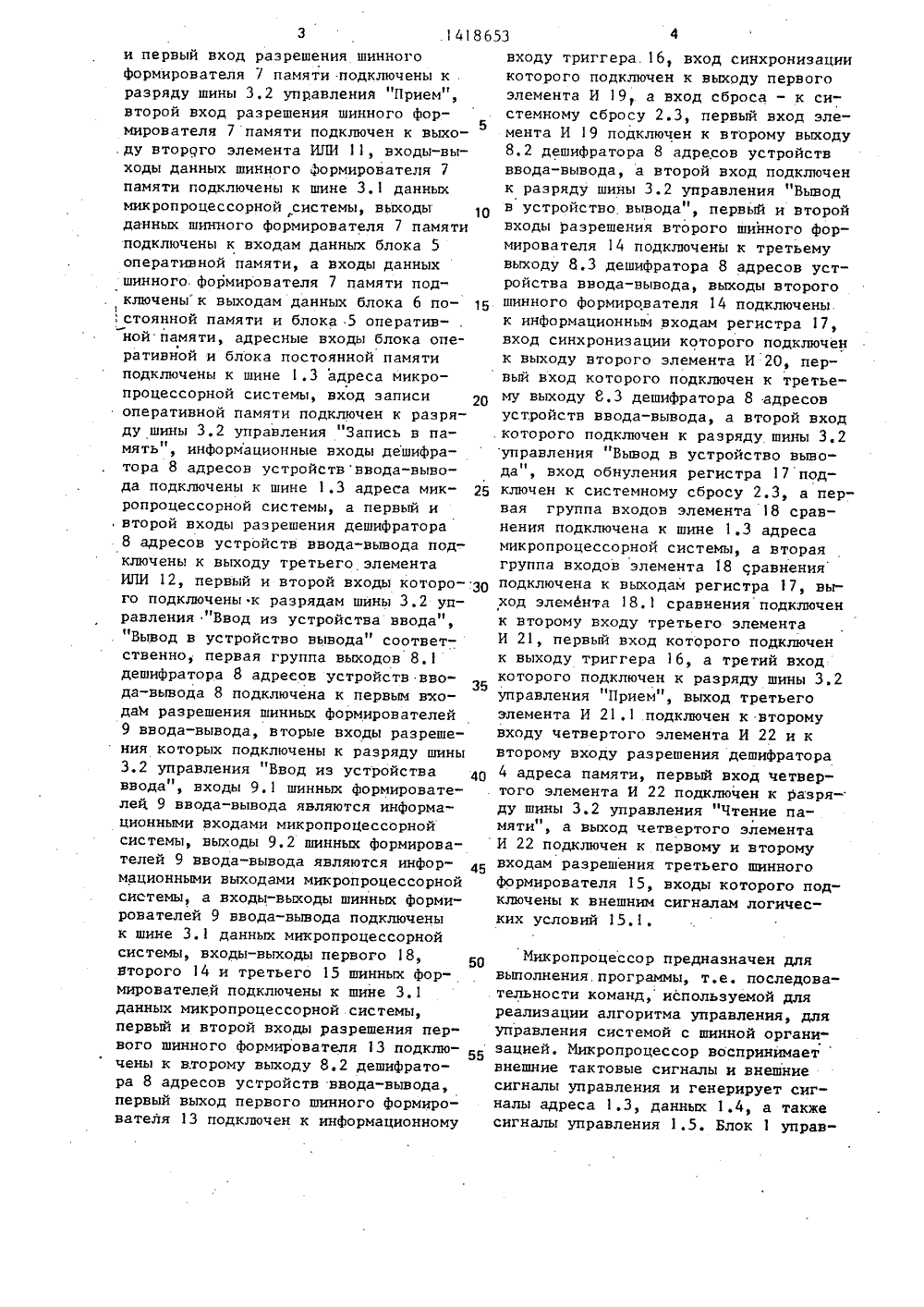

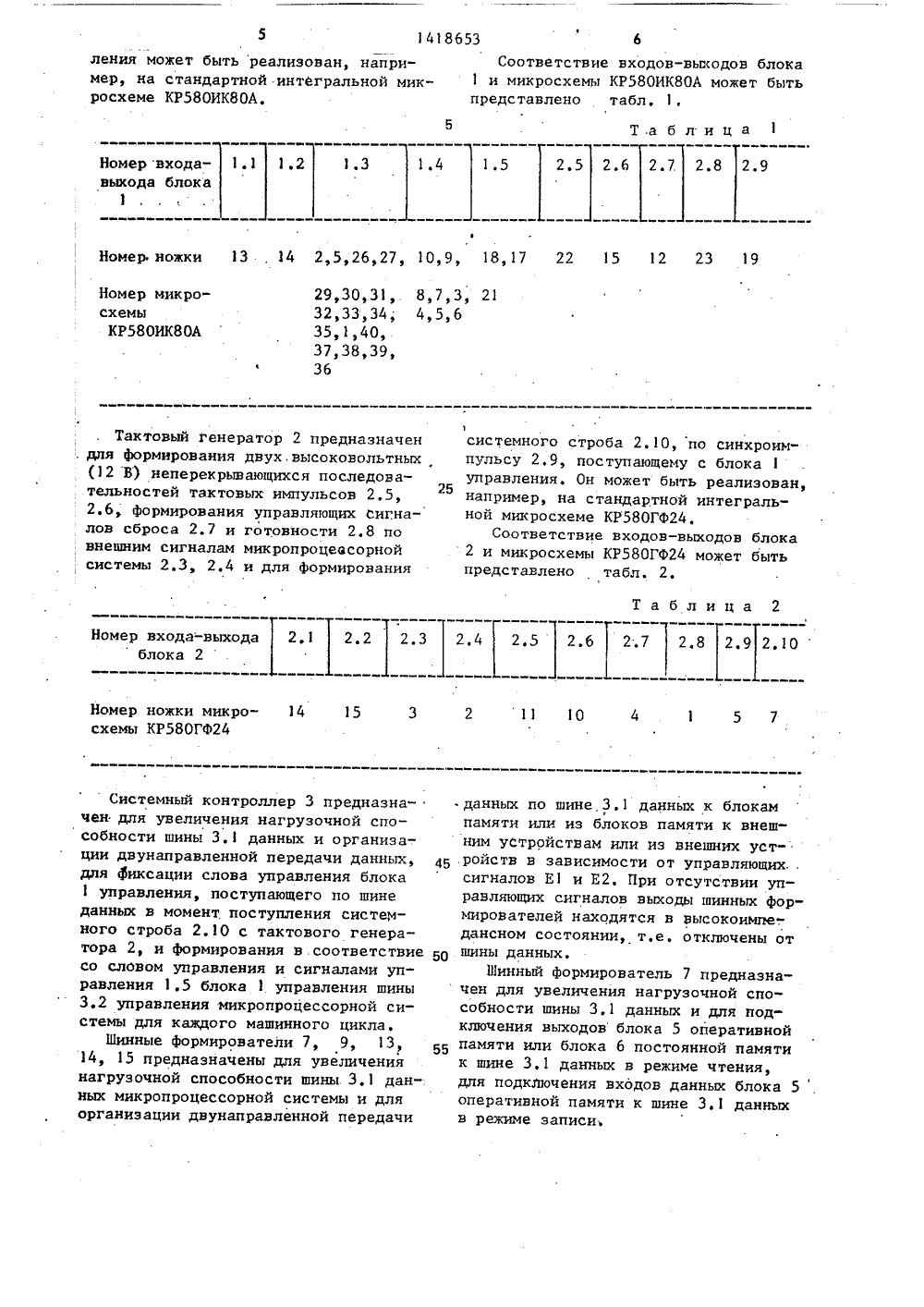

, 13 11 БЛЯО Т.А Д ИИОПИСАНИЕ ИЭОБРЕТЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ л. В Тимонькинрченкоенко ССР984.Р ру емь г ДЛЯГИЧЕ тносится к икроыть иссс си-. е и жетванн мати ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ(54) МИКРОПРОЦЕССПРОГРАММНОГО УПРАКИМИ ПРОЦЕССАМИ(57) Изобретениепроцессорной технпользовано в авто Г. Н.С. ХаН, Ткач88.8)идетельство С05 В 15/00,етельство ССС05 В 9/18,Пийль Е. И, Тие программирйств. - М: Эс, 69.ОРНАЯ СИСТЕМАВЛЕНИЯ ТЕХНОЛ стемах управления технологическимипроцессами. Цель изобретения - повышение быстродействия системы. Это достигается тем, что в известную систему, содержащую блок управления 1,тактовый генератор 2, системный контроллер 3, дешифратор 4 адреса памяти,блок 5 оперативной памяти, блок 6 постоянной памяти, шинный формировательпамяти 7, дешифратор 8 адресов уст-.ройств ввода-вывода, шинные формирователи 9 ввода-вывода, первый.10, втовторой 11 и третий 12 элементы ИЛИ,введены первый 13, второй 14 и третий15 шинные формирователи, триггер.16,регистр 17, элемент сравнения 18, пер-вый 19, .второй 20, третий 21 и четвертый 22 элементы И, Введение указанныхэлементов позволяет уменьшить время емуреализации программы многоальтернативного ветвления, 2 ил., 2 табл.17 1418 б 53 18 микропроцессорной системы, пятый выход тактового генератора подключен к го контроллера соответственно, входывыходы данных системного контроллераявляются шиной данных микропроцессорТ=1 с где Т ". общее время передачи управления;- количество обращений к подпрограмме;С - время выполнения команды 1 ЬР3(равно 1 О тактам). блока оперативной памяти и к второму входу второго элемента ИЛИ, второй вход разрешения блока постоянной памяти и первый вход разрешения шинного формирователя памяти подключены к Формула изобретения Микропроцессорная система для программного управления технологическими11процессами, содержащая блок управле- РазрЯДУ шины УпРавлениЯ ПРием , втония, тактовый генератор, системный рой вход разрешения шинного формироконтроллер, дешифратор адреса памяти,блок оперативной памяти, блок постоянной памяти, шинный Формировательпамяти, дешифратор адреса устройствввода-вывода, шинные формирователи сис, выхоДы Данных шинного формиввода-вывода, первый, второй и третий элементы ИЛИ, причем первый ивторой входы тактового генератора являются входами "Сброс" и "Готовность"микропроцессорной системы, пятый входтактового генератора подключен к выходу синхронизации блока управления,первый и второй выходы тактового гене- подключены к шине адреса микропроцесратора подключены к первому и второ" сорной системы, вход записи оперативму тактовым входам блока управления, ной памяти подключен к разряду шиныи Ф 1третий и четвертый выходы тактового управления Запись в память , инфоргенератора подключены к входам мационные входы дешифратора адресов"Сброс", Готовность" блока управле- . устройств ввода-вывода подключены кния соответственно, пятый и шестой шине адреса микропроцессорной систевходы блока управления являются вхо- мы, а первый и второй входы разрешедами "Захват" и "Запрос прерывания" ния дешифратора адресов устройств рователя памяти подключены к.входамданных блока оперативной памяти, авходы данных шинного формирователяпамяти подключены к выходам данныхблока постоянной памяти и блока оперативной памяти, адресные входы блокаоперативной и блока постоянной памяти выход третьего элемента И 21 активизируется (триггер 16 установлен) .и память системы отключается, шинный формирователь 7 памяти переводится в высокоимпедансное состояние, а третий шинный формирователь 15 подключает к шине .3.2 данных сигналы внешних логических условий 15,1, Таким образом, на шину 3.2 данных выводятся сигналы 151 Ф Ф Ф ФФФ хх, которые воспринимаются микропроцессором как второй байт командЫ 1 МР.Следовательно, осуществляется пе,реход по адресу Ф ф Фф ФФ х,хрФФФФЬЯ т.е. на одну из меток МО в , М 2 в зависимости от текущего значения сигналов внешних логических условий х 1, хоТаким образом, время многозначной передачи управления в предлагаемой микропроцессорной системе определяется соотношением входу синхронизации системного контроллера, адресные выходы блока управления являются шиной адреса микропроцессорной системы, входы-выходы данных блока управления и выходы управления подключены к входам-выходам,1 данных и входам управления системноной системы, а выходы управления системного контроллера являются шинойуправления микропроцессорной системы;информационные входы дешифратора адреса памяти подключены к шине адресамикропроцессорной системы, а первыйвход разрешения дешифратора адресапамяти подключен к выходу первогоэлемента ИЛИ; первый и второй входыкоторого подключены к разрядам шиныуправления "Чтение из памяти", "За пись в память" соответственно, первый выход дешифратора адреса памятиподключен к первому входу разрешенияблока постоянной памяти и первомувходу второго элемента ИЛИ, второй Зб выход дешифратора адреса памяти подключен к первому входу разрешения вателя памяти подключен к выходу вто 4, рого элемента ИЛИ, входы-выходы данных шинного формирователя памяти подключены к шине данных микропроцессорной19 ввода-вывода подключены к выходу третьего элемента ИПИ, первый и второй входы которого подключены к разрядам шины управления "Ввод из устройства ввода", "Вывод в устройство вывода" . соответственно, первая группа выходов дешифратора адресов устройств ввода. вывода подключена к первым входам разрешения шинных формирователей ввода- вывода, вторые входы разрешения которых подключены к разряду шины управления "Ввод из устройства ввода", входы шиннь 1 х формирователей ввода-вывода являются информационными входами 1 микропроцессорной системы, выходы шинных формирователей ввода-вывода являются информационными выходами микропроцессорной системы, а входы- выходы шинных формирователей вводаг вывода подключены к шине данных микропроцессорной системы, о т л и - ч а ю щ а я с я тем, что, с целью повьппения быстродействия, в нее введены первый, второй и третий;шинные формирователи, триггер, регистр, элемент сравнения, первый, второй, третий и четвертый элементы И, причем вхоДы-выходы первого, второго и третьего шинных формирователей подключеЭ ны к шине данных микропроцессорной системы, первый и второй входы разрешения первого шинного формирователя подключены к второму выходу дешифратора адресов устройств ввода-вывода, первый выход первого шинного формирователя подключен к информационному входу триггера, вход синхронизации которого подключен к выходу.первого элемента И, а вход сброса - к системному. сбросу, третьему выходу генератора, первый вход первого элемента И подключен к второму выходу,18653 20дешифратора адресов устройств вводавывода, а второй вход подключен кразрядушины управления "Вывод в устройство вывода", первый и второй входы разрешения второго шинного формирователя подключены к третьему выходу дешифратора адресов устройств ввода-вывода, выходы второго шинногоформирователя подключены к информационным входам регистра, вход синхронизации которого подключен к выходувторого элемента И, первый вход которого подключен к третьему выходу дешифратора адресов устройств вводавывода, а второй вход которого подключен к разряду шины управления "ВМвод в устройство вывода", вход рбнуления регистра подключен к системно- Ому сбросу - третьему выходу тактовогогенератора, первая группа входов элемента сравнения подключена к шине адреса микропроцессорной системы авторая группа входов элемента срав-.нения подключена к выходам регистра,выход элемента сравнения подключен квторому входу третьего элемента И,первый вход котоого подключен к вы-ходу триггера, а третий вход которо- О го подключен к разряду шины управления "Прием", выход третьего элементаИ подключен к второму входу четвертого элемента И и к второму входуразрешения дешифратора адреса памяти,первый вход четвертого элемента И 35подключен к разряду шины управления"Чтение памяти", а выход четвертогоэлемента И подключен к первому и второму входам разрешения третьего шинного формирователя, входы которогоподключены к внешним сигналам логических условий,Редактор Н, Гун роизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,Заказ 4151/43 Тираж 866 ВНИИПИ Государстве по делам изобре 113035, Москва, Ж, Подписноеного комитета СССРений и открытийРаушская наб., д.Изобретение относится к микропро-, цессорной технике и может быть использовано в автоматизированных системах управления технологическими процессами.5Цель изобретения - повышение быстродействия системы.На фиг.приведена функциональная схема предлагаемой микропроцессорной системь 1; на фиг, 2 - временная диаграмма работы микропроцессорной системы при осуществлении дисциплины реализации многозначного ветвления программы с использованием ко" 15 манды безусловной передачи управления (1 ИР).Микропроцессорная система для программного управления технологическими процессами содержит блок 1 управления, содержащий вход 1.1, являющийся входом "Захват 1 микропроцессорной системы, вход 1.2, являющийся входом Запрос прерывания 1 микропроцессорной системы, выходы .3, являю щиеся адресной шиной системы, йходы,.выходы 1.4, являющиеся входами-выходами Данных блока 1 управления выходы 1.5, являющиеся выходами управления блока 1 управления, тактовый ге нератор 2, содержащии входы 2 2,2, являющиеся входами кварцевого резонатора, вход 2,3, являющийся входом "Сброс" системы, вход 2.4, являющийся входом 31 готовность 1 системы, Вьеходы 2.5, 2.8, вход 2.9, выход 2,10, системный контроллер 3, содержащий ВхОДы-ВыхОДы Зеу,яВляющеЕеся шиной данньгс системы, и Выходы 3,2, являющиеся шиной управления системы, де- . 0 шифратор 4 адреса памяти, содержащий выходы 4.1, 4,2, блок 5 оперативной памяти, блок 6 постоянной памяти, шинный формирователь 7 памяти, дешиф- ратоее 8 адресов устройств ВВода-вьево да, содержащий выходы 8,1-8.3, шинные формирователи 9 ввода-вывода, содержащие входы 9,1, являющиеся информационными входами микропроцессорной системы, выходы 9.2, являющиеся информационными выходами микропроцессорной системы, первый 10, второй 11 и третий 12 элементы ИЛИ, первый 13 и второй 14 шинные формирователи, третий шинный формирователь 15; содержащий вход 15.1, являющийся информаци 55 онным входом логических условий микропроцессорной системы, триггер 6, регистр 17, элемент 18 сравнения, содержащий выход 18.1, первый 19 и второй 20 элементы И, третий элемент И 21, содержащий выход 21,1, и четвертый элемент И 22.Первый 2.1 и второй 2.2 входы тактового генератора 2 подключены к кварцевому резонатору, третий 2.3 и четвертый 2.4 входы тактового генератора 2 являются входами "Сброс", и "Го" ровность" микропроцессорной системы соответственно, пятый 2.9 вход тактового генератора 2 подключен к выходу синхронизации блока 1 управления, перпервый 2.5 1 е второй 2.6 выходы тактоВого генератора 2 подключены к первому и второму тактовым входам блока 1 управления, третий 2.7 и четвертый 2.8 выходы тактового генератора 2 подключены к входам "Сброс" и "Готовность" блока 1 управления соответственно, пятый 1,1 и шестой 1,2 входы блока 1 управления являются входами "Захват" и "Запрос прерывания" микропроцессорной системы, пятый 2.10 выхоц тактового генератора 2 подключен к входу синхронизации системного контроллера 3, адресные 1.3 выходы блока 1 управления являются шиной адреса микропроцессорной системы, входы-выходы 1.4 данных блока 1 управления и выходы 1.5 управления подключены к входам-выходам данных и входам управления системного контроллера 3 соотВетственно, входы-выходы 3.1 данных системного контроллера 3 являются шиной данных микропроцессорной системы а выходы 3.2 управления системного контроллера являются шиной управления микропроцессорной системы, информационные входы дешифратора 4 адреса памяти подключены к шине 1.3 адреса микропроцессорной системы, а перВый вход разрешения дешифратора 4 адреса памяти подключен к выходу первого элемента ИЛИ 10, первый и второй входы которого подключены к разрядам шины 3,2 управления "Чтение из памяти", "Запись в память" соответственно, первый выход 4.1 дешифратора 4 адреса памяти подключен к первому входу разрешения блока 6 постоянной памяти и первому входу второго элемента ИЛИ 11, второй выход 4,2 дешифратора 4 адреса памяти подключен к первому входу разрешения блока 5 оперативной памяти и к второму входу второго элемента ИЛИ 11, второй вход разрешения блока 6 постоянной памятии первый вход разрешения шинного формирователя 7 памяти подключены к . разряду шины 3.2 управления "Прием", второй вход разрешения шинного формирователя 7 памяти подключен к выхо. ду второго элемента ИЛИ 11, входы-выходы данных шинного формирователя 7 памяти подключены к шине 3. данных микропроцессорной системы, выходы данных шинного формирователя 7 памяти подключены к входам данных блока 5 оперативной памяти, а входы данных шинного формирователя 7 памяти подключенык выходам данных блока 6 по, стоянной памяти и блока 5 оперативной памяти, адресные входы блока оперативной и блока постоянной памяти подключены к шине 1.3 адреса микропроцессорной системы, вход записи оперативной памяти подключен к разряду шины 3,2 управления "Запись в память", информационные входы дешифратора 8 адресов устройств ввода-вывода подключены к шине 1.3 адреса микропроцессорной системы, а первый и , второй входы разрешения дешифратора 8 адресов устройств ввода-вывода подключены к выходу третьего элемента ИЛИ 12, первый и второй входы которого подключены к разрядам шины 3,2 управления "Ввод из устройства ввода", "Вывод в устройство вывода" соответственно, первая группа выходов 8,1 дешифратора 8 адресов устройств ввода-вывода 8 подключена к первым вхо- даМ разрешения шинных формирователей 9 ввода-вывода, вторые входы разрешения которых подключены к разряду шины 3.2 управления "Ввод из устройства ввода", входы 9,1 шинных формирователей 9 ввода-вывода являются информационными входами микропроцессорной системы, выходы 9.2 шинных формирователей 9 ввода-вывода являются информационными выходами микропроцессорной системы, а входы-выходы шинных формирователей 9 ввода-вывода подключены к шине 3.1 данных микропроцессорной системы, входы-выходы первого 18, второго 14 и третьего 15 шинных формирователей подключены к шине 3.1 данных микропроцессорной системы, первый и второй входы разрешения первого шинного формирователя 13 подключены к второму выходу 8.2 дешифратора 8 адресов устройств ввода-вывода, первый выход первого шинного формирователя 13 подключен к информационномувторому входу разрешения дешифратора 4 адреса памяти, первый вход четвертого элемента И 22 подключен к разряду шины 3,2 управления "Чтение памяти , а выход четвертого элементаИ 22 подключен к первому и второмувходам разрешения третьего шинногоформирователя 15, входы которого подключены к внешним сигналам логических условий 15 1 40 45 Микропроцессор предназначен для выполнения. программы, т,е. последовательности команд, используемой для реализации алгоритма управления, для управления системой с шинной организацией. Микропроцессор воспринимаетвнешние тактовые сигналы и внешние сигналы управления и генерирует сигналы адреса 1.3, данных 1.4, а также сигналы управления 1.5. Блок 1 управ 50 55 входу триггера 16, вход синхронизациикоторого подключен к выходу первогоэлемента И 19, а вход сброса - к системному сбросу 2.3, первый вход элемента И 19 подключен к второму выходу8.2 дешифратора 8 адресов устройствввода-вывода, а второй вход подключенк разряду шины 3,2 управления "Выводв устройство вывода", первый и второйвходы разрешения второго шинного формирователя 14 подключены к третьемувыходу 8,3 дешифратора 8 адресов устройства ввода-вывода, выходы второгошинного формирователя 14 подключенык информационным входам регистра 17,вход синхронизации которого подключенк выходу второго элемента И 20, первый вход которого подключен к третьему выходу 8.3 дешифратора 8 адресовустройств ввода-вывода, а второй вход. которого подключен к разряду шины 3.2управления "Вывод в устройство вывода", вход обнуления регистра 17 под ключен к системному сбросу 2.3, а первая группа входов элемента 18 сравнения подключена к шине 1.3 адресамикропроцессорной системы, а втораягруппа входов элемента 8 Чравнения З 0 подключена к выходам регистра 17, выход элемента 18.1 сравнения подключенк второму входу третьего элементаИ 21, первый вход которого подключенк выходу триггера 16, а третий входкоторого подключен к разряду шины 3,2 3511управления Прием", выход третьегоэлемента И 21,1 подключен к второмувходу четвертого элемента И 22 и к,17 22 15 1 о 29,30,31,. 8,7,3, 2135,1,40,37,38,39,36 омер микрохемыКР 580 ИК 80 А системного строба 2.О, по синхроимпульсу 2,9, поступающему с блока 1Буправления. Он может быть реализован,например, на стандартной интегральной микросхеме КР 580 ГФ 24,Соатветствие входов-выходов блока2 и микросхемы КР 580 Гф 24 может бытьпредставлено табл. 2,а б л и ц а а 2. 2.2 211 10 Системный контроллер 3 предназначен для увеличения нагрузочной способности шины 3,1 данных и организации двунаправленной передачи данных, для фиксации слова управления блока 1 управления, поступающего по шине данных в момент, поступления системного строба 2,10 с тактового генератора 2, и формирования в соответствие б 0 со словом управления и сигналами управления 1,5 блока 1 управления шины 3.2 управления микропроцессорной системы для каждого машинного цикла.Шинные формирователи 7, 9, 13, 14, 15 предназначены для увеличения нагрузочкой способности шины 3,1 данных микропроцессорной системы и для организации двунаправленной передачи ления может быть реализован, например, на стандартной интЕгральной микросхеме КР 580 ИК 80 А,Номер входа.1 1.2 1.3выхода блока ножки 13 , 14 2,5,26,27, 10 Тактовый генератор 2 предназначен . для формирования двух. высоковольтных (12 В) неперекрывающихся последовательностей тактовых импульсов 2,5, 2.6, формирования управляющих сигналов сброса 2.7 и готовности 2,8 по внешним сигналам микропроцессорной системы 2,3, 2.4 и для формирования Номер ножки микро 1схемы КР 580 Гф 24 Соответствие входов-выходов блока 1 и микросхемы КР 580 ИК 80 А может быть представлено табл. 1. 2.5 2.6 2.7. 2.8 2,9 данных по шине,3,1 данных к блокам памяти или из блоков памяти к внешним устройствам или из внешних уст.ройств в зависимости от управляющих сигналов Е 1 и Е 2, При отсутствии управляющих сигналов выходы шинных формирователей находятся в высокоимпе-. дансном состоянии, т,е. отключены от шины данных.Шинный формирователь 7 предназначен для увеличения нагрузочкой способности шины 3, данных и для нодключения выходов блока 5 оперативной памяти или блока 6 постоянной памяти к шине 3.1 данных в режиме чтения, для подключения входов данных блока 5 оперативной памяти к шине 3.1 данных в режиме записи.4186 35 Шинные формирователи 9 ввода-вывода предназначены для увеличения нагрузочной способности шины 3.1 данныхи для подключения к шине 3.1 данныхинформационных входов.9, в режиме.ввода из устройства ввода, для подклю. чения шины 3.1 данных к информацион-,ным выходам 9.2 в режиме вывода в устройство вывода. 10Шинный Формирователь 13 предназначен для .увеличения нагрузочной способности .разряда шины 3,1 данных и дляприема программирующего бита в режимевывода в устройство вывода. 15Шинный формирователь .14 предназначен для увеличения нагрузочной способности шины 3,1 данных и приема информации об адресе точки многозначноговетвления программы в режиме вывода в 20устройство вывода.Шинный формирователь 15 предназначен для увеличения нагрузочкой способности шины 3.1 данных и подключенияк ней сигналов внешних логических 25условий 15,1 в режиме чтения памяти.Дешифратор 4 адреса памяти предназначен для дешифрации адреса, вы 1ставленного на шине 1.3 адреса микропроцессорной системы, и выработки сиг налов подключения (выборки кристалла)либо блока 5 оперативной памяти, либоблока .6 постоянной памяти в том случае, если на шине 3,2 управления микропроцессорной системы выставленысигналы чтения памяти или записи впамять. В этом случае имеется активный уровень сигнала на входе Е 1,Дешифратор 4 адреса памяти предназначен также для блокировки памяти в 40точке многозначного ветвления программы. В этом случае имеется активныйуровень сигнала на входе Е 2 дешифратора адреса памяти.Блок 5 оперативной памяти предна- .45эначен для записи данных, поступающихиз микропроцессора, и хранения ихтолько во время работы микропроцессорной системы. Данные записываютсяи хранятся в ячейках памяти, которые 50выбираются в соответствии с их адресом по сигналам разрешения Е - выборка кристалла,МК - запись.Блок 5 оперативной памяти можетбыть реализован, например, на стан дартных интегральных микросхемах 541. РУ 2.Блок 6 постоянной памяти предназначен для хранения неразрушаемых данных 53 8и считывания их в блок 1 управления всоответствии с адресными сигналамипри наличии разрешающих сигналов Е 1,Е 2. Блок 6 постоянной памяти можетбыть реализован, например, на стандартных интегральных микросхемах 556.РТ 4,Дешифратор 8 адресов устройствввода-вывода предназначен для дешифрации адресов устройств ввода-выводапри наличии сигнала разрешения, который поступает на входы Е 1, Е 2 в томслучае, если на шине 3.2 управлениявыставлен сигнал вывода в устройствовывода либо. сигнал ввода в устройство ввода.Дешифратор 8 адресов устройств ввода-вывода в зависимости отадреса формирует сигналы подключения шинныхформирователей устройств ввода-вывода8.1, подключения шинного формирователя 13 - сигнал 8,2, сигнал подключения шинного формирователя 14 - сигнал8.3.Первый элемент ИЛИ 10 предназначендля формирования разрешающего сигнала .Е дешифратора 4 адреса памяти по наличию на шине 3.2 управления одногоиз сигналов Чтение памяти Записьв память", Второй элемент ИЛИ 11 предназначен для Формирования разрешающего сигнала Е 2 шинного формирователяпамяти по наличию на выходах дешифратора 4 адреса памяти одного из сигналов 4.1, 4.2, т.етогда, когда идетобращение блока управления либо кблоку 6 постоянной, либо к блоку 5оперативной памяти. Третий элементИЛИ 2 предназначен для формированияразрешающего сигнала Е 1, Е 2 для де- .шифратора 8 адресов устройств вводавывода по наличию на шине 3.2 управления одного из сигналов "Вывод в.устройство вывода", "Ввод в устройство ввода",Триггер 16 предназначен для приема с первого выхода шинного Формирователя 13 и хранения. программирующего бита для разрешения дисциплинымногоэначного ветвления программы(при установке триггера в состояниелогической "1"). Триггер 16 можетбыть реализован, например, на стандартной интегральной микросхеме 155ТМ 2. Регистр 17 предназначен для приемаи хранения программирующего сигнала,.65310щий сначала на вход 2,4 тактового генератора 2. Управление процессами обмена информацией в микропроцессорнойсистеме осуществляет системный контроллер 3, который принимает и дешифрирует слово состояния блока управления 1, поступающее по шине 1.4 данныхв первом такте каждого машинного цикла по сигналу с выхода 2,10 тактовогогенератора 2, который, в свою очередьформируется по сигналу синхронизацииблоха 1 управления, поступающему навход 2.9 тактового генератора 2.Микропроцессорная система можетработать в режимах прямого доступав память и прерывания при подаче соответствующих сигналов на входы .1и 1.2 (фиг. 1) блока управления ивведении дополнительного оборудования, однако в предлагаемой микропроцессорной системе эти режимы не используются,Выходные сигналы адреса блокауправления поступают на адресную шину 1.3 микропроцессорной системы.Системный контроллер 3 принимает также выходные сигналы управления 1.5 ипо слову состояния блока 1 управленияи сигналам управления 1.5 Формируетшину 3.2 управления микропроцессорной системы. Кроме того, системныйконтроллер 3 обеспечивает двунаправленную передачу данных по шине 1.4данных и формирует шину 3.1 данныхмикропроцессорной системы,Блок управления (фиг. 1) считывает и выполняет программу, записаннуюв блокипостоянной 6 или оперативной5 памяти. На дешифратор 4 адреса па"мяти поступает адресная информация с.шины 1,3 адреса и, если на ней уста";.новлен адрес памяти, а на шине 3.2управления имеются активные уровнисигналов Чтение из памяти", Записьв память", на выходе дешифратора 4.адреса памяти формируется либо сигнал4,1 подключения блока 6 постояннойпамяти если на шине адреса 1.3 адресблока 6 постоянной памяти, либо сигнал 1, 2 подключения блока 5 оперативной памяти, если на шине 1.3 адреса адрес блока 5 оперативной памяти.Выходы дешифратора 4 адреса памяти активизируются при наличии на шине1.3 адреса адреса памяти, при наличииразрешающего сигналас выхода первогоэлемента "ИЛИ" 10, который формируется, если на шине 3.2 управления име 418поступающего с шинного формирователя)определяющего точку многозначного вет"вления программы.Элемент 18 сравнения предназначендля формирования сигнала совпадения5информации, выставленной на шине 1.3адреса, и информации, хранящейся врегистре 7, т.е, для определенияточки многозначного ветвления програм мы,Первый элемент И 19 предназначендля Формирования сигнала синхронизации триггера 16 при совпадении сигнала с выхода 8.2 дешифратора 8 адресов устройств ввода-вывода и сигнала"Вывод в устройство вывода" на шине3.2 управления. Второй элемент И 20предназначен для формирования сигнала синхронизации регистра 17 при совпадении сигнала с. выхода 8.3 дешифра"тора 8 адресов .ввода-вывода и сигнала"Вывод в устройство вывода" на шине3.2 управления. Третий элемент И 21предназначен для формирования сигнала блокировки дешифратора 4 адресапамяти при совпадении сигнала 18.1 свыхода элемента 18 сравнения, сигналалогической единицы с выхода триггера,16 и сигнала "Прием" с шины 3.2 управ ления. Четвертый элемент И 22 предназначен для формирования сигнала подключения внешних логических условий15.1 к шине данных при совпадениисигнала 21.1 с выхода третьего элемента И и сигнала Чтение памяти с ши 1 135ны управления.Рассмотрим работу предлагаемоймикропроцессорной системы.Микропроцессорная система можетработать в двух режимах: обычный режим, режим многозначного ветвленияпрограммы,В обычном режиме работы тактовыйгенератор 2 Формирует на своих выходах 2,5 и 2.6 (фиг. 1, 2) тактовыепоследовательности, которые синхронизируют внутренние процессы в блокеуправления. Стабильность тактовогогенератора 2 обеспечивается подключе 50нием к его входам 2.1 и 2.2 кварцевого резонатора. Блок 1 управления генерирует выходные сигналы после сигнала "Сброс", который поступает навход 2.3 тактового генератора 2 и с55. выхода 2.7 тактового генератора 2 навход 2.7 блока 1 управления, если навходе 2.8 блока управления 1 установлен сигнал логической "1", поступаю4 8653 2ются либо активный уровень сигнала"Чтение из памяти", либо активныйуровень сигнала "Запись в память" ипри отсутствии запрещающего сигнала21.1.Сигналы 4.1 и 4.2 поступают напервые входы разрешения блоков постоянной 6 или оперативной 5 памяти.Второй вход разрешения блока 6 постоянной памяти активизируется сигналом"Прием" шины 32 управления микропроцессорной системы и, если выбран адрес блока 6 постоянной памяти, идетцикл ".Чтение из памяти", что сопровождается сигналом "Прием", то выходыблока 6 постоянной памяти подключаются через шинный формирователь 7 памяти к шине 3.1 данных микропроцессорной системы. При этом шинный формирователь 7 памяти переводится в режимвыдачи информации на шину 3.1 данныхпо первому входу разрешения сигналом"Прием" шины 3.2 управления, а повторомувходу разрешения - сигналом, 2 Бс выхода второгоэлемента ИЛИ 11, который формируется в случае, если идетобращение к блокам оперативной 5 илипостоянной 6 памяти, т.е.активизируется выход 4;1 или 4,2 дешифратора 4 30памяти. Чтение блока 5 оперативнойпамяти происходит аналогично чтениюблока 6 постоянной памяти, причем выходы данных блока 5 оперативной памяти и выходы данных блока 6 постоянной Зпамяти соединены по схеме "МОНТАЖНОЕИПИ". Запись в блок 5 оперативнойпамяти происходит при активизации выхода 4.2 дешифратора 4 адреса памятии при активизации второго разрешающеговхода блока 5 оперативной памяти,при этом шинный формирователь 7 памяти по первому разрешающему входу устанавливается в режим ввода с шины3.1 данных,45Обращение к устройствам ввода-вывода происходит в том случае, когдаблок 1 управления выставляет на шине1.3 адреса адрес устройства ввода-вывода при одновременной активизации В 0на шине 3.2 управления сигнала "Вводиз устройства ввод" либо "Вывод вустройство вывода". При этом активизируются первый и второй разрешающиевходы дешифратора 8 адресов устройствввода-вывода сигналом с выхода третьего элемента ИЛИ 12, на первый и второй входы которого поступают сигналышины управления "Ввод из устройства ввода", "Вывод в устройство вывода" соответственно, Кроме того, активизируются первый вход разрешения одного из шинных формирователей 9 устройства ввода-вывода одним из сигналов с первой группы выходов 8.1 дешифратораадресов устройств ввода-вывода в за- висимости от номера устройства ввода- вывода, к которому происходит обращение. Направление передачи данных определяется вторыми разрешающими входами шинных формирователей 9 устройств ввода-вывода, на которые поступит сигнал шины 3,2 управления "Ввод из устройства ввода". При этом в блоке 1 управления либо вводятся внешние информационные сигналы 9,1 по входам шинных формирователей 9 устройств ввода-вывода, либо выводится информация на внешние информационные выходы 9.2 по выходам шинных формирователей 9 устройств ввода-вывода,В режиме многозначного ветвления программы микропроцессорная система работает следующим образом.Вначале, при инициализации микропроцессорной системы производится программная настройка. При этом блок 1 управления обращается к триггеру 16, как к устройству вывода, т.е. выставляет на шине 1,3 адреса его адрес, второй выход 8.2 дешифратора 8 адресов устройств ввода-вывода акти-. визирует первый и второй разрешающие входы первого шинного формирователя 13 и бит информации с шины 3,1 данных микропроцессорной системы поступает на информационный вход триггера 16, который устанавливается го синхросигналу, поступающему с выхода первого элемента И 19, выход которого активизируется в случае, если идет обращение к триггеру 16 и активизирован сигнал "Вывод в устройство вывода" шины 3.2 управления. Предварительное обнуление триггера 16 производится сигналом сброса 2.2. Затем регистр 17, как в устройство вывода, выводится информация, определяющая точку многозначного ветвления программы. При этом второй шинный формирователь 14 по первому и второму разрешающим входам сигналом с третьего выхода 8.3 дешифратора 8 адресов устройств ввода-вывода подключается к шине 3.1 данных врежиме вывода в.устройство вывода,и информационные входы регистра 17 подключаются к шине 3.1 данныхмикропроцессорной системы. Запись инФормации в регистр 7 происходит приактивизации сигнала на выходе второгоЭлемента И 20, т,е, на вход синхрони- бзации регистра 17 поступает сигнал с. случае, если на шине 1.3 адреса устайовлен адрес регистра 17 и активизирован сигнал. "Вьвод в устройство вывода" шины 3.2 управления, который 1 Оподключен к второму входу второгоЭлемента И 20, первый вход которогойодключен к третьему выходу 8.3 дешифратора 8 адресов устройства вводаВывода а второй вход подключен к 15разряду шины 3.2 управления "Выводв устройство вьвода". Предварительноеобнуление регистра 17 может производиться сигналом сброса 2,3,Таким образом, предварительная 20настройка микропроцессорной системыдля режима многозначного ветвленияйрограммы заключается в установке1триггера 16, выходной сигнал которогоразрешает проведение режима многоЗначного ветвления программы и в записи в регистр 17 адреса точки многозначного ветвления программы.Точку многозначного ветвления программы определяет элемент 18 сравнения, выход 18.1 (фиг. 1, 2) активизируется при совпадении адреса, выставленного на шине 1,3 адреса (Фиг. 1, 2),и адреса, записанного в регистр 17,При втом если режим многозначноговетвления программы разрешен (установлен триггер 16), на шине 3.2 управления,активизирован сигнал "Прием", то активизируется выход 21,1(фиг. 1, 2) третьего элемента И 21, 4 Окоторый отключает дешифратор 4 адресапамяти по второму инверсному разрешающему (запрещающему) входу, и шинный формирователь 7 памяти переводится в высокоимпедансное состояние посвоим входам-выходам, Выход четвертого элемента, И 22, первый вход которого активизируется сигналом шины3.2 управления "Чтение памяти", авторой вход активизируется сигналом цс выхода 21,1 третьего элемента И 21,переводит третий шинный Формирователь15 по первому и второму разрешающимвходам в режим выдачи информации нашину 3.1 данных. Поэтому внешние ло-,гические условия 15,1 поступают на шишину 3.1 данных микропроцессорной системы. Внешние логические условия5,1 таким образом воспринимаются бло ввод логических условий;; сдвиг влево содержимогоАЗпереход на метку М 1, еслиС =сдвиг влево содержимого А;сдвиг влево содержимогоА;переход на метку МЗ, еслиС = 10х = 1 х = 0 М 2е х, = О х = 1;МЗх= 1 х 0 щПо времени такая операция многозначной передачи управления занимает 38 тактов работы микропроцессорной системы, причем время передачи управблоком управления как один из байтовкоманды (второй байт на фиг. 2). Поэтому осуществляется многозначноеветвление программы в зависимости отнабора логических условий 15,1(фиг. 2),т.е. второй байт адреса перехода трехбайткой команды безусловной передачи управления (1 МР) определяется самими внешними логическимиусловиями 15.1, поэтому адрес перехода является многозначным, зависящимнепосредственно от внешних логическихусловий 15,1,Рассмотрим пример реализации предлагаемой микропроцессорной системыдля микропроцессора КР 580 ИК 80 А,Необходимо обеспечить многозначную передачу управления в микропроцессорной системе в зависимости отвнешних сигналов логических условийх х, в процессе выполнения некоторой подпрограммы Р 1 А (т.е. обеспечить переход на одну из четырех метокМО, И 1, М 2, МЗ).Используем двухальтернативные команды перехода по переполнению 1 С,Порт ввода 167.1514186ления увеличивается при увеличении разрядности внешних сигналов логических условий и увеличении количества обращений к подпрограмме Р 1 А и определяется соотношением:Т=К И +2 е),где Т - общее время передачи управ 10ления;и - разрядность внешних сигналовлогических условий;1 - время ввода внешних сигналов15логических условий;й - суммарное времй выполнения1команд сдвига и перехода попереполнению;,- количество обращений к под 20программе,Используем команду РСН Ы. Порт ввода ф 7. Разрядность логических условий 48:РЫА е25РУБНН ; сохранить содержимое Н, Ь;1 МРОКТФ 7; ввод логических условий;МО 7 Н, А ; загрузка регистра Н;МЧ 1 Ь, Ф ; обнуление регистра Ь;РСНЬпереход на метки МО+М 2РОРН ; восстановление Н, И;МО: 53 16ляется временем выполнения команды безусловной передачи управления (1 МР). Причем время настройки для дисциплины реализации многоэначного ветвления программы не входит в общее время выполнения подпрограммы РМА и производится в процессе предварительной иницииализации микропроцессорной системы;ЖБТК:МЧС 8 ф ввод в аккумулятор числа8 Ф;011 ТРОКТф 5; вйвод в триггер;МЧ 1 ЭР ; ввод в аккумулятор числаРР;ОУТРОКТФ 6; вывод в регистр 17;РоА1 МР Щ; ЮУ+ ФфФ МО:М 1:М 2:МЗ:1 Здесь ОР-адрес второго байта команды 1 МР. Таким образом, переход.наодну из меток МО : МЗ в процессе выполнения каждого обращения к подпрограмме РА будет осуществляться эавремя выполнения команды безусловного перехода, т.е. за 10 тактов. Вре мя предварительной настройки, осуществляемой при инициировании микропроцессорной системы, не входящее вовремя выполнения подпрограммы РА,34 такта.Передача управления происходит наметке ЭР, т.е. в точке программы,когда содержимое программного счетчика или адрес, выставленный на шине1.3 адреса (фиг. 1, 2) было равно аДресу второго байта команды 1 МР в подпрограмме РМА. В этом случае адрес нашине 1.3 адреса равен адресу,.записанному в регистре 17 (фиг. 1, 2).Посигналу "Прием" шины 3,2 управления 3540 где Т - общее время передачи управления;. ды РСН Ы = 48 тактам.При использовании предлагаемой микропроцессорной системы время многозначной передачи управления опредеПо времени зто занимает 48 тактов работы микропроцессорной системы, припричем общее время передачи управления увеличивается при увеличении количества обращений к подпрограмме и 45 определяется соотношением:

СмотретьЗаявка

4187151, 28.01.1987

ПРЕДПРИЯТИЕ ПЯ Г-4651

ПУГАЧ ЕВГЕНИЙ ВАСИЛЬЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, УЛИТЕНКО ВАЛЕНТИН ПАВЛОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТЮРИН СЕРГЕЙ ФЕОФЕНТОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G05B 19/414, G05B 19/418

Метки: микропроцессорная, программного, процессами, технологическими

Опубликовано: 23.08.1988

Код ссылки

<a href="https://patents.su/12-1418653-mikroprocessornaya-sistema-dlya-programmnogo-upravleniya-tekhnologicheskimi-processami.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессорная система для программного управления технологическими процессами</a>

Предыдущий патент: Устройство для программного управления

Следующий патент: Программное временное устройство

Случайный патент: Способ пробивки ряда отверстий