Программно-управляемый цифровой фильтр

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1338006

Авторы: Петрова, Шполянский

Текст

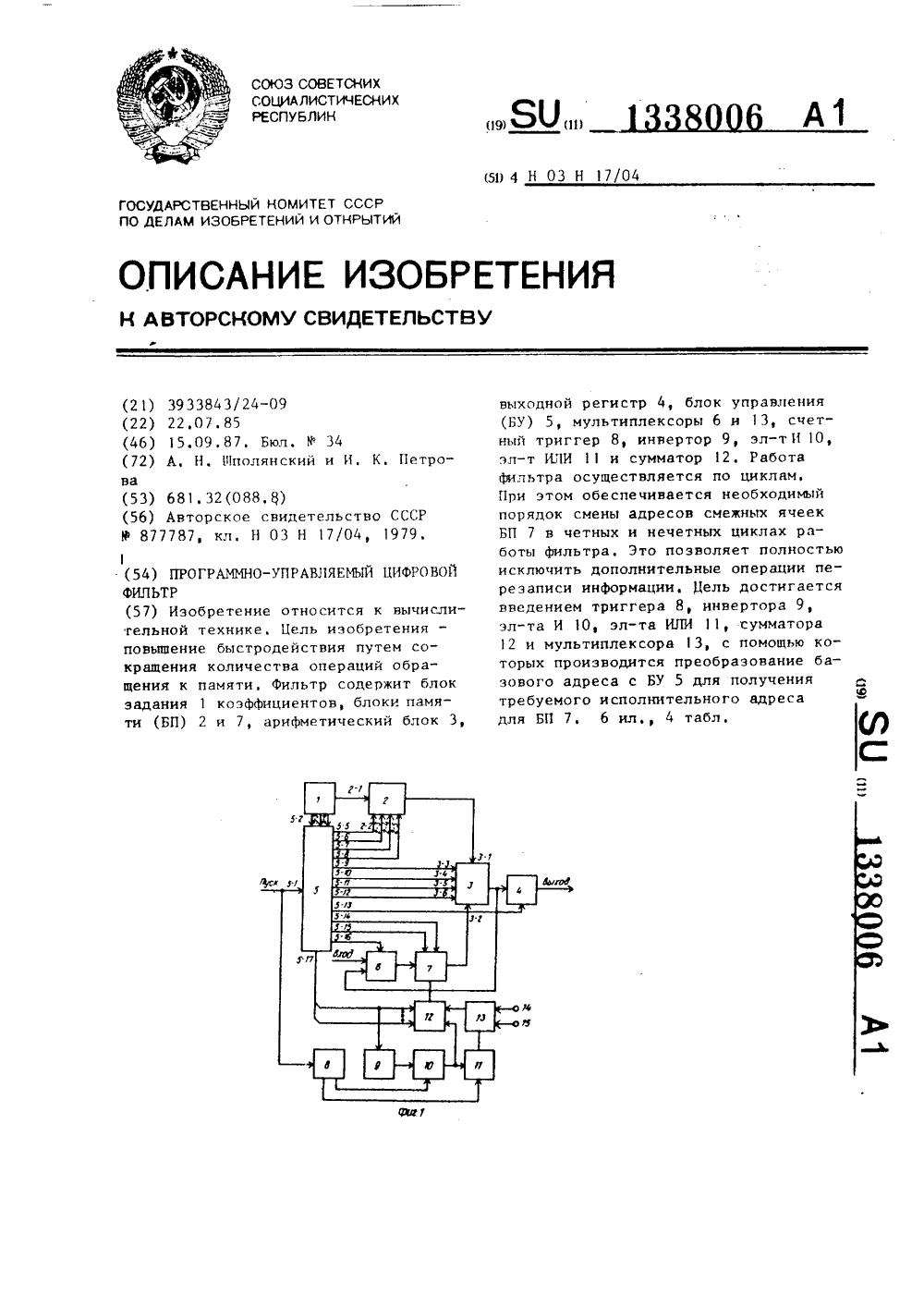

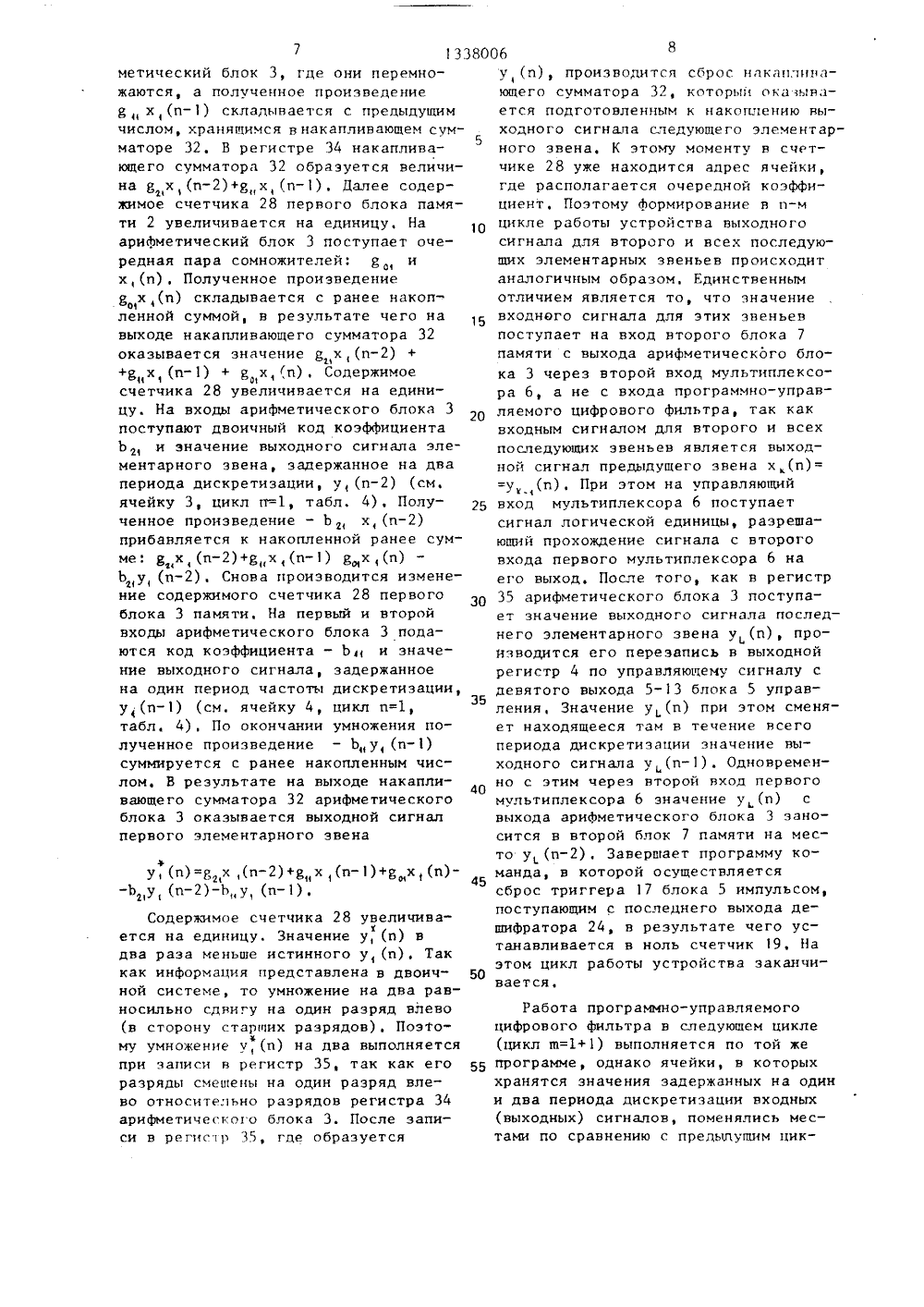

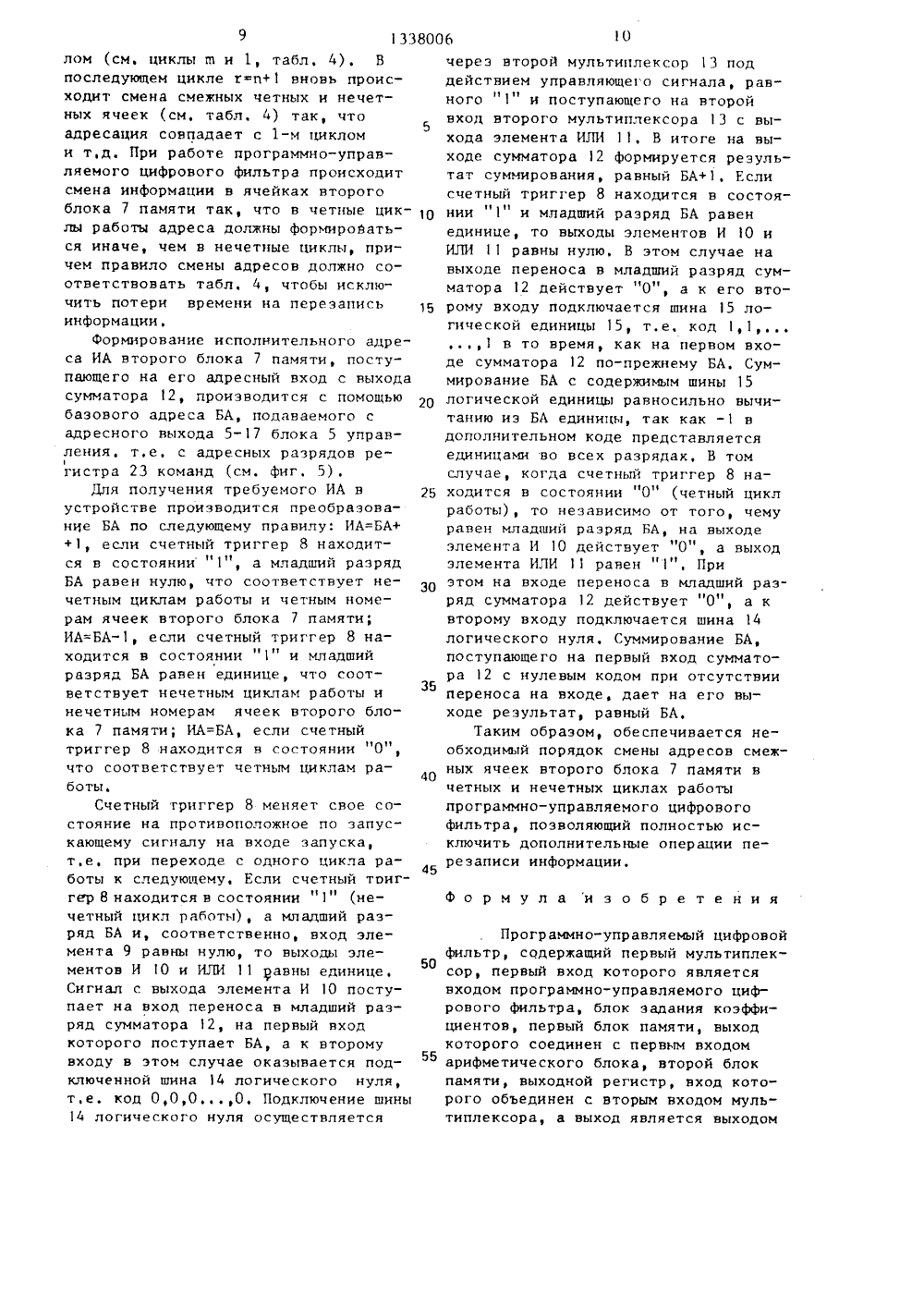

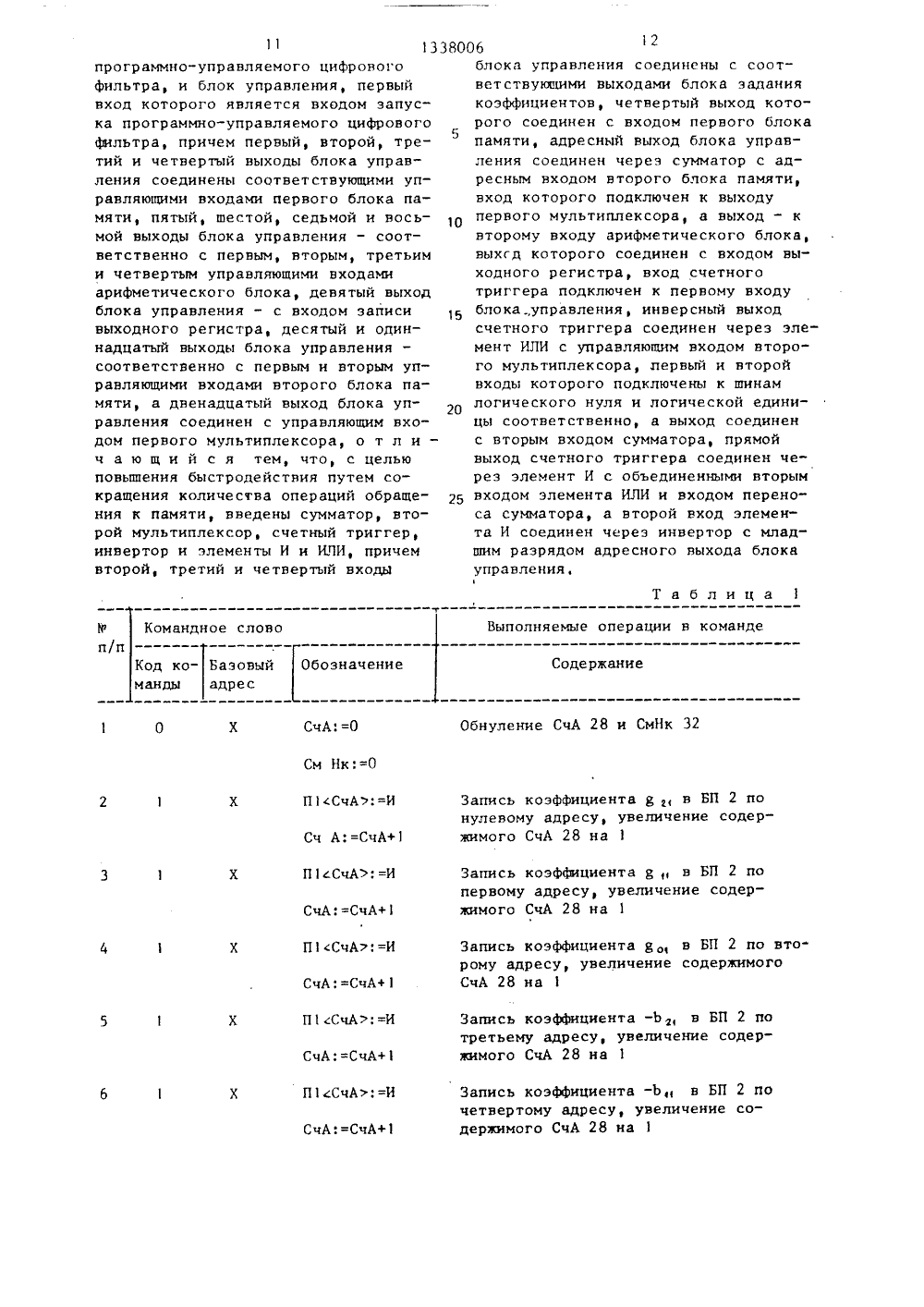

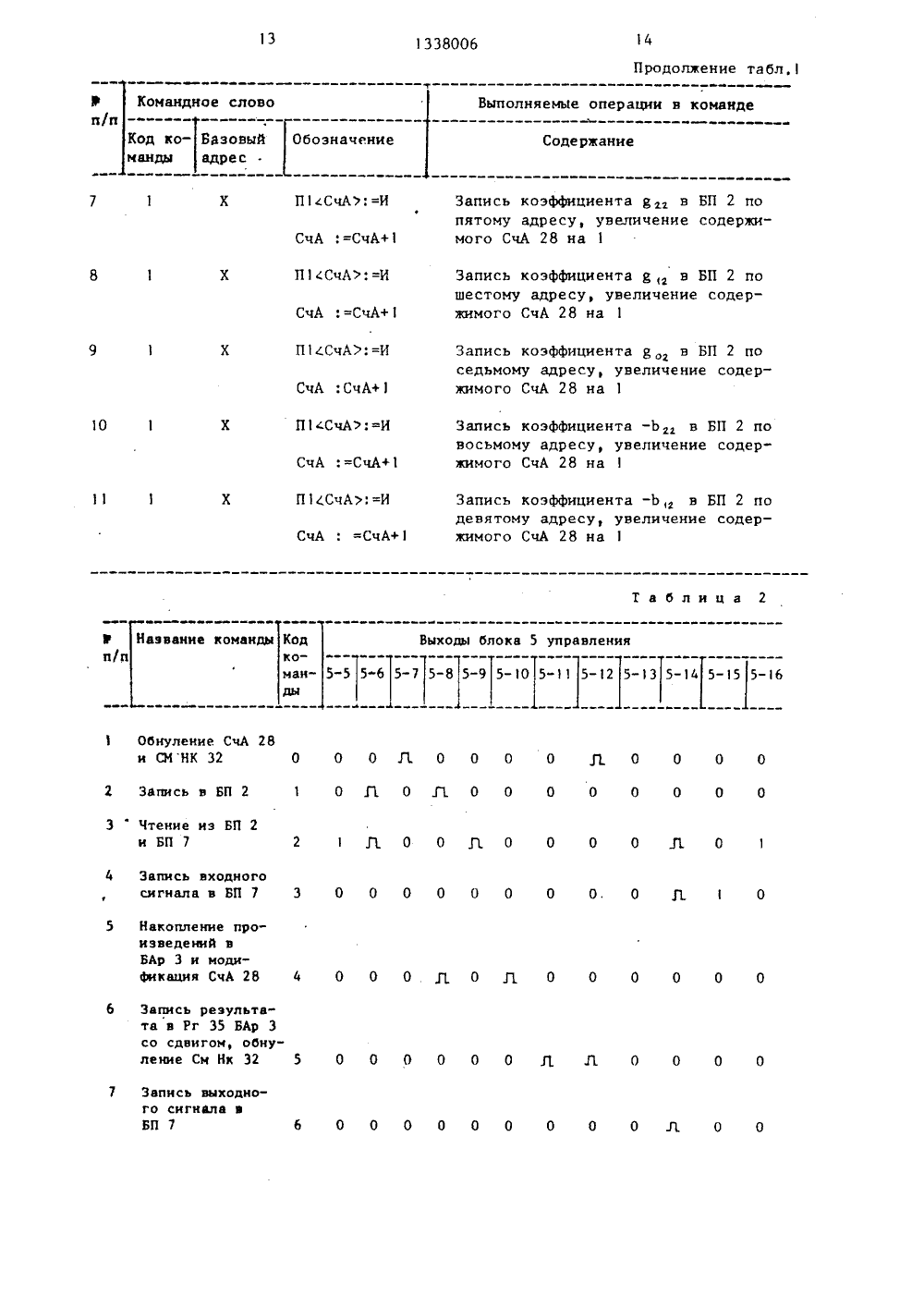

(57) Игельноповьппекращенщениязаданити (БП ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ А ВТОРСКОМУ СВИДЕТЕЛЬСТВУм 681, 32 (088. Ц)Авторское свидетельство С 787, кл, Н 03 Н 17/04, 19 зобретение относится к вычислий технике Цель изобретенияние быстродействия путем соня количества операций обрак памяти, Фильтр содержит блокя 1 коэффициентов блоки памя) 2 и 7, арифметический блок 3 выходной регистр 4, блок управления(БУ) 5, мультиплексоры 6 и 13, счетный триггер 8, инвертор 9, эл-т И 1 О,эл-т ИЛИ 11 и сумматор 12Работафильтра осуществляется по циклам.При этом обеспечивается необходимыйпорядок смены адресов смежных ячеекБП 7 в четных и нечетных циклах работы фильтра. Это позволяет полностьюисключить дополнительные операции перезаписи информации, Цель достигаетсявведением триггера 8, инвертора 9,эл-та И 10, эл-та ИЛИ 11, сумматора12 и мультиплексора 13, с помощью которых производится преобразование базового адреса с БУ 5 для получениятребуемого исполнительного адресадля БП 7. 6 ил., 4 табл(ЯА дв. система Фи/и Выполняемые операции в командеОбозначение Содервание и комментарии Командное слово Код ко- БАманды (дв, сист,Четный Нечетный цикл цикл+К х, (п- )+Вх,(п)-Ьх, (и)-Ьх, (и)Модификация адреса в СчА 28 1Запись у, (и) в Рг 35 са сдвигом и обнуление СмНК 32 Чтение В г иэ БП 2, х,(п) у, (и)из БП 7 и запись РГК 28 н РгВ 30 Запись у (и) в БП 7 на местоу (и) Накопление в СмН 32 Вггх(п)МодиФикация адреса в СчА 28 Чтение В,г иэ БП 2, х,(п) ду,(п) иэ БП 7 и запись в РгК 29 и РгВ 30 Накопление в СмНк 32гг хг(п)+В, х (и)Модификация адреса в СчА 28 Чтение В иэ БП 2, хг(п) у, (и)из БП 7 и запись в РгК 29 и РгВ 30 Накопление в Смнк 328 ггхг(п)+В,г (и)+Бог(п)Модификация адреса в СчА 28 Чтение - Ь г иэ БП 2уг (и)иэ БП 7 и запись в РгК 29 и РгВ 30 Накопление в СмНк 32 В хг(п)+ +Вх г(п)+Бог хг(п)-Ъггх г(п) Модификация адреса в СчА 28 Чтение - Ь, иэ БП 2, у (и)из БП 7 и запись в РгК 29 и РгВЗОНакопление в СмНк 32 уг (и)В ггх г(п 2)+Вг хг(п 1)+Во х г(п)гг Уг п)-Ь,г уг(п)Модификация адреса в СчА 28 Запись у" (и) в Рг 35 со сдвигоми обнуление СмНк 3213380 6 1,оопвене тпО т,мандное слово Выполняемые операции в команде ИА дв. система ный Нечетный Обоэначеине Содержание н коементариикл цикл д ко анды (дв, снст. Выхг=Рлись у (и) и выходнон регнст ВЫХ 4 и БП 7 на место у (и) 01 00 00 2 2 х , 1 А х: =Р г 3 Сброс в БУ 5 Тг 17, выэывающийпрекращение обработки до очередиго эапуска Тг: 27 9 етный цикл п=1 ечетный цикл п=щ 1 ф Четный цикл П 7 БА Содержание ячейки БП 7 БА Содержание ячейки БП 7 БА одержание кчей х,(т 0 х,(щ-)338006 Составитель С, Музычукактор Н, Киштулинец Техред В.Кадар К ктор Л. Вески 1 одписное 42/53ВНИИПИ ак крытиинаб.,4/ 3 3035,тная, 4 жгород роиэводственно-полиграфическое предприятие Государс тделам иэо осква, ЖТираж 901енного комиретений и5, Раушска1 1 33800И зобретение относится к вычислительной технике и может быть использовано в цифровых системах обработкислучайных процессов,5Цель изобретения - повышение быстродействия путем сокращения операцийобращения к памяти.На фиг, 1 приведена структурнаясхема программно-управляемого цифрового фильтра; на фиг, 2 - структурная схема блока управления; на фиг, 3 -структурная схема первого блока памяти; на фиг. 4 - структурная схемаарифметического блока; на фиг. 5структура командного слова; нафиг, 6 - временные диаграммы, поясняющие принцип работы,Программно-управляемый цифровойфильтр (фиг, 1) содержит блок 1 задания коэффициентов, первый блок 2памяти, (БП 2) вход 2- 1 первого блока 2 памяти, первый 2-2, второй 2-3третий 2-4 и четвертый 2-5 управляющие входы первого блока 2 памяти,арифметический блок 3 (БАр 3), первый 3-1 и второй 3-2 входы арифметического блока 3, первый 3-3, второй3-4, третий 3-5 и четвертый 3-6 управляющие входы арифметического блока, выходной регистр 4 (РгВых 4),блок 5 управления (БУ 5), первый 5-1,второй 5-2, третий 5-3 и четвертый5-4 входы блока 5 управления, с первого по двенадцатый выходы (5-5)- 35(5-16) блока 5 управления, адресныйвыход 5-17 блока 5 управления, первый мультиплексор 6 второй блок 7памяти (БП 7), счетный триггер 8, инвертор 9, элемент И 10, элементИЛИ 11, сумматор 12, второй мультиплексор 13, шину 14 логического нуляи шину 15 логической единицы. Блок 5 управления (фиг. 2) содержит элемент И 16, триггер 17 (Тг 17)тгенератор 18 импульсов, счетчик 19адреса, блок 20 памяти микропрограмм, первый 21 и второй 22 мультиплексоры, регистр 23 команд, дешифратор 24, элементы 25 задержки, блоки элементов И 26,Первый блок 2 памяти (фиг, 3) содержит запоминающий блок 27 и счетчик 28 адреса (СчА 28),Арифметический блок 3 (фиг, 4) содержит регистр 29 коэффициентов(РгК 29) регистр 30 выборок (РгВЗО),умножитель 31, накапливающий сумматор 6 232 (См 11 к 12)сумматор 33, первый 34 и второй 35 регистры (Рг 35),Программно-управляемый цифровой фильтр выполнен в соответствии с каскадной формой реализации цифровых рекурсивных фильтров с элементарными звеньями второго порядка. Работа каждого К-го элементарного звена производится по алгоритму, заданному раэностным уравнением Управление последовательностьюработы программно-управляемого цифрового фильтра производится блоком 5управления, представляющим собоймикропрограммный автомат, Микропрограмма работы фильтра хранится в блоке 20, Перед началом фильтрации производится запись коэффициентов фильтра иэ блока 1 задания коэффициентовв первый блок 2 памяти, т,е, исходноепрограммирование фильтра на нужнуюамплитудно-частотную характеристику(АЧХ), При этом на второй вход блока 5 управления из блока 1 заданиякоэффициентов подается потенциальный сигнал логического нуля, запрещающий запуск микропрограммы черезэлемент И 16 и переключающий мультиплексоры 21 и 22 блока 5 в положение при котором информационныйвход регистра 23 команд блока 5окаэывается подключенным к третьемувходу 5-3 блока 5, а тактовый вход -к четвертому входу 5-4 блока 5, После этого начинается выполнение программы записи коэффициентов фильтра впервый блок 2 памяти, Командное слово, установленное в блоке 1 заданиякоэффициентов через первый мультиплексор 21 блока 5 записывается в регистр 23 команд. Запись командногослова производится по тактовому импульсу, поступающему из блока 1 через второй мультиплексор 22 блока 5на тактовый вход регистра 23 команд.Командное слово (см, фиг, 5) состоит из кода и базового адреса,Программа записи коэффициентовдля фильтра четвертого порядка, состоящего иэ двух звеньев второго порядка, приведена в табл. 1,Для записи коэффициентов используются всего два типа команд: коман 133800625 40 да обнуления счетчика 28 адреса первого блока 2 памяти и накапливающегосумматора 32 арифметического блока 3(см. ниже; команда записи коэффициента в запоминающий блок 27 и прибавление единицы в счетчик 28 адресапервого блока 2 памяти,10В табл, 1 приняты следующие обозначения: П 1 сСчА- содержимое ячейкипервого блока 2 памяти, имеющей адрес, определяемый состоянием счетчика 28 адреса; И - число (коэффициентна входе 2-1 блока 2 памяти); Х -1значение безразлично,При записи в запоминающий блок 27первого блока 2 памяти сначала заносятся коэффициенты первого элементарного звена фильтра, затем второго ит.д. Порядок расположения коэффициентов по каждому элементарному звенуследующий: К,К цКок ю ккДля выполнения цифровой фильтрациипоследовательно соединенными элементарными звеньями второго порядка запоминающий блок 27 первого блока 2памяти должен содержать 5 х 1. ячеек,где Е - число каскадно включенныхзвеньев,После записи всех коэффициентовна второй вход 5-2 блока 5 управления из блока 1 подается потенциальный сигнал логической единицы, в результате чего программно-управляемыйцифровой фильтр переходит в режимфильтрации входного сигнала, При этомпервый 21 и второй 22 мультиплексорыблока 5 переключаются в положение,при котором информационный вход регистра 23 команд оказывается подключенным к выходу блока 20, а тактовыйвход - к выходу генератора 18 импульсов блока 5. Одновременно разрешаетсяпрохождение запускаюШих импульсов спервого входа 5-1 блока 5 управленияна триггер 17.При поступлении запускающего импульса триггер 17 переходит в единичное состояние, на входе установки вноль счетчика 19 появления "1", Счетчик 19 начинает счет импульсов генератора 18 (см, 36 на фиг, 6) и начинается выполнение внутренней программы устройства, хранящейся в блоке20 (цикл обработки). Каждой иэ командсоответствует свой набор управляющихсигналов на выходах блока 5 управления, которые определяют необходимую последовательность выполнения операций в программно-управляемом цифровом фильтре, Управляющие сигналы на выходах блока 5 управления Формируются следующим образом, В соответствии с состоянием счетчика 19, на счетный вход которого поступают тактовые импульсы с генератора 18, на выходе блока 20 появляется командное слово, структура которого приведена на фиг, 5, Интервалы времени (для к-го такта), в течении которых адрес-,на выходе счетчика 19 в командное слово на выходе блока 20 остаютсянеизменными, представлены соответственно диаграммами 37 и 38 на Фиг. 6, Командное слово записывается в регистр 23 команд по заднему фронту импульса генератора 18 (см. 39 на фиг. 6). В соответствии с кодом команды на одном или нескольких выходах дешифратора 24 появляется импульс, длительность которого равна длительности команды (см, 40 на фиг. 6). Выходные сигналы дешифратора 24 стробируются задержанными на элементах 25 задержки импульсами генератора 18, После стробирования в блоках элементов И 26 на выходах блока 5 управления появляется один или несколько управляющих импульсов (см, 41,42,43 на фиг, 6), наличие и временная расстановка которых обеспечивают требуемую последовательность выполнения операций в программно-управляемом цифровом фильтре, Временное положение импульса на диаграмме 41 соответствует второму, третьему и десятому выходам блока управления, а временные положения импульсов на диаграммах 42 и 43 - выходам 5-9, 5-10, 5-11 и 5-8, 5-12, 5-13 соответственно, Длительность нестробируемых управляющих сигналов на выходах 5-5, 5-15, 5-16 блока 5 равна длительности импульсов на выходах дешифратора 24 (см, 40 на фиг, 6), Набор необходимых управляюо 1 их сигналов, Формируемых блоком 5 управления для каждого типа команд, приведен в табл, 2, а в табл, 3 приведена программа фильтрации для случая, когда фильтр состоит из двух звеньев второго порядка, В табл, 3 обозначены: Рг К х Рг В - результат перемножения содержимого регистров 29 и 30 арифметического блока 3; Рг 35:=См5 133запись со сдвигом в регистр 35 содержимого накапливающего сумматора32 арифметического блока 3; Па (ИА)содержимое ячейки второго блока 7 памяти, имеющей исполнительный адрес,определяемый состоянием выхода сумматора 12.Для реализации программы в второмблоке 7 памяти каждому элементарномузвену фильтра отведены две ячейки дляхранения значений входных сигналовданного звена, задержанных на дваи один период частоты дискретизации,и две ячейки для хранения аналогичных значений выходного сигнала, Длясчитывания иэ второго блока 7 памятина управляющие входы этого блока должныбыть поданы сигнал логической единицы длительностью в целую команду,устанавливающий режим чтения (одиннадцатый выход 5-15 блока управления 5), и импульс считывания,При выполнении программы фильтрации под действием управляющих сигналов элементы программно-управляемогоцнфрового фильтра работают в следующей последовательности (см. табл. 3).Сначала сбрасываются (обнуляются)счетчик 28 первого блока 2 памяти инакапливающий сумматор 32 арифметического блока 3, после чего начинается формирование первого значенияна выходе первого звена у,(п). Выполняется одновременно (в одной команде) считывание значений коэффициента 8 , и входного сигнала х,(п),задержанного на два периода, из первого 2 и второго 7 блоков памятисоответственно, которые по управляющему импульсу на пятом выходе 5-9блока 5 управления записываются соот.ветственно в регистры 29 и 30 арифметического блока 3, Адрес ячейки,к которой производится обращение,определяется исполнительным адресом(ИА), поступающим на адресный входвторого блока 7 памяти с выхода сумматора 12ИА формируется в зависимости от базового адреса (БА), поступающего на сумматор 12 с адресного выхода 5-17 блока 5 управления,и порядкового номера цикла, в котором выполняется фильтрация входногосигнала,Содержимое ячеек второго блока 7памяти в трех смежных циклах работыпрограммно-управляемого цифрового8006 10 15 20 25 30 35 40 45 50 55 фильтра для первого и второго элементарных звеньев приведено в табл, 4.Для тех ячеек, в которых информация обновляется в течение цикла, показано их содержимое в начале и конце цикла. Так как выходные отсчеты к-го элементарного звена являются входными для (к+1)-го звена, то всего второй блок 7 памяти содержит 2(1,+1) ячеек, На умножителе 31 содержимое регистров 29 и 30 перемножается, образуя величину ях,(п) на его выходе, а значит и на информационном входе накапливающего сумматора 32. Затем производится запись входного сигнала х,(п) в ячейку 1 второго блока 7 памяти, т,е, в ту ячейку, где ранее находилось значение х (и) (см. табл, 4, цикл п=1). Для этого разрешается прохождение входного сигнала х,(п) с первого входа мультиплексора 6 на вход второго блока 7 памяти при наличии логического нуля на управляющем входе мультиплексора 6, поступающем с двенадцатого выхода 5-16 блока 5 управления, На второй управляющий вход второго блока 7 памяти подается сигнал логического нуля, обеспечивающий режим записи, после чего по импульсу, поступающему на первый управляющий вход второго блока 7 памяти происходит занесение информации в ячейку по ИА, сформировавшемуся к этому моменту на адресном входе второго блока 7Далее выходное значение накапливающего сумматора 32 суммируется с его входным значением в сумматоре 33 арифметического блока 3 и по управляющему импульсу, поступающему на второй управляющий вход 3-4 арифметического блока 3 с шестого выхода 5-10 блока 5 управления, полученный результат записывается в регистр 34, Так как регистр 34 был сброшен в первой команде, то на выходе накапливающего сумматора образуется произведение ц ,х (п), К содержимому счетчика 28 прибавляется единица по управляющему импульсу, поступающему с четвертого выхода 5-8 блока 5 управления на четвертый управляющий вход первого блока 2 памяти. Операндами для второго умножения являются двоичный код коэффициентаи и значение входного сигнала х,(п), поступающие из вторых ячеек первого и второго блоков 2 и 7 памяти в ариф38006 55 7 13 метический блок 3, где они перемножаются, а полученное произведениех,(п) складынается с предыдущим числом, хранящимся в накапливающем сумматоре 32, В регистре 34 накапливающего сумматора 32 образуется величина я х,(п)+ях,(п-). Далее содержимое счетчика 28 первого блока памяти 2 увеличивается на единицу, На арифметический блок 3 поступает очередная пара сомножителей:и х,(п), Полученное произведение д х (и) складывается с ранее накополенной суммой, в результате чего на выходе накапливающего сумматора 32 оказывается значение ц,х(п) + +8 вх,(п) + Ц,х,(п), СодеРжимое счетчика 28 увеличивается на единицу. На входы арифметического блока 3 поступают двоичный код коэффициента Ь, и значение выходного сигнала элементарного звена, задержанное на два периода дискретизации, у(п) (см. ячейку 3, цикл п=1, табл. 4). Полученное произведение - Ьх(д) прибанляется к накопленной ранее сумме: д х, (и)+ях(и) яо,х(и) Ь,у, (п), Снова производится изменение содержимого счетчика 28 первого блока 3 памяти, На первый и второй входы арифметического блока 3 подаются код коэффициента - Ь и значение выходного сигнала задержанное на один период частоты дискретизации, у(п) (см. ячейку 4, цикл п=1, табл. 4), По окончании умножения полученное произведение - Ь у,(п) суммируется с ранее накопленным числом. В результате на выходе накапливающего сумматора 32 арифметического блока 3 оказывается выходной сигнал первого элементарного звена у, (и) =Р х (и)+д х (и)+д х, (и)- -Ь,у, (п)-Ьу, (и)Содержимое счетчика 28 увеличивается на единицу. Значение у, (и) в два раза меньше истинного у, (и), Так как информация представлена в двоичной системе, то умножение на два равносильно сдвигу на один разряд влево (в сторону старших разрядов), Поэтому умножение у,(п) на два выполняется при записи в регистр 35, так как его разряды смешены на один разряд влево относительно разрядов регистра 34 арифметического блока 3. После записи в регср 35, где образуется 5 10 15 20 25 30 35 40 45 50 у (и), производится сброс накаплинающего сумматора 32, который окаынается подготовленным к накоплению выходного сигнала следующего элементарного звена. К этому моменту н счетчике 28 уже находится адрес ячейки,где располагается очередной коэффициент, Поэтому Формирование н и-мцикле работы устройства выходногосигнала для второго и всех последующих элементарных звеньев происходитаналогичным образом, Единственнымотличием является то, что значениевходного сигнала для этих звеньевпоступает на вход второго блока 7памяти с выхода арифметического блока 3 через второй вход мультиплексора 6, а не с входа программно-управляемого цифрового фильтра, так каквходным сигналом для второго и всехпоследующих звеньев является выходной сигнал предыдущего звена х,(п)==у,(п), При этом на управляющийвход мультиплексора 6 поступаетсигнал логической единицы, разрешающий прохождение сигнала с второговхода первого мультиплексора 6 наего выход. После того, как н регистр35 арифметического блока 3 поступает значение выходного сигнала последнего элементарного звена у(п), производится его перезапись в выходнойрегистр 4 по управляющему сигналу сденятого выхода 5-13 блока 5 управления, Значение у(п) при этом сменяет находящееся там в течение всегопериода дискретизации значение выходного сигнала у(п), Одновременно с этим через нторой вход первогомультиплексора 6 значение у(п) свыхода арифметического блока 3 заносится в второй блок 7 памяти на место у(п), Занершает программу команда, в которой осущестнляетсясброс триггера 17 блока 5 импульсом,поступающим с последнего выхода дешифратора 24, в результате чего устанавливается в ноль счетчик 19, Наэтом цикл работы устройства заканчивается. Работа программно-управляемого цифрового фильтра в следующем цикле (цикл ш=1+1) выполняется по той же программе, однако ячейки, н которых хранятся значения задержанных на один и два периода дискретизации входных (выходных) сигналов, поменялись местами по сравнению с предыдущим цик 9 33 лом (см. циклы ш и 1 табл, 4). В последующем цикле гд+ вновь происходит смена смежных четных и нечетных ячеек (см. табл, 4) так, что адресация совпадает с 1-м циклом и т,д, При работе программно-управляемого цифрового фильтра происходит смена информации в ячейках второго блока 7 памяти так, что в четные циклы работы адреса должны формироваться иначе, чем в нечетные циклы, причем правило смены адресов должно соответствовать табл, 4, чтобы исключить потери времени на перезапись информации.формирование исполнительного адреса ИА второго блока 7 памяти, поступающего на его адресный вход с выхода сумматора 12, производится с помощью базового адреса БА, подаваемого с адресного выхода 5-17 блока 5 управления, т,е, с адресных разрядов регистра 23 команд (см. фиг, 5)Для получения требуемого ИА в устройстве производится преобразование БА по следующему правилу: ИА=БА+ +1, если счетный триггер 8 находится в состоянии "1", а младший разряд БА равен нулю, что соответствует нечетным циклам работы и четным номерам ячеек второго блока 7 памяти; ИА=БА, если счетный триггер 8 находится в состоянии "1" и младший разряд БА равен единице, что соответствует нечетным циклам работы и нечетным номерам ячеек второго блока 7 памяти; ИА=БА, если счетный триггер 8 находится в состоянии "0", что соответствует четным циклам работы.Счетный триггер 8 меняет свое состояние на противоположное по запускающему сигналу на входе запуска, т,е, при переходе с одного цикла работы к следующему, Если счетный тоиггер 8 находится в состоянии "1" (нечетный цикл работы), а младший разряд БА и, соответственно, вход элемента 9 равны нулю, то выходы элементов И 1 О и ИЛИ 11 главны единице. Сигнал с выхода элемента И 1 О поступает на вход переноса в младший разряд сумматора 12, на первый вход которого поступает БА, а к второму входу в этом случае оказывается подключенной шина 14 логического нуля, те, код 0,0,0,0, Подключение шины 14 логического нуля осуществляетсяО 8006 45 50 55 5 1 О 15 20 25 30 35 40 через второй мультиплексор 13 поддействием управляющего сигнала, равного "1" и поступающего на второй вход второго мультиплексора 13 с выхода элемента ИЛИ 11. В итоге на выходе сумматора 12 формируется результат суммирования, равный БА+1. Еслисчетный триггер 8 находится в состоянии "1" и младший разряд БА равенединице, то выходы элементов И 10 иИЛИ 11 равны нулю. В этом случае навыходе переноса в младший разряд сумматора 12 действует "0", а к его второму входу подключается шина 15 логической единицы 15 т.е, код 1,1,,1 в то время, как на первом входе сумматора 12 по-прежнему БА. Суммирование БА с содержимым шины 15логической единицы равносильно вычитанию из БА единицы, так как - 1 вдополнительном коде представляетсяединицами во всех разрядах, В томслучае, когда счетный триггер 8 находится в состоянии 0 (четный циклработы), то независимо от того, чемуравен младший разряд БА, на выходеэлемента И 10 действует "0", а выходэлемента ИЛИ 11 равен "1", Приэтом на входе переноса в младший разряд сумматора 12 действует "0", а квторому входу подключается шина 14логического нуля, Суммирование БА,поступающего на первый вход сумматора 12 с нулевым кодом при отсутствиипереноса на входе, дает на его выходе результат, равный БА,Таким образом, обеспечивается необходимый порядок смены адресов смежных ячеек второго блока 7 памяти вчетных и нечетных циклах работыпрограммно-управляемого цифровогофильтра, позволяющий полностью исключить дополнительные операции перезаписи информации,Формула изобретения Программно-управляемый цифровой фильтр, содержащий первый мультиплексор, первый вход которого является входом программно-управляемого цифрового фильтра, блок задания коэффициентов, первый блок памяти, выход которого соединен с первым входом арифметического блока, второй блок памяти, выходной регистр, вход которого объединен с вторым входом мультиплексора, а выход является выходом13 380 программно-управляемого цифрового фильтра, и блок управления, первый вход которого является входом запуска программно-управляемого цифрового фильтра, причем первый, второй, тре 5 тий и четвертый выходы блока управления соединены соответствующими управляющими входами первого блока памяти, пятый, шестой, седьмой и восьмой выходы блока управления - соответственно с первым, вторым, третьим и четвертым управляющими входами арифметического блока, девятый выход блока управления - с входом записи выходного регистра, десятый и одиннадцатый выходы блока управления - соответственно с первым и вторым управляющими входами второго блока памяти, а двенадцатый выход блока управления соединен с управляющим входом первого мультиплексора, о т л и - ч а ю щ и й с я тем, что, с целью повышения быстродействия путем сокращения количества операций обращения к памяти, введены сумматор, второй мультиплексор, счетный триггер, инвертор и элементы И и ИЛИ, причем второй, третий и четвертый входы Таблица 1 Командное слово Ми/и Содержание Обнуление СчА 28 и СмНк 32 СчА: =0 См Нк:=0 Запись коэффициента яв БП 2 понулевому адресу, увеличение содержимого СчА 28 на 1 П 1(СчА);=И Сч А:=СчА+1 Запись коэффициента 8, в БП 2 по первому адресу, увеличение содержимого СчА 28 на 1 П 1 СчА): =И СчА:=СчА+ ПсСчА):=И Запись коэффициента я , в БП 2 по второму адресу, увеличение содержимогоСчА 28 на 1 СчА;=СчА+1 Запись коэффициента -Ь, в БП 2 по третьему адресу, увеличение содержимого СчА 28 на 1 П (СчА); =И СчА:=СчА+1 Запись коэффициента -Ь в БП 2 почетвертому адресу, увеличение содержимого СчА 28 на П 1(СчА): =И СчА:=СчА+1 Код ко- Базовый Обозначениеманды адрес 0612блока управления соединены с соответствующими выходами блока задания коэффициентов, четвертый выход которого соединен с входом первого блока памяти, адресный выход блока управления соединен через сумматор с адресным входом второго блока памяти,вход которого подключен к выходупервого мультиплексора, а выход - квторому входу арифметического блока,выход которого соединен с входом выходного регистра, вход счетноготриггера подключен к первому входублока.,управления, инверсный выходсчетного триггера соединен через элемент ИЛИ с управляющим входом второго мультиплексора, первый и второйвходы которого подключены к шинамлогического нуля и логической единицы соответственно, а выход соединенс вторым входом сумматора, прямойвыход счетного триггера соединен через элемент И с объединенными вторымвходом элемента ИЛИ и входом переноса сумматора, а второй вход элемента И соединен через инвертор с младшим разрядом адресного выхода блокауправления,1 Выполняемые операции в команде13 1338006 Продолжение табл,Командное слово 1и/и Код ко- Базовый Обозначениеманды адрес Содержание ПсСчА): =И 7 1 СчА :=СчА+1 П 1 сСчЛ): =И Х 8 1 СчА: =СчА+ 1 П 1(СчА:=И СчА :СчА+1 П 1 сСчА):=И 10 1 СчА :=СчА+1 П 1(СчА). =И 11 1 СчА : =СчА+1 Таблица 2 Название команды Код коФи/и 5-5 5 6 5- 7 5-8 5-9 5- О 5-1 5- 12 5- 13 5- 14 5- 5 5- 6 ман 1 Обнуление СчА 28 и СМНК 32 0 0 О Г О 0 О 0 Д. 0 0 О 0 0 Г 1. 0 Л. 0 0 О 0 О 0 О О 2 Запись в БП 23Чтение из БП 2 иБП 7 2Л О 0 Л О 0 О О Л. О 1 4 Запись входного сигнала в БП 7 Э 0 0 0 0 О 0 0 О. 0 Д,0 5 Накопление произведений вБАр 3 и модификация СчА 28 4 0 О 0 Я 0 Л 0 0 0 0 0 0 6 Запись результата в Рг 35 БАр Эсо сдвигом, обнуление См Нк 32 5 0 0 О 0 0 О Д, П О 0 О О 6 0 0 0 0 О О 0 О 0 Л. О О 7 Запись выходного сигнала в БП 7 Выполняемые операции в команде Запись коэффициента я в БП 2 по пятому адресу, увеличение содержимого СчА 28 на 1 Запись коэффициента яв БП 2 по шестому адресу, увеличение содержимого СчА 28 на 1 Запись коэффициента я в БП 2 по седьмому адресу, увеличение содержимого СчА 28 на 1 Запись коэффициента -Ь в БП 2 по восьмому адресу, увеличение содержимого СчА 28 на 1 Запись коэффициента -Ь, в БП 2 по девятому адресу, увеличение содержимого СчА 28 на 116 15 1338006 Продолжение табл,2 Ф Название командыи/и Код ко" 5-5 5-6 5- 7 5-8 5-9 5- 1 О 5- 1 1 5- 1 2 5- 1 3 5- 1 4 5- 1 5 5- 16 ман 7 О О О О О О Л О О О О О 8 О О О О О О О О Д. Д. О О 1 О Останов микропрограмьы 9 О О О О О О О О О О О О П р и м е ч а н и е, О и 1 обозначают соответственно нулевое и единичноесостояние на выходах блока 5 управления, длительностью н целую командузнаком .Г - обозначено появление в команде соответствующего управляющегоимпульса. Таблица 3 ИА дв, система Выполняемые операции в команде мандиое слово Четный Нечетныйт, цикл цикл дерзание н коммент означение од ковнды бнуление и СмНк 32 чА Чтение В иэ БП 2, х, (и)иэ БП 7 запись в РгК 29 и РгВ 3 00 2 о сигнала о х,(п) апись входи БП 7 нв ме мНк 32 В хпм: См+РгКхРгВ 4 4 акопление в одификвция а СчА:фСчЛ+ и)РгВ 3 Чтение В иэБП 7 и запись 5 2 гК:=П 1 сСчАх х29 РгВ:=П 2 сИА Накопление в СмНК 32 , х,(п)+Вх,(п Модификация адреса в См+РгкхРгВ чАэ СчЛ:=СчЛ П 2, х Ргк 2 и) иэ и РгВ 30 0 00 РгК:=П 1 СчЛ 7 2 тение В , иэП 7 и запись РгВ:=П 2 ИА м;=См+РгКхРг СчЛ:ОСчЛ+ 2 010 010 у, (и) иэ29 и РгВ 30 гК; =Пс СчА тение -Ьиз П 7 и запись в РгВ:=П 2 с 8 Запись результата в Рг 35 БАр3 без обнуленияСм Нк 32 9 Запись выходного сигнала в Рг Вых, 4 и БП 7 Рг К: Пс СчАэРгВ: П 2 сИА)П 2 с ИА): =Вход Накопл Вх,(Модифи ние в сумматоре СмНк 32 2)+Вч х,(п)+Во, х,(п ция адреса в СчА 28

СмотретьЗаявка

3933843, 22.07.1985

ПРЕДПРИЯТИЕ ПЯ Г-4152

ШПОЛЯНСКИЙ АЛЕКСАНДР НАУМОВИЧ, ПЕТРОВА ИРИНА КОНСТАНТИНОВНА

МПК / Метки

МПК: H03H 17/04

Метки: программно-управляемый, фильтр, цифровой

Опубликовано: 15.09.1987

Код ссылки

<a href="https://patents.su/12-1338006-programmno-upravlyaemyjj-cifrovojj-filtr.html" target="_blank" rel="follow" title="База патентов СССР">Программно-управляемый цифровой фильтр</a>

Предыдущий патент: Дискретный фазовращатель

Следующий патент: Управляемый фильтр со стабилизацией динамических характеристик

Случайный патент: Устройство для параметрического контроля интегральных схем