Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1206805

Авторы: Венедиктов, Соломаха, Шевяков

Текст

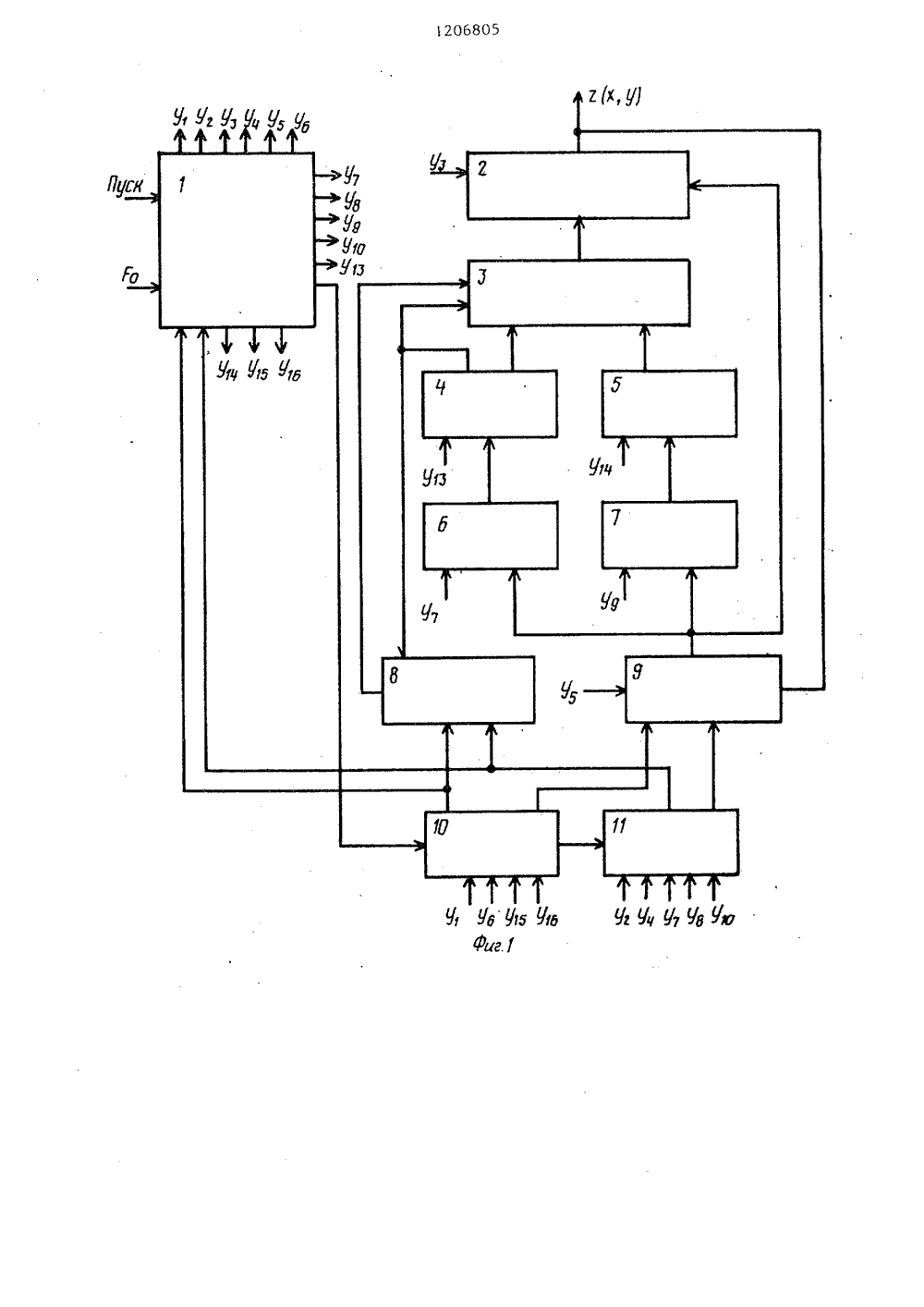

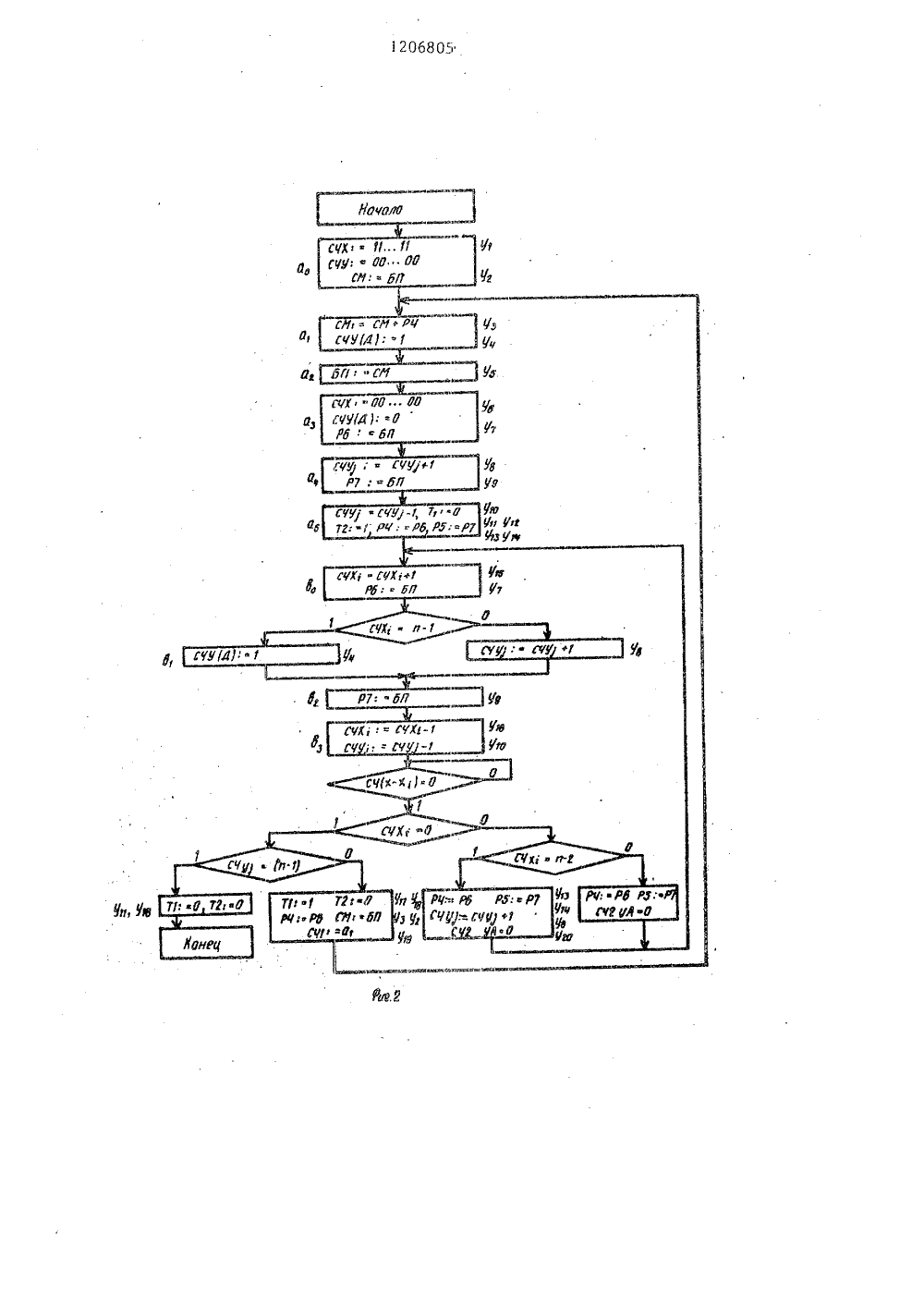

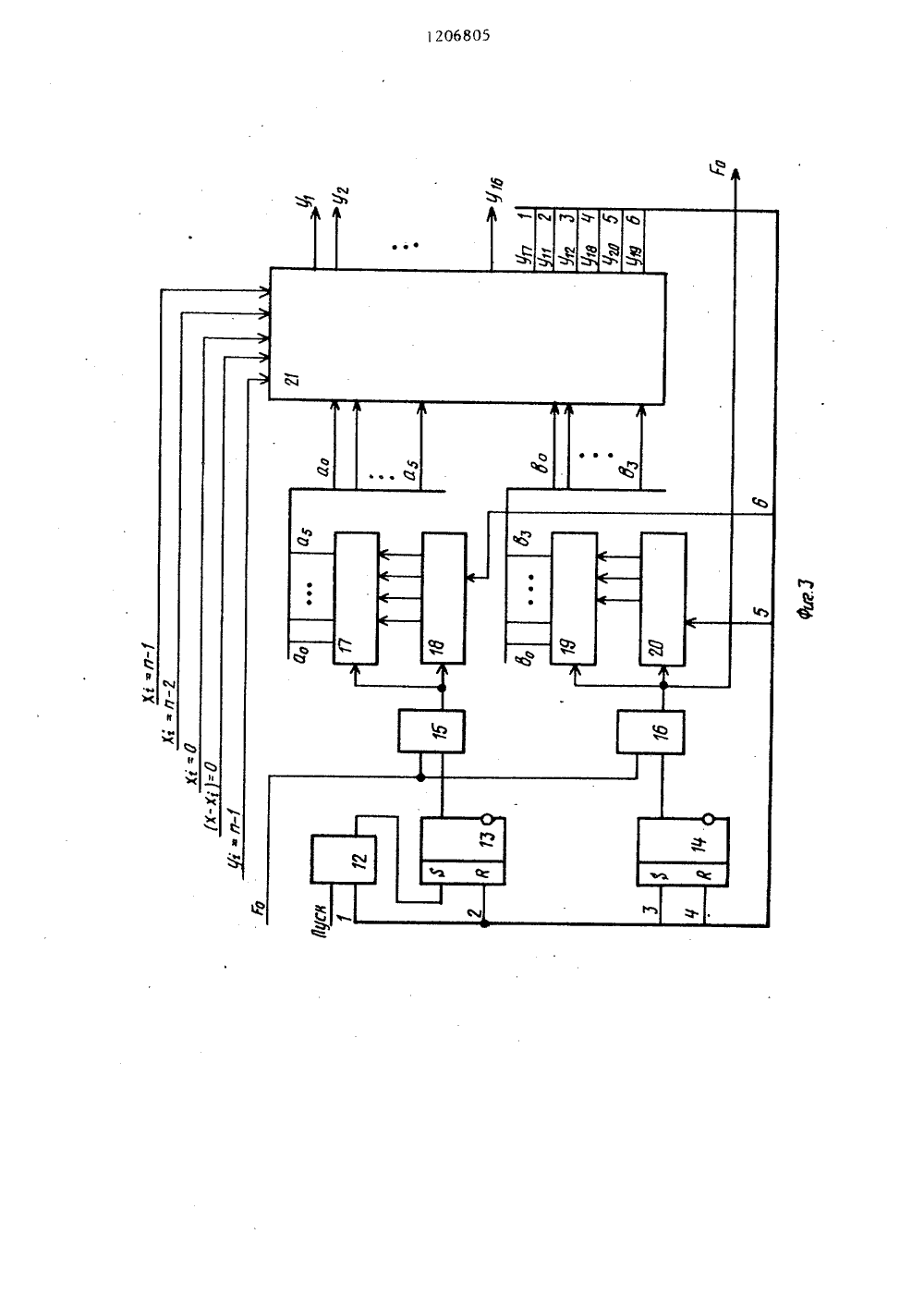

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 119) (11) 4 С 06 Г 15/353 ПИСАНИЕ ИЗОБРЕТЕНИ ах ам адресного входа бл хо блока памяти под и гр ключен амяти, вь д информацион м входам первого ов и информационвыход сумматор му второ еги ммато ой является выходом резул ства и соединен с инфо а ход ионным ход пуска икропрограммно входом блока памяти,тактовый вход блока м первая тветствуютактовый ого управдом первои днтерполятор микропрограмм нен с синхровхщими вход ыход бло ления сое го счетчи трепервыи, вторблока микропро раммног ии выходь ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ М ДВТОРСМОМУ СВИДЕТЕЛЬСТ(56) Авторское свидетельство СССР Р 763879, кл. С 06 Р 1/02, 1978.Авторское свидетельство СССР М 942040, кл. С 06 Р 15/353, 1980. (54)(57) ИНТЕРПОЛЯТОР, содержащий сумматор, первый, второй и третий ре гистрь., первый и второй счетчики, блок микропрограммного управления и блок памяти, причем выход переполнения первого счетчика подключен к синхровходу второго счетчика, первые группы информационных выходов обоих счетчиков подключены к первой и втого управления являются со управления соединены с входами разрешения записи первого, второго итретьего регистров соответственно,третий и четвертый выходы блока микропрограммного управления подключены к входам обратного счета первогои второго счетчиков соответственно,пятый и шестой выходы блока микропрограммного управления подключены квходу записи блока памяти и разрешающему входу сумматора, о т л и ч аю щ и й с я тем, что, с целью повышения точности интерполирования функции двух переменных, в него введеныблок сравнения, четвертый регистр,коммутатор, причем вторые группы информационных выходов первого и второго счетчиков подключены к информационным входам блока сравнения,вход стробирования блока сравнения соединен с выходом старшего разрядапервого регистра, а выход блока срав.нения соединен с первым управляющимвходом коммутатора,.информационныевходы которого подключены к выходампервого и второго регистров, выходкоммутатора подключен к информационному в у сумматора, вход разрешения записи четвертого регистра подключен к седьмому выходу блока управления, и вторая группы входов условий перехода блока микропрограммного управления соединена свторыми группами информационных выходов первого и второго счетчиков соответственно.1206805 Рг Составитель В,СоринКоссей Техред Т,Дубинчак Корректор В. Бутяга Закаэ 8 673ного исно СССР а г ст йр ний и5 р Рауш 7 5/51 ИИПИ 1 осуд о делам и 035, Моск тент", г,Ужгород,ул.ИроектнаИзобретение относится к вычислительной технике, автоматике и теле- механике и может быть использовано в качестве задающих устройств при сканировании двумерных функции уст -ройств линеаризации характеристик двухкя.нальных измерительных греобразователей развертывающего типа ит,пЦель изобретения - повышение точности интерполирования поверхностей заданцых функциями двух переменных в узловых точках с равнамерньм разбиением их области определения.На Фиг 1 представлена схема интерпопятара; на фиг.2 - микропрограмма Функционирования интерполята -ра; на фиг,З - блок микропрограммного управ, пения; на фиг.Йблоксравнения, вариант построения; наФиг 5 - распределение памяти интерполятора; на Фиг.б - расположениеплоских треугольниксв на 1.-м квадрате. разбиения области опрецеленияфункции, два варианта; на Фиг.7построение счетчика аргумента СгХ(СгУ) вариант; на Фиг.8 - временная,циаграмма работы блока управления, на Фиг,9 - комбинационна.я схема блока управленияИнтерпалятор поверхности соцержит блок 1 микропрограммного управления, сумматор 2, коммутатор 3, регистры -7 блок 8 сравнения, блок9 памяти, счетчики 10 и, 11,В состав блока 1 управления( Фиг,З) входят элемент ИЛИ 12, дватриггера 13 и 14 которые совместно с элементами И 15 и 16 обеспечивают работу распределителей сигналов 17-20, построенных по схемесчетчик (С, - дешифратор ,ДШ,. Первый из распределителей предназначендля Формирования состояний а авто -мята, второй - состояний Ь. Состояния а, и Ь дешифраторов и осведокмительные сигналых = п, х;=п, х; =О, х-х;=О,у, =и поступают на шифратор 21 блока упрявления. Как следует из микропрограммы ( Фиг.2), при состоянии а.(чФормируются управляющие сигналы ,. С )у и у причем, так как у, не Формлруется ни при каком другом состоянии распределителей сигналов (а, илиЬ ), то вход а .непосредствев.но подается на выход УС 1 у,), Лнапогич". но Формуются УС у, у , у- УьУ- УУ 1Схема блока 8 сравнения (Фиг.ч )содержит схему 22 сравнения, сумматор 23, элементы НЕ 24 и 25,Вариант построения счетчика 10( Фиг.7 а) содержит счетчик 26 элемент ИЛИ 27, элемент И 28, реверсивный с етчик 29. элементы И 30-32,1 О Вариант построения счетчика 11( Фиг,7 б) содержит счетчик 33, эле-.мент ИЛИ 3 реверсивный счетчик 35,триггер 36, элемент И 37.11)ифратор 21 (Фиг,9) содержит элг 15 менты ИЛИ 38- 41 элсменты И 42-ц 7элементы ИЛИ 48-59,Работа интерполятора происходитследующим образом.Б янтерпаляторе реализуется кусоч 20 но-плоскостная аппроксимация КЛАВ,в соответствии с которой заданнаяповерхность на каждом ьЗ-м квадратеразбиения области определения Функций 1(х,у) заменяется двумя плоски ми треуголъньми поверхностями(Фиг,б а,б)Рясположение этих треугольниковвь бирается так, чтобы обеспечить наилучшее из двух возможных вариантов ЗО (Фиг.б а,б), приближение годобластиОриентапия диагонали Аявляющейся следом линии пересечения треуч ольников, обозначается соотьетствующими признаками А;1-0,1, которыевместе с параметрами аппроксимации3.запоминаются в памяти устройства.Например, вариант о,(фиг,б) позволяет при данных ордипатах1 21 , 2.+11-1более точно по сравнению с прототи"п.пом приближать выпуклые участки поверхности, а вя.риант 8 - вогнутые.На Фиг.б обозначения 51 и 6, -погрешности аппроксимации подобласти д) с помощью кусочнолинейной аппроксимации (прототип) и кусочноплоскостной (предлагаемое устройство)При КПА значение производной в течение времени развертывания функциивнутри Ц - го квадрата разбиения об,асти ее существования определяетсянаклоном соответствующего треугольника и может быть записано для случая. показанного на Фиг.ба, какЬ 2.(Х,У) = (С (7;+13-;7.(/-Ч( Х + 1 . 1где Ч - операция ИЛИ (Функция логического выбора)31206805 4С =0, при ( х-х;)с(у - у); ников 1) -го кавдрата разбиепри (х-х 1)(у уния.2 - шаг аппроксимации, Для случая, показанного наи задает принадлежность точки с ко- фиг,6 б, выражение производной псординатами х и у одному из треуголь 5 х имеет видД 2 (Х,У): С (; -;,)ЧС,(,;-г; ,)1 а";С = 1 ел.1(У ),О, если ( х-х;)с(у-у) и учитывая, что рассмотренные случаирасположения треугольников разли 1) 4чаются соответствующим значениемВводя обоВво я обозначения 10признака А -(0,1, получаем общееЬ .11 - 21+1,/, 111+1выражение для вычисления значенияпроизводной на 13-м квадрате раз=-)ЧАь)1 У)314;(У+1-У)30 35 40 Это выражение и положено в основу реализации устройства.Управление процессом построчногоразвертывания осуществляется с по 2мощью последовательно включенныхсчетчиков аргументов С 10 и 11,младшие разряды которых фиксируютвеличины ( х-х и (у - у, соответственно, а старшие - коды номеровквадратов разбиения Ц (х; и у; ).Формирование значения С 1= 0, Цосуществляется с помощью блока 8сравнения, к входам схемы 22 сравнения подключается код (х-х;)-ипрямой или дополнительный код (у -УД, Формирование дополнительногокода (У-У)д=у+, - у осуществляетсяс помощью сумматора 23, к которомув зависимости от признака А; подключается прямой или обратный (инверсный ) код у-у . Кроме того, навход переноса младшего разряда сумматора 23 подключается блок 1 в случае формирования дополнительногокода,На фиг.5 показано распределениеблока 9 памяти. В ячейках, адресакоторых задаются значениями х; ,у,хранятся: Е начальное значениефункций; д Е; - величины приращений для построчного развертыванияГ(х,у); АЕ - величины приращенийдля вычисления значений функции вначале каждой строки; Ейск - ячейкадля хранения текущего значения функ-55ции в начале строки.Функционирование устройства осуществляется по сигналам у - у 4 блока 1 управления (фиг.31 в соответствии с микропрограммой (фиг.2) .В исходном состоянии (перед генерированием функции) в сумматор 2 интерполятора из блока 9 памяти передается начальное значение функции Еоо 1(хо Уо )Для этого блок Управления по состоянию а, присваивает счетчикам 10 и 11 адрес ячейки памяти, где хранится значение 2, Далее содержимое сумматора 2 передается в ячейку блока 9 памяти, где хранится текущее значение функции в начале стРоки (Е с ). Адрес этой ячейки задается с помощью дополнительного разряда счетчика 11 ( состояния а, а). Затем счетчик 10 обнуляется, в счетчике 11 сбрасывается дополнительный разряд и следует обращение к блоку 9 памяти за величинами 4 Ео и 62 оч, которые помещаются соответственно в регистры 6 и 7. Завершающим действи- ф ем процесса подготовки к развертыванию является передача содержимого регистров 6 и 7 в регистры 4 и 5 соответственно и перевод интерполятора из режима подготовки в режим развертывания соответствующей строки поверхности. Это достигается с помощью триггеров управления 1 блока, первый иэ которых отключает первый распределитель, а второй включает второй, и, кроме того, подключает тактовую частоту Р к входу счетчика 10 и управляющему входу сумматора 2. Таким образом, в счетчике 10 фиксируется из менение аргумента Х , а в сумматоре 2 к начальному значению Е начинаютприбавляться с частотой Р приращения Ь Ео или ЬЕс+ . За счет это го обеспечивается развертывание Е(х,у). Выбор одно из двух регист" ров 4 и 5, в которые занесены Ь Е 1 и Ь.Е +, осуществляется с помощью коммутатора 3 и блока 8 сравнения в соответствии с выражением 1, При этом значение признака А; хРанится в дополнительном разряде вместе с приращением Л Е; и после выборки его из блока 9 памяти будет находиться в дополнительном разряде регистра 4, Содержимое этого разряда. и подключается ко входам блока 8 сравнения и коммутатора 3.Параллельно с развертывачием Г(х,у) на 1.-м интервале разбиения по Х обеспечивается чтение приращений 5 Е;.,;и ЬЕ,т,е, для следуюф 4щего интервала, которые помещаются в регистры 6 и 7,При появлении импульса переполнения ( СЧХ - Х, =О) анализируются условия( СЧХ; (0) Л (СЧХ; ф п) - соответствующее переходу на следующий интервал разбиения по Х . В этом случае содержимое регистров 6 и 7 передается в регистры 4 и 5, а процесс развертывания и выборки приращений для следующего интерваларазбиения по Л продолжается;( СчХ; ф О) Л (СчХ; =и) - соответствующее переходу на последнийинтервал разбиения по МДействияаналогичны предыдущему случаю, эаисключением того, что в регистр 6помещается приращение Д Е, а навходе БП устанавливается адрес ординаты Е т,(Сч У(Д 1: =1( б Е;), осуществляется вычислениенового значения функции в начале сле.2 О дующей строки (состояние а 1 и за-.пись нового значения Ер в БП 9(состояние а). Далее повторяютсядействия по выбору приращений ЬЕО,1и ВЕ + (состояния а, а и пере - 25 ход к началу развертывания следующей строки состояние а);(СчХ; Ф 01( СчУ; ) =и) - соответствующее окончанию развертывания поро верхности. В этом случае работа устройства заканчивается.

СмотретьЗаявка

3757014, 21.06.1984

РЯЗАНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ВЕНЕДИКТОВ АНАТОЛИЙ ЗАХАРОВИЧ, СОЛОМАХА ВАЛЕНТИН НИКОЛАЕВИЧ, ШЕВЯКОВ АЛЕКСАНДР ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 17/17

Метки: интерполятор

Опубликовано: 23.01.1986

Код ссылки

<a href="https://patents.su/12-1206805-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Цифровой коррелятор для обнаружения эхо-сигналов

Следующий патент: Устройство для редактирования списка

Случайный патент: Устройство для защиты трехфазной электроустановки от неполнофазных режимов работы