Сбоеустойчивое микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

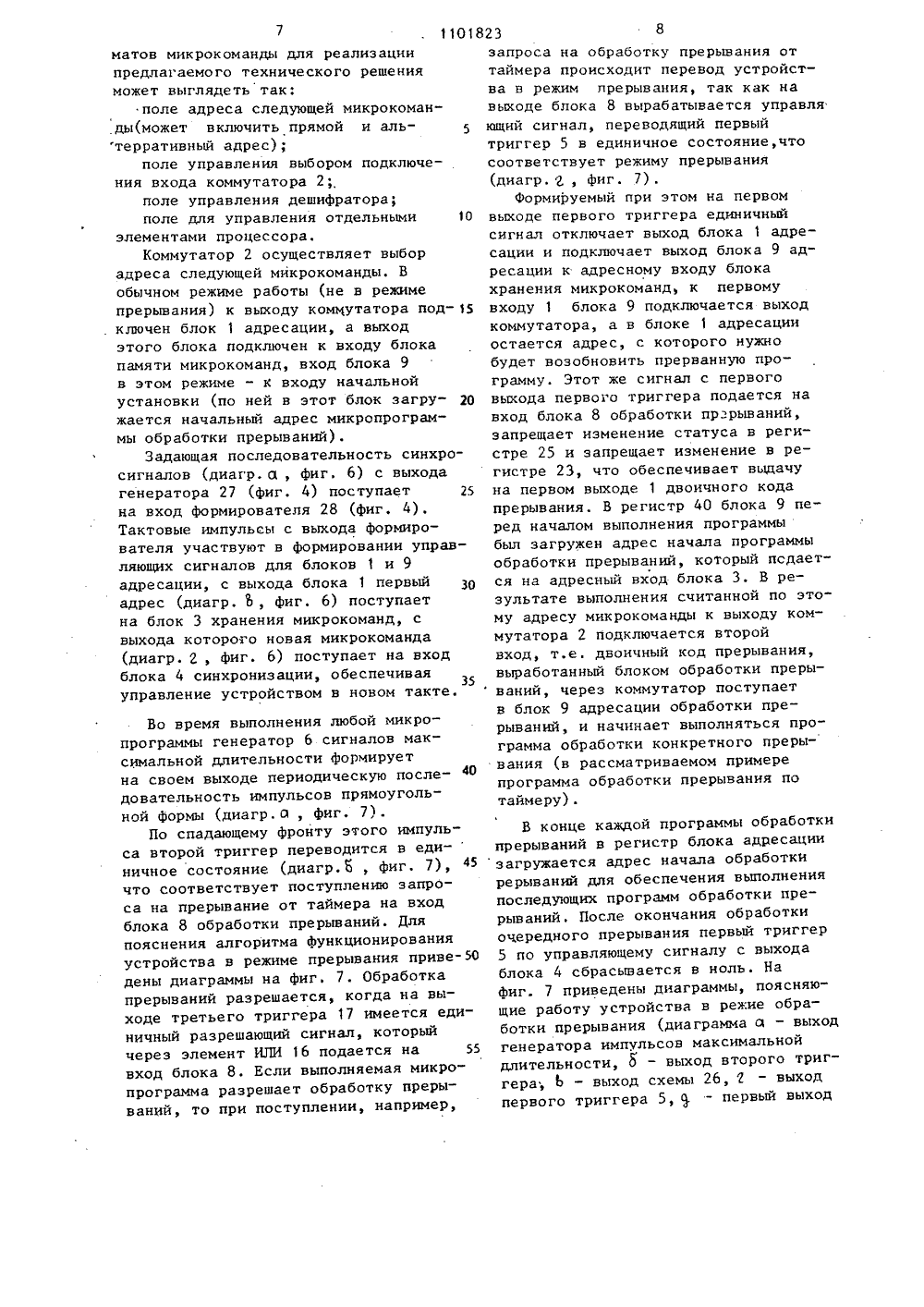

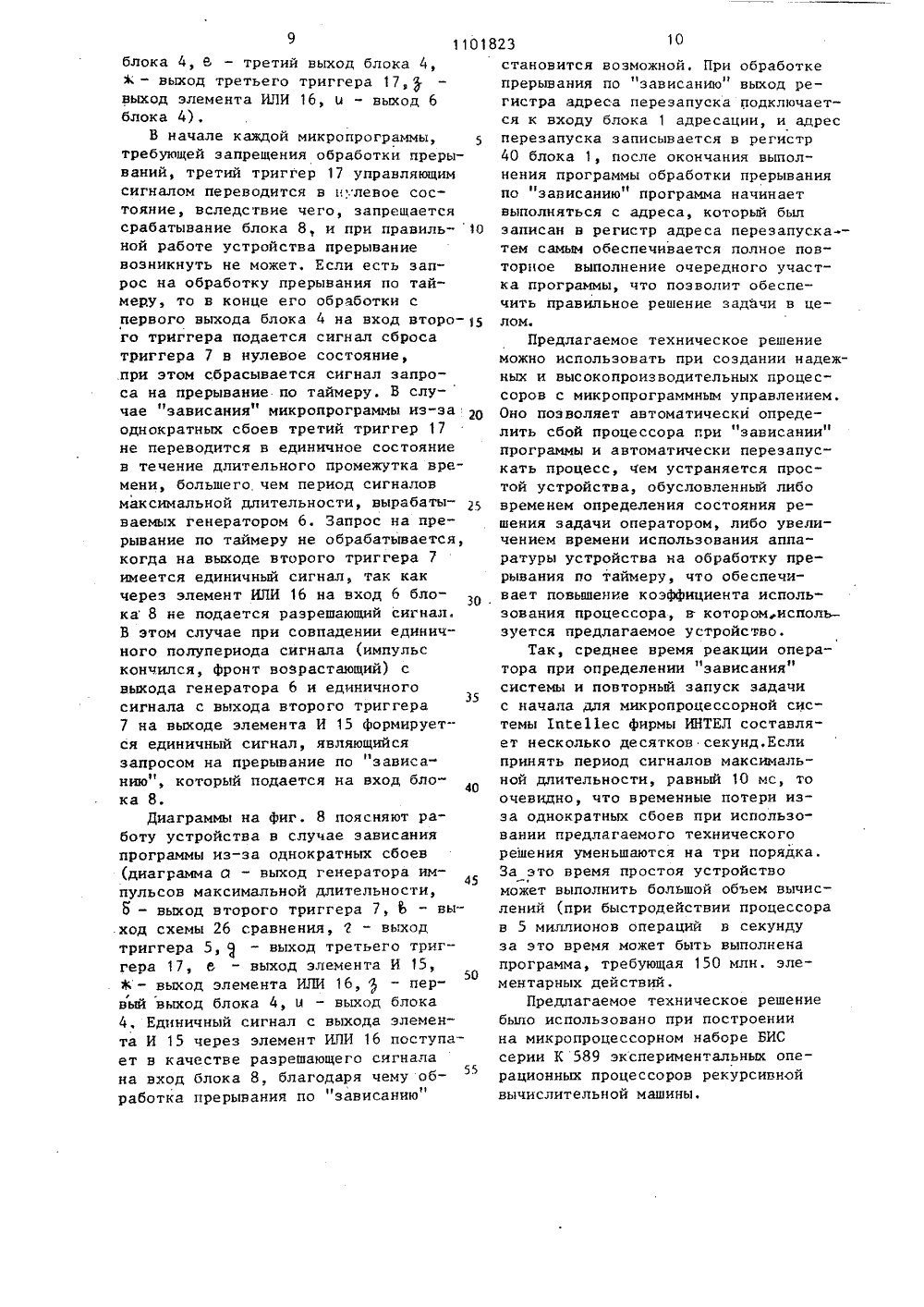

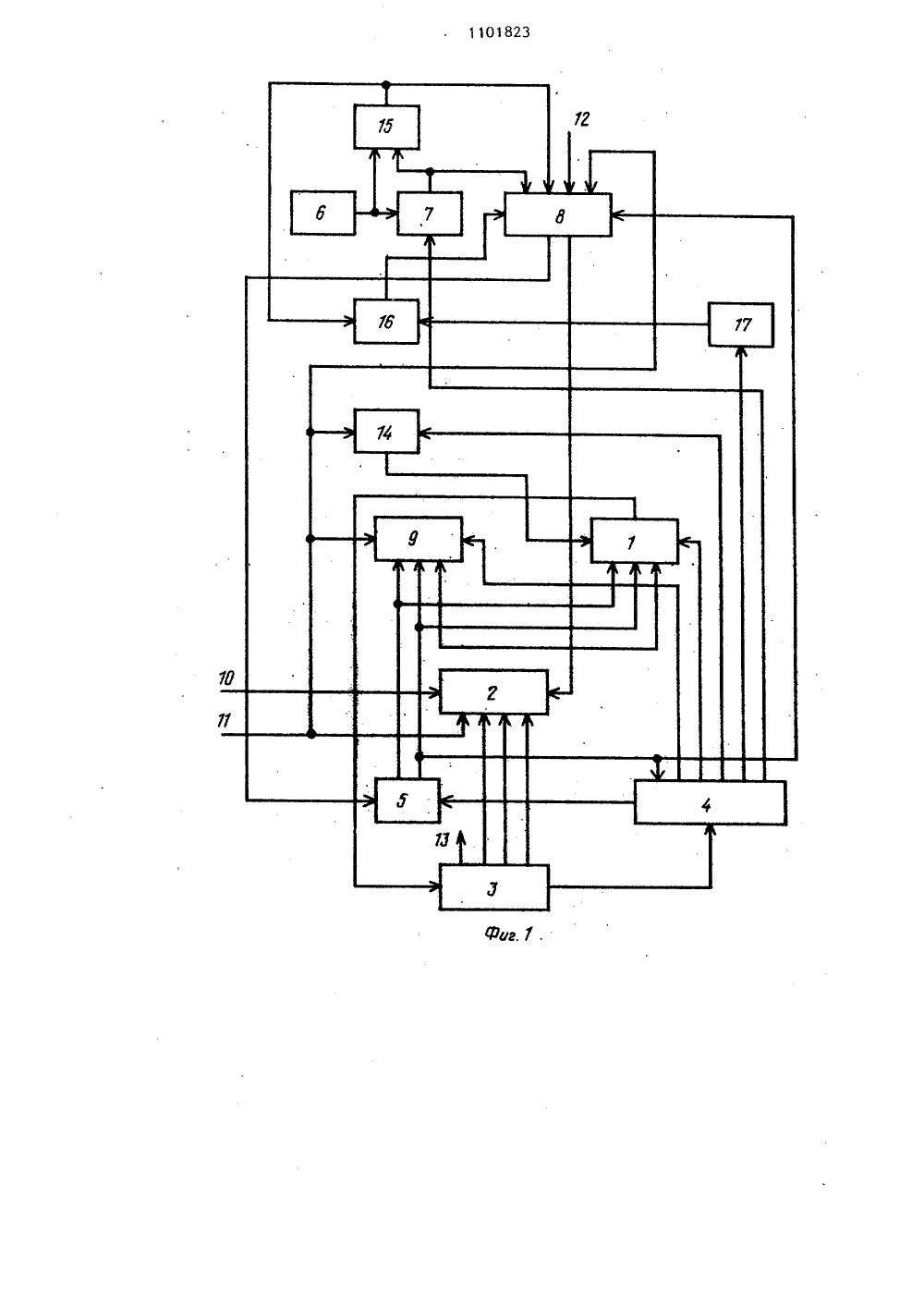

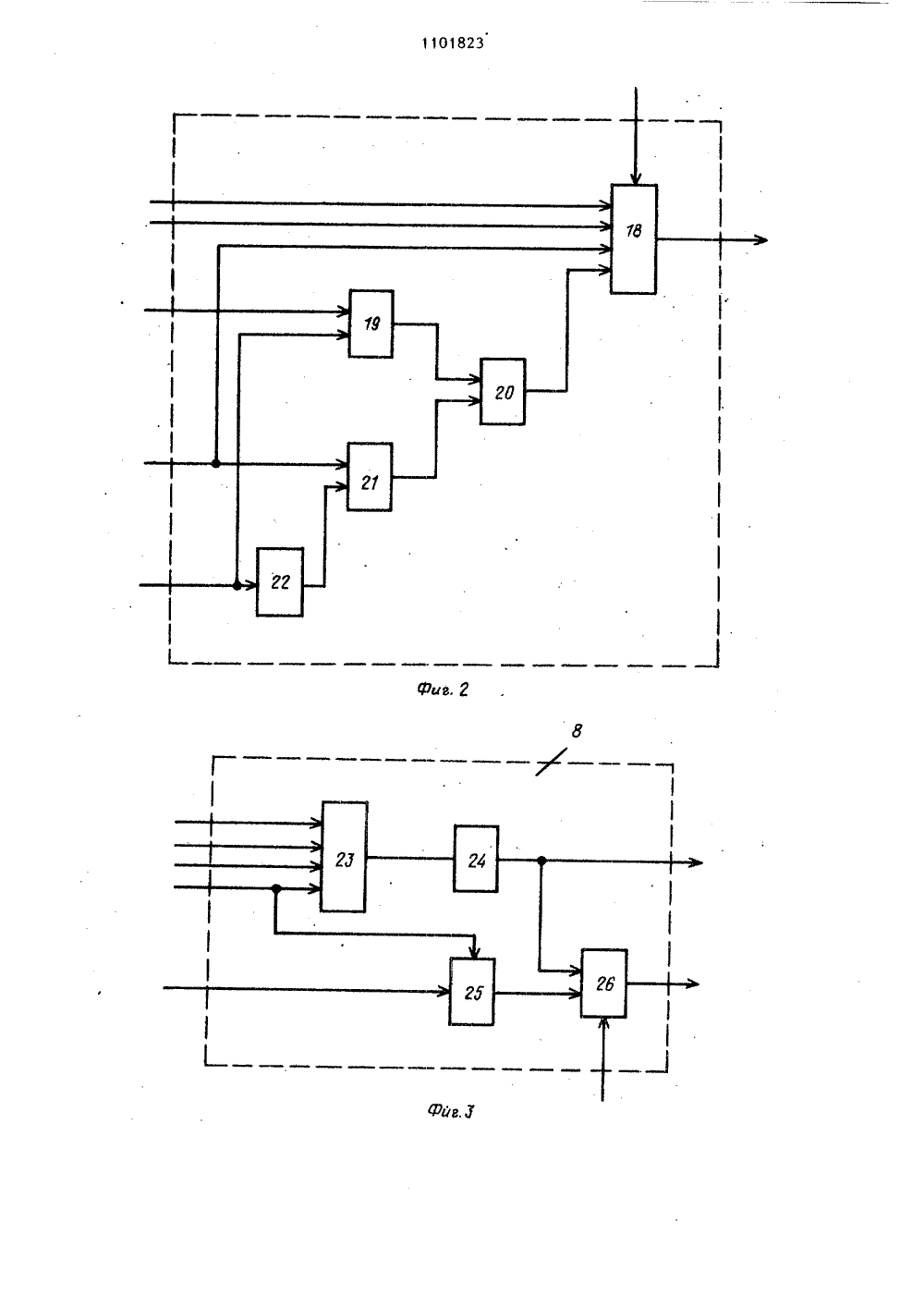

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕ ОНИ ХРЕСПУБЛИН(19) (И) 3(51) С 06 Р 9/22 лг ПИСА ИЗОБРЕТЕНИ вт ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬ(ТИЙ(46) 07,07.84. Бюл, У 25 (72) С.В. Горбачев, В.Д. Диденко, Е,А. Бурова и В.А, Торгашев (71) Ленинградский институт авиационного приборостроения и Ленинградский научно-исследовательский вычислительный центр АН СССР(56) 1. Авторское свидетельство СССР И 525956, кл. С Об Р 9/22, 1965.2, Авторское свидетельство СССР У 551648, кл. С 06 Г 15/16, 1974 (прототип).(54)(57) 1. СБОЕУСТОЙЧИВОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок адресации, коммутатор,блок памяти микрокоманд, блок синхронизации, первый триггер, блок обра.ботки прерываний, блок адресации врежиме прерывания, выход которогообъединен с выходом блока адресациии соединен с адресным входом блокапамяти микрокоманд, первый, второйи третий управляющие выходы которогосоединены соответственно с первымвходом блока синхронизации, выходомуправления устройства и с первымуправляющим входом коммутатора, второйуправляющий вход которого соединенс управляющим входом устройства,первый, второй и третий информационные входы коммутатора соединены соответственно с первым, вторым адресными выходами блока памяти микрокоманд и первым выходом. блока обработкипрерываний, второй выход которогосоединен с единичным входом первоготриггера, нулевой вход которого соединен с первым выходом блока синхронизации, второй и третий выходы которого соединены соответственно спервыми управляющими входами блоковадресации в режиме прерывания, первые информационные входы которыхсоединены с выходом коммутатора,четвертый информационный вход которого соединен с входом адреса устройства, с вторым информационнымвходом блока адресации в режиме прерывания и с первым входом блока обработки прерываний, второй вход которого соединен с входом запроса напрерывание устройства, выход второготриггера соединен с третьим входомблока обработки прерываний, четвертый вход которого соединен с вторымвходом блока синхронизации, с единичным выходом первого триггера и с орыми управляющими входами блоковадресации в режиме прерывания, третьиуправляющие входы которых соединеныс нулевым выходом первого триггера,выход генератора импульсов максимальной длительности соединен с единичнымвходом второго триггера, нулевойвход которого соединен с четвертымвыходом блока синхронизации, о т -л и ч а ю щ е е с я тем, что, сцелью повышения коэффициента использования оборуцования путем автоматического перезапуска процесса приоднократных сбоях и зацикливанияпрограмм, устройство дополнительно.содержит регистр адреса перезапуска,элемент И, элемент ИЛИ, третий триггер, причем информационный вход регистра адреса перезапуска соединен свходом адреса устройства, а управляющий вход - с пятым выходом блока син 11018231101823 оставитель Л, Логаневехред А. Бабинец ктор В. Даик Заказ 4769/3 дписно Патент",Ужгород, ул. Проектная, 4 илиал 3 Тираж б 99ВНИИПИ Государственногопо делам изобретений113035, Москва, Ж, Рау омитета СССоткрытийкая наб., д рректор В. Бутяга11 О хронизации, а выход регистра адреса перезапуска соединен с вторым информационным входом блока адресации, шестой выход блока синхронизации соединен с входом третьего триггера, единичный выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента И и с пятым входом блока обработки прерываний, шестой вход которого соединен с выходом элемента ИЛИ, выход генератора импульсов максимальной длительности соединен с первым входом элемента И, второй вход которого соединен с выходом второго триггера. 2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок обработки 82 Зпрерываний содержит первый, второй регистры, шифратор и схему сравнения, первый и второй инфориационные входы которой соединены соответственно с выходами шифратора и первого регистра, управляющий вход схемы сравнения соединен с шестым входом блока а выход - с вторым выходом блока, управляющие входы первого и второго регистров соединены с четвертым входом блока, информационный вход первого регистра соединен с первым входом блока, второй, третий и пятый входы блока объединены и подключены к информационному входу второго регистра, выход которого соединен с входаи шифратора, выход которого подключен к первому выходу блока.Изобретение относится к вычислительной технике и может найти применение при создании микропрограммируемых специализированных и универсальных высокопроизводительных цифровых вычислительных машин, а именна устройств управления работой процессоров с микропрограммной реализацией.Известно микропрограммное устройство управления, которое предусмат ривает вхождение в режим прерывания при обнаружении зависания вычислительного процесса ЯОднако существующие методы обнарушения и вхожцения в режим прерыва ния существенно снижают коэффициент использования оборудования и, в конечном итоге, увеличивают время прохождения задачи.Наиболее близким к изобретению является устройство, содержащее блок адресации, коммутатор, блок хранения микрокоманд, блок управления и синхронизации, первый триггер, генератор импульсов максимальной длитель- " ности, второй триггер, блок обработки прерываний, блок адресации в режиме прерывания, шину управления выбором прямого и альтернативного адреса, шину начальной установки, шину внешних запросов на прерывания шину управления элементами процессора, причем выход блока адресации подключен к выходу блока адресации в режиме прерывания и к входу блока хранения микрокоианд, второй и пятый входы которого соединены соответственно с шиной управления элементами процессора и с шестым входом коммутатора, четвертый вход которого подключен к третьему выходу блока хранения микрокаманд, первый и четвертый выходы которого соединены соответственно с первым входом блока управления и синхронизации и пятым входом коммутатора, первый и второй входы которого подключены соответственно к шине управления выбором прямого и альтернативного адреса и первым выходом блока обработки прерываний, третий вход которого соединен с вторым входом управления и синхронизации, с третьии входом блока адресации, с четвертым входам блока адресации в режиме прерывания и с первымвыходом первого триггера, второй ипервый входы которого подключены ктретьему выходу блока управления исинхронизации и второму выходу блокаобработки прерываний, четвертыйвход которого соединен с шиной начальной установки, с третьим входом комму 3 11018 татора и пятым входом блока адресации в режиме обработки прерываний, первый входкоторого соединен с выходом коммутатора и первым входом блока адресации, четвертый вход которого подключен к второму выходу первого триггера и к третьему входу блока адресации в режиме прерывания, второй вход которого соединен с четвертым выходом блока управления и синхрониза.10 ции, второй и первый выходы которого подключены соответственно к выходу генератора импульсов максимальной длительности и к второму входу блока обработки прерываний, первый вход 15 которого соединен с шиной внешних прерываний 21.В известном микропрограммном устройстве наибольшие трудности появляются при определении состояния "зави сания" программы. Если состояние зависания определяется оператором, время решения задачи увеличивается, так как среднее время реакции оператора при определении "зависания" и повторный запуск с начала. составляет несколько десятков секунд (ЭО с). Использование генератора сигналов максимальной длительности (он формирует сигнал запроса прерывания по30 таймеру) усложняет обработку прерывания программными способами. Кроме того, прерывание процесса вычисления по таймеру не связано с состоянием процесса - находится ли он в состоянии "зависания" или в состоянии пра- З 5 вильного выполнения (поэтому в изобретении предлагается автоматическое определение состояния зависания без участия оператора и возможнос 40 ности формирования прерывания работы устройства только в случае зависания). 23 4объединен с выходом блока адресации и соединен с адресным входом блока памяти микрскоманд, первый, второй и третий управляющие выходы которого соединены соответственно с первым входом блока синхронизации, выходом управления устройства и с первым управляющим входом коммутатора, второй уПравляющий вход которого соединен с управляющим входом устройства, первый, второй и третий информационные входы коммутатора соединены соответственно с первым, вторым адресными выходами блока памяти микрокоманд и первым выходом блока обработки прерываний, второй выход которого соединен с единичным входом первого триггера, нулевой вход которого соединен с первым выходом блока синхронизации, второй и третий выходы которого соединены соответственно с первыми управляющими входами блока адресации и адресации в режиме прерывания, первые информационные входы которых соединены с выходом коммутатора, четвертый информационный вход которого соединен с входом адреса устройства, с вторым информационным входом блока адресации в режиме прерывания и с первым входом блока обработки прерываний, второй вход которого соединен с входом запроса на прерывание устройства, выход второго триггера соединен с третьим входом блока обработки прерываний, четвертый вход которого соединен с вторым входом блока синхронизации, единичным выходом первого триггера и с вторыми управляющими входами блоков адресации в режиме прерывания, третьи управляющие входы которых соединены с нулевым выходом первого триггера, выход генератора импульсов максимальнойЦелью изобретения является повышение коэффициента использования оборудования путем автоматического перезапуска процесса при однократных сбоях и. зацикливании программ.Поставленная цель достигается тем, что в сбоеустойчивое микро программное устройство управления, содержащее блок адресации, коммутатор, блок памяти микрокоманд, блок синхронизации, первый триггер, генератор импульсов максимальной длитель ности, второй триггер, блок обработки прерывания, блок адресации в режиме прерывания, выход которого длительности соединен с единичным входом второго триггера, нулевой вход которого соединен с четвертым выходом блока синхронизации, введе-, ны регистр адреса перезапуска, элемент И элемент ИЛИ, третий триггер, причем информационный вход регистра адреса перезапуска соединен с входом адреса устройства, а управляющий вход - с пятым выходом блока синхронизации, выход регистра адреса перезапуска - с вторым информационным входом блока адресации, шестой выход блока синхронизации - с входом третьего триггера, единичный выход11018 15 50 55 которого соединен с первым входомэлемента ИЛИ, второй вход которогосоединен с выходом элемента И и спятым входом блока обработки прерынаний, шестой вход которого соединенс выходом элемента ИЛИ, выход генератора импульсов максимальной длительности соединен с первым входом элемента И, второй вход которого соединен с выходом второго триггера. 10При этом блок обработки прерываний содержит первый, второй регистры, шифратор и схему сравнения, первый и второй информационные входыкоторой соединены соответственно с 15выходами шифратора и первого регистра, управляющий вход схемы сравнения соединен с шестым входом блока,а выход - с вторым выходом блока,управляющие входы первого и второгорегистров - с четвертым входом блока,информационный вход первого регистра - с первым входом блока, второй,третий и пятый входы блока объединены и подключены к информационному 5входу второго регистра, выход которого соединен с входом шифратора,выход которого подключен к первомувходу блока,Таким образом, введение регистра З 0адреса перезапуска, схемы И, схемыИЛИ, триггера обеспечивает выявление "зависания" программы, автоматический ее перезапуск и формированиесигнала прерывания только при зави.сании программы.На фиг. 1 изображена блок-схемапредлагаемого устройства, на фиг.2 ;блок-схема коммутатора; на фиг.3блок-схема обработки прерываний; на 40фиг. 4 - блок-схема блока синхронизации; на фиг. 5 - блок-схема блокаадресации; на фиг. 6 - временныедиаграммы основного цикла работыустройства; на фиг. 7 - временныедиаграммы работы устройства в режимеобработки прерывания; на фиг. 8 -временные диаграммы работы устройствапри зависании программы. Предлагаемое микропрограммное устройство содержит (фиг. 1) блок 1 адресации, коммутатор 2, блок 3 памяти микрокоманд, блок 4 синхронизации, триггер 5, генератор 6 импульсов максимальной длительности, триггер 7; блок 8 обработки прерываний, блок 9 адресации в режиме прерывания, управляющий вход 10 устройства,. 23 6вход 11 адреса устройства, вход 12запроса на прерывание устройства,выход 13 управления устройства, регистр 14 адреса перезапуска, элементИ 15,элемент ИЛИ 16, триггер 17.Входящий в микропграммное устройство управления коммутатор фиг.2)содержит коммутатор 18, группу 19элементов И, группу 20 элементов ИЛИ,группу 21 элементов И, элемент НЕ 22.Входящий в микрограммное устройство управления блок обработкипрерываний (фиг. 3) содержит регистр23, шифратор 24, регистр 25", схему26 сравнения.Входящий в микропрограммное устройство управления блок синхронизациисодержит генератор 27, формирователь28, элемент НЕ 29, дешифратор 30,элементы 2 И 31-34, элементы ЗИ 35 и36, элементы 2 ИЛИ 37 и 38,Входящий в микропрограммное устройство управления блок 1 адресации(фиг. 5) содержит группу 39 элементовИ, регистр 40, группу 41 элементовИЛИ, группу 42 элементов И, группу43 элементов И,Регистр 14 адреса перезапускапредназначен для хранения начальногоадреса микропрограммы и может бытьреализован на регистровых схемахК 589 ИР 12,Злемент И 15 предназначен для формирования запроса на прерывание в случае однократного сбоя и зацикливания и может быть реализован на схеме К 155 ЛИ 1.Злемент ИЛИ 16 предназначен для формирования сигнала разрешения обработки прерывания и может быть реализован на схеме К 155 ЛЛ 1.Третий триггер 17 предназначен для обеспечения запрещения обработки прерываний и может быть реализован на схеме К 155 ТМ 2.Микропрограммное устройство работает следующим образом.При включении устройства на вход блока 3 памяти микрокоманд поступает определенный адрес (обычно нулевой), с которого начинается микропрограмма, назначение которой - загрузка начального адреса с внешней шины в качестве начального адреса микропрограммы. Адрес с выхода блока 1 адресации поступает на адресный вход блока . 3, с которого считывается первая микрокоманда. Один нз возможных фор 1101823матов микрокоманды для реализации предлагаемого технического решения может выглядеть так;поле адреса следующей микрокоманды(может включить прямой и аль 5 терративный адрес);поле управления выбором подключения входа коммутатора 2;поле управления дешифратора;поле для управления отдельными элементами процессора,Коммутатор 2 осуществляет выбор адреса следующей микрокоманды. В обычном режиме работы (не в режиме прерывания) к выходу коммутатора под . ключен блок 1 адресации, а выход этого блока подключен к входу блока памяти микрокоманд, вход блока 9 в этом режиме - к входу начальной установки (по ней в этот блок загру жается начальный адрес микропрограммы обработки прерываний).Задающая последовательность синхросигналов (диагр, а, фиг. 6) с выхода генератора 27 (фиг. 4) поступает 25 на вход формирователя 28 (фиг, 4). Тактовые импульсы с выхода формирователя участвуют в формировании управляющих сигналов для блоков 1 и 9 адресации, с выхода блока 1 первый адрес (диагр. о, фиг, 6) поступает на блок 3 хранения микрокоманд, с выхода которого новая микрокоманда (диагр2, фиг. 6) поступает на вход блока 4 синхронизации, обеспечивая управление устройством в новом такте. Во время выполнения любой микропрограммы генератор 6 сигналов максимальной длительности формирует на своем выходе периодическую после довательность импульсов прямоугольной формы (диагр. а, фиг. 7).По спадающему фронту этого импульса второй триггер переводится в еди-ничное состояние (диагр.6 , фиг. 7), 45 что соответствует поступлению запроса на прерывание от таймера на вход блока 8 обработки прерываний, Для пояснения алгоритма функционирования устройства в режиме прерывания приве дены диаграммы на фиг. 7. Обработка прерываний разрешается, когда на выходе третьего триггера 17 имеется единичный разрешающий сигнал, который через элемент ИЛИ 16 подается на 55 вход блока 8. Если выполняемая микропрограмма разрешает обработку прерываний, то при поступлении, например,запроса на обработку прерывания оттаймера происходит перевод устройства в режим прерывания, так как навыходе блока 8 вырабатывается управляющий сигнал, переводящий первый триггер 5 в единичное состояние,что соответствует режиму прерывания (диагр. Я, фиг. 7).Формируемый при этом на первом выходе первого триггера единичный сигнал отключает выход блока 1 адресации и подключает выход блока 9 адресации к адресному входу блока хранения микрокоманд, к первому входу 1 блока 9 подключается выход коммутатора, а в блоке 1 адресацииостается адрес, с которого нужно будет возобновить прерванную программу. Этот же сигнал с первоговыхода первого триггера подается навход блока 8 обработки прерываний,запрещает изменение статуса в регистре 25 и запрещает изменение в регистре 23, что обеспечивает выдачуна первом выходе 1 двоичного кодапрерывания. В регистр 40 блока 9 перед началом выполнения программыбыл загружен адрес начала программыобработки прерываний, который псдается на адресный вход блока 3. В результате выполнения считанной по это"му адресу микрокоманды к выходу коммутатора 2 подключается второй вход, т.е. двоичный код прерывания,выработанный блоком обработки прерываний, через коммутатор поступает в блок 9 адресации обработки прерываний, и начинает выполняться программа обработки конкретного прерывания (в рассматриваемом примерепрограмма обработки прерывания потаймеру). В конце каждой программы обработки прерываний в регистр блока адресации загружается адрес начала обработки рерываний для обеспечения выполнения последующих программ обработки прерываний. После окончания обработки очередного прерывания первый триггер 5 по управляющему сигналу с выхода блока 4 сбрасывается в ноль. На фиг. 7 приведены диаграммы, поясняющие работу устройства в режие обработки прерывания (диаграмма а - выход генератора импульсов максимальной длительности,- выход второго триггера; Ь - выход схемы 26, 2 - выход первого триггера 5, ф - первый выходблока 4, 6 - третий выход блока 4,Ж - выход третьего триггера 17,выход элемента ИЛИ 1 б, и - выход 6блока 4),В начале каждой микропрограммы,требующей запрещения обработки прерываний, третий триггер 17 управляющимсигналом переводится в .левое состояние, вследствие чего, запрещаетсясрабатывание блока 8, и при правильной работе устройства прерываниевозникнуть не может. Если есть запрос на обработку прерывания по таймеру, то в конце его обработки спервого выхода блока 4 на вход второго триггера подается сигнал сбросатриггера 7 в нулевое состояние,при этом сбрасывается сигнал запроса на прерывание по таймеру, В случае "зависания" микропрограммы из-заоднократных сбоев третий триггер 17не переводится в единичное состояниев течение длительного промежутка времени, большего чем период сигналовмаксимальной длительности, вырабатываемых генератором б. Запрос на прерывание по таймеру не обрабатывается,когда на выходе второго триггера 7имеется единичный сигнал, так какчерез элемент ИЛИ 16 на вход б блока 8 не подается разрешающий сигнал.В этом случае при совпадении единичного полупериода сигнала (импульскончился, фронт возрастающий) свыхода генератора б и единичного35сигнала с выхода второго триггера7 на выходе элемента И 15 формируется единичный сигнал, являющийсязапросом на прерывание по "зависа"нию", который подается на вход блока 8.Диаграммы на фиг. 8 поясняют работу устройства в случае зависанияпрограммы из-за однократных сбоев(диаграмма а - выход генератора им 45пульсов максимальной длительности,6 - выход второго триггера 7, Ь - выход схемы 26 сравнения, 7 - выходтриггера 5,- выход третьего триггера 17, б - выход элемента И 15504 - выход элемента ИЛИ 16,- первый выход блока 4, ц - выход блока4, Единичный сигнал с выхода элемента И 15 через элемент ИЛИ 16 поступает в качестве разрешающего сигналана вход блока 8, благодаря чему об 55работка прерывания по "зависанию" становится возможнойПри обработке прерывания по "зависанию" выход регистра адреса перезапуска подключается к входу блока 1 адресации, и адрес перезапуска записывается в регистр 40 блока 1, после окончания выполнения программы обработки прерывания по "зависанию программа начинает выполняться с адреса, который был записан в регистр адреса перезапуска тем самым обеспечивается полное повторное выполнение очередного участка программы, что позволит обеспечить правильное решение задачи в целом.Предлагаемое техническое решение можно использовать при создании надежных и высокопроизводительных процессоров с микропрограммным управлением. Оно позволяет автоматически определить сбой процессора при "зависании" программы и автоматически перезапускать процесс, чем устраняется простой устройства, обусловленный либо временем определения состояния решения задачи оператором, либо увеличением времени использования аппаратуры устройства на обработку прерывания по таймеру, что обеспечивает повышение коэффициента использования процессора, в которомиспользуется предлагаемое устройство.Так, среднее время реакции оператора при определении "зависания" системы и повторный запуск задачи с начала для микропроцессорной системы 1 п 1 е 11 ес фирмы ИНТЕЛ составляет несколько десятков секунд. Если принять период сигналов максимальной длительности, равный 10 мс, то очевидно, что временные потери изза однократных сбоев при использовании предлагаемого технического решения уменьшаются на три порядка. За это время простоя устройство может выполнить большой объем вычислений (при быстродействии процессора в 5 миллионов операций в секунду за это время может быть выполнена программа, требующая 150 млн. элементарных действий.Предлагаемое техническое решение было использовано при построении на микропроцессорном наборе БИС серии К 589 экспериментальных операционных процессоров рекурсивной вычислительной машины.

СмотретьЗаявка

3496094, 01.10.1982

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ, ЛЕНИНГРАДСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ВЫЧИСЛИТЕЛЬНЫЙ ЦЕНТР АН СССР

ГОРБАЧЕВ СЕРГЕЙ ВЛАДИМИРОВИЧ, ДИДЕНКО ВЛАДИМИР ДМИТРИЕВИЧ, БУРОВА ЕЛЕНА АЛЕКСЕЕВНА, ТОРГАШЕВ ВАЛЕРИЙ АНТОНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное, сбоеустойчивое

Опубликовано: 07.07.1984

Код ссылки

<a href="https://patents.su/12-1101823-sboeustojjchivoe-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Сбоеустойчивое микропрограммное устройство управления</a>

Предыдущий патент: Делительно-множительное устройство

Следующий патент: Мажоритарное устройство

Случайный патент: Способ сейсмической разведки