Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1305851

Авторы: Воротов, Грушвицкий, Могнонов, Мурсаев, Смолов

Текст

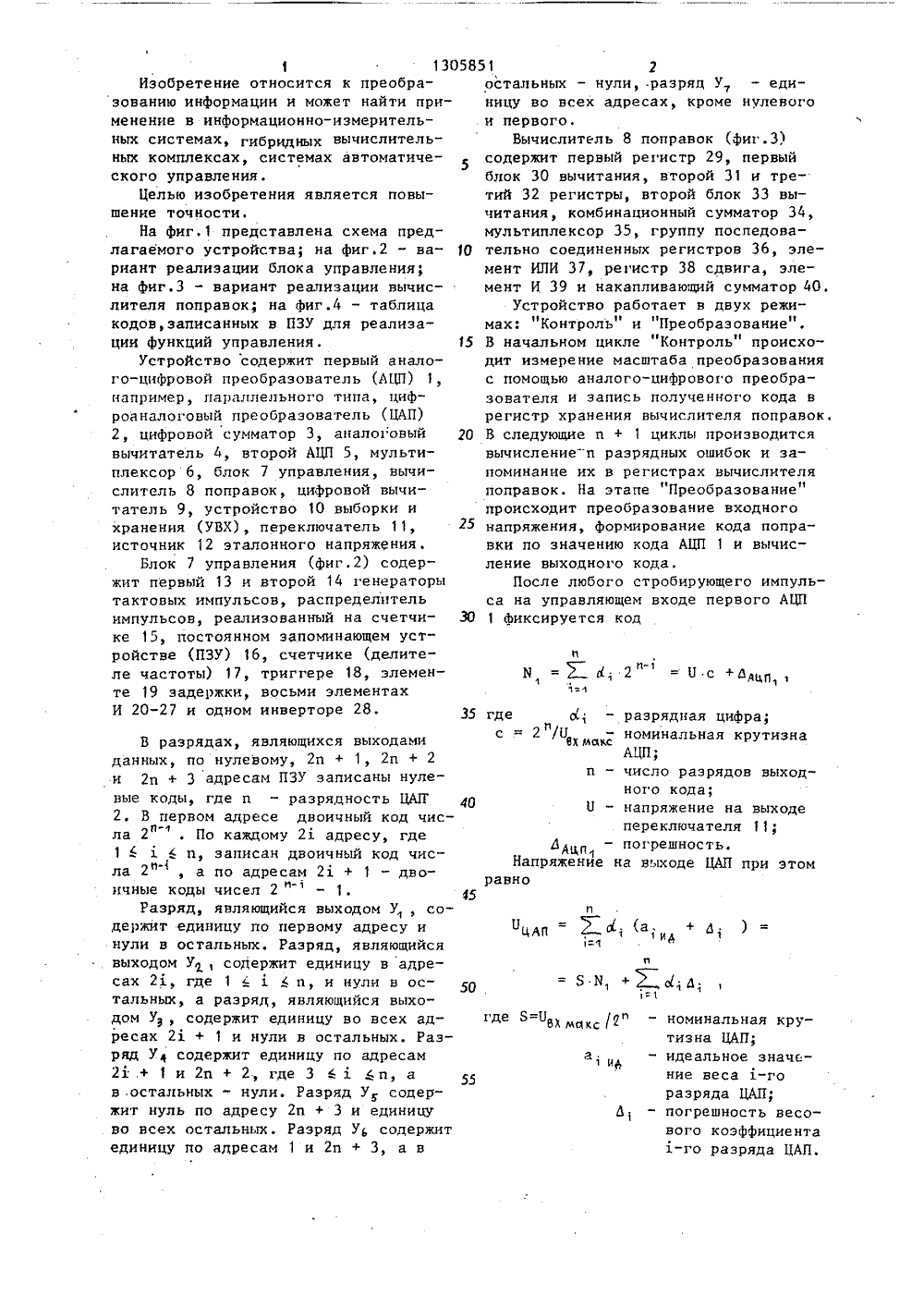

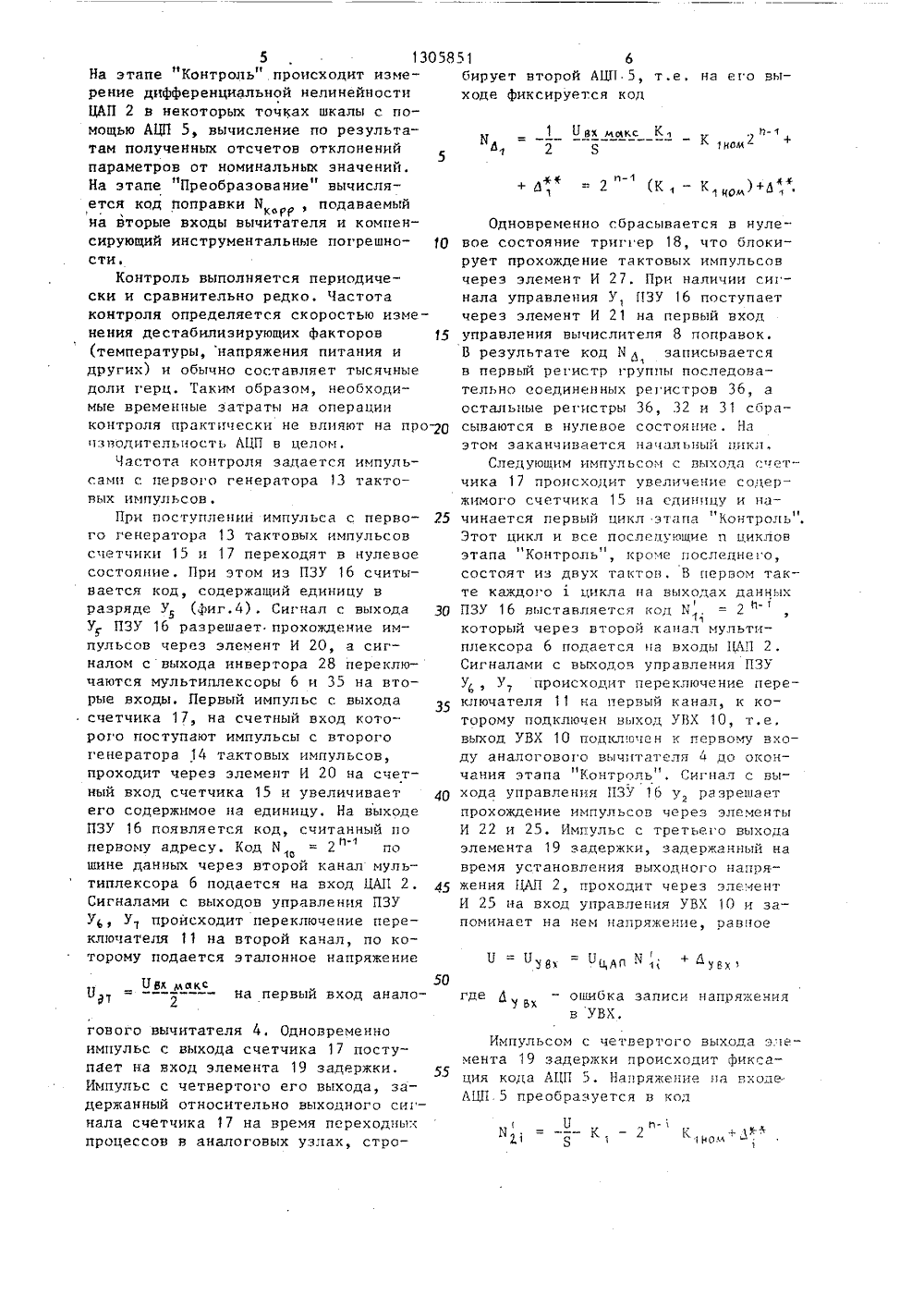

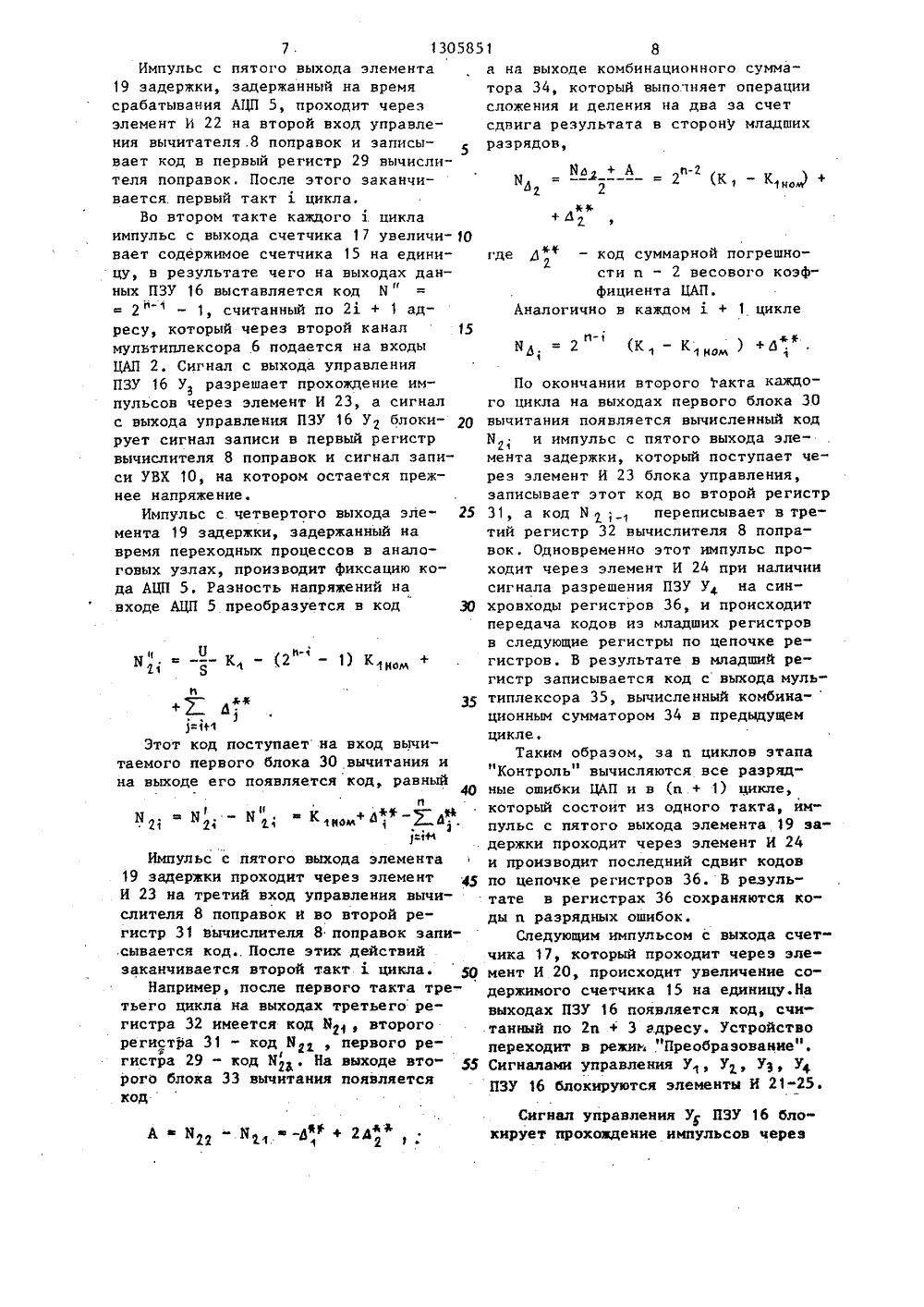

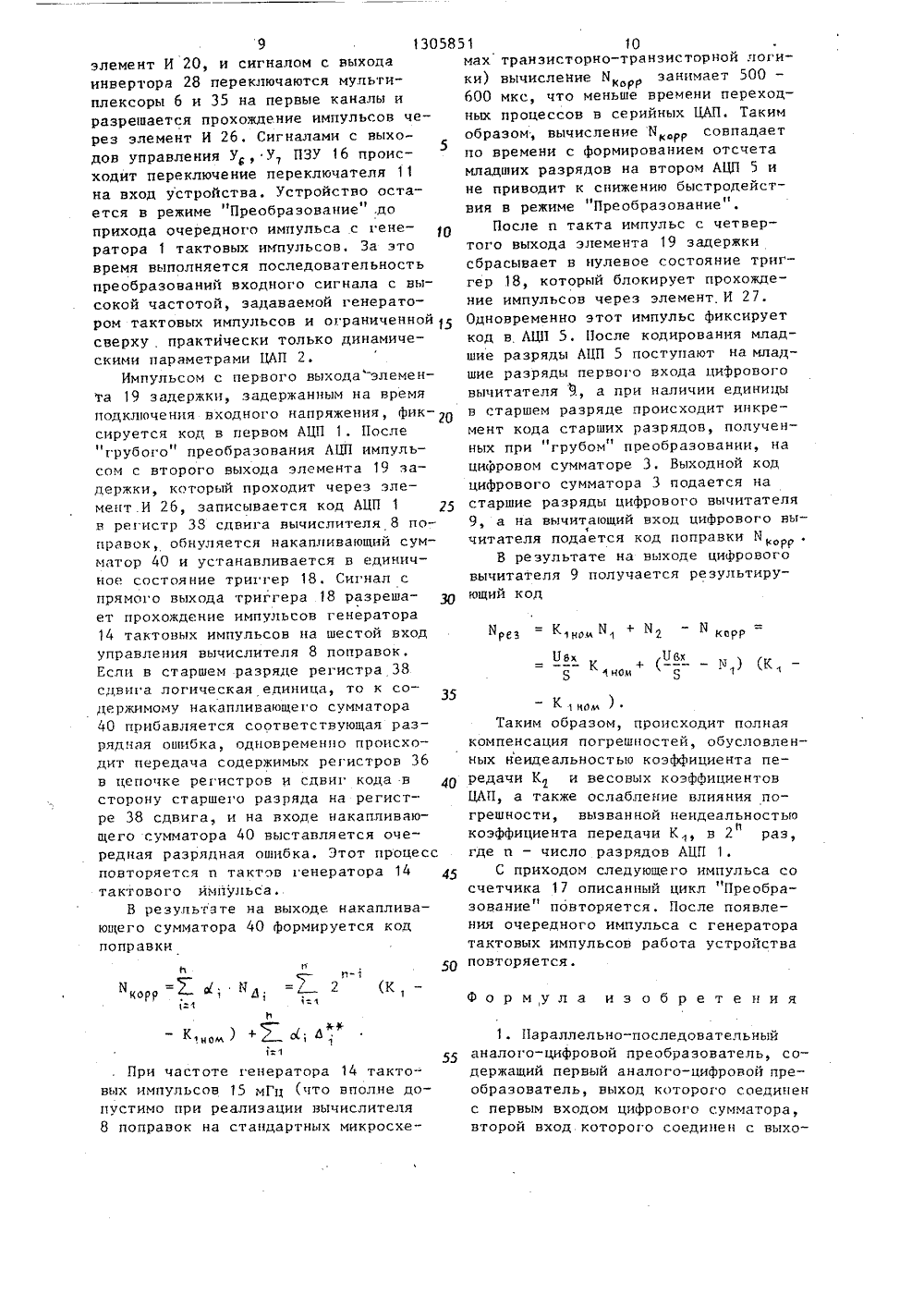

(56) Электроник Бюл.15кий электротехничеИ,ульянова (Ленинав, Р.И.Грушвицкий, ,Х.Мурсаев 8,8)а, 1981, 9 19, ст.Бе Преоб ля маль 1982, Кондалев А,И. и ли формы информации - Киев: Наукова дум3 эовате- ЭВМ..48-49,ЛЬбразо- примеельных льных УДАРСТВЕННЪЙ НОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЪТИЙ СКОМУ СВИДЕТЕЛЬСТВ(54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТ (57) Изобретение касается пре вания информации и может найт нение в информационно-измерит системах, гибридных вычислите комплексах, системах автоматического управления, Цель изобретения " повышение точности. Существенным отличием предлагаемого преобразователя от известных является применение цифровой коррекции результатов преобразования по резальтатам контрольных измерений, реализуемых за счет введения в преобразователь, состоящий из аналого-цифровых преобразователей, цифроаналогового преобразователя, цифрового сумматора, аналогового вычитателя, дополнительных блоков мультиплексора, блока управления, вычислителя поправок, цифрового вычитателя, устройства выборки и хранения, переключателя, источника эталонного ф напряжения, что обеспечивает существенное (в десять и более раз) повышение точности при его работе в ши- (, роком температурном диапазоне, 2 э.п. Ф-лы, 4 ил.130585 ставитель В,Махнанхред В.Кравчук Корректор М.Демчик колайчук едакт Тирах 902осударственного комитета С лам изобретений и открытий Москва, Ж, Раущская наб одписное Заказ НИИП 4 303 ктная 4 изводственно-полиграфическое предприятие, г.уагород35 где с; - разрядная цифра; с = 2 /П - номинальная крутизна ВХ макс АЦП; и - число разрядов выходного кода; Ц - напряжение на выходе переключателя 11; ДАп - погрешность,Напряжение на выходе ЦАП при этом равно(а. + а ) 1 Ид 11Б И ЦЬХ макс / номинальная крутизна ЦАП;идеальное значение веса Э.-го разряда ЦАП;погрешность весового коэффициента -го разряда ЦАП.13058Изобретение относится к преобразованию информации и может найти применение в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматического управления.Целью изобретения является повышение точностиНа фиг,1 представлена схема предлагаемого устройства; на фиг.2 - ва риант реализации блока управления; на фиг.З - вариант реализации вычислителя поправок; на Фиг.4 - таблица кодов, записанных в ПЗУ для реализации функций управления. 5Устройство содержит первый аналогоо-цифровой преобразователь (ЛЦП) 1, например, параллельного типа, цифроаналоговый преобразователь (ЦАП) 2, циФровой сумматор 3, аналоговый 20 вычитатель 4, второй АЦП 5, мультиплексор б, блок 7 управления, вычислитель 8 поправок, цифровой вычитатель 9, устройство 10 выборки и хранения (УВХ), переключатель 11, 25 источник 12 эталонного напряжения.Блок 7 управления (Фиг.2) содержит первый 13 и второй 14 генераторы тактовых импульсов, распределитель импульсов, реализованный на счетчи ке 15, постоянном запоминающем устройстве (ПЗУ) 16, счетчике (делителе частоты) 17, триггере 18, элементе 19 задержки, восьми элементах И 20-27 и одном инверторе 28. В разрядах, являющихся выходами данных, по нулевому, 2 и + 1, 2 и + 2 и 2 и + 3 адресам ПЗУ записаны нулевые коды, где и - разряцность ЦАП 2. В первом адресе двоичный код чисЛ ла 2 . По каждому 2 х адресу, где 1 6и, записан двоичный код числа 2 , а по адресам 2 х + 1 - двоичные коды чисел 2- 1.15Разряд, являющийся выходом У, содержит единицу по первому адресу и нули в остальных. Разряд, являющийся выходом У 1 1 содержит единицу в адресах 21, где 1х с и, и нули в остальных, а разряд, являющийся выходом У, содержит единицу во всех адресах 2 х + 1 и нули в остальных. Разряд У содержит единицу по адресам 21,+ 1 и 2 и + 2, где 3 с х (и, а в .остальных - нули. Разряд У содержит нуль по адресу 2 и + 3 и единицу во всех остальных. Разряд Уь содержит единицу по адресам 1 и 2 и + 3, а в 51 2остальных - нули, .разряд У - единицу во всех адресах, кроме нулевого и первого.Вычислитель 8 поправок (фиг.З) содержит первый регистр 29, первый блок 30 вычитания, второй 31 и третий 32 регистры, второй блок 33 вычитания, комбинационный сумматор 34, мультиплексор 35, группу поспедовательно соединенных регистров 36, элемент ИЛИ 37, регистр 38 сдвига, элемент И 39 и накапливающий сумматор 40.Устройство работает в двух режимах: "Контроль и "Преобразование". В начальном цикле "Контроль" происходит измерение масштаба преобразования с помощью аналого-цифрового преобразователя и запись полученного кода в регистр хранения вычислителя поправок, В следующие и + 1 циклы производится вычисление и разрядных ошибок и запоминание их в регистрах вычислителя поправок. На этапе "Преобразование" происходит преобразование входного напряжения, Формирование кода поправки по значению кода АЦП 1 и вычисление выходного кода.После любого стробирующего импульса на управляющем входе первого АЦП 1 фиксируется код П3 1305851 4На выходе вычитателя формируется читателя, число, представленное кодом; напряжение на первых входах вычитателя, равноАЦП 21 ЦАП 2111 с 1К 1(П Я 1 8) (К 1 К 2)х Я,С Ы., 2 -К 2.сСд 1 Ю1-1где К 1 и К 2 - коэффициенты передачи вычитателя по инвертирующему и неинвертирующему входам соответственно, причем для правильной работы уст ройства следует принятьа номинальное значение К 1 ом Должно 20 быть равно целой степени двойки, например"1 ном25где и - число разрядов АЦП 5.Обозначив суммарную ошибку,обусловленную влиянием неидеальности задания а. и неравенством коэффициентов передачи вычитателя по разным входам, какд-(К -К) 82" -К д., 1 2 2 1запишем3511Бдцп = К(П Я Я) + . д+,1 в 1Код на выходе АЦП 1 равен40Я 2цдо с Дд 1 ППусть с = 1/8 (при других соотношениях получаются аналогичные результаты, если соответствующим образом изменить К 2).ТогдаЯ " К (П/8 - Я ) + -7 Ы.д. д8 1 1 ЯЮ 5 О%Код, поступающий на первые входы вычитателя 9, состоит из двух групп иразрядов с выходов второго АЦП .5, являющихся младшими разрядами ко да и кода суммы выходного кода первого АЦП 1 и старшего. разряда второго АЦП 5. Учитывая позиции этих групп в разрядной сетке кода на входах,вы Я + "-КЯ +КП8 1 1-К) 2п 1 д К 1БТак как Д фц 11 не превышает еди ницы с младшего разряда кода Я 2 и соответственно Я , , а Я , , ш = 2 " 1 , где обычно и равно 6 или 8, то относительная погрешность, вносимая Д щв,п в результат преобразова 5ния, пренебрежимо мала и в дальнейшем Д 1 пренебрегаем, Д А 1также не влйяет на результат преобразования, если только величина Д ,я 8 КАМ 1 не превышает допустимого диайазона входных сигналов АЦП 5.Таким образом, если переключатель 11 коммутирует на вход первого АЦП 1 входной сигнал О По , код на первом входе вычитателя 9 представляет число, отличающееся от идеального значения на величину, зависящую от этого кода и инструментальных погревностей устройства, т.е. ошибок задания коэффициентов К , К 2 и а 2. Для компенсации этих погрешйостей на вторых входах вычитателя 9 должен формы" роваться код, равныйКор Д К 1 8о 1 11=2Работа АЦП подразделяется на два этапа - "Контроль" и "Преобразование",51 6бирует второй АЦП.5, т.е. на ега выходе фиксируется кад 1 Би макс И М К 2 +2 Б1 НОМ Ох ЦАП 1 уьхПвк макс 50 Б = ----- на первый вход анала- где- ошибка записи напряжения ут УЬх в УВХ, говаго вычитателя 4. Одновременноимпульс с выхода счетчика 17 поступает на вход элемента 19 задержки.Импульс с четвертого ега выхода, задержанный относительно выходного сигнала счетчика 17 на время переходныхпроцессов в аналоговых узлах, страИмпульсом с четвертага выхода элемента 19 задержки происходит фиксация кода АЦП 5, Напряжение на вхаде- АЦП.5 преобразуется в кад Б5 . 13058 На этапе Контроль" происходит измерение дифференциальной нелинейности ЦАП 2 в некоторых точках шкалы с помощью АЦП 5, вычисление по результатам полученных отсчетов отклонений параметров от номинальных значений.На этапе "Преобразование" вычисляется код поправки Ик, , подаваемый иа вторые входы вычитателя и компенсирующий инструментальные погрешно сти.Контроль выполняется периодически и сравнительно редко. Частота контроля определяется скоростью изменения дестабилизирующих факторов 15 (температуры, напряжения питания и других) и обычно составляет тысячные доли герц. Таким образом, необходимые временные затраты на операции контроля практически не влияют на праизвадительнасть АЦП в целом.Частота контроля задается импульсами с первого генератора 13 тактов Летх ИГ 1 пульсавПри поступлении импульса с перво га генератора 13 тактовых импульсов счетчики 15 и 17 переходят в нулевое состояние. При этом из ПЗУ 16 считывается кад, содержащий единицу вразряде У (фиг.4). Сигнал с выхода 30 У ПЗУ 16 разрешает прохождение импульсов через элемент И 20, а сигналом свыхода инвертара 28 переключаются мультиплексоры 6 и 35 на вторые входы. Первый импульс с выхода счетчика 17, на счетный вход которого поступают импульсы с второго генератора 14 тактовых импульсов, проходит через элемент И 20 на счетный вход счетчика 15 и увеличивает щ его содержимое на единицу. На выходе ПЗУ 16 появляется кад, считанный па первому адресу. Код Я = 2" па шине данных через второй канал мультиплексора 6 падается на вход ЦАП 2, д 5 Сигналами с выходов управления ПЗУ Ус, Ут происходит переключение переключателя 11 на второй канал, по которому подается эталонное напряжение Одновременно сбрасывается в нулевое состояние триггер 18, чта блокирует прохождение тактовых импульсов через элемент И 27. При наличии сиг - нала управления У, ПЗУ 16 поступает через элемент И 21 на первый вход управления вычислителя 8 поправок, В результате кад 11 А записывается в первый регистр группь последовательно соединенных регистров 36, а остальные регистры 36, 32 и 31 сбрасываются в нулевое состояние . Нд этом заканчивается начдльный пики,Следующим импульсом с выхадд с летчика 17 происходит увеличение содержимого счетчика 15 на единицу и начинается первый цикл этдпа Контроль . Этот цикл и все последующие и циклов этапа Контроль , кроме последнего, состоят из двух тактов. В нервам такте каждого д цикла на выходах данныхт - 1"ПЗУ 16 выставляется кад 11 . = 2 " который через второй канал мультиплексора 6 подается иа входы ЦАП 2, Сигналами с выходов управления ПЗУ У, У происходит переключение переключателя 11 нд первый канал, к которому подключен выход УВХ 10, т.е. выход УВХ 10 подключен к первому входу аналогового вычитдтеля 4 да окончания этапа Кантрольтт, Сигнал с выхода управления ПЗУ 16 у, разрешает прохождение импульсов через элементы И 22 и 25. Импульс с третьего выхода элемента 19 задержки, задержанный на время установления выходного напряжения ЦАП 2, проходит через элемент И 25 на вход управления УВХ 10 и запоминает на нем напряжение, равное7 130585Импульс с пятого выхода элемента 19 задержки, задержанный на время срабатывания АЦП 5, проходит через элемент И 22 на второй вход управления вычитателя .8 поправок и записы 5 вает код в первый регистр 29 вычислителя поправок. После этого заканчивается. первый тактцикла.Во втором такте каждого 1. цикла импульс с выхода счетчика 17 увеличи О вает содержимое счетчика 15 на единицу, в результате чего на выходах данных ПЗУ 16 выставляется код М "2 " " - 1, считанный по 21 + 1 адресу, который через второй канал 15 мультиплексора 6 подается на входы ЦАП 2. Сигнал с выхода управления ПЗУ 16 У разрешает прохождение им 3пульсов через элемент И 23, а сигнал с выхода управления ПЗУ 16 У блоки рует сигнал записи в первый регистр вычислителя 8 поправок и сигнал записи УВХ 10, на котором остается прежнее напряжение.Импульс с четвертого выхода эле мента 19 задержки, задержанный на время переходных процессов в аналоговых узлах, производит фиксацию кода АЦП 5, Разность напряжений на входе АЦП 5 преобразуется в код 30 8 К - (2 - 1) ном + ьФ% 351фМЭтот код поступает на вход вычитаемого первого блока 30 вычитания и на выходе его появляется код, равный40нй Н .: И, - Н, - К +,1 дн21 2 Й 1 180 мрМИмпульс с пятого выхода элемента 19 задержки проходит через элемент 45 И 23 на третий вход управления вычислителя 8 поправок и во второй регистр 31 вычислителя 8 поправок запи.сывается код После этих действий заканчивается второй такт ь цикла. 50Например, после первого такта третьего цикла на выходах третьего регистра 32 имеется код 0, второго регистра 31 - код Я , первого регистра 29 - код Я . На выходе вто рого блока 33 вычитания появляется код 1 8а на выходе комбинационного сумматора 34, который выполняет операциисложения и деления на два за счетсдвига результата в сторону младшихразрядов,Йа + А о 2М = -- = 2 (К К +21 1 ном где Дф - код суммарной погрешности и - 2 весового коэф"фициента ЦАП.Аналогично в каждом д + 1 цикле По окончании второго 1 акта каждого цикла на выходах первого блока 30вычитания появляется вычисленный кодН; и импульс с пятого выхода элемента задержки, который поступает через элемент И 23 блока управления,записывает этот код во второй регистр31, а код И ;переписывает в третий регистр 32 вычислителя 8 поправок. Одновременно этот импульс проходит через элемент И 24 при наличиисигнала разрешения ПЗУ У на синхровходы регистров 36, и происходитпередача кодов из младших регистровв следующие регистры по цепочке регистров. В результате в младший регистр записывается код с выхода мультиплексора 35, вычисленный комбина-ционным сумматором 34 в предыдущемцикле,Таким образом, за п циклов этапа"Контроль" вычисляются все разрядные ошибки ЦАП и в (и + 1) цикле,который состоит из одного такта, импульс с пятого выхода элемента 19 задержки проходит через элемент И 24и производит последний сдвиг кодовпо цепочке регистров 36. В результате в регистрах 36 сохраняются коды и разрядных ошибок.Следующим импульсом с выхода счетчика 17, который проходит через элемент И 20, происходит увеличение содержимого счетчика 15 на единицу.Навыходах ПЗУ 16 появляется код, считанный по 2 п + 3 адресу, Устройствопереходит в режим ."Преобразование".Сигналами управления У, У, У, УПЗУ 16 блокируются элементы И 21-25.АЯ " Я"Д + 2 йф 22 Й 1 1 2 Сигнал управления У ПЗУ 16 блокирует прохождение импульсов через05851 1 Омах транзисторно-транзисторной логики) вычисление М занимает 500 -600 мкс, что меньше времени переходных процессов в серийных ЦАП. Такимобразом, вычисление И, совпадаетпо времени с формированием отсчетамладших разрядов на втором АЦП 5 ине приводит к снижению быстродействия в режиме "Преобразование".После и такта импульс с четвертого выхода элемента 19 задержкисбрасывает в нулевое состояние триггер 18, который блокирует прохождение импульсов через элемент, И 27. 5 Одновременно этот импульс фиксируеткод в АЦП 5. После кодирования младшие разряды АЦП 5 поступают на младшие разряды первого входа цифровоговычитателя Ъ, а при наличии единицыв старшем разряде происходит инкремент кода старших разрядов, полученных при "грубом" преобразовании, нацифровом сумматоре 3. Выходной кодцифрового сумматора 3 подается на 25 старшие разряды цифрового вычитателя9, а на вычитающий вход цифрового вычитателя подается код поправки И,В результате на выходе цифровоговычитателя 9 получается результирующий код 50 лЫорр Е о(, И,9 13 элемент И 20, и сигналом с выхода инвертора 28 переключаются мупьтиплексоры 6 и 35 на первые канапы и разрешается прохождение импульсов через элемент И 26. Сигналами с выходов управления У, У, ПЗУ 6 происходит переключение переключателя 11 на вход устройства, Устройство остается в режиме "Преобразование" .до прихода очередного импульса с генератора 1 тактовых импульсов, За это время выполняется последовательность преобразований входного сигнала с высокой частотой, задаваемой генератором тактовых импульсов и ограниченной сверху практически только динамическими параметрами ЦАП 2.Импульсом с первого выхода элемента 19 задержки, задержанным на время подключения входного напряжения, фиксируется код в первом АЦП 1. После "грубого" преобразования АЦП импульсом с второго выхода элемента 19 задержки, который проходит через элемент.И 26, записывается код АЦП 1 в регистр 38 сдвига вычислителя 8 поправок, обнуляется накапливающий сумматор 40 и устанавливается в единичное состояние триггер 18. Сигнал с прямого выхода триггера 18 разрешает прохождение импульсов генератора 14 тактовых импульсов на шестой вход управления вычислителя 8 поправок. Если в старшем разряде регистра 38 сдвига логическая единица, то к содержимому накапливающего сумматора 40 прибавляется соответствующая разрядная ошибка, одновременно происходит передача содержимых регистров 36 в цепочке регистров и сдвиг кода в 40 сторону старшего разряда на регистре 38 сдвига, и на входе накапливающего сумматора 40 выставляется очередная разрядная ошибка. Этот процесс повторяется п тактов генератора 14 45 тактового импульса.В результате на выходе накапливающего сумматора 40 формируется код поправки 11 рбз 1 ном 111 2корр Кном )Таким образом, происходит полная компенсация погрешностей, обусловленных неидеальностью коэффициента передачи К 2 и весовых коэффициентов ЦАП, а также ослабление влияния погрешности, вызванной неидеальностью коэффициента передачи К, в 2" раз, где и - число разрядов АЦП 1.С приходом следующего импульса со счетчика 17 описанный цикл "Преобра 11зование повторяется. После появления очередного импульса с генератора тактовых импульсов работа устройства повторяется. Формула изобретенияКсном ) сПри частоте генератора 14 тактовых импульсов 15 м"ц (что вполне допустимо при реализации вычислителя 8 поправок на стандартных микросхе 1. Параллельно-последовательный аналого-цифровой преобразователь, содержащий первый аналого-цифровой преобразователь, выход которого соединен с первым входом цифрового сумматора, второй вход которого соединен с выхо1305851 12 10 20 35 40 45 55 дам старшего разряда второго аналога-цифрового преобразователя, входкоторого подключен к выходу аналогового вычитателя, первый вход которого объединен с,информационным входомпервого аналого-цифрового преобразователя, а второй вход соединен с выходом циФроаналогового преобразователя, о т л и ч а ю щ и й с я тем,что, с целью повышения точности, внего введены источник эталонного напряжения, устройство выборки и хранения, переключатель, мультиплексор, вычислитель поправок, цифровойвычитатель и блок управления, информационный выход которого соединен спервым информационным входом мультиплексора, второй информационный входкотарога соединен с выходом первогоаналого-цифрового преобразователя иобъединен с первым информационнымвходом вычислителя поправок, выходподключен к входу цифроаналоговогопреобразователя, адресный вход объединен с первым управляющим входомвычислителя поправок и подключен кпервому управляющему выходу блокауправления, второй управляющий выходкоторого соединен с входом синхронизации первого аналого-цифрового преобразователя, третий уйравляющий выход - с входом синхронизации второго аналого-цифрового преобразователя, выход младших разрядов которогосоединен с вторым информационнымвходом вычислителя поправок и подключен к входам первой группы входов цифровага вычитателя, входы старших разрядов которого подключены квыходам цифравага сумматора соответственно, а вторая группа входов цифрового вычитателя подключена к выходу вычислителя поправок, управляющиевходы которого с второго по седьмойсоединены с соответствующими управляющими вьгхадами с четвертого па девятый блока управления, десятый управляющий выход которого подключен куправляющему входу устройства выборки и хранения, одиннадцатый управляющий выход - к управляющему входу переключателя, первый информационныйвход которого соединен с выходом устройства выборки и хранения, второйинформационный вход - с выходом истачника эталонного напряжения, третийинформационный вход является шинойпреобразуемого сигнала, а выход подключен к информационному входу первага аналога-цифрового преобразователя, причем выход цифровсго вычитателя является выходной шиной устройства, а информационный вход устройства выборки и хранения ссединен с выходом цифроаналогового преобразователя.2. Преобразователь по п.1, о т - л и ч а ю щ и й с я тем, что вычислитель поправок выполнен на трех регистрах, двух блоках вычитания, комбинационном и накапливающем сумматорах, мультиплексоре, регистре сдвига, элементах И и ИЛИ, группе последовательно соединенных регистров, первый информационный вход первого иэкоторых объединен с первым входомпервого блока вычитания и информационным входом первого регистра иявляется вторым управляющим входомвычислителя, выход соединен с вторымвходом первого блока вычитания, выход которого соединен с информационным входом второго регистра, выход 25. которого соединен с информационным входом третьего регистра и первымвходом второго блока вычитания, входы синхронизации второго и третьегорегистров объединены и являются тре 30 тьим управляющим входом вычислителя, второй вход второго блока вычитания соединен с выходом третьего регистра, а выход - с первым входом комбинационного сумматора, второй вход которого подключен к выходу первого регистра группы последовательно соединенных регистров, а выход соединен с первым инФормационнымвходом мультиплексора, второй информационный вход которого объединен синформационным входом накапливающегосумматора и соединен с выходом последнего регистра группы последовательно соединенных регистров, аадресный вход является пятым управляющим входом вычислителя, второй информационный вход первого из группы последовательно соединенных регистров соединен с выходом муль 50 типлексора, первый вход синхрониэации объединен с входами сброса всехостальных регистров группы cаследоватепьна соединенных регистров, свходами сброса второго и третьего регистров и является первым управляющим входом вычисиителя, второй входсинхронизации объединен с входами синхронизации остальных регистров группы последовательно соединенных ре 13 13 гистров и подключен к выходу элемента ИЛИ, первый вход которого является четвертым управляющим входом вычислителя, второй вход объединен с первым входом эпемента И и первым входом синхронизации регистра сдвига и является шестым управляющим входом вычислителя, вход управления записью параллельного кода регистра сдвига объединен с входом сброса накапливающего сумматора и является седьмым управляющим входом вычислителя, информационный вход является первым информационным входом вычислителя, а выход старшего разряда соединен с вторым входом элемента И, выход которого подключен к входу синхронизации накапливающего сумматора, выход которого является выходом вычислите- ляв 3. Преобразователь по п. 1, о т - л и ч а ю щ и й с я тем, что блок управления выполнен на двух счетчиках, элементе задержки, восьми эле. ментах И, постоянном запоминающем устройстве, инверторе,триггере двух генераторах тактовых импульсов, выход первого из которых соединен с входами сброса первого и второго счетчиков, выход второго генератора тактовых импульсов соединен с входом синхронизации первого счетчика, выход переполнения которого подключен к входу элемента задержки и первому входу первого элемента И, выход ко-, торого соединен с входом синхронизации второго счетчика, выход которого подключен к адресному входу постоянного запоминающего устройства, управляющие выходы которого с первого по 05851 14четвертый соединены с первыми входами соответствующих элементов И свторого по пятый, вторые входы которых объединены и подключены к первому выходу элемента задержки, а выходыявляются соответственно четвертым,пятым, шестым и седьмым управляющимивыходами блока, пятый управляющий выход постоянного запоминающего устройо10 ства соединен с вторым входом первогоэлемента И, через инвертор подключенк первому входу шестого элементаИ и является первым управляющим выходом блока, шестой .управляющий выходс,5 постоянного запоминающего устройстваявляется одиннадцатым управляющим выхОдом блока, информационный выход постоянного запоминающего устройстваявляется информационным выходом бло 20 ка, второй выход элемента задержкиявляется вторым управляющим выходомблока, третий выход соединен с вторымвходом шестого элемента И, выход которого соединен с входом установки25триггера и является восьмым управляющим выходом блока, четвертый выходэлемента задержки соединен с первымвходом седьмого элемента И, второйвход которого подключен к второму30 управляющему выходу, постоянного запоминающего устройства, а выхоц является девятым управляющим выходомблока, пятый выход элемента задержки соединен с входом сброса тригге 35 ра и является третьим управляющим выходом блока, выход триггера соединенс первым входом восьмого элемента И,второй вход которого подключен к выходу второго генератора тактовых им 40 пульсов, а выход является десятымуправляющим выходом блока, 1305851

СмотретьЗаявка

3898178, 17.05.1985

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ВОРОТОВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ГРУШВИЦКИЙ РОСТИСЛАВ ИГОРЕВИЧ, МОГНОНОВ ПЕТР БОРИСОВИЧ, МУРСАЕВ АЛЕКСАНДР ХАФИЗОВИЧ, СМОЛОВ ВЛАДИМИР БОРИСОВИЧ

МПК / Метки

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 23.04.1987

Код ссылки

<a href="https://patents.su/11-1305851-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Преобразователь угла поворота вала в код

Следующий патент: Аналого-цифровой преобразователь

Случайный патент: 86585