Устройство для вычисления логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

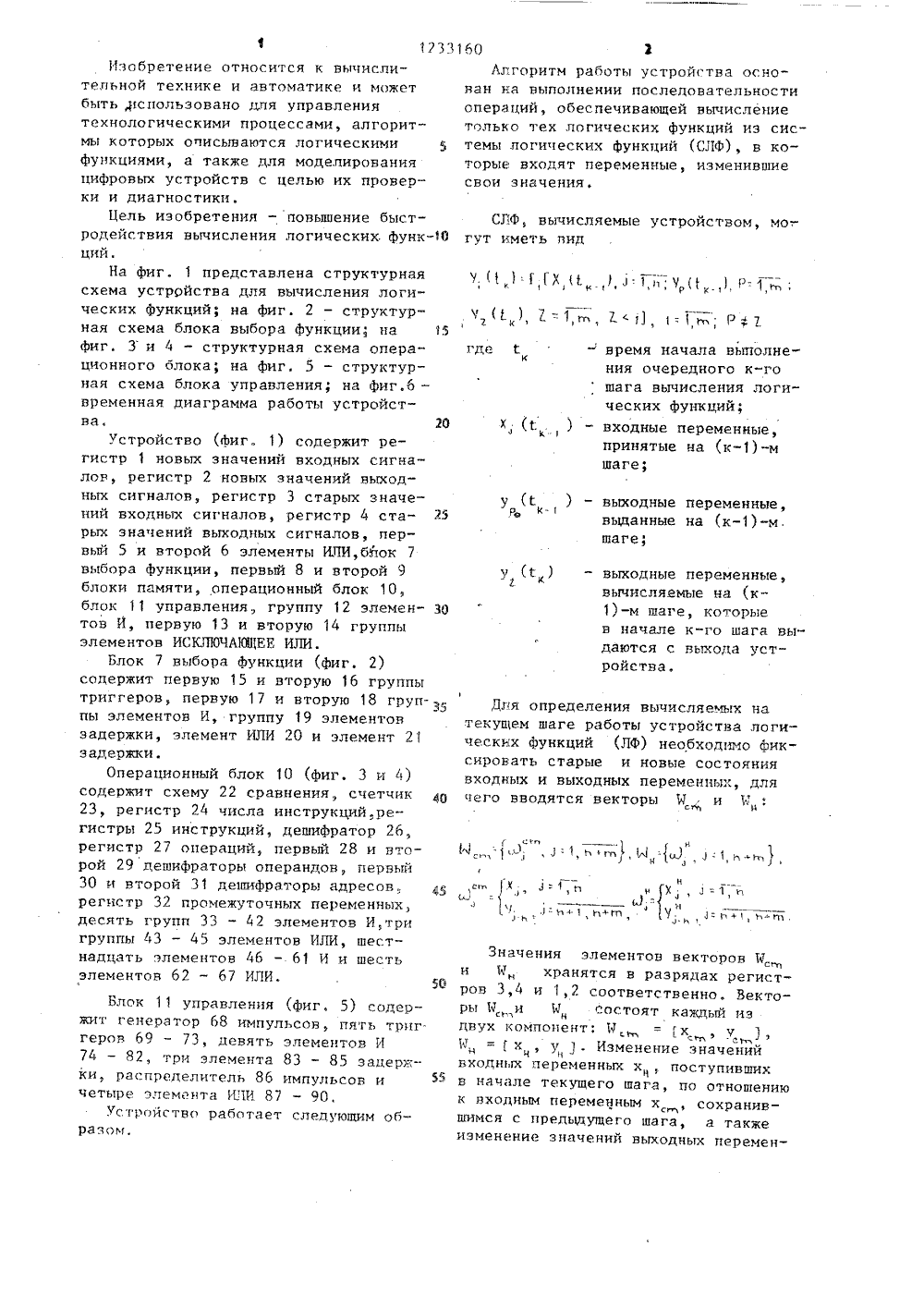

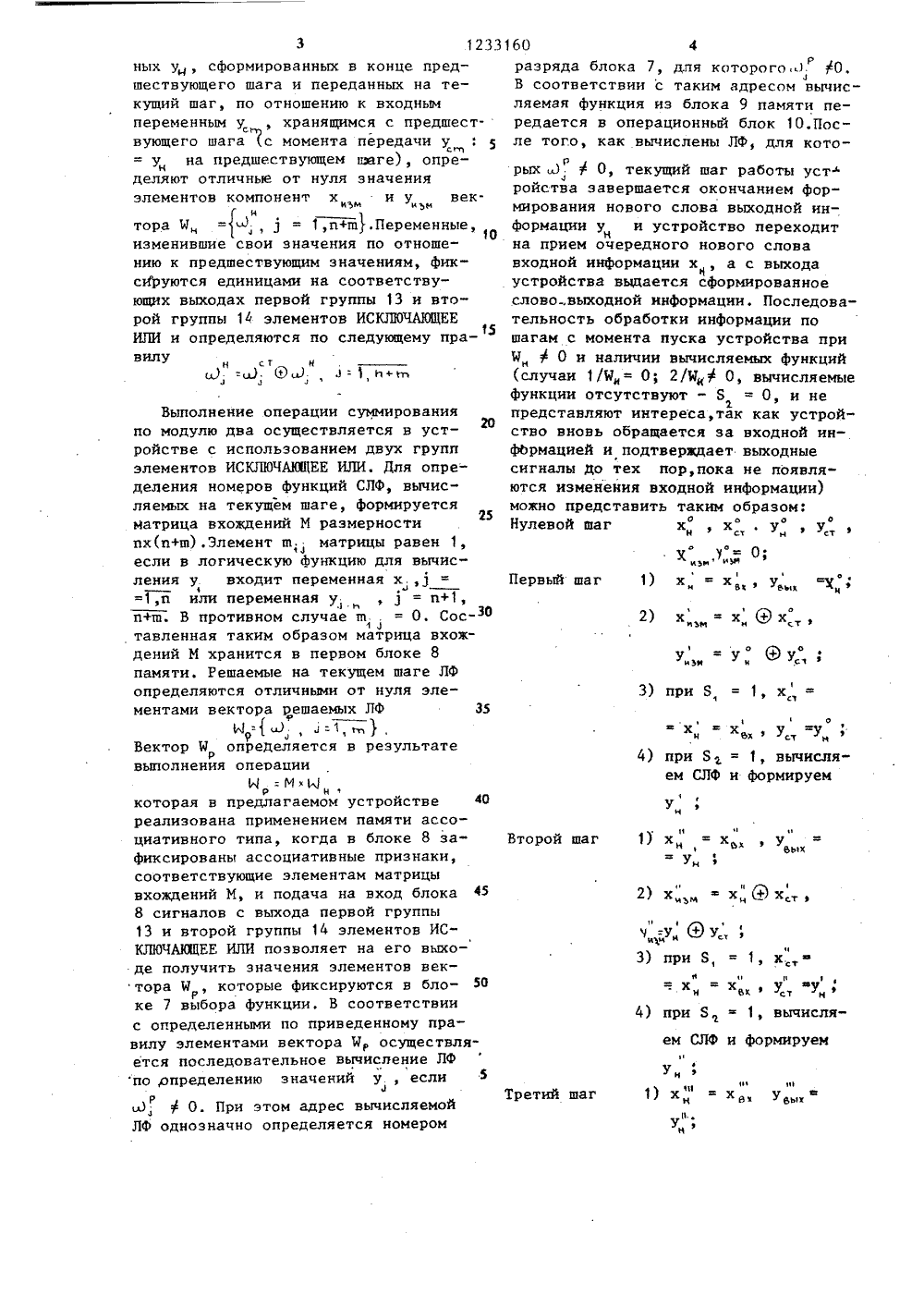

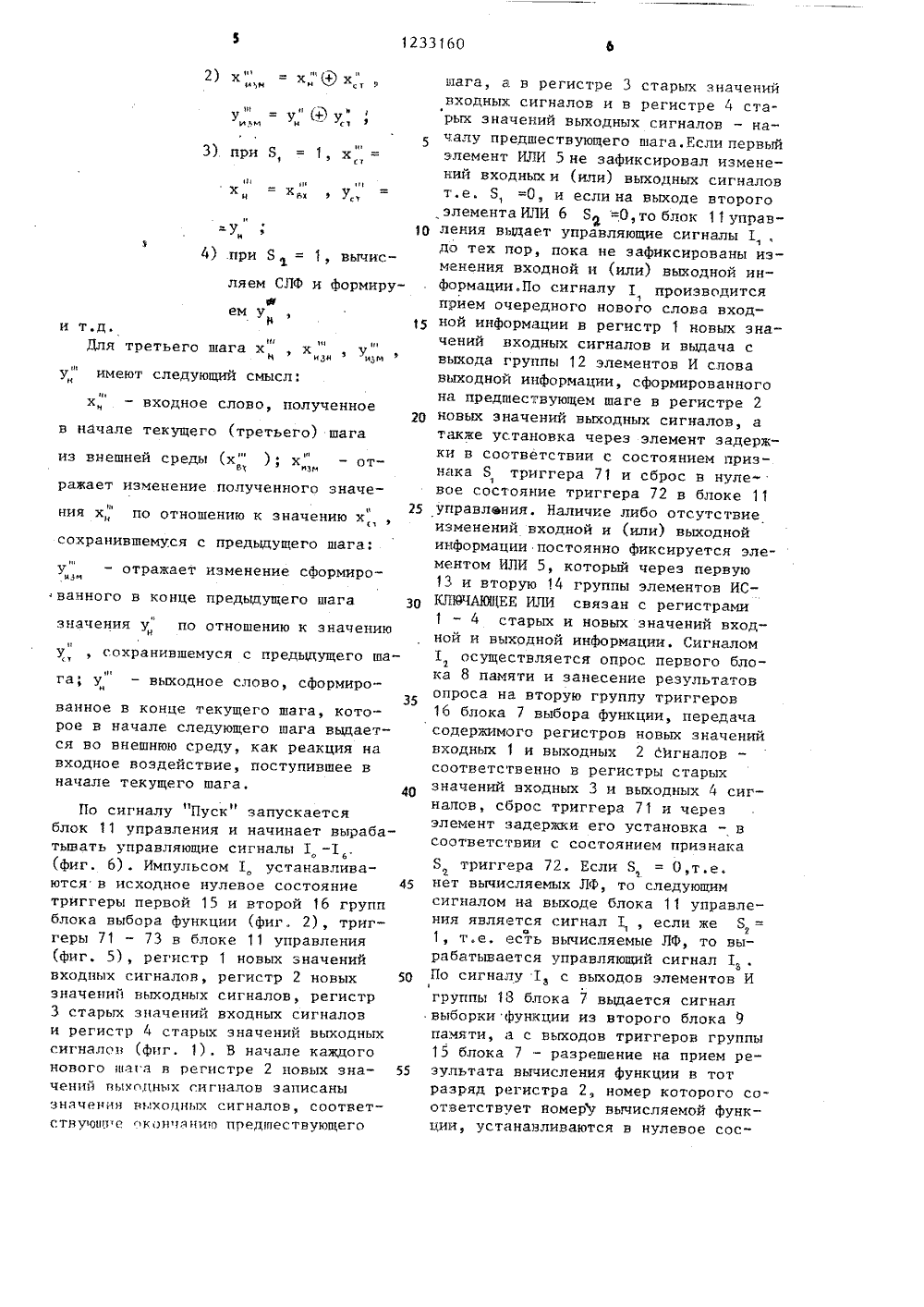

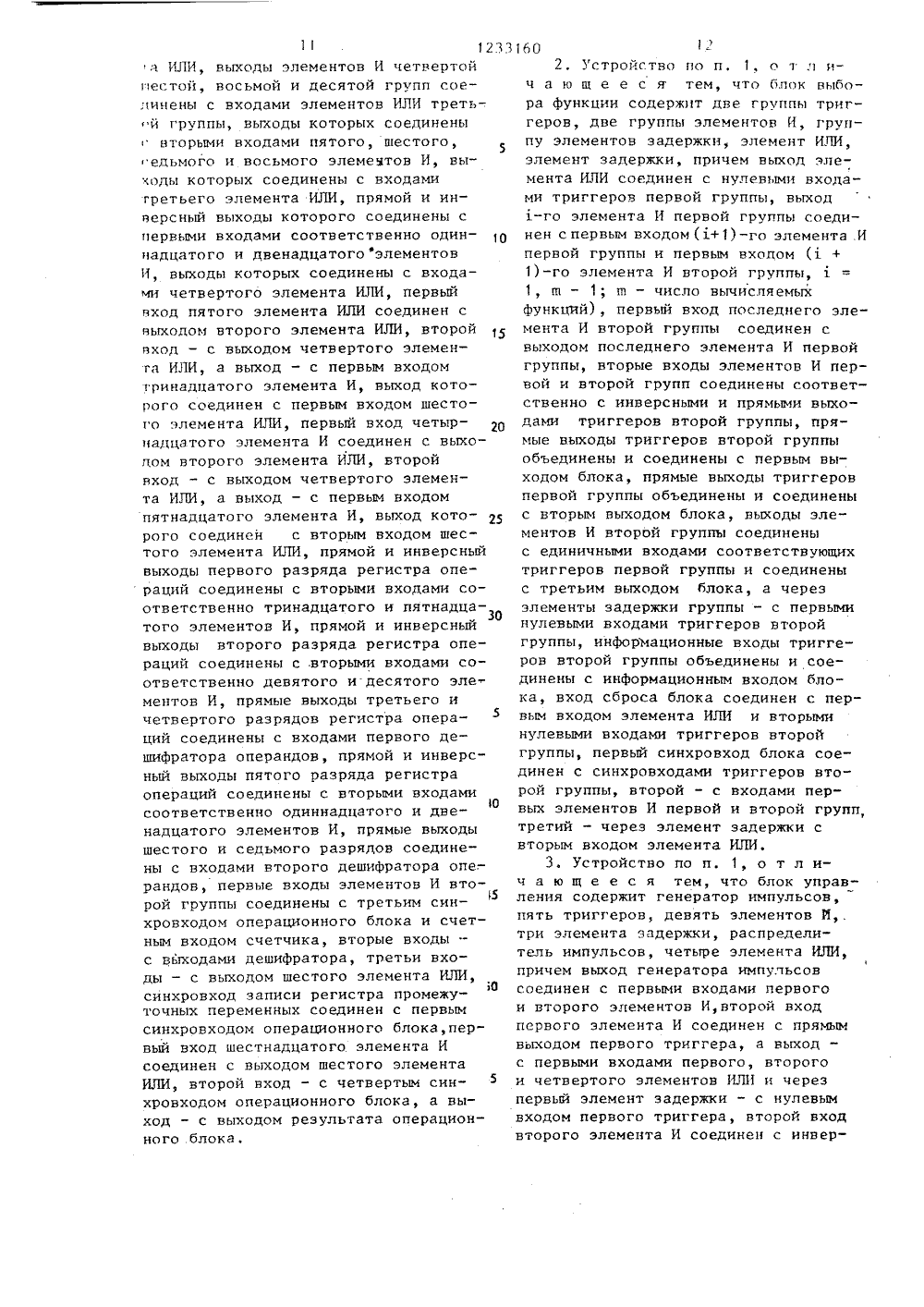

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 11% (11) 04 С 06 Р 15/2 ГОСУД АРС ПО ДЕЛА О Е СВИДЕТ В.Н АВТОРСН ЕЕННЫЙ КОМИТЕТ СССР ЗОБРетений и ОтнРытий АНИЕ ИЗОБ(56) Авторское свидетельство СССРКф 732878, кл. С 06 Р 15/20, 1980.Авторское свидетельство СССРУ 1164724, кл. С 06 Р .15/20, 1982.(54) УСТРОЙСТВО ДЛЯ,ВЫЧИСЛЕНИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ (57) Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повышение быстродействия. Устрочство представляетсобой сложную структуру включающую такие блоки, как блок выбора функции и блок управления, имеющие специфику в схемном выполнении, характернуюдля решенияданной задачи. Изобретение может быть использовано для управления технологическими процессами алгоритмы которых описываются логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагностики. 2 з.п.ф"лы, 6 ил.1233160 впуск ВьабЭ Вьа 7 Вьа. Я 1 йцЯгьжВи.З 1 Ья 77,ю,Ю г Сос Н.Рогупич Тех251 Тираж б НИИПИ Государствепо делам изобрет 113035, Москва,Подписноеомитета СССРоткрыткой ного нии -35 аушская наб., д. ул. тна изводст Вьм 79 1, дьи 801, Вьи, 81 1 8 Кг , 8 ьУд, 77 73) Вьц. 78 п Вил. 7375 ЗЬИ,Ж 51 ЙЮ. г Бьи.,итель О.МорозО .Садко КорректорЛ.Пилипенко нно-полиграфическое предприятие, г. УжгородИзобретение относится к вычислите,пьной технике и автоматике и может быть использовано для управления технологическими процессами, алгоритмы которых описываются логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагностики.Цель изобретения - повышение быстродействия вычисления логических. ФункО ций.На фиг. 1 представлена структурная схема устррйства для вычисления логических функций; на фиг. 2 - структурная схема блока выбора функции на 15 фиг. 3 и 4 - структурная схема операционного блока; на фиг. 5 - структурная схема блока управления; на фиг.б - временная диаграмма работы устройства. 2 ОУстройство (фиг. 1) содержит регистр 1 новых значений входных сигналов, регистр 2 новых значений вьжодных сигналов, регистр 3 старых значений входных сигналов, регистр 4 ста рьж значений выходных сигналов, пер" вый 5 и второй 6 элементы ИЛИ,блок 7 выбора функции, первый 8 и второй 9 блоки памяти, операционный блок 10, блок 11 управления группу 12 элемен- ЗО тов Й, первую 13 и вторую 14 группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.Блок 7 выбора Функции (Фиг. 2) содержит первую 15 и вторую 16 группы триггеров, первую 17 и вторую 18 груп- пы элементов И, группу 19 элементов задержки, элемент ИЛИ 20 и элемент 21 задержки.Операционный блок 10 (фиг, 3 и 4) содержит схему 22 сравнения счетчик 23, регистр 24 числа инструкций,ре. гистры 25 инструкций, дешифратор 26, регистр 27 операций, первый 28 и второй 29 дешифраторы операндов, первый 30 и второй 31 дешифраторы адресов, регистр 32 промежуточных переменных,. десять групп 33 - 42 элементов И,три группы 43 - 45 элементов ИЛИ, шестнадцать элементов 46 - 61 И и шесть элементов 62 - 67 ИЛИ.ЫБлок 11 управления (фиг. 5) содержит генератор 68 импульсов, пять триг.геров 69 - 3, девять элементов И74 - 82, три элемента 83 - 85 задержки, распределитель 86 импульсов ичетыре элемента ИЛИ 87 - 90,Ус.тройство работает следующим образом, СЛФ, вычисляемые устройством, мо-,гут иметь вид у. ) Е,Г)(,(Е,), д 1,1, у,(,.,), 1,у . ), Е=1,7, у 3, 1=( .тъ, РФ. время начала выполнения очередного к-гошага вычисления логических функций; Х(1:., ) - входные переменные,принятые на (к)-мшаге; где у (С ) - выходные переменные,р К-выданные на (к)-мшаге;- выходные переменные,вычисляемые на (к 1)-м шаге, которыев начале к-го шага выу2 даются с выхода устройства. Для определения вычисляемых на текущем шаге работы устройства логических функций (ЛФ) необходмо фиксировать старые и новые состояния входных и выходных переменных, для чего вводятся векторы М и Ыс 6 1"),-1 . 3.-1,, А .)-.1, ь,) ( Значения элементов векторов У.С и У хранятся в разрядах регистров 3,4 и 1,2 соответственно. Векторы Ь, и У состоят каждый из двух компонент: 1), = х у"-.л ф с, 1, = ( х , у ). Изменение значений входных переменных х, поступивших в начале текущего шага, по отношению к входным переменным х, , сохранившимся с предыдущего шага, а также изменение значений выходных переменАлгоритм работы устройства основан на выполнении последовательности операций, обеспечивающей вычисление только тех логических функций из системы логических функций (СЛФ), в которые входят переменные, изменившие свои значения.Третий шаг ных у сформированных в конце предшествующего шага и переданных на текущий шаг, по отношению к входным переменным у, , хранящимся с предшествующего шага с момента передачи уснап = у на предшествующем ваге), определяют отличные от нуля значения элементов компонент х и у век.иЪм и ЪчНтора И =3 = 1,п+ш.Переменные, изменившие свои значения по отношению к предшествующим значениям, фиксируются единицами на соответствующих выходах первой группы 13 и второй группы 14 элементов ИСКЛЮЧАЮЩЕЕ15 ИЛИ и определяются но следующему правилуН сТ Нсд=оЭ Оаэи), з = 1, и+о Выполнение операции суммированияпо модулю два осуществляется в уст 20ройстве с использованием двух группэлементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Для определения номеров функций СЛФ, вычисляемых на текущем шаге, формируется25матрица вхождений М размерностипх(п+ш).Элемент ш,. матрицы равен 1,если в логическую функцию для вычисления у входит переменная х.,11=1,п или переменная у, , 1 = и+1,и+ш. В противном случае ш = О. Сос-ЗО1тавленная таким образом матрица вхождений М хранится в первом блоке 8памяти. Решаемые на текущем шаге Лфопределяются отличными от нуля элементами вектора решаемых Лф 35и:(, :,Вектор И определяется в результатевыполнения опеоапииИ =Мйкоторая в предлагаемом устройстве 40реализована применением памяти ассоциативного типа, когда в блоке 8 зафиксированы ассоциативные признаки,соответствующие элементам матрицывхождений М, и подача на вход блока 458 сигналов с выхода первой группы13 и второй группы 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ позволяет на его выходе получить значения элементов вектора Ч , которые фиксируются в блоке 7 выбора функции, В соответствиис определенными по приведенному правилу элементами вектора Ир осуществляется последовательное вычисление Лфпо определению значений у , еслииО. При этом адрес вычисляемойЛФ однозначно определяется номером 160 4разряда блока 7, для которого . 0,р В соответствии с таким адресом вычисляемая функция из блока 9 памяти передается в операционный блок 10.После того, как вычислены Лф, для которых ).О, текущий шаг работы уст ройства завершается окончанием формирования нового слова выходной информации у и устройство переходит на прием очередного нового слова входной информации х , а с выходанфустройства выдается сформированное слово, выходной информации. Последовательность обработки информации по шагам с момента пуска устройства при Ы Ф О и наличии вычисляемых функций (случаи 1/Ы= О 2/И, Ф О, вычисляемые функции отсутствуют - Б = О, и не представляют интереса,так как устройство вновь обращается за входной инфбрмацией и подтверждает выходные сигналы до тех пор,пока не появляются изменения входной информации) можно представить таким образом: Нулевой шагПервый шаг 1) х= х, у 1ох хУ Ун Ьх ф ст н 4) при 8 = 1, вычисляем СЛФ и формируем 4) при Я 1, вычисляляем СЛФ и формируйем ув ния х 11=У ф н 4) .при Б = 1, вычис и т.д.Для третьего шага хх, у"м ф идн идму" имеют следующий смысл: х . - входное слово, полученноев начале текущего (третьего) шага из внешней среды (х" ); х" - отвиьм ражает изменение полученного значепо отношению к значению х сохранившемуся с предьдущего шага:у - отражает изменение. сформироМЗмванного в конце предьдущего шага значения у по отношению к значениюНу , сохранившемуся с предьдущего ша 111га; у - выходное слово, сформированное в конце текущего шага, которое в начале следующего шага выдается во внешнюю среду, как реакция навходное воздействие, поступившее вначале текущего шага. По сигналу Пуск запускается блок 11 управления и начинает вырабатывать управляющие сигналы 1, -1,.(фиг, 6). Импульсом 1, устанавливаются в исходное нулевое состояние триггеры первой 15 и второй 16 групп блока выбора функции (фиг. 2), триггеры 71 - 73 в блоке 11 управления (фиг. 5), регистр 1 новых значений входных сигналов, регистр 2 новых значений выходных сигналов, регистр 3 старых значений входных сигналов и регистр 4 старых значений выходных сигналов (фиг. 1). В начале каждого нового шага в регистре 2 новых значений выходных сигналов записаны значения выходных сигналов, соответствуюцв е окончанию предшествующего шага, а в регистре 3 старых значений входных сигналов и в регистре 4 старых значений выходных сигналов - началу предшествующего шага. Если первый элемент ИЛИ 5 не зафиксировал изменений входных и (или) выходных сигналов т.е. Б =О, и если на выходе второго элемента ИЛИ 6 Б =,О, то блок 11 управления вьдает управляющие сигналы 1до тех пор, пока не зафиксированы изменения входной и (или) выходной информации.По сигналу 1 производится1прием очередного нового слова входной информации в регистр 1 новых значении входных сигналов и выдача с выхода группы 12 элементов И слова выходной информации, сформированного на предшествующем шаге в регистре 2 новых значений выходных сигналов, а также установка через элемент задержки в соответствии с состоянием признака Б триггера 71 и сброс в нулевое состояние триггера 72 в блоке 11 25 управления. Наличке либо отсутствиеизменений входной и (или) выходнойинформации постоянно фиксируется элементом ИЛИ 5, который через первую13 и вторую 14 группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ связан с регистрами- 4 старых и новых значений входной и выходной информации. Сигналом1, осуществляется опрос первого блока 8 памяти и занесение результатовопроса на вторую группу триггеров16 блока 7 выбора функции, передачасодержимого регистров новых значенийвходных 1 и выходных 2 сигналовсоответственно в регистры старыхзначений входных 3 и выходных 4 сигналов, сброс триггера 71 и черезэлемент задержки его установка - всоответствии с состоянием признакаБ триггера 72. Если Б = О,т,е,нет вычисляемых ЛФ, то следующимсигналом на выходе блока 11 управления является сигнал 1 если же Б, =1, т,е. есть вычисляемые ЛФ, то вырабатывается управляющий сигнал 1 5 п По сигналу 1 с выходов элементов И1группы 18 бпока 7 вьдается сигналвыборки функции из второго блока 9памяти, а с выходов триггеров группы15 блока 7 - разрешение на прием ре зупьтата вычисления функции в тотразряд регистра 2, номер которого соответствует номеру вычисляемой функции, устанавливаются в нулевое сос 7 1233 тояние счетчик 23 и регистр 32 промежуточных переменных и в единичное состояние триггер 71 блока 11 управления. Сигнал 1 производит передачу инструкции, номер которой соответствует числу в счетчике 23, которая выбирается дешифратором 26, на входы регистра 27 операций, первого 30 и второго 31 дешифраторов адреса. Дешифратор 26 выбирает также разряд в ре- О гистре 32 промежуточных переменных, номер которого соответствует номеру выбранной инструкции, для приема промежуточного результата. При сигнале "Несравнение", т.е, Я =- О, из блока 11 управления выдается далее сигнал 1 , по которому производится занесение результата выполненной инструкции в подготовленный для приема разряд регистра 32 промежуточных пере менных и прибавляется единица в младший разряд счетчика 23. В случае появления сигналаСравнениепосле прибавления очередной единицы, т.е. Б = 1, очередной сигнал 1, помимо 25 указанных действий, производит установку в единичное состояние триггера 73 и сброс в нулевое состояние триггера 71 в блоке 11 управления. Тогда следующим управляющим сигналом является Т ,который производит занесение результата выполненной инструкции в подготовленный для приема разряд регистра 2 новых значений выходных сигналов, сбрасывает в нулевое состо 35 яние триггеры группы 15 блока 9 и триггер 73 блока 11, устанавливает в соответствии с признаком Я 1 триггер 72 блока 11,т,е. либо подтверждает единичное состояние, в случае если есть еще вычисляемые ЛФ, либо сбрасывает в нулевое состояние в противном случае. Таким образом, до выдачи сигнала со схемы 22 сравнения производится поочередное выполнение всех инструкций вычисляемой ЛФ. При выполнении последней инструкции выдается сигнал со схемь 22 сравнения и результат попадает в регистр 2 новых значений выходных сигналов. Затем процесс 50 вычисления СЛФ повторяется для очередной функции до тех пор, пока не вычисляются все функции. Тогда триггеры 71 - 73 блока 11 оказываются в нулевом состоянии и переводят блок 11 55 управления на выдачу сигналов для приема очередного входного и выдачу полученного выходного слова. Останов 160устройства может производиться в любой момент его работы нажатием кнопки "Стоп".Формула изобретения1, Устройство для вычисления логических функций, содержащее регистр новых значений входных сигналов, регистр новых значений выходных сигналов, регистр старых значений входных сигналов, регистр старых значений выходных сигналов, первый и второй элементы ИЛИ, блок выбора функции, два блока памяти, операционный блок, блок управления, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия, в него введены группа элементов И, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы элементов И группы соединены с выходами результата устройства, информационный вход регистра новых значений входных сигналов соединен с информационным входом устройства, выход регистра старых значений входных сигналов соединен с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы выходы которых соединены с первой группой входов первого элемента ИЛИ и первой группой информационных входов первого блока памяти, выход регистра новых значений входных сигналов соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы и с входом регистра старых значений входных сигналов, выход регистра новых значений выходных сигналов соединен с первыми входами элементовИСКЛЮ- ЧАЮЩЕЕ ИЛИ второй группы и с входом регистра старых значений выходных сигналов,выход которого соединен с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы которых соединены с второй группой входов первого элемента ИЛИ и с второй группой информационных входов первого блока памяти, Выход которого соединен с информационным Входом блока выбора функции, первый выход которого соединен с входом второго элемента ИЛИ, второй выход - с управляющим входом записи регистра новых значений выходных сигналов, третий выход - с адресным входом второго блока памяти, вход инструкций операционного блока соединен с выходом второго блока памяти, первый, второй. и третий информацион 9 1233цые входы операционного блока соединены соответственно с выходами регистров старых значений выходных сигналов, новых значений входных сигналов и новых значений выходных сигналов, выход результата операционногоблока соединен с информационным входом регистра новых значений выходныхсигналов, вторые входы элементов И группы соединены с выходом регистра новых значений выходных сигналов, выход сброса блока управления соединен с входом сброса блока выбора функции и входами сброса регистров старых и новых значений входных и выходных сигналов, выход управления записи блока управления соединен с первыми входами элементов И группы и синхровходом регистра новых значений входных сигналов, первый выход тактовых импульсов блока управления соединен с синхровходами регистров старых значений входных и выходных сигналов и первым синхровходом блокавыбора функции, второй выход тактовых 25импульсов блока управления соединен с вторым синхровходом блока выбора функции и первым синхровходом операционного блока, третий выход тактовых импульсов блока управления соеди- ЗО нен с вторым синхровходом операционного блока, четвертый выход тактовых импульсов блока управления соединен с третьим синхровходом операционного блока, пятый выход тактовых импульсов блока управления соединен с треть им синхровходом блока выбора функции и четвертым синхровходом операционного блока, входы запуска и останова блока управления соединены соответственно с входами запуска и останова устройства, первый, второй и третий входы признаков блока управления соединены соответственно с выходами первого и второго элементов ИЛИ и с выходом признака окончания работы операционного блока, причем операционный блок содержит схему сравнения, счетчик, регистр числа инструкций, регистры инструкций, дешифратор,о регистр операций, два дешифратора операндов, два дешифратора адресов, регистр промежуточных переменных, десять групп элементов И, три группы элементов ИЛИ, шестнадцать элементов ,И и шесть элементов ИЛИ, причем первый вход схемы сравнения соединен с выходом регистра числа инструкций,160второй - с. выходом счетчик, яыхол схемы сравнения соединен с выходом признака окончания работы операционного блока, вход дешифратора соединен с. выходом счетчика, вход сброса счетчика соединен с первым сицхровходом операционного блока, входь 1 регистра числа инструкций и регистров инструкций соединены с входом инструкций операционного блока, первые входы элементов И первой группы соединеныс вторым синхровходом операционного блока, вторые входы элементов И первой группы соединены с выходами регистров инструкций, третьи входы с соответствующими выходами дешифратора, а выходы - с входами соответст-. вующих элементов ИЛИ первой, второй и третьей подгрупп первой группы выходы которых соединены с входами соответственно регистра операций,первого и второго дешифраторов адреса, выходы элементов И второй группы соединены с входами регистра промежуточных переменных, первый, второй и третий информационные входы операционного блока соединены с первыми входами элементов И соответственно третьей и четвертой, пятой и шестой, седьмой и восьмой групп, первые входы элементов И девятой и десятой групп соединены с выходами регистра промежуточных переменных, вторые входы элементов И третьей, пятой, седьмой и девятой групп соединены с выходами первого дешифратора адреса, вторые входы элементов И четвертой, шестой, восьмой и десятой групп соединены с выходами второго дешифратора адреса, первые входы первого,второго, третьего и четвертого элементов И соединены с выходами первого дешифратора операндов, первые входы пятого, шестого, седьмого и восьмогоэлементов И соединены с выходами второго дешифратора операндов, выходы элементов И третьей, пятой, седьмой и девятой групп соединены с входами элементов ИЛИ второй группы,выходы которых соединены с вторыми входами первого, второго, третьего и четвертого элементов И, выходы которых соединены с входами первого элемента ИЛИ прямой и инверсный выходы которого соединены с первыми входами соответственно девятого и десятого элементов И , выходы которых соединены с входами второго элемен 11 123а ИЛИ, выходы элементов И четвертой пестой, восьмой и десятой групп соединены с входами элементов ИЛИ третье й группы, выходы которых соединенывторыми входами пятого, шестого,едьмого и восьмого элементов И, выходы которых соединены с входамигретьего элемента ИЛИ, прямой и инверсный выходы которого соединены с первыми входами соответственно одиннадцатого и двенадцатого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, первый вход пятого элемента ИЛИ соединен с выходом второго элемента ИЛИ, второй вход - с выходом четвертого элемента ИЛИ, а выход - с первым входом тринадцатого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, первый вход четырнадцатого элемента И соединен с выходом второго элемента ИЛИ, второй вход - с выходом четвертого элемента ИЛИ, а выход - с первым входом пятнадцатого элемента И, выход которого соединен с вторым входом шестого элемента ИЛИ, прямой и инверсный выходы первого разряда регистра операций соединены с вторыми входами соответственно тринадцатого и пятнадца 30 того элементов И, прямой и инверсный выходы второго разряда регистра операций соединены с .вторыми входами соответственно девятого и.десятого эле ментов И, прямые выходы третьего и четвертого разрядов регистра операций соединены с входами первого дешифратора операндов, прямой и инверсный выходы пятого разряда регистра операций соединены с вторыми входами0 соответственно одиннадцатого и двенадцатого элементов И, прямые выходы шестого и седьмого разрядов соединены с входами второго дешифратора опе. - рандов, первые входы элементов И второй группы соединены с третьим син 15 хровходом операционного блока и счетным входом счетчика, вторые входы - с выходами дешифратора, третьи входы - с выходом шестого элемента ИЛИ,0 синхровход записи регистра промежуточных переменных соединен с первым синхровходом операционного блока,первый вход шестнадцатого элемента И соединен с выходом шестого элемента ИЛИ, второй вход - с четвертым синхровходом операционного блока, а выход - с выходом результата операционного блока. 3160 22, Устройство по п, 1, о т л ич а ю щ е е с я тем, что блок выбора функции содержит две группы триггеров, две группы элементов И, группу элементов задержки, элемент ИЛИ,элемент задержки, причем выход элемента ИЛИ соединен с нулевыми входами триггеров первой группы, выход-го элемента И первой группы соединен с первым входом (д+1)-го элемента Ипервой группы и первым входом ( +1)-го элемента И второй группы,1, ш - 1; т - число вычисляемьгхфункций), первый вход последнего элемента И второй группы соединен свыходом последнего элемента И первойгруппы, вторые входы элементов И первой и второй групп соединены соответственно с инверсными и прямыми выходами триггеров второй группы, прямые выходы триггеров второй группыобъединены и соединены с первым выходом блока, прямые выходы триггеровпервой группы объединены и соединеныс вторым выходом блока, выходы элементов И второй группы соединеныс единичными входами соответствующихтриггеров первой группы и соединеныс третьим выходом блока, а черезэлементы задержки группы - с первыминулевыми входами триггеров второйгруппы, информационные входы триггеров второй группы объединены и соединены с информационным входом блока, вход сброса блока соединен с первым входом элемента ИЛИ и вторыминулевыми входами триггеров второйгруппы, первый синхровход блока соединен с синхровходами триггеров второй группы, второй - с входами первых элементов И первой и второй групп,третий - через элемент задержки с вторым входом элемента ИЛИ.3. Устройство по и, 1, о т л ич а ю щ е е с я тем, что блок управления содержит генератор импульсов, пять триггеров, девять элементов И,. три элемента задержки, распределитель импульсов, четыре элемента ИЛИ, причем выход генератора импульсов соединен с первыми входами первого и второго элементов И,второй вход первого элемента И соединен с прямым выходом первого триггера, а выход с первыми входами первого, второго и четвертого элементов ИЛИ и через первый элемент задержки - с нулевым входом первого триггера, второй вход второго элемента И соединен с инвер 1.31233 сным выходом первого григгера, третий вход - с прямым выходом второго триггера, а выход - с входом распределителя импульсов, первый вход признаков блока соединен с информацион" ным входом третьего триггера, второй - с информационным входом четвертого триггера, третий - с первым входом третьего элемента И и с информационным входом пятого триггера, выход четвертого элемента И соединен с вторым входом первого элемента ИЛИ и через второй элемент задержки - с синхровходом третьего триггера,выход пятого элемента И соединен с вторым вхо- дом второго элемента ИЛИ и через третий эл"мент задержки - с первым входом третьего элемента ИЛИ выход шестого элемента И соединен с единичным входом третьего триггера, выход седьмого элемента И соединен с вторым входом третьего элемента И и с синхровходом пятого триггера выход третьего элемента И соединен с третьим входом второго элемента ИЛИ,первый 5 выход распределитепя импульсов соединен с первыми входами четвертого,шестого, восьмого и девятого элементов И, второй выход. распределителя импульсов соединен с первыми входами пятого и седьмого элементов И, вторые входы четвертого, шестого, девятого элементов И соединены с инверсным выходом третьего триггера, вторые входы пятого,седьмого и восьмого элементов И -35 160 14прямым выходом треьеГо ри гера,третьи входы четвертого и пятого элементов И соединены с инверсным выходом четвертого триггера, третьи входы шестого, седьмого, восьмого и девятого элементов И - с прямым выходомчетвертого триггера, четвертые входышестого и девятого элементов И группы - соответственно с инверсным ипрямым выходами пятого триггера, выход девятого элемента И группы соединен с вторыми входами третьего и четвертого элементов ИЛИ, нулевой входтретьего триггера соединен с выходомвторого элемента ИЛИ, нулевой входчетвертого триггера соединен с выходсм первого элемента ИЛИ, синхровходчетвертого триггера соединен с выходом третьего элемента ИЛИ, нулевой:вход пятого триггера соединен с выходом четвертого элемента ИЛИ,входзапуска блока соединен с единичнымизходами первого и второго триггерови с входом генератора импульсов, входостановка блока соединен с нулевымвходом второго триггера, выход сброса блока соединен с выходом первогоэлемента И, выход управления записиблока соединен с выходом четвертогоэлемента И, первый, второй, третий,четвертый и пятый выходы тактовыхимпульсов блока соединены соответственно с выходами пятого, шестого,седьмого, восьмого и девятого элементов И,

СмотретьЗаявка

3603698, 08.06.1983

МОГИЛЕВСКИЙ МАШИНОСТРОИТЕЛЬНЫЙ ИНСТИТУТ

КУКЛИН ГРИГОРИЙ ВАСИЛЬЕВИЧ, ПАВУЧУК ВЛАДИМИР ПАВЛОВИЧ

МПК / Метки

МПК: G06F 17/00

Метки: вычисления, логических, функций

Опубликовано: 23.05.1986

Код ссылки

<a href="https://patents.su/11-1233160-ustrojjstvo-dlya-vychisleniya-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логических функций</a>

Предыдущий патент: Вычислительная система

Следующий патент: Устройство для распределения задач в вычислительной системе

Случайный патент: Нож к устройству для измельчения пищевых продуктов