Вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1233159

Авторы: Козюминский, Мятликов

Текст

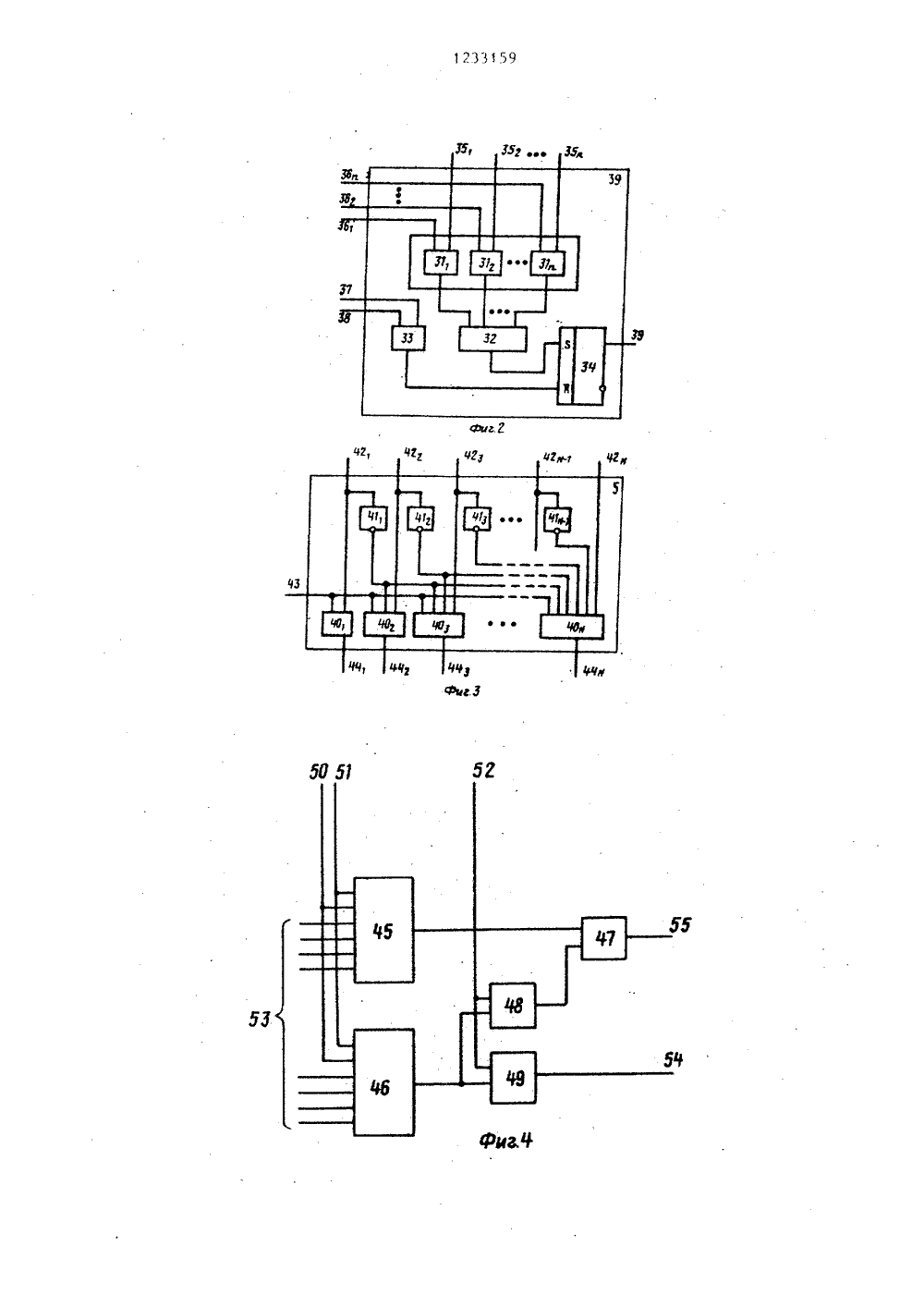

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК би 4 С О 6 Р 1 5 /О(54) ВЫЧИСЛИ (57) Изобрет лительной те ЕЛЬНАЯ СИСТЕМА У 19ий и А.И,Мятлико испольэовани и обработки изобретения родействия. типных опера шифратора ад ные комплекты инстав и структура. А.А.Васенкова,дио и связь, и блок прио ность призн цели изобре ельство СССР Р 15/00, 1974 ельство СССР Р 7/38, 1979.5 иле ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(21) 3637495/24 - 24 (22) 23.08.83 (46) 23.05.86. Бюл (72) В.Д.Козюминск (53) 681.325(088.8 (56) Микропроцессо тегральных схем, с Справочник./Под ре В.А.Шахнова, М.: Р 1982, рис. 7.1.Авторское свиде В 479114, кл. С 06Авторское свиде 9 763804, кл. С 06 ние относится к вычис - нике и предназначено д в системах для хранен воичных кодов. Целью вляется повышение быст истема содержит М одно ионных блоков, два дееса, группу элементов тета. Данная совокупов позволяет достичьИзобретение относится к вычислительной технике и используется в системах для хранения и обработки двоичных кодов.Цель изобретения - повышение быстродействия системы.На Фиг, 1 представлена структурнаясхема системы; на Фиг. 2 - Функциональная схема узла формирования ассоциативных признаков; на Фиг. 3блок приоритета; на фиг. 4 - схемаодного разряда комбинационного сумматора; на фиг. 5 - объединение отдельных разрядов комбинационного сумматора,15Система (Фиг, 1) содержит И однотипных операционных блоков 1. -1Мпервый дешифратор 2 адреса, второйдешифратор 3 адреса, группу элементовИ 4, блок 5 г 1 риоритета и имеет информационный вход 6, информационныйвыход 7, вход 8 маски, вход 9 коданастройки (кода операции), вход 10синхронизации, входы 11-17 кода операции, адресные входы 18 и 19. Операционный блок 1 содержит комбинационный сумматор 20, регистр 21, первыйи второй элементы ИЛИ 22 и 23, первый"третий элементы И 24-26, первую и,вторую группы элементов И 27 и 28,узел 28 Формирования ассоциативныхпризнаков и четвертый элемент И 30.Входы элемента 22 блока 1 подключены к -му выходу дешифратора 2,входу 11, выходам элементов И 24и 251 Входы элементов И 27 первойгруппы подключены к выходу элемента22 и входу 9 системы, а выходы этихэлементов И - к управляющему входу40сумматора 20, выходы которого подключены к входу регистра 21 и информационному входу узла 29. Первыйинформационный вход сумматора 20подключен к выходу регистра. 21 и входам элементов И 28 второй группы, а45второй информационный вход сумматора20 - к информационному входу 6 системы. Синхровход регистра 21 подключен к выходу элемента 30, входы которого подключены к выходу элемента 22и входу 10 системы. Вход маски узла29 подключен к входу 8 маски системы,а входы сброса узла 29 - к входу 15системы и выходу элемента 26, выходузла 29 - к,первому входу .элемента25 и г-му входу блока 5, 1-и вьгходкоторого подключен к первым входамэлементов 24 и 26 и входу элемента 23, второй вход которого подключен к 1-му вьгходу дешифратора 3, Выход элемента 23 подключен к входам элементов И 28 второй группы, выходь 1 которых подключены к информационному выходу 7 системы, который подключен также к входам элементов И 4 группы, другие входы которых подключены к входу 16 системы, а выходы - к информационному входу 6 системы, Вторые входы элементов 24-26 подключены к входам 12-14 системы соответственно. Входы дешифраторов 2 и 3 подключены к адресным входам 18 и 19 системы, Стробирующий вход блока 5 подключен к входу 17 системы.Узел 29 Формирования ассоциативных признаков (Фиг. 2) содержит п элементов ИЛИ 31, -31 , элемент И 32, образующие коммутатор, элемент ИЛИ 33, триггер 34 и имеет информационный вход 35-35, вход 36 -36 маски, первый и второй входы 37 и 38 сброса и выход 39. При этом первые входы элементов 31 -31 подключены к разрядам информационного входа 35 -35, а их вторые входы - к разрядам входа 361 -36 маски, а выходы - к входам элемента 32, выход которого подключен к единичному входу триггера 34, Ну левой вход триггера 34 подключен к выходу элемента 33, входы которого подключены к входам 37 и 38 узла, а выход триггера 34 - к выходу 39 узла,Блок 5 приоритета (Фиг. 3) содержит И элементов И 40,-40 , элементы НЕ 41, -41, и имеет информационный вход 42,-42, стробирующий вход 43 и выходы 44, -44 . При этом первый вход элемента 40 ( = 1,И) подключен кстробирующему входу 43 блока, второй вход элемента 40, - к входу 42, блока, а остальные . - 2 входов элемента 40 (1 = 2,д) - к выходам элементов 41, -41 . входы элементов 41, к входам 42, блока, а выходы элементов 40, -40, - к выходам 44 -44 блока приоритета. Схема комбинационного сумматора 20 может быть построена по любому принципу, Операции, выполняемые сумматором, определяют операции, выполняемые блооками 1 -1, системы. Например, схема известного разряда комбинационного сумматора (фиг, 4) реализует любые операции типа Р 1(А,В) + Р 2(А,В), где Г(А,В) - некоторая поразрядная логическая операция над операндами Ли В.Схема одссого разряда сумматора 20 содержит мультиплексоры 45 и 46, элемент ИЛИ 41 элемент И 48 и элемент 49 сложения по модулю два и имеет первый информационный вход 50, второй иссформационный вход 51, вход Я переноса, управляющие входы 53, выход 54 результата и выход 55 переноса.Схема и-разрядного сумматора 20 (Фиг. 5) включает разряды сумматора 10 56, -56, при этом выходы 54, являются вьсходами сигнала результата Б с.-го разряда х = 1,и, а выходы 55; - выходами сигнала переноса из с.-го разряда. Кроме того, вход 52; переноса 15 -го разряда подключен к выходу 54 переноса (-1)-го разряда. При обработке чисел в обратных кодах выход Р переноса п-го разряда сумматора подключается к входу 52, переноса 20 первого разряда. При обработке чисел в дополнительных кодах выходы 54 и 52 сумматора не используются .Функциональные возможности сумматора полностью определяются функци ональными возможностями одного разря да (Фиг. 4). Реализация в сумматоре 20 операций типа Я = Г 1(А,В)+Р 2(А,В) достигается тем, что в схеме -го разряда (фиг. 4) вьсходноу сигнал результата Б, = Р (А;,В; )ЙРа сигнал переноса Р, = сс.(А,В, )Ч ЧГ 3(А., В;) Р где М(А В,) и ГВ (А В ) - логические Функции, реализуемые мультиплексорами 45 и 46 со 35 ответственно, причем Функция сс.,Лс ,В ) = Р 1(А В ) 8 Р 2(А, В, ), а Функ. ция /3 (АсВ ) = Р 1(А В )Д+Р 2(АВ ). Возможность реализации мультиплексором логических Функций Вытека - 40 ет из логического выражения мультиплексора, например, для мультиплексора 45 можно записать с(А, В. ) =А В Г.Г,Ч А В У,ЧА В Д Чженссг 1 1) уп 1 оссс;сетс я, 11 асс 1 са 1ссри 11, =0 =0 и 1, =И, =1 ссс 11) получим х(Л В )= Л В ЧЛ ВДля реализации в сумматоре 20, выполненном в соответствии с фиг, 4 и 5, операции В = Р 1(Л,В) + Р 2(Л,В) необходимо найти значения функций с( и В , реализуемых мультиплексорами 45 и 46 соответственно при всех наборах их аргументов, и подать эти значения на соответствующие входы настройки мультиплексоров. Например, пусть требуется выполнить операцию Б = А + В. Тогда Р 1(А,В) =А, а Р 2(А,В)- =В. Для нахождения логических функций ь(АВ,) и Г 3(А В, ), реализуемых соответственно мультиплексорами 45 и 46 с.-го разряда ( = 1,п) при выполнении в сумматоре заданной операции, составляют таблицу истинности требуемой операции для -го разряда без учета сигналов. переноса Р из ( - 1)-го разряда.В Р 1 Р 2 Г 1 + Р 2 1) О 0 1 0 1 0 1 О О 0 0 1 0 1 1 1 О 1 1 1 0 0 1 Для настройки мультиплексоров необходимо значения 0 и 1 логических функ-. ций сс.и р подать на соответствующие входы 53.Вычислительная система может работать в нескольких режимах.Режим 1. Операции выполняются в -ом блоке 1 в соответствии с выра чА ВГУ (1) где А, и В, - сигналы, подаваемые наинформационные входы50 и 51 мультиплексора,50Б, -1 Г - сигналы настройки, подаваемые на. управляющие входы 53 мульти -плексора.Так как при настройке схемы сигналы 55 с 1, -ГГ принимают нулевое или единичное значение в зависимости от реализуемой функции, то логическое выражением(Т ) - информация на входе 6системы:некоторая операция, выполняемая сумматором 20. Для реализации этого режима на вход десссифратора 2 подается адрес А 1= 1 (на вход 16), на вход 6 - двоичнаяинФормация 1 , на вход 9 сумматоракод настройки О, соответствующий операций а , Сигналы на остальных входах системы равны нулю. Операциявыполняется только в том блокевход элемента 22 которого подключенк возбуждаемому выходу дещифратора 2,что определяется кодом А = 1, поступающим на вход дещифратора 2, По аигналу синхронизации С, подаваемому навход 10, производится запись результата операции в регистр 21 -го блока 1,Режим 2, Операция выполняется в-ом блоке 1 в соответствии с выражениемсВ. С : =Ж С .СК С ,2 О где К С.- содержимое регистра 21Ф3-го блока, 1 Ф В отличие от предыдущего режима работы в этом режиме входная информа 1 цИя Зхх На ВХОД 6 НЕ ПОдаЕтСя, а На вход 19 подается код,адреса А на вход 16 - сигнал 17 = 1. В этом режиме сигналы с выхода регистра 21 3-го блока, номер которого определен адресом А поступают через группу элементов 28, открытых сигналом с выхода дещифратора 3, на выход 7 системы и через группу элементов 4, открытых сигналом 11, - на вход 6, что обеспечивает подключение выходов регистра 21 3-го блока 1 к входам сумматора -го блока 1.Режим 3. Выполняются операции ассоциативного поиска. В этом режиме происходит установка триггера 34 узла 29 тех блоков 1, для которых выход 40 ные сигналы всех незамаскированных разрядов сумматора 20 равны "1" при выполнении в этих сумматорах любой из операций типа45сЕС 1 с 1 , х = 1, И.1 ВхПеред реализацией данного режима производится обнуление триггеров 34 всех блоков 1 сигналом П = 1, подаваемым на вход 15 системы. На вход 9 подается код У выбора операции, выполняемой в сумматоре 20, на вход 6 - код . , на вход 11 - сигнал Б, = 1. В результате действия сигнала У открыты элементы 27 и 30 блоков 1 не. зависимо от кода адреса А, и код 0 выбора операции поступает одновременно на входы кода операции сумматоров всех блоков 1 и н сумматорах20 выполняется операция сК С+с 3 х, х = 1, МРезультат этой операции с выходакаждого сумматора 20 поступает навходы 35-35, элементов ИЛИ узла 29.Если при этом во всех разрядахсигналы равны "1", то на выходе элемента 32 узла 29 появляется сигнал"1", который устанавливает триггер 34в единичное состояние. Если требуется проверить не все разряды сумматора 20 на равенстно их "1", то в этомслучае на вход 8 подается код маски1, в котором для проверяемых разрядон сигнал .равен "0", а для маскируемых разрядов - "1". В режиме ассоциативного поиска сигнал синхронизации С на вход 10 не подается.Ре;ким 4. Режим ассоциативной обработки. Этот режим может выполняться только после режима 3 (ассоциативного неиска). Обработка производитсяво всех блоках, в которых триггер 34узла 29 находится в единичном состоянии, и выполняется н соответствии свыражением сК С= СК Сс 1 .1 1 ЬхВыполнение операций производитсятак же, как н режиме 1, но адрес А =О,а. сигнал"Г. на входе 12 равен "1".Если в этом режиме сигнал А,то обработка в -ом блоке 1 выполняется независимо от состояния триггера 34 -го блока 1Режим 5. Режим ассоциативной приоритетной обработки. Обработка выполняется так же, как и в примере 4, но сигнал П = О, а сигнал П. на входе 13 ранен "1". Сигнал У на входе 17 также равен " 1", Блок 5 приоритета определя т старший по приоритету блок 1, ( = 1,И), в котором триггер 34 находится в единичном состоянии. Под действием сигнала П = 1 на выходе блока 5 появляется сигнал, определяющий старший по приоритету блок 1, н котором на выходе триггера 34 присутствует "1". Зтот сигнал через элементы 24 (так как П 1) соответствующего блока 1 и элемент 22 открывает элементы 27 и 30, В результате только в выбранном блоке 1 обеспечиваются выполнение н сумматоре 20 требуемой операции и запись результата по сигналу С в регистр 21, По окончании данного режима при необхо 1233159димости обнуляется по сигналу=1 (подается на вход 14) триггер 34 блока 1, определяемого блоком 5. В этом случае одновременно с сигналом5 подается сигналРежим 6. Режим обработки с выполнением операций в соответствии с выражением В. С := (К С (К Сс1приоритетным ассоциативным выбором К С . Режим выполняется после режима 3. В данном режиме на вход 18 поступает код адреса А, =и подаются сигна ы У 1 = 1, Б, = О, 6 = 1 1= О, Сигнал приоритетной выборки,15 с выхода 3 блока 5 через элемент 23 открывает элементы 28 группы и ггодключает регистр 21 3 -го блока к выходу 7 системы, который, в свою очередь, подключен по сигналу= 1 201 через элементы группы 4 к входу 6, откуда информация поступает на обработку в блок 1, адрес которого определен кодом А . По окончании операции при необходимости сигналом25 обнуляется триггер 34 блока 1Режим 7. Считывание информации из -го блока 1. Считывание информации из .-го блока 1 может быть осуществлено по адресу А = . В этом случае код А =подается на вход 19,гв результате чего сигнал на д-ом выходе дешифратора 3 через элемент 23 открывает элементы группы 28 и под 35 ключает выходы регистра 21 -го блока 1. к выходу 7 системы, откуда и снимается считываемая информация, Может быть осуществлено и приоритетное ассоциативное считывание. В этом случае код А = О, а сигнал= 1. В результате к выходу 7 подключается регистр 21 блока 1., номер которогоопределяется блоком 5, При считьгвании информации сигнал С на вход 10 синхронизации не подается.Таким образом, предпагаемая вычислительная система может работать в различных режимах обработки информации, что расширяет ее Функциональные50 возможности и область применения и соответственно повышает быстродействие.Формула из об ре те нияВычислительная система, содержащаяИ операционных блоков, каждый из которьгх включает комбинированный сумматор и регистр, информациоцный вход которого соединен с выходом комбинационного сумматора, о т л и ч а ющ а я с я тем, что, с целью повышения быстродействия, она содержит два дешифратора адреса, блок приоритета и группу элементов И, а каждый-й операционный блок 15 Ы ) допопнительно содержит два элемента ИЛИ, четыре элемента И, две группы элементов И и узел формирования ассоциативных приэкаков,- включающий коммутатор, элементИ и триггер, установочный вход, вход сброса и выход которого подключены соответственно к выходу коммутатора, выходу элемента ИЛИ и-му входу блока приоритета, первыгг, второй, третий и четвертый входы и выход первого элемента ИЛИ 1 -го операционного блока соединены соответственно с г-м вьгходом первого дешифратора адреса, входом кода операции системы, выходами первого и второго элементов И и первыми входами элементов И пер,вой группы г -го операционного блока, информационный и управляющий входы коммутатора и первый и второй входы элемента ИЛИ узла формирования ассоциативных признаков каждого операционного блока подключены соответственно к выходу комбинационного сумматора этого операционного блока, входам.маски и кода операции системы и выходу третьего элемента И того же операционного блока, первые входы первого, второго и третьего элементов И каждого операционного блока соединены с входом кода операции системы,-й выход блока приоритета подключен к первому входу второго элемента ИЛИ и вторым входам первого и третьего элементов И 1-го операционного блока, второй вход второго элемента И каждого операционного блока соединен с выходом триггера узла формирования ассоциативных признаков того же операционного блока, первые и вторые входы и выходы элементов И второй группы под. ключены соответственно к выходу регистра и выходу второго элемента ИЛИ того же операционного блока и информационному выходу системы, второй вход второго элемента ИЛИ 1 -го операционного блока соединен с г-м выходом второго дешифратора адреса, управляющий вход и первый и второй информационные входы комбинационногосумматора каждого операционного олок подключены соответственно к выходам элементов И первой группы ивыходу регистра того яе операционного блока и информационному входусистемы, вторые входы элементов Ипервой группы каждого операционногоблока соединены с входом кода операции системы, выход и первый и второйвходы четвертого элемента И каждогооперационного блока подключены соответственно к синхровходу регистра,выходам элементов И первой группы того же операционного блока и входу синхрониэацни системы, первые и вто - рые входы и выходы элементов И группы соединены соответственно с входоь кода операции и информационным выходом системы и вторыми информационными входами комбинационных сумматоров 10 всех операционных блоков, а входыпервого и второго дешифраторов адреса подключены к адресному входу сисгемы.1233159 и Составитель Г. ВиталиеТехред О.Сопка ктор Е,Сирохман акто г лич лраж 671 Подписи ак Государственного комитета СССРелам изобретений и открытийосква, Ж-.5, Раушская наб., д. 4/ ВНИИ 1303 оизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектна

СмотретьЗаявка

3637495, 23.08.1983

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПВО

КОЗЮМИНСКИЙ ВАЛЕРИЙ ДМИТРИЕВИЧ, МЯТЛИКОВ АНАТОЛИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: вычислительная

Опубликовано: 23.05.1986

Код ссылки

<a href="https://patents.su/8-1233159-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система</a>

Предыдущий патент: Устройство для сопряжения абонентов с каналами связи

Следующий патент: Устройство для вычисления логических функций

Случайный патент: Аппарат непрерывного действия для приготовления паточной рассиропки