Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

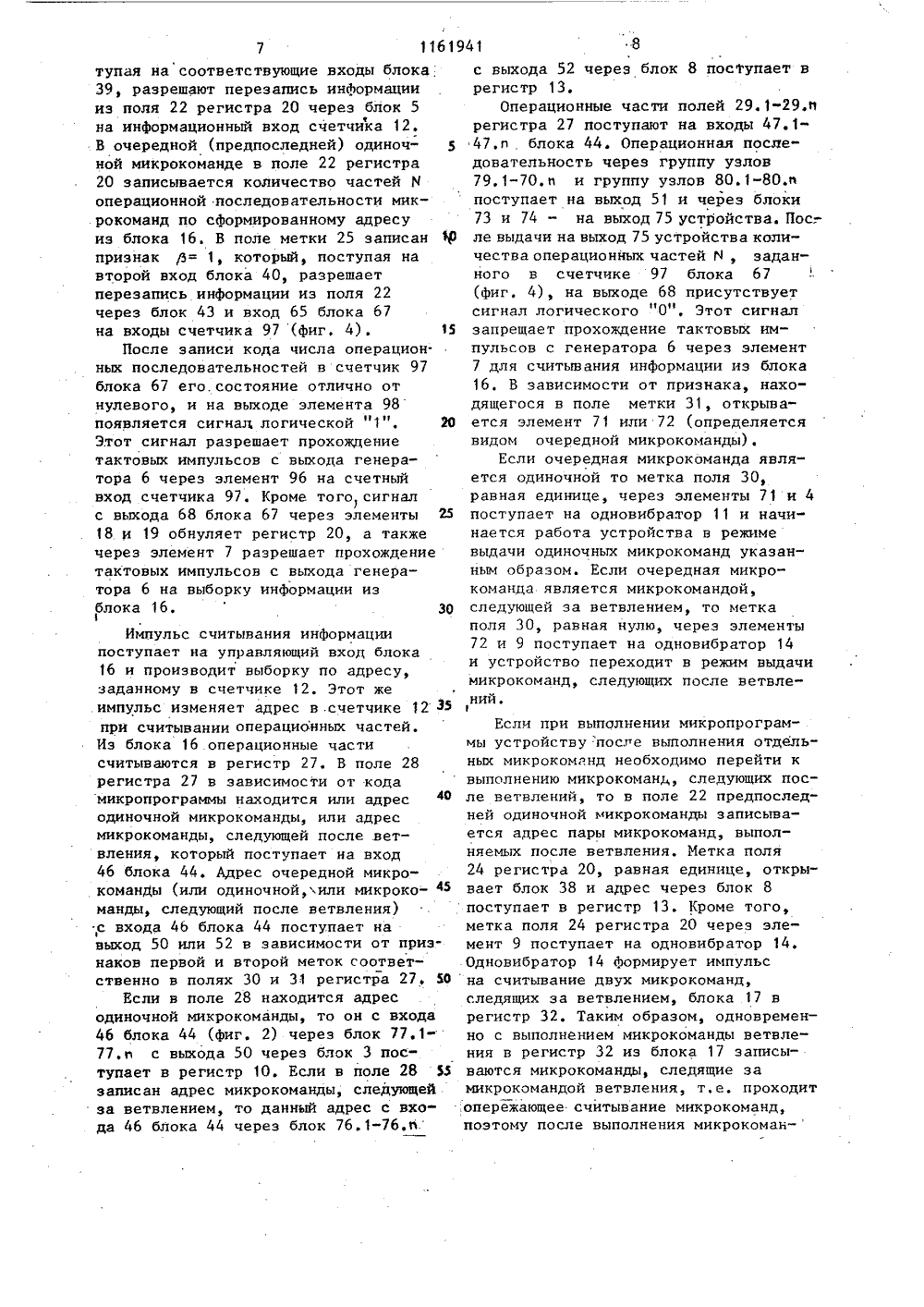

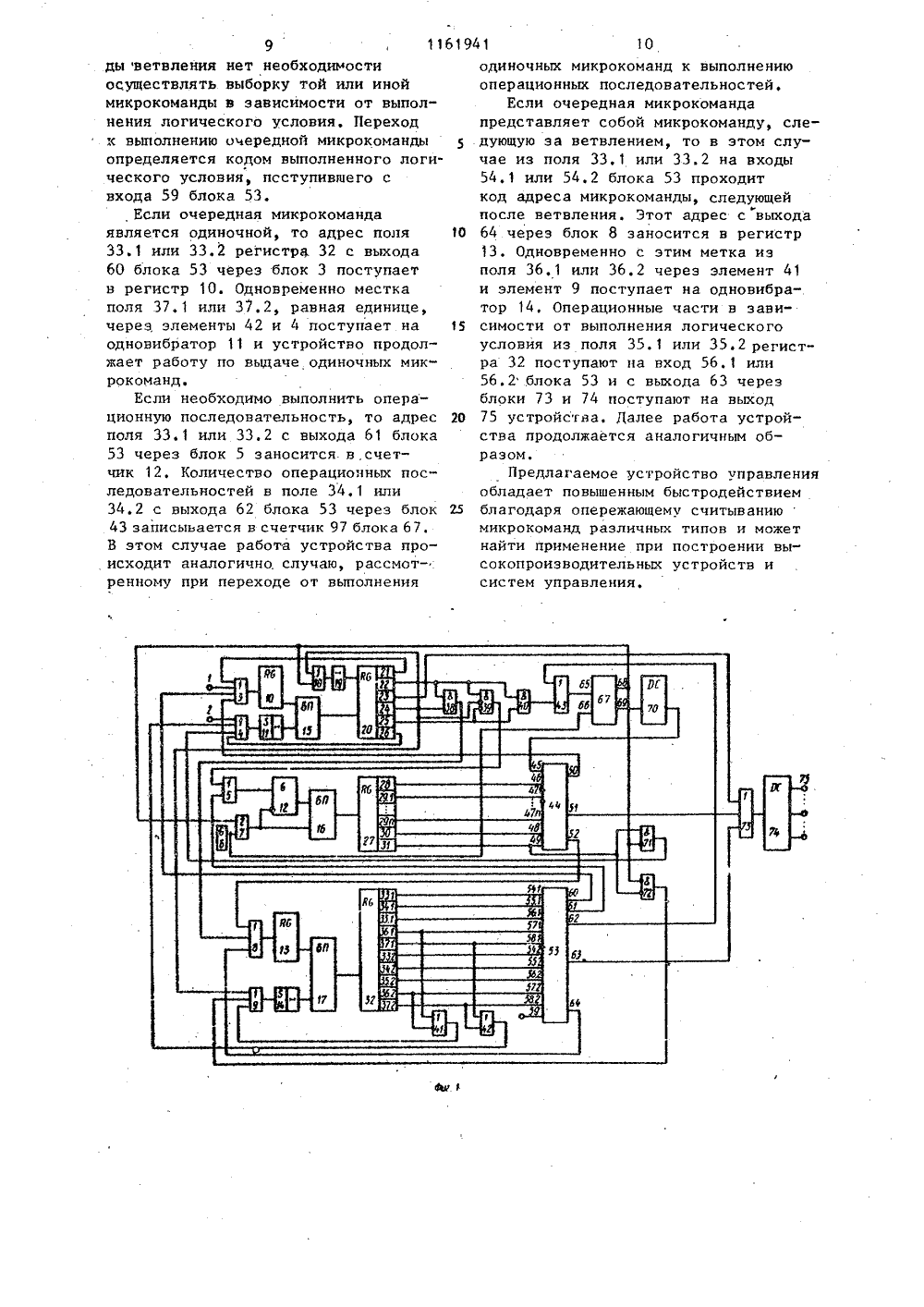

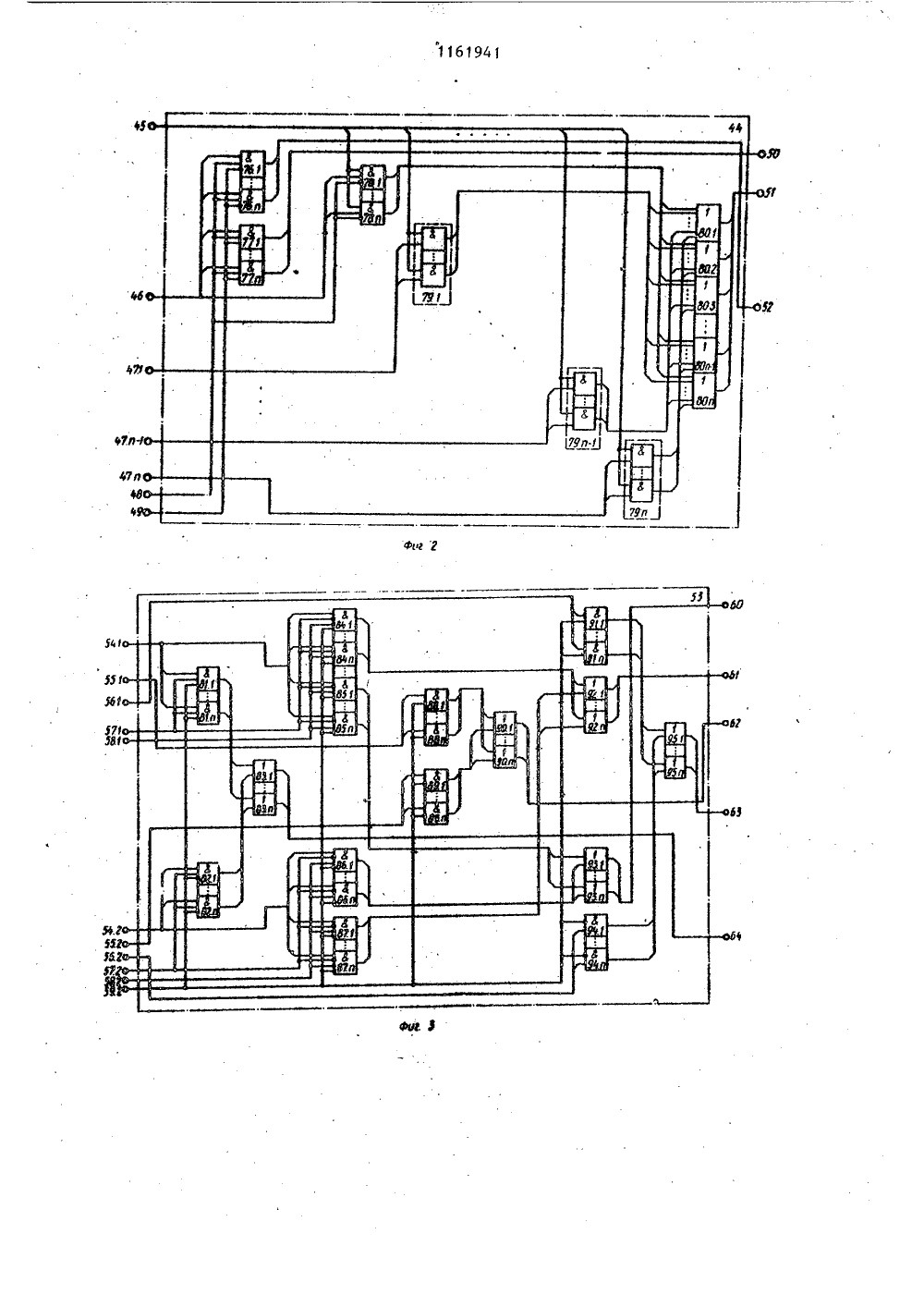

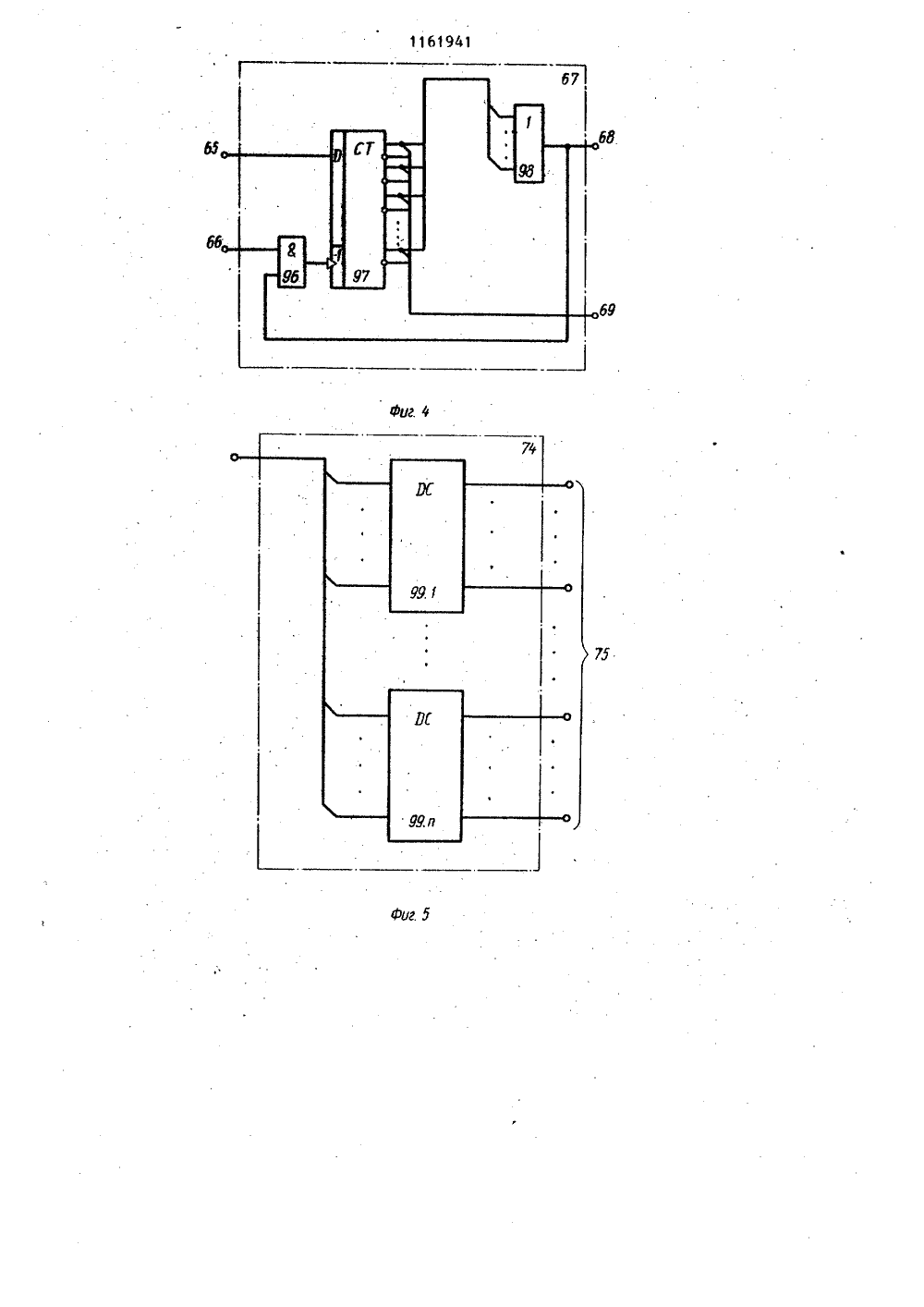

СОЮЗ СОВЕТСНИХОЦИДЛИСТИЧЕСНИХРЕСПУБЛИН 9 22 ОМИТЕТ СССР НИЙ И ОТН 1;ЫТ удм стеенный ДЕЛдМ ИЗОЩЕ НИЕ ИЗОБРЕТЕН(56) Авторское свидетельство СССР У 746517, кл. С 06 Р 9/22, 1980.Авторское свидетельство СССР У 561964, кл. С 06 Р 9/22, 1976.Авторское свидетельство СССР Мф 608159, кл, С 06 Р 9/22, 1978.Авторское свидетельство СССР У 913379, кл. С 06 Р 9/22, 1980. (54)(57) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее три блока памяти, два регистра адреса, три регистра микрокоманды, первый блок коммутаторов, дешифратор, блок дешифраторов микроопераций, четыре блока элементов ИЛИ, три блока элементов И, четыре элемента ИЛИ .и блок управления, включающий элемент И, счетчик и элемент ИЛИ, вход и выход которого соединены соответственно с прямым выходом счетчика и .первым входом элемента И, выход которого подключен к счетному входу счетчика, информационный выход которого соединен с входом дешифратора, выходы первого, второго и тр тьего блоков памяти подключены к информационным входам соответственно первого, второго и третьего регистров микрокоманды, первый адресный выход, первый операционный выход, второй адресньгй выход и второй операционный выход третьего регистра микрокоманды соединены соответственно .с первым, вторым, третьим и четвертым информационными входами первого блока коммутаторов, первый вход первого блока элементов ИЛИ подключен к адресному входу устройства, а вход и выход блока дешифраторов микроопераций соединены соответственно с выходом второго блока элементов ИЛИ и в 1 ходом устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, оно содержит счетчик реса, второй блок коммутаторов, три элемента И, пятый элемент ИЛИ, элемент задержки, генератор тактовых им сов и два одновибратора, выходы которых подключены к управляющим входам соответственно первого и третьего блоков памяти, выходы первого и второго регистров адреса и счетчика адреса соединены с адресными входами .соответственно первого, третьего и второго блоков памяти, второй, третий и четвертый входы и выход первого блока элементов ИЛИ подключены соответственно к адресному выходу первого регистра микрокоманды, первым адресным выходам первого и второго блоков коммутаторов и входу первого регистра адреса, первые входы первого, второго ,и третьего блоков элементов И соединены с дополнительным адресным выходом первого регистра микрокоманды, выход первой метки которого подключен к вторым входам первого и второго фф блоков элементов И, выход второй метки первого регистра микрокоманды соединен с третьим входом второго блока элементов И и вторым входом третьего блока элементов И, выход первого элемента И подключен к счетному входу счетчика адреса И управля 116194116 1Составитель Г. Виталиевактор Л, Алексеенко Техред Л.Мартяшова ектор раж 71 Подпис аз 3969/50 омичиета СССР ВНИИПИ Государственног по делам изобретений113035, Москва, Ж, Рауш открытии ая наб.,атент", г, Ужгород, ул. Проектная, 4 филиал 111а)1161941 кицему входу второго блока памяти,выход генератора тактовых импульсов,соединен с первым входом первогоэлемента И и вторым входом элемента Иблока управления, выход элемента ИЛИкоторого подключен к второму входупервого элемента И, первым входамвторого и третьего элементов И, выходы третьего, четвертого и пятого блоков элементов ИЛИ соединены соответственно с входом второго регистраадреса, информационным входом счетчика адреса и информационным входомсчетчика блока управления, выходыпервого, второго, третьего, четвертого и пятого элементов ИЛИ подключенысоответственно к входу первого одновибратора, входу элемента задержки,входу второго одновибратора, первомувходу третьего элемента ИЛИ и первомувходу первого элемента ИЛИ, второй,третий и четвертый входы которогосоединены соответственно с входомпуска устройства, выходом второгоэлемента И и выходом третьей меткипервого регистра микрокоманды, входсброса которого подключен к выходуэлемента задержки, первый и второйвходы второго элемента ИЛИ соединенысоответственно с выходом первой меткипервого регистра микрокоманды ивыходом элемента ИЛИ блока управления,первый и второй входы четвертого блокаэлементов ИЛИ подключены соответственно к выходу второго блока элементов Ии второму адресному выходу первогоблока коммутаторов, третий адресныйвыход которого соединен с первымвходом третьего блока элементов ИЛИ,второй и третий входы которого подклю.чены соответственно к выходу первогоблока элементов И и второму адресномувыходу второго блока. коммутаторов,первый, второй и третий входы второгоблока элементов ИЛИ соединены соответИзобретение относится к вычисли,тельной технике и автоматике и может быть использовано .при построении микропрограммных устройств и систем повышенного быстродействия. ственно с информационными выходамипервого и второго блоков коммутаторови первого регистра микрокоманды, второй ж третий входы третьего элементаИЛИ подключены соответственно к выходу третьего элемента И и выходупервой метки первого регистра микрокоманды, первый и второй информационные .входы, первый, второй и третийуправляющие входы второго блокакоммутаторов соединены соответственно с адресным и информационным выходами второго регистра микрокоманды,выходом дешифратора, выходами первойи второй метки второго регистрамикрокомаиды, кроме того, вторыевходы второго и третьего элементов Иподключены к выходу второй меткивторого регистра микрокоманды, первый и второи входы пятого блока элементов И соединены соответственно синформационным выходом первого блокакоммутаторов и выходом третьего блокаэлементов И, пятый и шестой информационные входы, первый, второй, третий, четвертый и пятый управляющиевходы первого блока коммутаторовподключены соответственно к первомудополнительному и второму дополнительному адресным выходам, выходупервой метки, выходу второй метки,дополнительному выходу первой метки,дополнительному выходу второй меткитретьего регистра микрокоманды ивходу логических условий устройства,первый и второй входы четвертогоэлемента ИЛИ соединены соответственно с выходом первой метки и дополнительным выходом первой метки третьегорегистра микрокоманды, а первый ивторой входы пятого элемента ИЛИподключены соответственно к выходувторой метки и дополнительному выходувторой метки третьего регистра микрокоманды. Цель изобретения - увеличениебыстродействия устройства,На фиг. 1 представлена функциональная схема предлагаемого микро программного устройства управления;3 1161941 4 57. 1, третьим 57.2, вторым 58. 1,четвертым 58,2 и пятым 59 управляющими входами, первый адресный выход60, второй адресный выход 61,числовой выход 62, операционныйвыход 63, третий адресный выход 64,информационный вход 65 блока управления, управляющий вход 66 блокауправления, блок 67 управления, управляющий 68 и информационный 69 выходы на фиг. 2 - функциональная схемавторого блока коммутаторов; на фиг. 3 функциональная схема первого блокакоммутаторов; на фиг. 4 - функциональная схема блока управления; нафиг. 5 - функциональная схема блокадешифраторов микроопераций; на фиг, 6форматы микрокоманд первого, второгои третьего блоков памяти; нафиг. 7 " фрагмент выполняемой микро О программы; на фиг. 8 - временные блока 67 управления, дешифратор 70, втодиаграммы работы блоков памяти для рой элемент И 71, третий элемент И 72,изображенного на фиг, 7 фрагмента второй блок 73 элементов ИЛИ, блокмикропрограммы. 74 дешифраторов микроопераций иМикропрограммное устройство управ в иод 5 Устройства.ления (фиг. 1) имеет адресный вход 1 Бторой блок 44 коммутатороввход 2 пуска и содержит первый блок (фиг, 2) содержит первый 76.1-76.п,3 элементов ИЛИ, первый элемент ИЛИ 4, второи 77. 1-77. п, третий 78. 1-78,ь,четвертый блок 5 элементов ИЛИ, гене. - Узлы элементов И, группу узлов элератор 6 тактовых импульсов, первый 20 ментов И 79.1-79. и, узел элементовИЛИ 80.1-80,н,элемент Иф 7, третий блок 8 элементовтор 11, счетчик 12 адреса, второй второй 82. 1-82. и узлы элементов И, пер- .вый узел элементов ИЛИ 83, 1-83.п, третийрегистр 13 адреса, второй одновибра 84,1-84.п,четвертый 85.1-85.п,пятыйтор 14, первый 15, второй 16 и третий17 блоки памяти, второй элемент ИЛИ 86.1-86,о, шестой 87.1-87.п, седьмойэлементов И, второй 90.1-90.пформационный регистр 20 с адресным орои 9 .1 90.п, девятый 91.1-91.ь, третий 92.1-92.и21, дополнительным адресным 22, опе- ЗО - . , Ретий 92, 1-92.п,четвертый 93.1-93.л узлы элементоврационным 23 полями, с полями первой,второй и третьей меток 24, 25 и 26ИЛИ десятый зел 94.1-94.п эле(фиг. 6 а), второй информационныйтов И и пятый 95,1-95,оый 95,1-95,о узел элементов ИЛИ.регистр 27 с адресным 28, операционными 29, 1-29.п полями и полями пер управления (фиг, 4) содер"Блок 67 п авления (фиг 4)вой и второй меток 30 и 31 (фиг,бб), жит элемент И 96 э двоичный счетчиктретий информационный регистр 3297 и элемент ИЛИ 98и двумя адресными 33.1 и 33.2, двумя лок 74 дешифраторов микрооперадополнительньии адресными 34,1 и ции (фиг. 5) содержит цешифраторы34.2, двумя операционными 35. 1 и 40микрооперации.35.2 полями, двумя полями первой . На фиг., 6 использованы следующиеметки 36.1 и 36,2 и двумя полями . обозначения: А- адресная частьвторой метки 37.1 и 37.2, первый 38 . . - дополнительная адреснаявторой 39 и третий 40 блоки элемен- ась или код количества операционтов И, четвертый 41 и пятый 42; 45 ых частей Я - опеРационная часть;элементы ИЛИ, пятый блок 43 элемен- Я ) - адресно-операционная часть;тов И, второй блок 44 коммутаторов с 1(= 1,) - операционные частипервым управляющим входом 45, первымуправляющим входом 46, вторым инфорсоответственно перваятретья метки,,мационным входом 47,1-47.в, вторымуправляющим входом 48, третьим управ- На фиг. 7 использованы обозначеляющим входом 49, с первым адресным ния: А; - адреса одиночных микровыходом 50, операционным выходом.51, команд 1 А - адреса участков операвторым адресным выходом 52 блока 44, ционных последовательностей; А1 Впервый блок 53 коммутаторов с первым 55 адреса микрокоманд, следующие за54.1, третьим 54,2, пятым 55.1, ветвлениями в микропрограммах;шестым 55.2, вторым 56,1, четвертым й - операционные части .микрокоманд156.2 информационными входами, первым Яф- операционные части последова 1161941тельностей микропрограммы; ю, и- количество операционных частей, которые считываются из соответствующей операционной последовательности; .- количество операционных частей,1 которое необходимо считать из операционной последовательности, х - логические условия.На Фиг. 8 показаны временные диаграммы работы блоков памяти для фрагмента микропрограммы, представленной на фиг. 7, при различных реализациях логических условий.Микропрограммное устройство управления (фиг. 1) работает следующим 15 образом.В исходном положении элементы памяти устройства находятся в нулевом состоянии. Предположим, что выполняется микропрограмма, Фрагмент 20 которой представлен на фиг. 7. Микропрограммное устройство управления выполняет одиночные Микрокоманды (режим 1), операционные последовательности микрокоманд (режим 2) и 25 микрокоманды, следующие после микро- команд ветвления (режим 3). Адрес первой микрокоманды с входа 1 через блок 3 подается на информационный вход регистра 10 одновременно с З 0 записью адреса, по которому необходимо считать микрокоманду из блока 15. с входа 2 пуска устройства через элемент 4 поступает на вход одновибратора 11 сигнал о начале работы устрой-ства. Одновибрагор 11 формирует импульс считывания, по которому считывается одиночная микрокомаща из блока 15 в регистр 20.При записи одиночной микрокоманды 40 из блока 15 в поле 21 регистра 20 записывается адрес очередной микро- команДы (фиг. 6 а), в поле 22 " адрес следующей микрокоманды, в поле 23 - операционная часть одиночной микро" 45 команды. В поле метки 24 записывается признак О, который определяется следующим образом; 1, если в.поле 22 записан/адрес микрокоманды, следующей эа ветвлением; й, - О, если в поле 22 записан адрес операционной последовательности или выполняются одиночные микрокоманды 55В поле метки 25 регистра 20 записывается признак р, который определяется следующим образом: 1, если в поле 22 записано количество М операционных частей последовательности;0 - в остальных случаях.В поле метки 26 регистра 26 записывается признак , который определяется следукнцим образом1, если в поле 21 записанадрес одиночной микрокоманды,0 в остальных случаях,Операционная часть Я поступившейодиночной микрокоманды с выхода 23регистра 20 через блок 23 поступаетна вход блока 74 и с его выходов навыход 75 устройства. Ацресная частьформируется в зависимости от того,из какого блока памяти необходимосчитать информацию в следующем микротакте работы устройства, т.е. определяется выполняемой. микропрограммой,Если после выполнения одиночнойгикрокоманды выполняется также одиночная микрокоманда, то адрес очередноймикрокоманды из поля 21 регистра 20через блок 3 заносится в регистр 1 О.Одновременно с этим в поле метки 26формируется признак .= 1. Этотпризнак - метка поступает через эле-.мент 4 на вход одновибратора 11, который формирует с задержкой Импульссчитывания информации из,блока 15 поадресу, записанному в регистре 10,Задержка формирования импульса считывания на выходе одновибратора необходимадля того, чтобы сформировать импульссчитывания раньше, чем будет сформированадрес очередной одиночной микрокомандыв регистре 10, Аналогичным образомпроходит функционирование устройствав режиме выдаяи одиноких микрокоманд.В последней одиночной микрокомандев поле метки 24 записывается признако= 1, который через элементы 18 и19 поступает на вход установки в"0" регистра 20 и приводит его висходное состояние,1Если в процессе выполнения одиночных микрокоманд необходимо перейтик выполнению операционной последовательности микрокоманд, то за микрокоманду до перехода к выполнениюнового режима работы в поле 22 первого информационного регистра заносится адрес операционной последовательности. Так как в поле метки 24признак о = О, а.в поле метки 25признак ; - О, то эти признаки, поступая на соответствующие входы блока 39, разрешают перезапись информации из поля 22 регистра 20 через блок 5 на информационный вход счетчика 12. В очередной (предпоследней) одиноч ной микрокоманде в поле 22 регистра 20 записывается количество частей М операционной последовательности микрокоманд по сформированному адресу из блока 16. В поле метки 25 записан Ц 1 признак Д= 1, который, поступая на второй вход блока 40, разрешает перезапись информации из поля 22 через блок 43 и вход 65 блока 67 на входы счетчика 9 (фиг, 4). 15После записи кода числа операционных последовательностей в счетчик 97 блока 67 его.состояние отлично от нулевого, и на выходе элемента 98 появляется сигнал логической "1". 20 Этот сигнал разрешает прохождение тактовых импульсов с выхода генератора 6 через элемент 96 на счетный вход счетчика 97, Кроме того сигнал с выхода 68 блока 67 через элементы 25 18 и 19 обнуляет регистр 20, а также через элемент 7 разрешает прохождение тактовых импульсов с выхода генератора 6 на выборку информации из блока 16. 30Импульс считывания информации поступает на управляющий вход блока 16 и производит выборку по адресу, заданному в счетчике 12. Этот же импульс изменяет адрес в .счетчике 12 З 5 при считывании операционных частей. Из блока 16 операционные части считываются в регистр 27, В поле 28 регистра 27 в зависимости от кода микропрограммы находится или адрес ф 0 одиночной мнкрокоманды, или адрес микрокоманды, следующей после ветвления, который поступает на вход 46 блока 44. Адрес очередной микрокоман(ы (или одиночной,или микроко манды, следующий после ветвления) ,с входа 46 блока 44 поступает на выход 50 или 52 в зависимости от признаков первой и второй меток соответственно в полях 30 и 31 регистра 27. 0Если в поле 28 находится адрес одиночной микрокоманды, то он с входа 46 блока 44 (фиг. 2) через блок 77.1- 77.о с выхода 50 через блок 3 поступает в регистр 10. Если в поле 28 5 записан адрес микрокоманды, следующей за ветвлением, то данный адрес с входа 46 блока 44 через блок 76.1-76.6. с выхода 52 через блок 8 поступает врегистр 13.Операционные части полей 29. 1-29.прегистра 27 поступают на входы 47.147,л блока 44. Операционная после"довательность через группу узлов79,1-70,о и группу узлов 80.1-80.поступает на выход 51 и через блоки73 и 74 - на выход 75 устройства. Пос.ле выдачи на выход 75 устройства количества операционных частей М, заданного в счетчике 97 блока 67(фиг. 4), на выходе 68 присутствуетсигнал логического "0". Этот сигналзапрещает прохождение тактовых импульсов с генератора 6 через элемент7 для считывания информации из блока16. В зависимости от признака, находящегося в поле метки 31, открывается элемент 71 или 72 (определяетсявидом очередной микрокоманды),Если очередная микрокоманда является одиночной то метка поля 30,равная единице, через элементы 71 и 4поступает на одновибратор 11 и начинается работа устройства в режимевыдачи одиночных микрокоманд указанным образом. Если очередная микрокоманда является микрокомандой,следующей эа ветвлением, то меткаполя 30, равная нулю, через элементы72 и 9 поступает на одновибратор 14и устройство переходит в режим выдачимикрокоманд, следующих после ветвлений.Если при выполнении микропрограммы устройству после выполнения отдель"ных микрокоманд необходимо перейти квыполнению микрокоманде, следующих после ветвлений, то в оле 22 предпоследней одиночной микрокоманды записывается адрес пары микрокоманд, выполняемых после ветвления. Метка поля24 регистра 20, равная единице, открывает блок 38 и адрес через блок 8поступает в регистр 13. Кроме того,метка поля 24 регистра 20 через элемент 9 поступает на одновибратор 14,Одновибратор 14 формирует импульсна считывание двух микрокоманд,следящих за ветвлением, блока 17 врегистр 32. Таким образом, одновременно с выполнением микрокоманды ветвления в регистр 32 иэ блока 17 записываются микрокоманды, следящие замикрокомандой ветвления, т,е. проходитопережающее считывание микрокоманд,поэтому после выполнения микрокоман-1 О одиночных микрокоманд к выполнениюоперационных последовательностей.Если очередная микрокомандапредставляет собой микрокоманду, следующую за ветвлением, то в этом случае из поля 33.1 или 33.2 на входы54,1 или 54,2 блока 53 проходиткод адреса микрокоманды, следующейпосле ветвления. Этот адрес с выхода 10 64 через блок 8 заносится в регистр13. Одновременно с этим метка изполя 36.1 или 36.2 через элемент 41и элемент 9 поступает на одновибратор 14. Операционные части в зави симости от выполнения логическогоусловия из поля 35.1 или 35.2 регистра 32 поступают на вход 56,1 или56.2 блока 53 и с выхода 63 черезблоки 73 и 74 поступают на выход 20 75 устройства. Далее работа устройства продолжается аналогичным образом.Предлагаемое устройство управленияобладает повышенным быстродействием 25 благодаря опережающему считываниюмикрокоманд различных типов и можетнайти применение при построении высокопроизводительных устройств исистем управления. 9 1161941ды ветвления нет необходимостиосуществлять выборку той или иноймикрокоманды в зависимости от выполнения логического условия, Переходк выполнению очередной микрокомандыопределяется кодом выполненного логического условия, псступивщего свхода 59 блока 53.Если очередная микрокомандаявляется одиночной, то адрес поля33.1 или 33.2 регистре 32 с выхода60 блока 53 через блок 3 поступаетв регистр 10. Одновременно месткаполя 37,1 или 37.2, равная единице,через элементы 42 и 4 поступает наодновибратор 11 и устройство продолжает работу по выдаче одиночных микрокоманд,Если необходимо выполнить операционную последовательность, то адресполя 33.1 или 33,2 с выхода 61 блока53 через блок 5 заносится в,счетчик 12, Количество операционных последовательностей в поле 34,1 или34,2 с выхода 62 блока 53 через блок43 записыьается в счетчик 97 блока 67.В этом случае работа устройства происходит аналогично, случаю, рассмотренному при переходе от выполнения

СмотретьЗаявка

3549923, 08.02.1983

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, БУРДА АЛЕКСАНДР ВЛАДИМИРОВИЧ, МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.06.1985

Код ссылки

<a href="https://patents.su/11-1161941-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Двухканальный генератор случайного процесса

Следующий патент: Мультимикропрограммное устройство управления

Случайный патент: Отказоустойчивый многофункциональный логический модуль