Устройство для умножения чисел в модулярной системе счисления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1352483

Авторы: Коляда, Ревинский, Селянинов, Чернявский

Текст

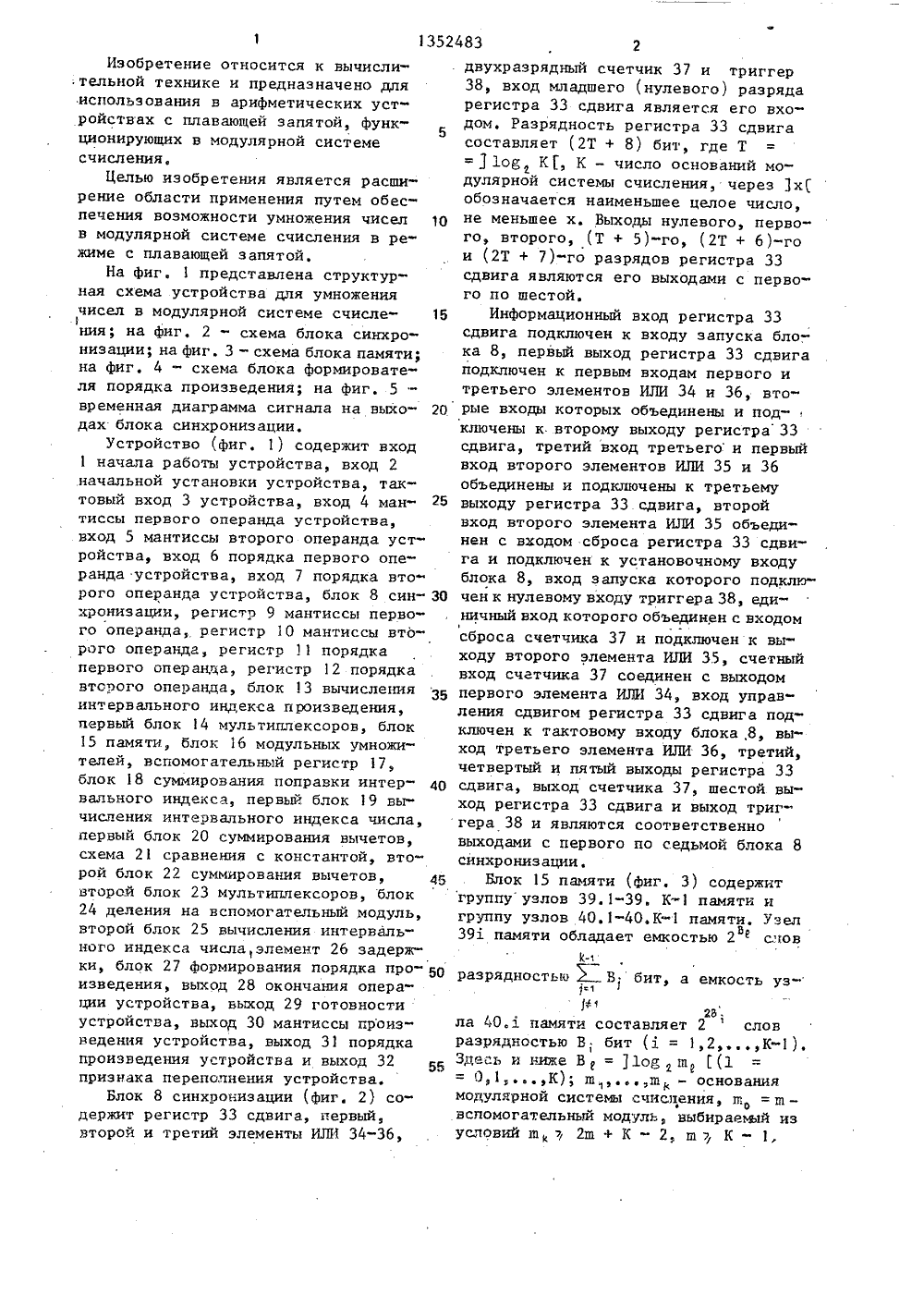

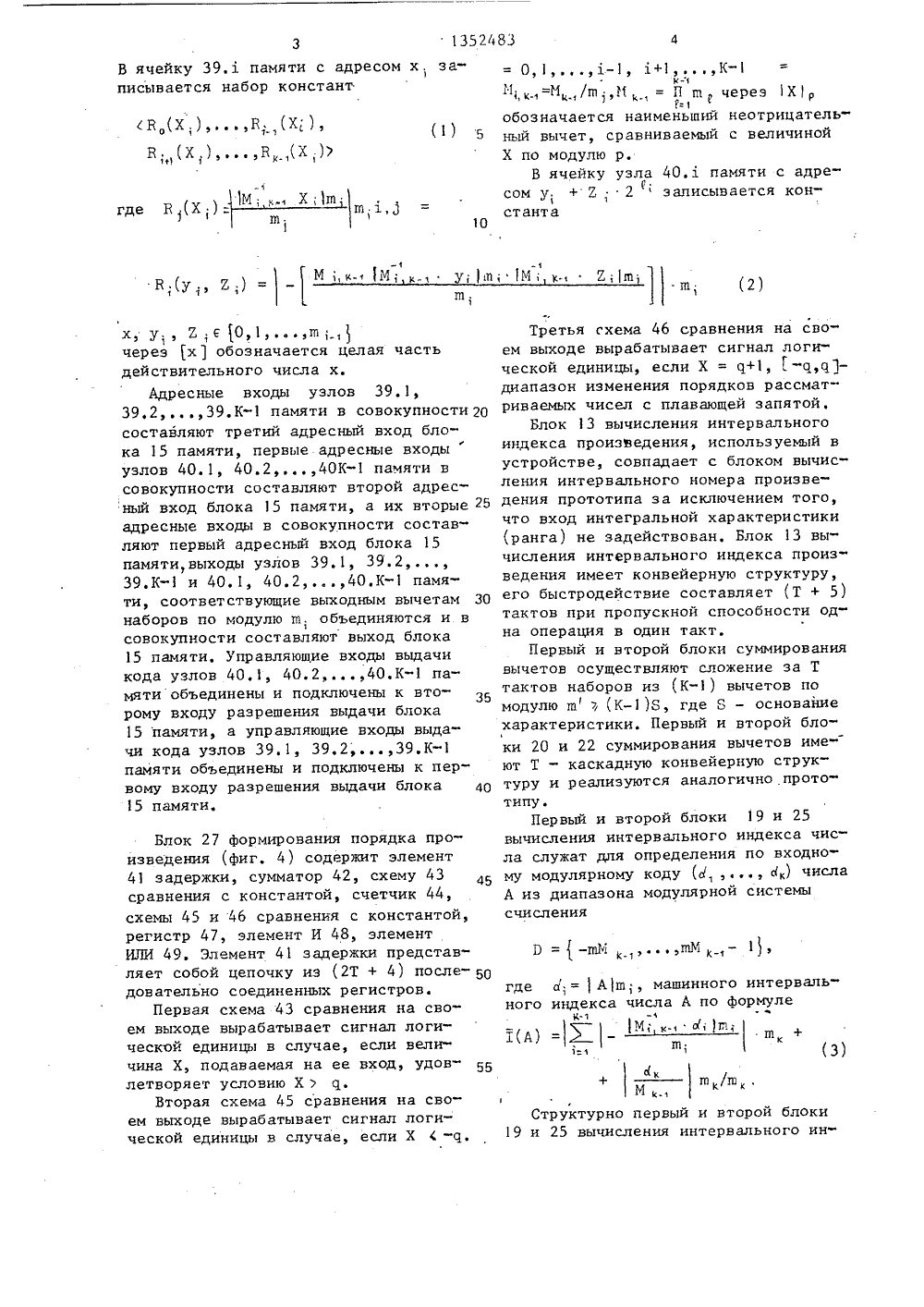

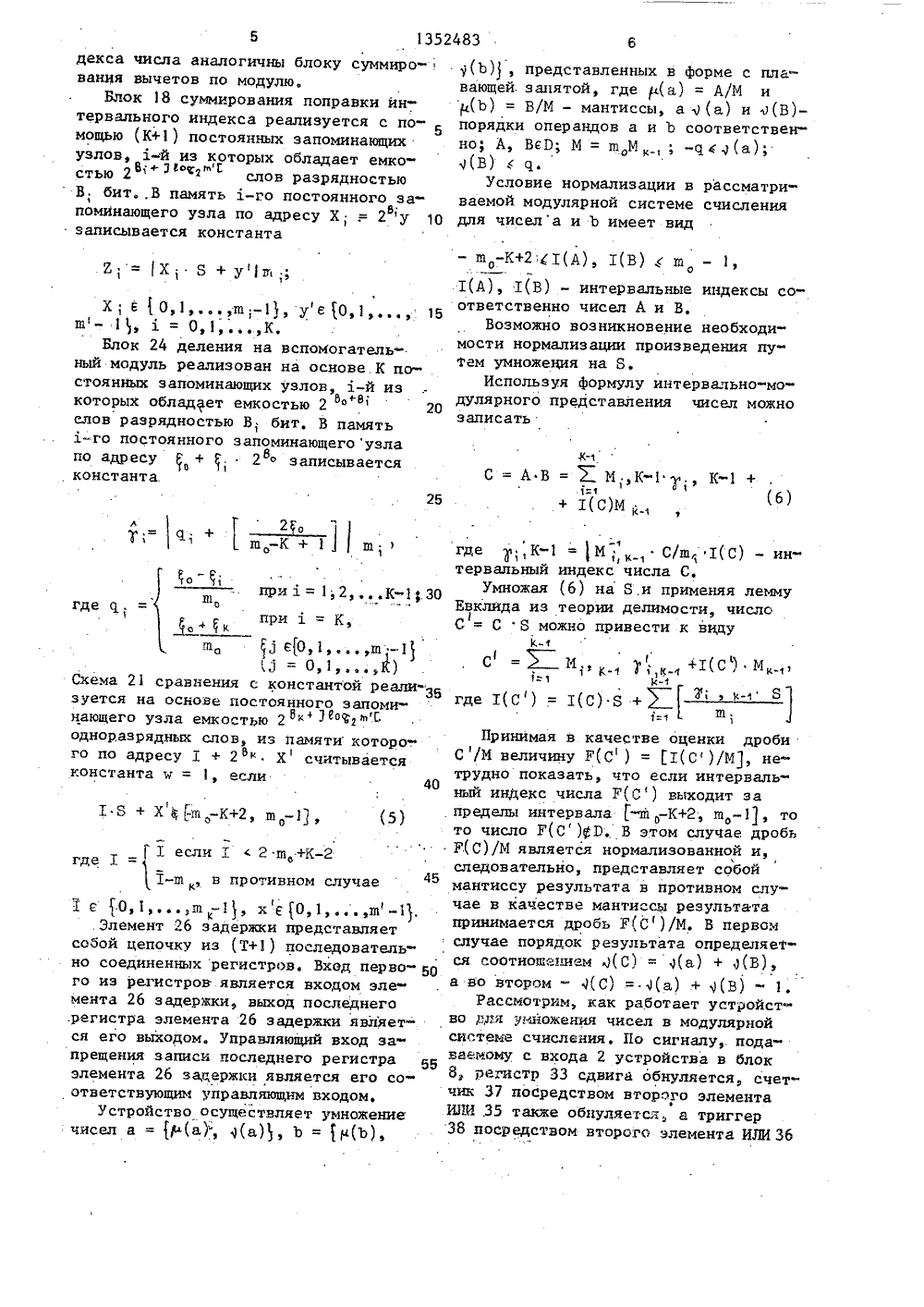

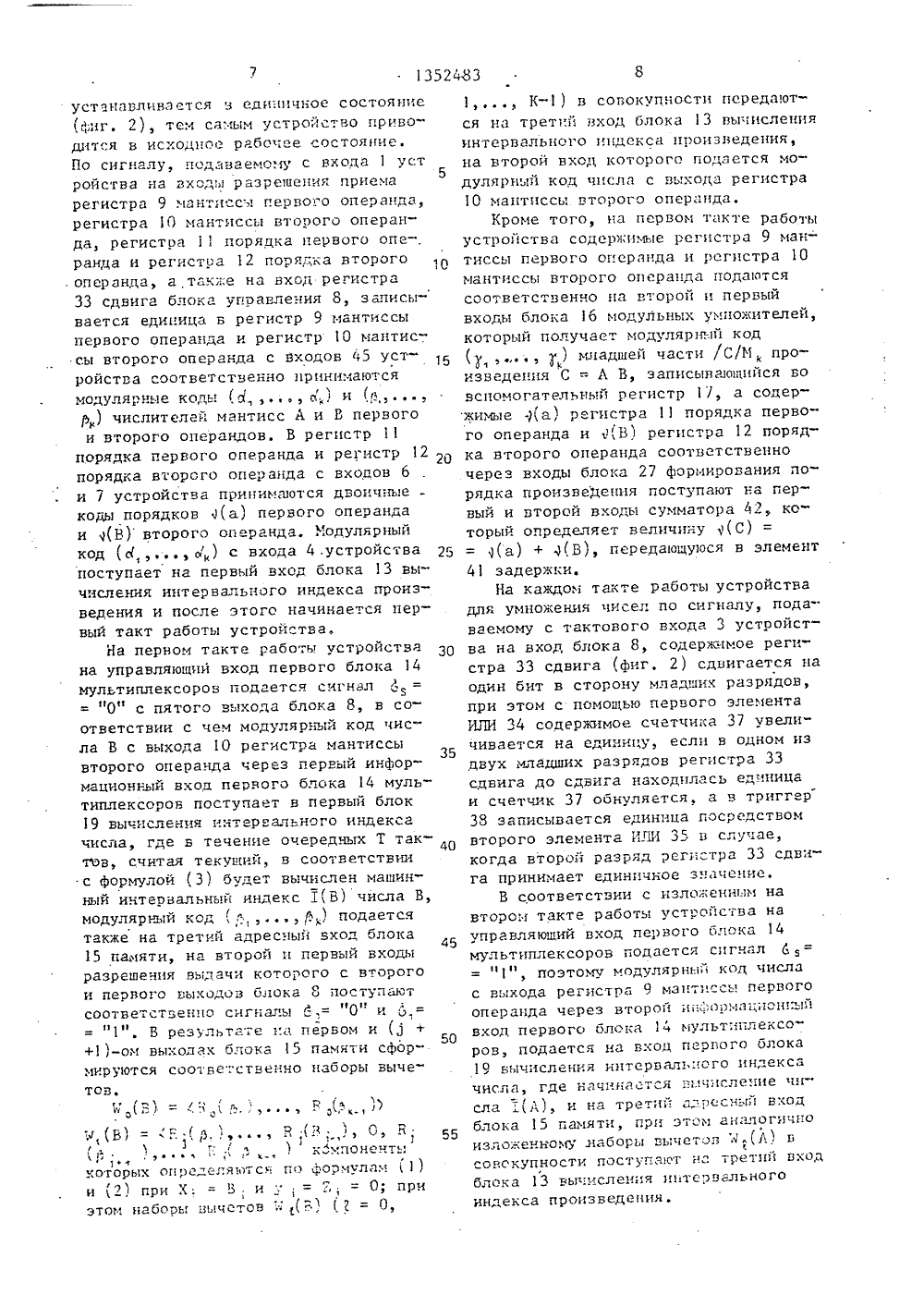

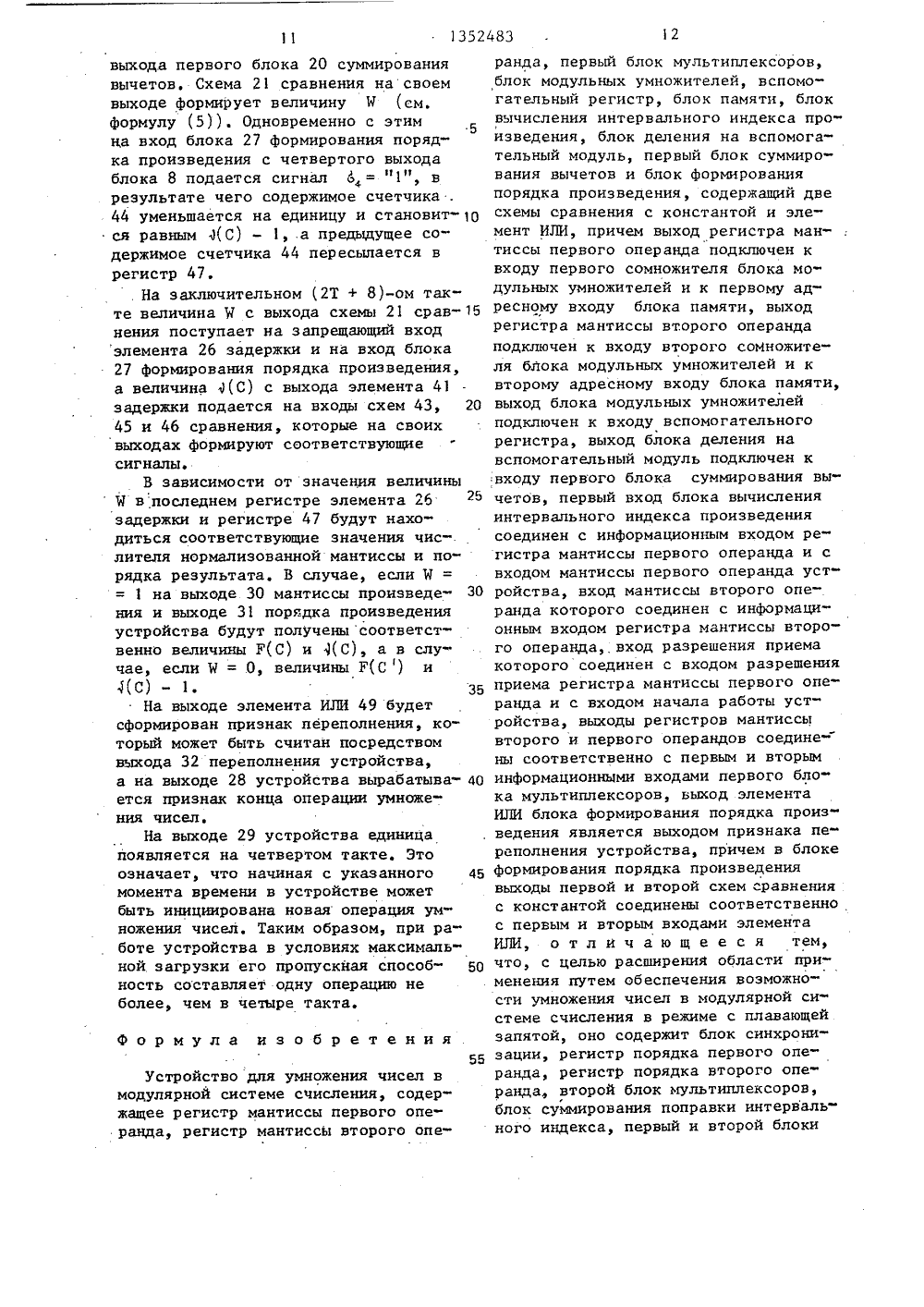

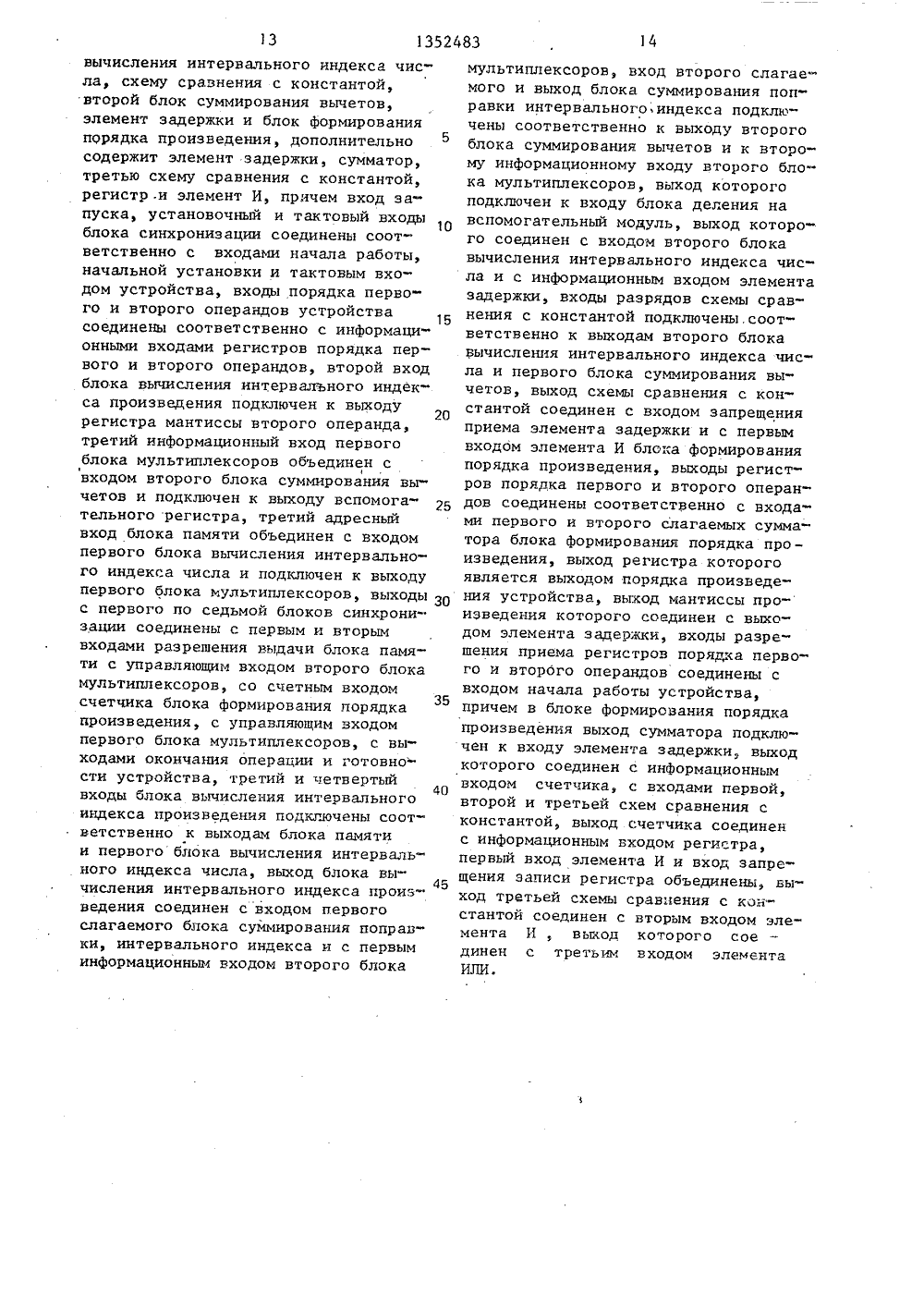

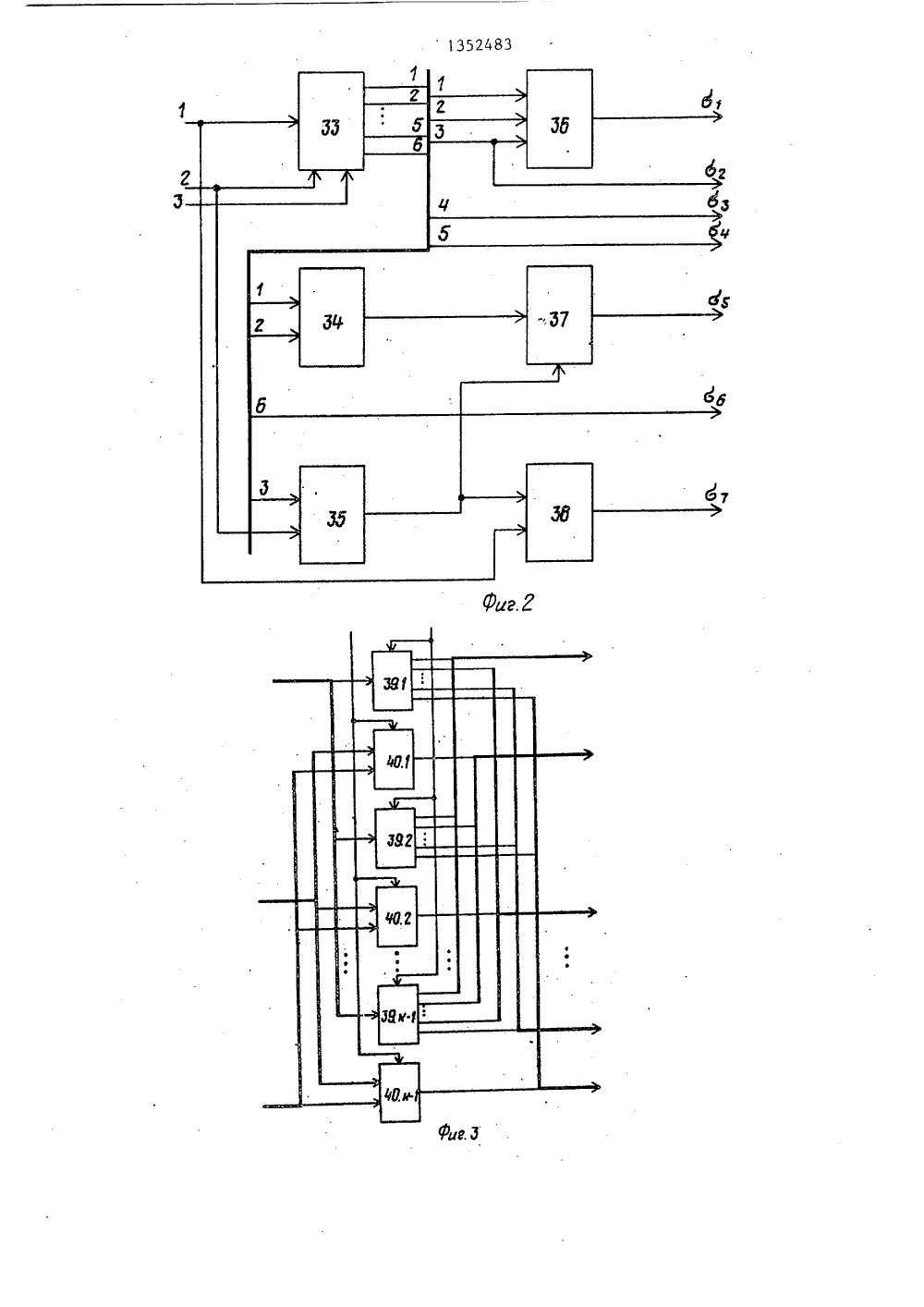

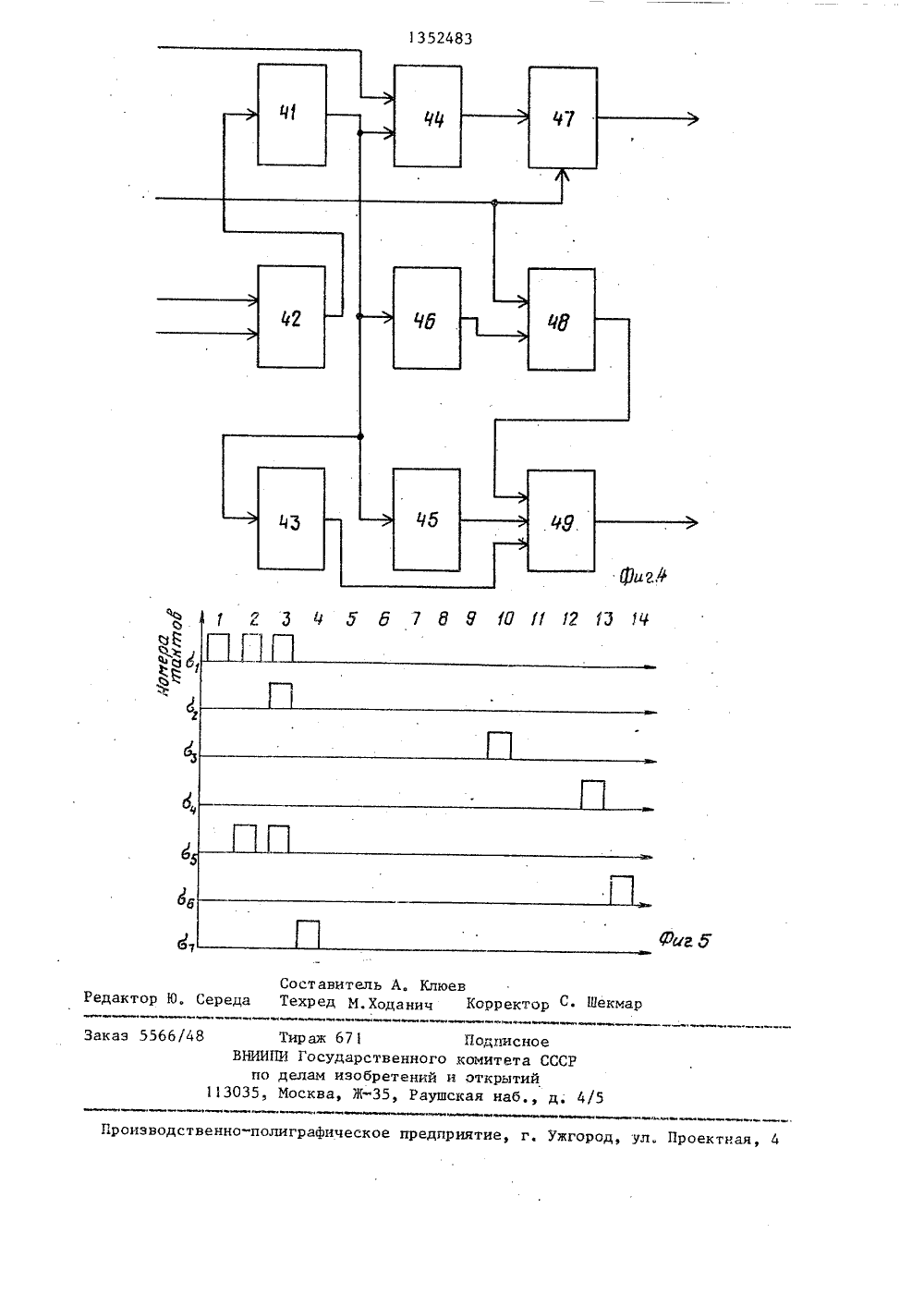

,1352483 А 1 СПУБЛИН 19) 06 Р 7/ 51) ИСАНИЕ ИЗОБРЕТЕНИВТОРСКОМУ СВИДЕТЕЛЬСТВУ ьский инстих проблем РеЧер скип ский идетельство СССР 06 Р 7/72, 1984. етельство СССР 06 Р 7/72, 1983.(54) УСТРОЙСТВО ДЛЯВ МОДУЛЯРНОЙ СИСТЕ(57) Изобретение олительной технике ЧИС УМНОЖЕНИЯ МЕ СЧИСЛЕНИЯ носится к1 чисо предназна арифметич щей запят ескихой,системерасшииспользовани устроиствах с пла одулярно бретения ункционирующих в числения, Цель из ение области прим беспечения умноже дсрка нения за ия чисел в модуГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское св1244665, кл, ОАвторское свид1149254, кл, 0 лярнои системе счисления в режиме с плавающей запятой, Поставленная цель достигается тем, что устройство для умножения чисел в модулярной системе счисления, содержащее регистры 9, 1 О мантиссы первого и второго операндов, блок 13 вычисления интервального индекса произведения, блок 14 мультиплексоров, блок 15 памяти, блок 16 модульных умножителей, вспомогательный регистр 17, блок 20 суммирования вычетов, блок 24 деления на вспомогательный модуль, содержит блок 8 синхронизации, регистры 11, 2 порядка первого и второго операндов, блок 18 суммирования поправки й интервального индекса, блоки 19, 25Ж вычисления интервального индекса числа, схему 21 сравнения с константой, блок 22 суммирования вычетов, блок 23 мультиплексоров, элемент 26 зажки и блок 27 формирования порядпроизведения с соответствующими связями, 5 ил.1352483 Составитель А. КлюевТехред И.Ходанич Корректор С, Юехмар Редактор Ю. Се каэ 5566/48 Производственно-полиграфическое предприятие, г. Ужгород, ул ктная, 4 Тираж 671 ВНИИПИ Государственног по делам иэобретений 113035, Москва, Ж, РаушПодписноекомитета СССРоткрытийская наб д. 4/20 25 рого операнда устройства, блок 8 синхронизации регистр 9 мантиссы первого операнда, регистр 10 мантиссы второго операнда, регистр 11 порядка 35 40 ного индекса числа, элемент 26 задержки, блок 27 формирования порядка про Изобретение относится к вычисли.тельной технике н предназначено для использования в арифметических устройствах с плавающей запятой, функционирующих в модулярной системе счисленияЦелью изобретения является расширение области применения путем обеспечения возможности умножения чисел в модулярной системе счисления в режиме с плавающей запятой.На фиг. 1 представлена структурная схема устройства для умножения чисел в модулярной системе счисления; на фиг. 2 - схема блока синхронизации; на фиг. 3 - схема блока памяти; на фиг. 4 - схема блока формирователя порядка произведения; на фиг, 5 временная диаграмма сигнала на выходах блока синхронизации,Устройство (фиг. 1) содержит вход 1 начала работы устройства, вход 2 начальной установки устройства, тактовый вход 3 устройства, вход 4 мантиссы первого операнда устройства,вход 5 мантиссы второго операнда устройства, вход 6 порядка первого операнда устройства, вход 7 порядка втопервого операнда, регистр 12 порядка второго операнда, блок 13 вычисленияинтервального индекса произведения,первый блок 14 мультиплексоров, блок15 памяти, блок 16 модульных умножителей, вспомогательнь".й регистр 17,блок 18 суммирования поправки интервального индекса, первый блок 19 вьг" числения интервального индекса числа,первый блок 20 суммирования вычетов,схема 21 сравнения с константой, второй блок 22 суммирования вычетов,второй блок 23 мультиплексоров, блок24 деления на вспомогательный модуль,второй блок 25 вычисления интервальизведения, выход 28 окончания операции устройства, выход 29 готовностиустройства, выход 30 мантиссы произведения устройства, выход 31 порядка произведения устройства и выход 32 признака переполнения устройства,Блок 8 синхронизации (фиг, 2) содержит регистр 33 сдвига, первый, второй и третий элементы ИЛИ 34-36,5 10 15 двухразрядный счетчик 37 и триггер38, вход младшего (нулевого) разрядарегистра 33 сдвига является его входом. Разрядность регистра 33 сдвигасоставляет (2 Т + 8) бит, где Т= .1 1 од К , К - число оснований модулярной системы счисления, через 1 х(обозначается наименьшее целое число,не меньшее х, Выходы нулевого, первого, второго, (Т + 5)-го, (2 Т + 6)-гои (2 Т + 7)-го разрядов регистра 33сдвига являются его выходами с первого по шестой.Информационный вход регистра 33сдвига подключен к входу запуска бло-.ка 8, первый выход регистра 33 сдвигаподключен к первым входам первого итретьего элементов ИЛИ 34 и 36, вто рые входы которых объединены и подключены к. второму выходу регистра 33сдвига, третий вход третьегои первыйвход второго элементов ИЛИ 35 и 36объединены и подключены к третьемувыходу регистра 33 сдвига, второйвход второго элемента ИЛИ 35 объединен с входом сброса регистра 33 сдвига и подключен к установочному входублока 8, вход запуска которого подключен к нулевому входу триггера 38, единичный вход которого объединен с входом1сброса счетчика 37 и подключен к выходу второго элемента ИЛИ 35, счетныйвход счетчика 37 соединен с выходомпервого элемента ИЛИ 34, вход управления сдвигом регистра 33 сдвига подключен к тактовому входу блока,8, выход третьего элемента ИЛИ 36, третий,четвертый и пятый выходы регистра 33сдвига, выход счетчика 37, шестой выход регистра 33 сдвига и выход триггера 38 и являются соответственновыходами с первого по седьмой блока 8синхронизации,Блок 15 памяти (фиг, 3) содержитгруппу узлов 39.1-39. Кпамяти игруппу узлов 40.1-40.Кпамяти, Узел39 памяти обладает емкостью 2словв;РразрядностьюВ бит, а емкость уз 11 фйв,ла 40, памяти составляет 2слонразрядностью В; бит ( = 1,2К).Здесь и киже В= Я 1 од ш Г(10 13,1,К); ш,ш - основаниямодулярной системы счиспения, и =ш -ф овспомогательный модуль, выбираемай изусловийш2 ш+ Кш, К,,В ( 2 1 - М 1 к М 1 к-У 1 п 1 1 М 1 к 12 ш шМ ,шМ- 1) 1 кМ ш,Ъ,В ячейку 39.1 памяти с адресом х. записывается набор констант х, у 2 е 0,1ш;,через х 1 обозначается целая частьдействительного числа х,Адресные входы узлов 39,1,39,239,Кпамяти в совокупности 20составляют третий адресный вход блока 15 памяти, первые адресные входыузлов 40.1, 40.240 Кпамяти всовокупности составляют второй адресный вход блока 15 памяти, а их вторые 25адресные входы в совокупности составляют первый адресный вход блока 15памяти, выходы узлов 39,1, 39,2,39.Ки 40.1, 40.240,Кпамяти, соответствующие выходным вычетам 30наборов по модулю ш. объединяются и всовокупности составляют выход блока15 памяти, Управляющие входы выдачикода узлов 40.1, 40.240,Кпамяти объединены и подключены к второму входу разрешения выдачи блока15 памяти, а управляющие входы выдачи кода узлов 39.1, 39.239,К памяти объединены и подключены к первому входу разрешения выдачи блока 4015 памяти,Блок 27 формирования порядка произведения (фиг. 4) содержит элемент 41 задержки, сумматор 42, схему 43 45 сравнения с константой, счетчик 44, схемы 45 и 46 сравнения с константой, регистр 47, элемент И 48, элемент ИЛИ 49, Элемент 41 задержки представляет собой цепочку из (2 Т + 4) после О довательно соединенных регистров.Первая схема 43 сравнения на своем выходе вырабатывает сигнал логической единицы в случае, если величина Х, подаваемая на ее вход, удовлетворяет условию Х )Вторая схема 45 сравнения на своем выходе вырабатывает сигнал логической единицы в случае, если Х С -о,= О,1,1-1, 1+1К к -111; .,=М /ш;,М к, = П ш через 1 Х)р обозначается наименьший неотрицательный вычет, сравниваемый с величиной Х по модулю р.В ячейку узла 40.1 памяти с адресом у. + 2 2записывается кон 1 1станта Третья схема 46 сравнения на своем выходе вырабатывает сигнал логической единицы, если Х = с 1+1,диапазон изменения порядков рассматриваемых чисел с плавающей запятой,Блок 13 вычисления интервальногоиндекса произведения, используемый вустройстве, совпадает с блоком вычисления интервального номера произведения прототипа за исключением того,что вход интегральной характеристики(ранга) не задействован, Блок 13 вычисления интервального индекса произведения имеет конвейерную структуРу,его быстродействие составляет (Т + 5)тактов при пропускной способности одна операция в один такт.Первый и второй блоки суммированиявычетов осуществляют сложение за Ттактов наборов из (К) вычетов помодулю п 1(К)Я, где Б - основаниехарактеристики. Первый и второй блоки 20 и 22 суммирования вычетов имеют Т - каскадную конвейерную структуру и реализуются аналогично прототипу.Первый и второй блоки 19 и 25вычисления интервального индекса числа служат для определения по входному модулярному коду (Ыяк) числаА из диапазона модулярной системысчисления где с; = 1 Аш;, машинного интервального индекса числа А по формуле Структурно первый и второй блоки 19 и 25 вычисления интервального ин(В)ЧУсловие нормализации в рассматриваемой модулярной системе счисления для чисела и Ь имеет вид- ш -К+21(А), 1(В) ( ш - 1,1(А), 1(В) - интервальные индексы соответственно чисел А и В.Возможно возникновение необходимости нормализации произведения путем умножеция на Б,Используя формулу интервально-модулярного представления чисел можнозаписать Е;= Х; Б + у 1 ш(6) 25- Ч+ где у;,К=М; , С/ш 1(С) - интервальный индекс числа С.Умножая (6) на Я.и применяя лемму Евклида из теории делимости, число С = СБ можно привести к видуК-ЬшПринимая в качестве оценки дробиС /М величину Р(С ) = 1(С)/М, нетрудно показать, что если интервальный инДекс числа Р(С) выходит за .пределы интервала -ш -К+2, ш,-1, то то число Р(С)Р, В этом случае дробь . Р(С)/М является нормализованной и, следовательно, представляет собой мантиссу результата в противном случае в качестве мантиссы результата принимается дробь У(С)/М. В первом случае порядок результата определяется соотношением 1(С) = 1(а) + 1(В)а во втором - 1(С) =.1(а) + (В) - 1.Рассмотрим, как работает устройство для умножения чисел в модулярнойсистеме счисления. По сигналу, подаваемому с входа 2 устройства в блок8, регистр ЗЗ сдвига обнуляется счетчик 37 посредством второго элементаИЛИ .35 также обнуляется а триггер38 посредством второго элемента ИЛИ 36 о1 = 1; 2, К1. Зогде Ч. =о1 при= К,о+ 1и Ц е 0,1ш Ц = 0,1К) Схема 21 сравнения с константой реали-З 5 зуется на основе постоянного запоминающего узла емкостью 2" Офодноразрядных слов, из памятикоторого по адресу 1 + 2 " Х считывается константа ч = 1, если 40(5) декса числа аналогичны блоку суммиро-вания вычетов по модулю.Блок 18 суммирования поправки интервального индекса реализуется с по 5 мощью (К+1) постоянных запоминающих узлов, -й из которых обладает емкостью 2" слов разрядностью;+ ро ьГВ. битВ память -го постоянного зав; поминающего узла по адресу Х - 2 у 10 записывается константа Б 1 Ое 1 еффф,ш;-1, у е 10,1., 15 ш-, х = 0,1К.Блок 24 деления на вспомогательный модуль реализован на основе К постоянных запоминающих узлов, -й изо+зкоторых обладает емкостью 220 слов разрядностью В; бит, В память -го постоянного запоминающего узла по адресу Е + . 2 о записывается константа 1 Б + Х-ш;К+2, ш -1, 1 если 1 с 2 ш +Кгде 1=т1-ш , в противном случае 1 е 0,1ш -1, х Е 0,1ш,.Элемент 26 задержки представляет собой цепочку из (Т+1) последовательно соединенных регистров. Вход перво го из регистров является входом элемента 26 задержки, выход последнего .регистра элемента 26 задержки является его выходом Управляющий вход запрещения записи последнего регистра элемента 26 задержки является его соответствующим управляющим входом.Устройство осуществляет умножение чисел а =(а), с)(а), Ь =(Ь) К-С = А В = с . М , К у , , К +1-) ,1оп е "с"яютс по,вормъл 1 (1)риХ; = В.и;,=К,=О; при1боры вычетов,1 ( 2 = О,55 устанавливается в единичное состояние (фиг, 2), тем самым устройство приводится в исходное рабочее состояние. По сигналу, подаваемо.л с входа 1 уст ройства на входы разрешения приема5 регистра 9 мантиссы первого операнда, регистра О мантиссы второго операнда, регистра 11 поряцка первого опе-. ранда и регистра 12 порядка второго . операнда, а таки;е на вход регистра 33 сдвига блока угравления 8, записы- вается единица в регистр 9 мантиссы первого операнда и регистр О мантиссы второго операнда с Входов 45 устройства соответственно принимаются модулярные коды (.(, ок) и (,о,, р ) числителеи мантисс А и В первогоКи второго операндов. В регистр 11 порядка первого операнда и регистр 12 порядка второго операнда с входов 6 и 7 устройства принимаются двоичные коды порядков а) первого операнда и 1(Б) ВторОГО Операндае Модулярный код (с(, с,) с входа 4 .устройства поступает на первый вхоп блока 13 вычисления интервального индекса произведения и после этого начинается первый такт работы устройства.На первом такте работы устройства на управляющии вход первого блока 14 мультиплексоров подается с лгнал 5 = "О" с пятого выхода блока 8, в соответствии с чем модулярный код числа В с выхода 10 регистра мантиссы35 второго операнда через первый информационный вход первого блока 14 мультиплексоров поступает в первый блок 19 вычисления интервального индекса числа Где в течение Очередных Т так О тов, считая текущий, в соответствии с формулой (3) будет вычислен машинный интервальный индекс 1(В) числа В, модулярньй код (,",л,) подается также на третий адресный вход блока 15 памяти, на второй и первый входы разрешения выдачи которого с второго и первоГО выходов 631 оеа 8 поступают11 3.М соответственно сигнаы д,= Ои = "1", В результате 1.а первом и (150 +1)-ом выходах блока 5 памяти сформируются соответственно наборы вычеК) в согокупности передаются на трет.й вход блока 3 вычисленияинтервального идакса произведения,на второй вход которого подается модулярный код числа с выхода регистра1 О мантиссы второго операнда.Кроме того, на первом такте работыустройства содержимые регистра 9 мантиссы первого операнда и регистра 10мантиссы второго операнда подаютсясоответственно на второй и первыйвходы блока 1 б модульных умножителей,который получает модулярный коц(у у ) младшей части /С/Мпроизведения С =- Л В, эаписывающийся воВспомогательный регистр 7, а содержимые -1(а) регистра 11 порядка первого операнда и (В) регистра 12 порядка второго операнда соответственночерез входы блока 27 формирования порядка произведения поступают на первый и второй входы сумматора 42, который определяет величину (С)- (а) + (Б), передающуюся в элемент41 задержки,На каждом такте работы устройствадля умножения чисел по сигналу, подаваемому с тактового входа 3 устройства на вход блока 8, содерымое регистра 33 сдвига (фиг, 2) сдвигается наодин бит в сторону младших разрядов,при этом с помощью первого элементаИЛИ 34 содержимое счетчика 37 увели"чивается на единицу, если в одном из,цвух младших разрядов регистра 33сцВиГа дО сдвига находилась единицаи счетчик 37 обнуляется, а в триггер38 записывается единица посредствомвторого элемента ИГЛ 35 в случае,когда второй разряд реги"тра 33 сдвига принимает единичное значение,В соответствии с изложенилм навтором такте работы устройства науправляющий вход первого блока 14мультиплексоров подается сигнал"1, поэтому модулярный код числас выхода регистра 9 мантиссы первогооперанда через второй ин:ормацион 1:ыиВход перВОГО Олокя 14 мульт:п 1 лексоров, подается на вход первого блока19 вычисления и 1 тервал 1.ого индексачисла, где начинается вычисление числа(А), и на третий адресный входблока 15 памяти, при этом аналогичноизложенному яаборы вь;четов :(.(Л всовокупности поступают на трет 1 й входблока 13 Вычисления интервальногоиндекса произведения, 1352483 О)(С) = (Н;( у,),Н (РЭ компоненты которых определяются по формулам (1) и (2) при Х= р; у.Е; = Ы;,при этом наборй вычетов У(С) в совокупности передаотся на третий вход блока 13 вычисления интервального индекса произведения.На пятом такте работы устройства модулярный код (у у ) с выхода вспомогательного регистра 17 пода ется на вход второго блока 22 суммирования вычетов, где в течение очередных Т тактов, считая текущий, буд т вычислена величина-1М .,;1 ш;, Яш 1)-ом такте машинный ининдекс 1(В) числа В с выНа (Т + тервальныи,сленья и 19 а первого блокавального индход блока 1о декса пр т екса чи в .а поступае3 вычисления интервальоизведения,а в 0На (Т + 2)-ом такте машиый интервальньй индекс (Л) числа Л с выхода первого блока 9 вычисления ин- тервального индекса числа поступает на вход блока 13 вычисления интервального индекса произведения.На (Т + 5)-ом такте блок 13 выения интервального индекса произведениязавершает вычисление интерисл На третьем такте работы устройства модуляриый код (у у) числа./ С/ с выхода вспомогательного регистра 17 через третий информациошый вход первого блока 14 мультиплексоров,5 на управляющий вход которого подается сигнал 6 = "2", поступает на третий адресный вход блока 15 памяти, на . второй и первый адресные входы. которо.10 го подаются соответственно коды чисел В с регистра 1 О мантиссы второго операнда и А - с регистра 9 мантиссы первого операнда, На второй и первый входы разрешения выдачи блока 15 памяти подаются сигналы 6 = "1" и 6,= = "1", в результате на первом и . + + 1)-ом выходах блока 15 памяти сформируются соответственно наборы констант 20 вального индекса 1(С) числа С, 1(С) = ( ).Йа (Т + 6)-ом такте работы устройства на упраляющй вход второго блока 23 лультшексоров с третьего выхода блока 8 подается сигнал 6 = "О", поэтому модулярный код величины 1( С).поступающий с выхода блока 13 вычисления иитервгльного индекса произведения на первый ичформационный вход второго блока 23 мультиплексоров, подается на вход блока 24 деления на вспомогательный модуль. Одновременно с этим величина 1(С) поступает на первый вход блока 18 суммирования поправки интервального индекса, на второй вход которого с выхода второго блока 22 суммирования вычетов поступает величина. Блок 18 на своем выходе сформируетмодулярный код (, ) величины 1(СНа (Т + 7)-ом такте блок 24 деления на вспомогательный модуль определяет модулярщй код ( ъ ъ ) величины Г(С), который передается в элемент 26 задержки, а также поступает на входы первого блока 20 сужирования вычетов и второго блока 25 вычисления интервального индекса числа, где в течение очередных Т тактов, считая текущий, будут вычислены соответственно величиныХ = с шП и 1(Р(С, Одновременно с этим на управляющий вход второго блока 23 мультиплексоров подается сигнал 6 = "1", в соответствгл с.чем модулярный код величчны 1(С), поступающий с выхода блока 18 на второй информационный вхсд блока 23 мультиплексоров, подается на вход блока 24 деления на вспомогательный модульНа (Т + 8)"о такте работы устрой ства блок 24 деления на вспомогателььк модуль опрелепяет мопулярты код (Л 1 л;уу, ) вели ины ." (ь ), которьн передается в элемент 26 задержки,На (2 Т + 6)-ом такте величины)(С) с выхода элемента 41 задержки поступают в счетчик 44;1,а (2 Т + 7)-ом такте работы устройства на вход схемы 21 сравнепя сРо" стятой оступают . Мплаииь 1(Р () ) с выхода второо блока 25 ычислепяинтервального идекса числа.и Хвыхода первого блока 20 суммирования вычетов. Схема 21 сравнения на своем выходе формирует величину У (см.формулу (5. Одновременно с этим иа вход блока 27 формирования порядка произведения с четвертого выхода блока 8 подается сигнал 6 = "1", в результате чего содержимое счетчика .44 уменьшается на единицу и становит ся равным 1(С) - 1, .а предыдущее содержимое счетчика 44 пересылается в регистр 47.На заключительном (2 Т + 8)-ом такте величина У с выхода схемы 21 срав кения поступает на запрещающий вход элемента 26 задержки и на вход блока 27 формирования порядка произведения, а величина 1(С) с выхода элемента 41 задержки подается на входы схем 43, 20 45 и 46 сравнения, которые на своих выходах формируют соответствующие сигналы.В зависимости от значения величины Ч впоследнем регистре элемента 26 задержки и регистре 47 будут находиться соответствующие значения чис-. лителя нормализованной мантиссы и порядка результата, В случае, если М =1 на выходе 30 мантиссы произведе- З 0 ния и выходе 31 порядка произведения устройства будут получены соответственно величины Р(С) и 4 С), а в случае, если Ю = О, величины Р(С ) и 1(С) - 1.35На выходе элемента ИЛИ 49 будет сформирован признак переполнения, который может быть считан посредством выхода 32 переполнения устройства, а на выходе 28 устройства вырабатыва ется признак конца операции умножения чисел.На выходе 29 устройства единица появляется на четвертом такте. Это означает, что начиная с указанного 45 момента времени в устройстве может быть инициирована новая операция умножения чисел. Таким образом, при работе устройства в условиях максимальной загрузки его пропускная способ ность составляет одну операцию не более, чем в четыре такта. Формула изобретения55 Устройство для умножения чисел в модулярной системе счисления, содержащее регистр мантиссы первого операнда, регистр мантиссы второго операнда, первый блок мультиплексоров,блок модульных умножителей, вспомогательный регистр, блок памяти, блоквычисления интервального индекса произведения, блок деления на вспомогательный модуль, первый блок суммирования вычетов и блок формированияпорядка произведения, содержащий двесхемы сравнения с константой и элемент ИЛИ, причем выход регистра мантиссы первого операнда подключен квходу первого сомножителя блока модульных умножителей н к первому адресному входу блока памяти, выходрегистра мантиссы второго операндаподключен к входу второго сомножителя блока модульных умножителей и квторому адресному входу блока памяти,выход блока модульных умножителейподключен к входу вспомогательногорегистра, выход блока деления навспомогательный модуль подключен квходу первого блока суммирования вычетов, первый вход блока вычисленияинтервального индекса произведениясоединен с информационным входом регистра мантиссы первого операнда и свходом мантиссы первого операнда устройства, вход мантиссы второго операнда которого соединен с информационным входом регистра мантиссы второго операнда вход разрешения приемакоторого соединен с входом разрешенияприема регистра мантиссы первого операнда и с входом начала работы устройства, выходы регистров мантиссывторого и первого операндов соедине=ны соответственно с первым и вторыминформационными входами первого блока мультиплексоров, ьыход элементаИЛИ блока формирования порядка произведения является выходом признака переполнения устройства, причем в блокеформирования порядка произведениявыходы первой и второй схем сравненияс константой соединены соответственнос первым и вторым входами элементаИЛИ, о т л и ч а ю щ е е с я тем,что, с целью расширения области применения путем обеспечения воэможности умножения чисел в модулярной системе счисления в режиме с плавающейзапятой, оно содержит блок синхронизации, регистр порядка первого операнда, регистр порядка второго операнда, второй блок мультиплексоров,блок суммирования поправки интервального индекса, первый и второй блокивычисления интервального индекса числа, схему сравнения с константой, второй блок суммирования вычетов, элемент задержки и блок формирования пОрядка произведения, дополнительно содержит элемент задержки, сумматор, третью схему сравнения с константой, регистр .и элемент И, причем вход запуска, установочный и тактовый входы блока синхронизации соединены соот ветственно с входами начала работы, начальной установки и тактовым входом устройства, входы порядка первого и второго операндов устройства соединены соответственно с информационными входами регистров порядка первого и второго операндов, второй вход блока вычисления интервалъного индекса произведения подключен к выходу регистра мантиссы второго операнда, третий информационный вход первого блока мультиплексоров объединен с 1входом второго блока суммирования вьг" четов и подключен к выходу вспомогательного регистра, третий адресный вход блока памяти объединен с входом первого блока вычисления интервального индекса числа и подключен к выходу первого блока мультиплексоров, выходы ЗО с первого по седьмой блоков синхронизации соединены с первым и вторым входами разрешения выдачи блока памяти с управляющим входом второго блока мультиплексоров, со счетным входом счетчика блока формирования порядка35 произведения, с управляющим входом первого блока мультиплексоров, с выходами окончания операции и готовно- сти устройства третий и четвертый40 входы блока вычисления интервального индекса произведения подключены соответственно к выходам блока памяти и первого блока вычисления интервального индекса числа, выход блока вычисления интервального индекса произведения соединен с входом первого слагаемого блока суммирования поправки, интервального индекса и с первым информационным входом второго блока мультиплексоров, вход второго слагаемого и выход блока суммирования поправки интервального индекса подключены соответственно к выходу второго блока суммирования вычетов и к второму информационному входу второго блока мультиплексоров, выход которого подключен к входу блока деления на вспомогательный модуль, выход которого соединен с входом второго блока вычисления интервального индекса числа и с информационным входом элемента задержки, входы разрядов схемы сравнения с константой подключены,соответственно к выходам второго блока вычисления интервального индекса числа и первого блока суммирования вычетов, выход схемы сравнения с константой соединен с входом запрещения приема элемента задержки и с первым входом элемента И блока формирования порядка произведения, выходы регистров порядка первого и второго операндов соединены соответственно с входами первого и второго слагаемых сумматора блока формирования порядка про - изведения, выход регистра которого является выходом горядка произведения устройства, выход мантиссы произведения которого соединен с выходом элемента задержки, входы разрешения приема регистров порядка первого и второго операндов соединены с входом начала работы устройства, причем в блоке формирования порядкапроизведения выход сумматора подключен к входу элемента задержки, выход которого соединен с информационным входом счетчика, с входами первой, второй и третьей схем сравнения с константой, выход счетчика соединен с информационным входом регистра, первый вход элемента И и вход запрещения записи регистра объединены, выход третьей схемы сравнения с кон" стантой соединен с вторым входом элемента И , выход которого сое динен с третьщ входом элемента ИЛИ.

СмотретьЗаявка

4080969, 26.05.1986

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИКЛАДНЫХ ФИЗИЧЕСКИХ ПРОБЛЕМ ИМ. А. Н. СЕВЧЕНКО

КОЛЯДА АНДРЕЙ АЛЕКСЕЕВИЧ, РЕВИНСКИЙ ВИКТОР ВИКЕНТЬЕВИЧ, СЕЛЯНИНОВ МИХАИЛ ЮРЬЕВИЧ, ЧЕРНЯВСКИЙ АЛЕКСАНДР ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: модулярной, системе, счисления, умножения, чисел

Опубликовано: 15.11.1987

Код ссылки

<a href="https://patents.su/10-1352483-ustrojjstvo-dlya-umnozheniya-chisel-v-modulyarnojj-sisteme-schisleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел в модулярной системе счисления</a>

Предыдущий патент: Умножитель частоты

Следующий патент: Программируемый контроллер

Случайный патент: Способ производства клееной фанеры