Вычислительный преобразователь информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

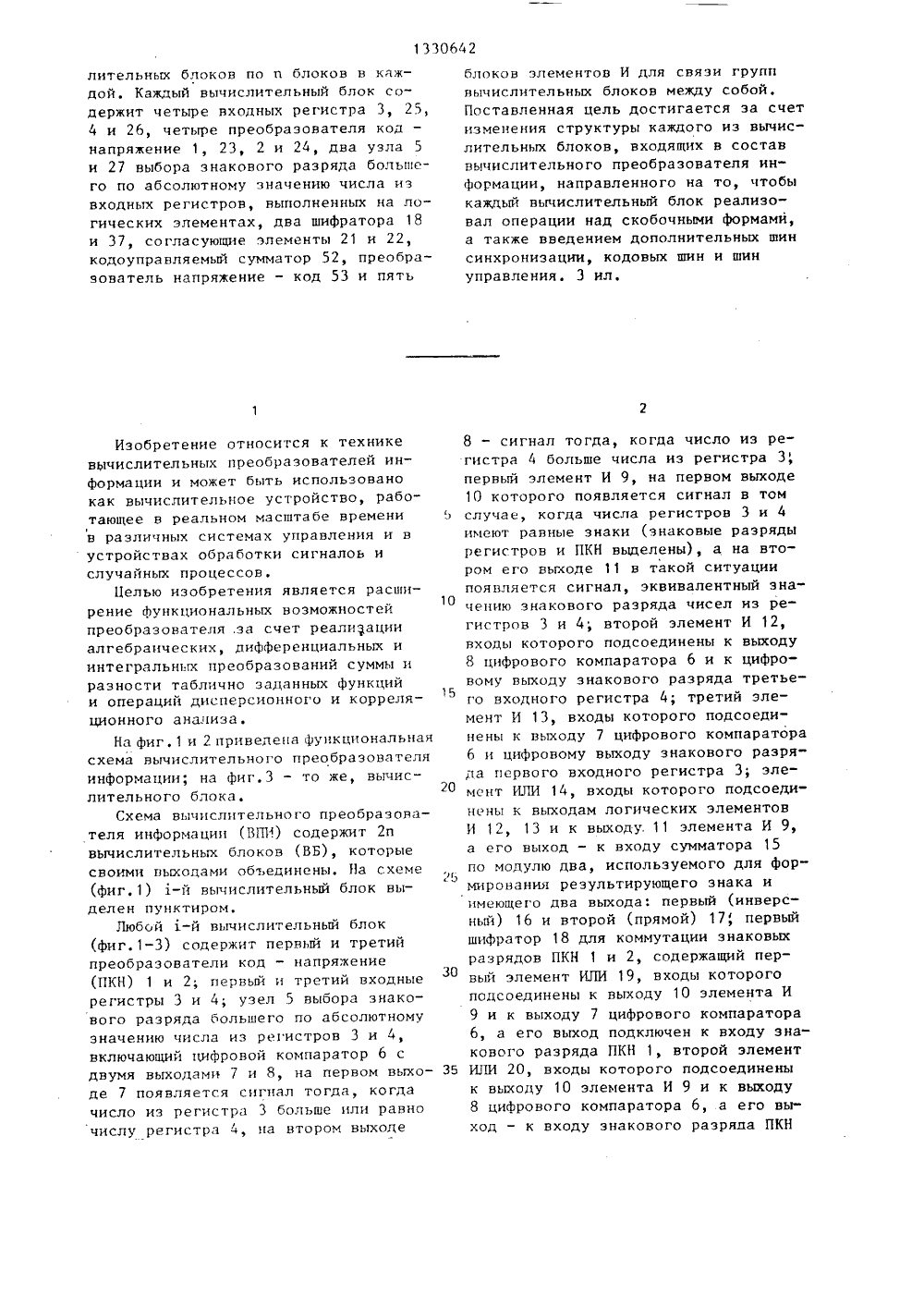

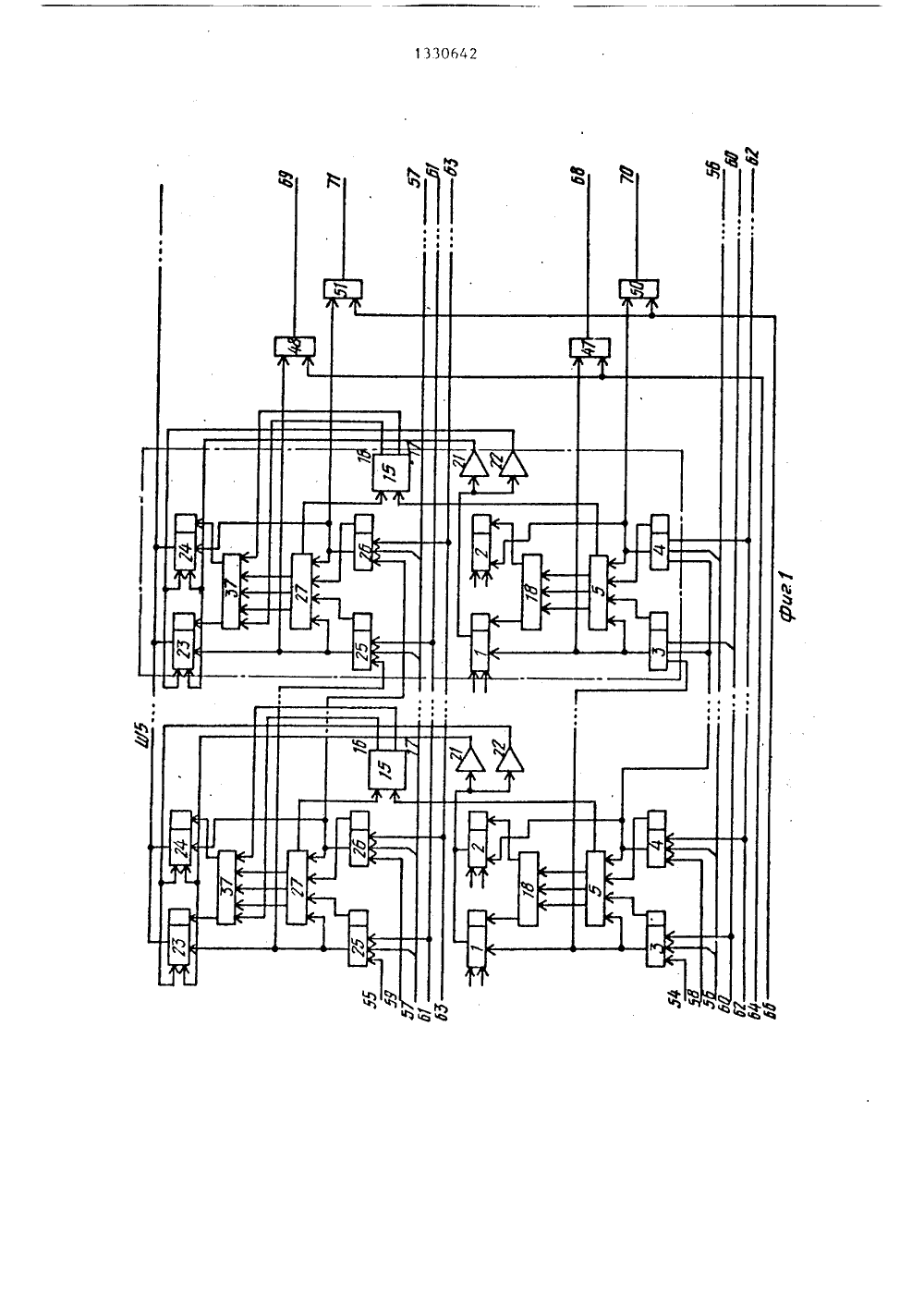

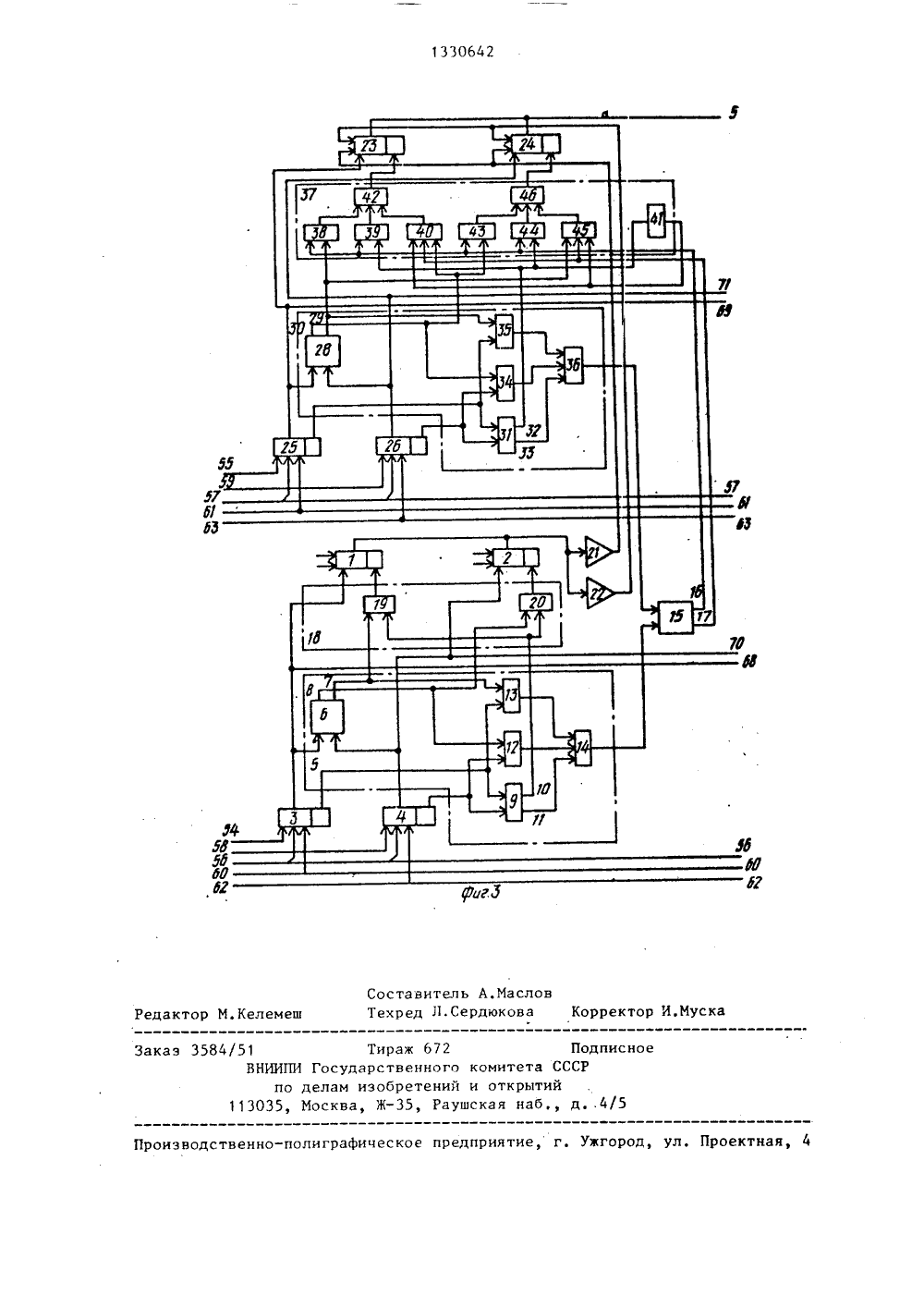

(50 4 С 0 ИСАНИЕ ИЗОБРЕТЕНИ как вычиотающее в30. Григорьев в различустройствахрсионного и ых системах управ бработки сигналов орреляционного ан анных случайных в ния, дисп ецентриро соры Раоцессов ропро лич я распп ностей е- релстемы. льство Л 1/00,ние функци образовате гебраическ нальных возм ССР.1985 я за счет реализаци х, дифференциальных иний и,ных преобразованити таблично эаданний дисперсионного тег и суммы х функ(57) Изобретение оттельным преобразова ЕОБРАЗОВАТЕЛЬ разнос операц онного корреляцильныи преоб руппы вычис нал а. Вычисл держит дв ситс вычислирмации разовательА елям йа Ж СУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ К А ВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Смолов В.Б. Мимикропроцессорные си связь, 1981, с.32Авторское свидет1176351, кл. С 06 и может быть использова лительное устройство, р реальном масштабе време елью изобретения являет1330642 Составитель А, Масловтор М.Келемеш Техред Л.Сердюкова Корректор И.Мус едприятие город, ул. Проектна 57 б 1 О каэ 3584/51 ВНИИПИ Госу амит по делам и отк 113035, Москв кая1330642 8 - сигнал тогда, когда число из регистра 4 больше числа из регистра 3, первый элемент И 9, на первом выходе 10 которого появляется сигнал в том случае, когда числа регистров 3 и 4 имеют равные знаки (энаковые разряды регистров и ПКН выделены), а на втором его выходе 11 в такой ситуации появляется сигнал, эквивалентный значению знакового разряда чисел из регистров 3 и 4, второй элемент И 12, входы которого подсоединены к выходу 8 цифрового компаратора 6 и к цифровому выходу знакового разряда третьего входного регистра 4; третий элемент И 13, входы которого подсоединены к выходу 7 цифрового компаратора 6 и цифровому выходу знакового разряда первого входного регистра 3; элемент ИЛИ 14, входы которого подсоединены к выходам логических элементов И 12, 13 и к выходу. 11 элемента И 9, а его выход - к входу сумматора 15 по модулю два, используемого для формирования результирующего знака и имеющего два выхода; первый (инверсный) 16 и второй (прямой) 17, первый шифратор 18 для коммутации знаковых разрядов ПКН 1 и 2, содержащий первый элемент ИЛИ 19, входы которого подсоединены к выходу 10 элемента И 9 и к выходу 7 цифрового компаратора 6, а его выход подключен к входу знакового разряда ПКН 1, второй элемент ИЛИ 20, входы которого подсоединены к выходу 10 элемента И 9 и к выходу 8 цифрового компаратора 6, а его выход - к входу знакового разряда ПКН лительных блоков по п блоков в каждой. Каждый вычислительный блок содержит четыре входных регистра 3, 25,4 и 26, четыре преобразователя коднапряжение 1, 23, 2 и 24, два узла 5и 27 выбора знакового разряда большего по абсолютному значению числа извходных регистров, выполненных на логических элементах, два шифратора 18и 37, согласующие элементы 21 и 22,кодоуправляемый сумматор 52, преобразователь напряжение - код 53 и пять Изобретение относится к технике вычислительных преобразователей информации и может быть использовано как вычислительное устройство, работающее в реальном масштабе времени в различных системах управления и в устройствах обработки сигналоь и случайных процессов.Целью изобретения является расширение функциональных возможностей преобразователя .за счет реализации алгебраических, дифференциальных и интегральных преобразований суммы и разности таблично заданных функций и операций дисперсионного и корреляционного анализа.На фиг. 1 и 2 приведена функциональная схема вычислительного преобразователя информации; на фиг.3 - то же, вычислительного блока.Схема вычислительного преобразователя информации (ВПИ) содержит 2 п вычислительных блоков (ВБ), которые своими выходами объединены. На схеме (фиг.1) д-й вычислительный блок выделен пунктиром.Любой 1-й вычислительный блок (фиг.1-3) содержит первый и третий преобразователи код - напряжение (ПКН) 1 и 2; первый и третий входные регистры 3 и 4; узел 5 выбора знакового разряда большего по абсолютному значению числа из регистров 3 и 4, включающий цифровой компаратор 6 с двумя выходами 7 и 8, на первом выходе 7 появляется сигнал тогда, когда число из регистра 3 больше или равно числу регистра 4, на втором выходе 10 15 20 2 с 3035 блоков элементов И для связи группвычислительных блоков между собой,Поставленная цель достигается эа счетизменения структуры каждого из вычислительных блоков, входящих в составвычислительного преобразователя информации, направленного на то, чтобыкаждый вычислительный блок реализовал операции над скобочными формами,а также введением дополнительных шинсинхронизации, кодовых шин и шинуправления. 3 ил2 (логическая единица на выходах элементов ИЛИ 19,20 соответствует знаку"+", логический нуль - знаку - ). 5Любой 1-й вычислительный блок содержит также первый и второй согласующие элементы 21 и 22 (усилитель 21 является повторителем сигнала, поступающего на его вход из ПКН 1 и 2, а уси литель 22 инвертирует знак сигнала, поступающего на его вход из ПКН 1 и 2), второй и четвертый ПКН 23 и 24, выходы которых объединены; второй и четвертый регистры 25 и 26; узел 27 15 выбора знакового разряда большего по абсолютному значению числа из регистров 25 и 26, включающий в себя цифровой компаратор 28 с двумя выходами 29 и 30 (на первом выходе 29 появля ется сигнал тогда, когда число из регистра 25 больше или равно числу из регистра 26, на втором выходе 30 - сигнал тогда, когда число из регистра 26 больше числа из регистра 25), пер вый элемент И 31, на первом выходе 32 которого появляется сигнал в том случае, когда числа из регистров 25 и 26 имеют равные знаки, а на втором выходе 33 в такой ситуации - сигнал, 30 эквивалентный значению знакового разряда чисел иэ регистров 25 и 26, второй элемент И 34, входы которого подсоединены к вьжоду 30 цифрового компаратора 28 и к выходу знакового раз ряда регистра 26, третий элемент И 35, входы которого подсоединены к выходу 29 цифрового компаратора 28 и выходу знакового разряда регистра 25, элемент ИЛИ 36, входы которого подк лючены к выходам элементов И 31,34, 35, а его выход - к входу сумматора 15 по модулю два, второй шифратор 37 для коммутации знаковых разрядов ПКН 23 и 24 содержащий первый элемент 45 И 38, входы которого подсоединены к выходу 16 сумматора 15 по модулю два и к выходу 29 цифрового компаратора 28, второй элемент И 39, входы которого подключены к выходу 16 сумматора 50 15 по модулю два и к выходу 32 элемента И 31, третий элемент И 40, входы которого подключены к второму выходу 17 сумматора 15 по модулю два, к выходу 30 цифрового компаратора 28 и к выходу инвертора 41, вход которого подсоединен к выходу 32 элемента И 31, первый элемент ИЛИ 42, входы которого подсоединены к выходам элементов И 38-40, а его выход подключен к входу знакового разряда ПКН 23, четвертый элемент И 43, входы которого подключены к выходу 16 сумматора 15 по модулю два и к выходу 30 цифрового компаратора 28, пятый элемент И 44, входы которого подключены к выходу 16 сумматора 15 по модулю два и выходу 32 элемента И 31, шестой элемент И 45, входы которого подключены к вьжоду 29 цифрового компаратора 28, к выходу инвертора 41 и к выходу 17 сумматора 15 по модулю два, второй элемент ИЛИ 46, входы которого подсоединены к выходам элементов И 43-45, а его выход - к входу знакового разряда ПКН 24.Преобразователь информации включает в себя также первый, второй, третий, четвертый и пятый блоки элементов И соответственно 47 - 51, кодоуправляемый сумматор 52, ПНК 53, шесть информационных входов 54-59, четыре входа 60-63 синхронизации, три входа 64-66 задания режимов работы. Вход 67 кодоуправляемого сумматора 52 является входом задания шага квантования ВПИ. Первые регистры соседних ВБ связаны между собой шинами 68, вторые регистры - шинами 69, третьи регистры - шинами 70 и четвертые регистры - шинами 71.Взаимодействие блоков и обработка информации в преобразователе информации осуществляется следующим образом.Подлежащая обработке цифровая информация в виде ш-разрядньж чисел М Мз, Б и И параллельно поступает на третий и четвертый информационные входы 56 и 57 преобразователя информации, являющиеся одновременно вторыми входами первых, вторых, третьих и четвертый регистров 3,25,4 и 26 всех 2 п вычислительных блоков, либо - последовательно на первый, второй, пятый и шестой входы 54 - 59 преобразователя информации, являющиеся первыми входами регистров 3,25,4 и 26 первого вычислительного блока.При последовательном занесении информации возможно независимое перемещение информации вдоль регистров 3,25, 4 и 26 всех вычислительных блоков эа счет того, что выходы первых, вторых, третьих и четвертых регистров 3,25, 4 и 26 1-го вычислительного блока соединены с первыми входами первых 3, соответственно вторых 25, третьих 4.(р(4 / к /е являетс аналоговым выходоинформации,которо преобр зователя лючен к торого ный цифро- У кото(4) ,((12 г Цаык 1 В 2 и четвертых 26 регистров (1+1)-го ВБ.Занесение, а также независимое перемещение чисел Н И , И и И вдольвсех вычислительных блоков 2 п возможно только при подаче синхроимпульсов 5(сдвига), которые соответственно соединены с первыми 3, вторыми 25, третьими 4 и четвертыми 26 регистрамивсех ВБ. В каждом д-м вычислительном блоке информация обрабатывается следующим образом.В первый 3, второй 25, третий 4 15 и четвертый 26 регистры заносятся соответственно числа Н Нз, Х 2, М 4 имеющие знаковые разряды. Регистры 3,4, 25 и 26 своими выходами соответственно подключены к цифровым входам 20 ПКН 1,2,23 и 24. Полярность напряжения на выходе ПКН 23 и 24 соответствует результирующему знаку перемножаемых Ско ок (М 1 +12 2) в 7 /4 4 к где К о/.2, о/.в, с/.4 - знаковые разряды. Полярность напряжения на выходе ПКН 23 и 24 определяется выходными сигналами узла 5 выбора знакового разряда большего по абсолютному значению числа из регистров 3 и 4, шифратора 30 18, сумматора 15 по модулю двр, согласующих элементов 21 и 22, выходы которых соответственно подключены к первым и вторым аналоговым (умножающим) входам положительного и отрица тельного напряжений ПКН 23 и 24, узла 27 выбора знакового разряда большего по абсолютному значению числа из регистоов 25 и 26, шифратор 37. При этом на выходах узлов 5 появляются цифровые сигналы г для которыхесли о/. = о/. г. = Ос., если О/.фм.и (1,(-(Н 21( (1)О/1 к ЕСЛИ В/1, к 2( И ( Н//( 1,/к У в/3 ь если вф 4 и /Нв// /111/ (2) на выходе сумматора 15 по модулю два - цифровые сигналы г , г;, для которых г, =г,у; г,=г; Яу,; (3) на выходах шифратора 18 коммутации знаковых разрядов ПКН 1 и 2 - сигналы /3 и (321, для которых551, если /И//И 21/ ИМ,ФМ 2(-1, если.ы.2; и /11 / / М 2 2 6ЕСЛИ 0(; ф В 2 И /И /с / к 42; (- 1, если (М/ ( М 2; / и в, а на объединенных выходах ПКН 1 и 2 формируется напряжение0=К( Р Н/1 + Р 21 121 ) к где К=У /2 - коэффициент преобраЮ+4зования, на выходе шифратора 37 коммутации знаковых разрядов ПКН 23 и 24 формируются два сигнала ; и ;, для ко- торых 1есливьв, = 04 И г- 11ЕСЛИ ( М 1(-(Н 41( к В(31 В 41 ф1если (Нв,(с(К 4,вв, ФЫ 4,к1 ЕСЛИ / Я 31(с ( Н 41( ФВ(ф 31-1, если в( = Ы 4 и г; =О,1, если в/.к, = в/4 и г, =11, если (М(Я 4;/, Ф, 114; г=1 -1, если (Яв 1( (И 4,(;ов; Фв/ г; 1 (8) -1, если о/ в(,4 и г; О, а на объединенных выходах преобразователей ПКН 23 и 24 формируется нап- ряжение ц=к (/, /к/+, /к/1( /к/ +(9) Своими выходами все вычислительные блоки гальванически соединены в одну точку А, в которой формируется напряжение 0, равное2цщк, /2 п, 3,/м+ 4 /Н 4(где 2 п - число блоков.Из точки А сигнал подается на аналоговый вход кодоуправляемого сумматора 52, масштаб которого может изменяться путем задания чисел Я и Н на его цифровом входе так, что на его выходе (1) формируется напряжение, равное Выход сумматора 52 под входу ПНК 53, на выходе к (выход ) образуется двои вой эквивалент напряжения рый равенгде К=1/ /2 - масштаб преобразования0преобразователя 53;1 - разрядность преобразователя 53.Подставляя в выражение (12) вместо Пего значение, полученное из формулы (11), после преобразований получим соотношение Рвг=2 741 /114 / Информацияс ПКН 53 при наличии раз 2 нИ 6 2 (х, +А; ) (у;+В; ) л 1 45 4) г /2 п;-г где К х;,А;,у ,В, - соответственно цифровые отсчеты первой, второй, третьей и четвертой функции.В случае обработки информации в реальном масштабе времени соотношение (14) для момента с записывается в виде(15) решающего сигнала на входе 65 задания режимов работы через блок элементов15 И 49 поступает на третий вход первого регистра 3 (и+1)-го вычислительного блока, Все 2 п блоков разделены на две секции: от 1 до и-го и от (и+1)- го до 2 п-го блока. Секции при наличии разрешающих сигналов на первых 64 и на третьих 66 входах задания режимов работы соединяются между собой через блоки элементов И 47 48 50 51,25Вычисления в предлагаемом преобразователе информации осуществляется на базе следующих элементарных операций.1. Операция сложения первой и второй, третьей и четвертой Функции и умножения полученных сумм Функций, 30 отсчеты которых записаны соответственно в регистры 3,4,25 и 26 вычислительных блоков, При этом отсчеты функций могут быть занесены либо параллельно за один такт во все регистры по входам 54 и 57, либо последовательно за 2 п тактов по входам 54, 58,55,59.После полного занесения информации во все регистры 3,4,25 и 26 на цифро вом выходе преобразователя информации появится число г, величина которого определяется выражением" 2, Операция занесения информации по синхроимпульсу в момент 1 на первый регистр 3 первого ВБ через вход 54 с одновременной передачей (сдвигом) информации с первого регистра 3 (1-1)-го ВБ на первый регистр 3 1-го ВБ. Условимся эту операцию обозначить -х, =х , если =1х; =х . , если д 1, где х; - код, поступающий на вход 54 ВПИ и на первый вход первого регистра 3 первого ВБ в момент(стрелка над числом х; обозначает сдвиг на первых регистрах 3 этого числа по синхроимпульсу).При выполнении такой операции преобразователь информации осуществляет преобразование информации для момента в соответствии с соотношениемг г =(х, +А. ) (у; +В; ) . (17)5,С 113 . Операция занесения информа ции А либо у , , либо В , по с и их роимпул ь с у в момент 1 соответственно н а третий регистр 4 или второй регистр 2 9 , или четвертый регистр 2 6 первого В Б соо тв е т с т в е н но через вход 5 8 или 5 5 , или 5 9 с одновременной передачей ( сд вигом ) информации соответственно с тр еть е го регистра 4 (- 1 ) - го В Б н а тр етий регистр 4- го В Б или с второгорегистра 2 5 ( д - 1 ) - го В Б н а второй регистр 2 5 д - г о В Б , или с четвертого регистра 2 6 ( д - 1 ) - го В Б на четвертый регистр 2 6 1- го В Б ,Условимся эту операцию обозначатьФ К,=К, если 1=1; К =К;.,если 11;А;, если используется вход 58 где К. = у, , если используется вход 55В;, если используется вход 59К - код, поступающий на вход 58 или 55, или 59 соответственно на вход третьего регистра 4 или второго регистра 25, или четвертого регистра 26 первого ВБ (Ке А,у,В 3), Стрелка над числом Кобозначает сдвиг наФ регистрах 4 или регистрах 25, или регистрах 26 этого числа по синхроимпульсу,При выполнении этой операции преобразователь информации осуществляет для момента й преобразование информации в соответствии с одним иэ выражений:информация поступает по входу 581 1 ь, пг =- --- , (х; +А а) (у +Вс)(19)5,Ф с 1информация по с т уп а ет по в ходу 5 555 бь 2 нгс М ", (х, +А, ) (у+В, ); (20)5,1информация поступает по входу 593 61 1г =- ---(х, +А) (у +В )(21) 10+ 1 "фт 1информация одновременно поступает по входам 58,55,59ь,+г =- ---(х. +А. ) (у +В ) . (22)И ., , 1, 1,сС учетом первой элементарной операции возможны и другие комбинации перемещения информации вдоль первых 3, третьих 4, вторых 25 и четвертых 26 регистров. 20Число возможных комбинаций перемещения информации вдоль регистров соответствует, 15 (четыре для случая, когда информация перемещается вдоль 25 одной одноименной группы регистров;шесть для случая, когда информация перемещается вдоль двух одноименных групп регистров; четыре для случая, когда информация перемещается вдоль 30 трех одноименных групп регистров,одна для случая, когда информация перемещается вдоль четырех одноименных групп регистров).4. Операция занесения информации х либо А, либо у, Либо по синхроимпульсу в момент 1.соответственно на первый 3 либо на третий 4, либо на второй 25, либо на четвертый 26 д 0 регистры первого ВБ соответственно либо по входу 55, либо по входу 58, либо по входу 54, либо пс входу 59 и занесение информации г по синхроимпульсу в момент С по третьему входу 5 в первый регистр 3 (и+1)-го ВБ с одновременным сдвигом информации с первого регистра 3 либо третьего регистра 4, либо второго регистра 25, либо четвертого регистра 26 (-1)-го ВБ соответственно в регистр 3 либо в регистр 4, либо в регистр 25, либов регистр 26-го ВБ (=1,2Ч; п, Ч=2 п) и сдвигом информации с первого регистра 3 (3-1)-го ВБ в первый регистр 3 3-го ВБ (3=(п+1), (и+2), (и+23)(2 п.Условно эту операцию обозначим так:+ , (х +А + ) (у +В), (24)где хРьех ; к,; А ЕА, АД;А-А, А у,еу , у;уеу , у; ВрфВР 1 Вр5 Г 1 Вф В 1,Условная запись, к примеру,о - ф 3 ох е 1 хр, х, означает, что х,может принимать значение хР, либо1Узначение х ,Соотношение (24) описывает достаточно большое множество различныхпреобразований информации, расположенной в преобразователе информации,время выполнения всех элементарныхопераций равно периоду следованиясинхроимпульсов по входам 60-63 синхронизации. Информация с выхода блокаэлементов И 49 поступает только приреализации элементарной операции (23). Выполнение рассмотренных выше элементарных операций, на базе которых обуществляется преобразование информации, расположенной в регистрах преобразователя информации, в виде преобразований (15), (17), (19)-(22), (24) обеспечивается в зависимости от различных комбинаций сигналов на инФормационных входах 54-59, входах 64-65 задания режимов работы и входах 60-63 синхронизации реализации в натуральном масштабе времени операций алгебраического сложения, умножения и деления двух чисел, интегрирования, дифференцирования, вычисления корреляционной Функции центрированного эргодического случайного процесса, прямого преобразования Фурье, операции Фильтрации в соответствии с адгоритмами работы нерекурсивного где М, - код, поступаемый в момент С на вход 54 или 58, или 55, или 59 соответственно на вход первого 3 или третьего 4, или второго 25, или четвертого 26 регистров первого ВБ (Ме х, А, у, В 3) .При выполнении этой операции преобразователь информации осуществляет разнообразные преобразования информации, заданные соотношениями:1015 55 или рекурсивного цифрового фильтра,а также реализация операций над скобочными формами, таких как умножениечисла на скобку, умножение скобок,интегрирование, дифференцированиесуммы и разности двух функций, операции корреляционного и дисперсионногоанализа нецентрированных случайныхвеличин и процессов,Формула изобретенияВычислительнь преобразователь информации, содержащий первы, второй и третий блоки элементов И, преобразователь напряжение - код, кодо- управляемый сумматор и 2 п вычислительных блоков, каждый из которых содержит первый и второй входные регистры, первый и второй преобразователи код - напряжение, первый согласующий элемент и сумматор по модулю два, информационный вход первого преобразователя код - напряжение соединен с информационным выходом первого входного регистра, а его выход подключен через первый согласующий элемент к первому аналоговому входу второго преобразователя код - напряжение, цифровой вход которого подключен к информационному выходу второго входного регистра, выходы вторых преобразователей код - напряжение всех вычислительных блоков соединены между собой и подключены к аналоговому входу кодоуправляемого сумматора, цифровой вход которого является входом задания шага квантования вычислительного преобразователя, а выход подключен. ко входу преобразователя напряжение - код и является аналоговым выходом вычислительного преобразователя, причем 2 п вычислительных блоков разделены на две группы по и вычислительных блоков в каждой группе, информационные выходы первых и вторых регистров .-го вычислительного блока в каждой группе соединены с первыми информационными входами соответственно первого и второго входных регистров (.+1)-го вычислительного блока, первые информацион,ные входы первого и второго входных регистров первого вычислительного блока являются первым и вторым информационными входами вычислительного преобразователя, вторые информаци-. онные входы соответственно первых и вторых входных регистров всех вы 20 25 30 35 40 45 50,числительных блоков объединены и являются соответственно третьим и четвертым информационными входами вычислительного преобразователя, входысинхронизации первых и вторых входныхрегистров соответственно объединеныи является соответственно первым ивторым входами синхронизации вычислительного преобразователя, первые входы первого и второго блоков элементовИ объединены и являются первым входомзадания режима работы вычислительногопреобразователя, их вторые входы соединены с информационными выходамисоответственно первого и второго входных регистров и-го вычислительногоблока, а выходы подключены к первыминформационным входам соответственно первого и второго входных регистров(п+1) - го вычислительного блока, одиниз входов третьего блока элементов Иявляется вторым входом задания режимаработы вычислительного преобразователя, а его другой вход и выход подключены соответственно к выходу преобразователя напряжение - код и ктретьему информационному входу первовходного регистра (и+1)-го вычислительного блока, выход преобразователянапряжение - код является цифровымвыходом вычислительного преобразователя, о т л и ч а ю щ и й с я тем,что, с целью расширения функциональных возможностей за счет реализацииалгебраических, дифференциальных иинтегральных преобразований суммы иразности таблично заданных функцийи операции дисперсионного и корреляционного анализа, он содержит четвертый и пятый блоки элементов И и вкаждом вычислительном блоке третийи четверты входные регистры, третийи четвертый преобразователи код - напряжение, второй согласующий элемент,первый и второй шифраторы и первый ивторой узлы выбора знаковых разрядовбольших по абсолютному значению чиселво входных регистрах, каждьп из которых выполнен в виде цифрового компаратора, первого, второго и третьегоэлементов И и элемента ИЛИ, три входакоторого подключены соответственно к одному из выходов первого элементаИ и к выходам второго и третьего элементов И, другие выходы первых элементов И первого и второго узлов выбора знаковых разрядов больших по абсолютному значению чисел во входныхрегистрах соединены с первыми входами соответственно первого и второго шифраторов, первые входы первого и второго и первый вход третьего элементов И первого узла выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах подключены к выходам знаковых разрядов соответственно третьего и первого входных регистров соответствующего вычислительного блока, первые входы первого и второго и первый вход третьего элементов И второго узла выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах - к выходам знаковых разрядов соответственно четвертого и второго входных регистров соответствующего вычислительного блока, первый вход третьего и второй вход первого элементов И в каждом узле выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах объединены, а вторые входы третьих и вторых элементов И подключены в каждом из этих узлов соответственно к первому и второму выходам цифровых компараторов, входы цифровых компараторов первого и второго узлов выбора знаковых разрядов больших по абсолютному значению чисел во входных регистрах в каждом вычислительном блоке подключены к информационным выходам соответственно первого и третьего и второго и четвертого входных регистров этих блоков, а их выходы соединены соответственно со вя орыми и третьими входами соответствующих шифраторов, информационные входы третьего и четвертого преобразователей код - напряжение подключены к информационным выходам соответственно третьего и четвертого входных регистров, два выхода первого шифратора подключены в каждом вычЯслнтельном блоке к входам знаковых разрядов соответственно первого и третьего преобразователей код - напряжение, выходы которых объединены и подключены через первый и второй согласукщие элементы соответственно к первому аналоговому входу четвертого и к вторым аналоговым входам второго и четвертого преобразователей код - напряжение, выходы которых объединены, четвертый и пятый входы второго шифратора подключены соответственно к первому и второму выходам сумматора по модулю два, а два его выхода - к входам знаковыхразрядов соответственно второго и четвертого преобразователей код - напряжение, первые входы четвертого и пятого блоков элементов И объединены и являются третьим входом задания режима работы вычислительного преоб разователя, их вторые входы соединеныс информационными выходами соответственно третьего и четвертого входных регистров и-го вычислительного блока, а выходы подключены к первым информационным вхОдам соответственно третьего и четвертого входяых регистров (п+1)-го вычислительного блока, первые информационные входы третьего и четвертого входных регистров первого вычислительного блока являются соответственно пятым и шестым информационными входами вычислительного преобразователя, входы синхронизации третьих и четвертых входных регистров аосоответственно объединены и являются соответственно третьим и четвертым входами синхронизации вычислительного преобразователя.

СмотретьЗаявка

3934281, 12.07.1985

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ АВИАЦИОННОЕ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ИМ. ЛЕНИНСКОГО КОМСОМОЛА УКРАИНЫ

АЛИПОВ НИКОЛАЙ ВАСИЛЬЕВИЧ, ГРИГОРЬЕВ АЛЕКСАНДР ВИКТОРОВИЧ, ТИМЧЕНКО АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G06J 1/00

Метки: вычислительный, информации

Опубликовано: 15.08.1987

Код ссылки

<a href="https://patents.su/10-1330642-vychislitelnyjj-preobrazovatel-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительный преобразователь информации</a>

Предыдущий патент: Устройство для моделирования электрической машины постоянного тока

Следующий патент: Устройство для распознавания формы сигнала

Случайный патент: Пыленепроницаемая камера для нанесения покрытий