Устройство для контроля микропроцессорной системы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1566332

Автор: Комаров

Текст

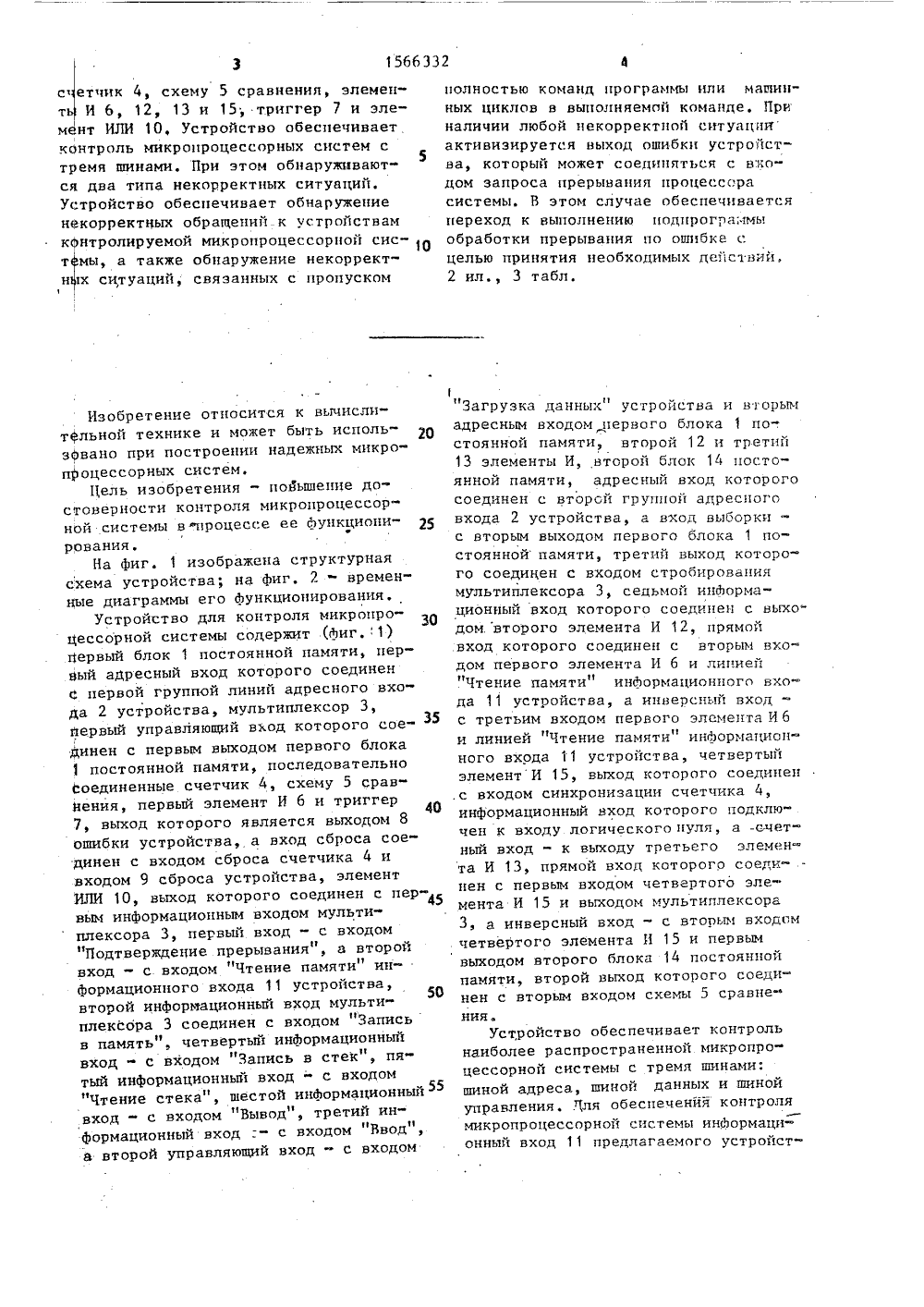

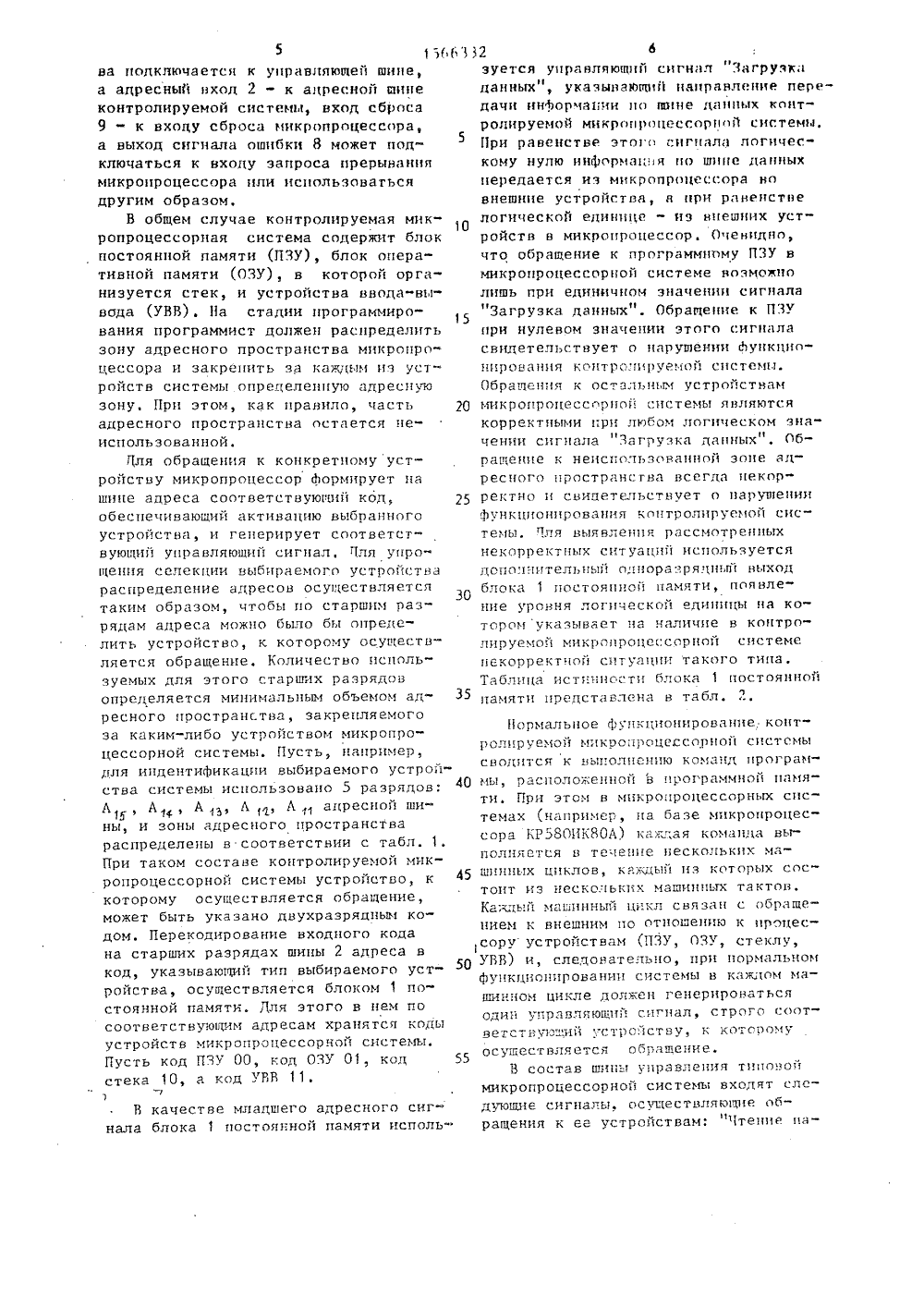

СВОЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХ1 ЕСПУБЛИН 28 1)5 С 06 Н АВТОРОМ Р 19гонньгйг хцоло о сссР1985, СССР1987. тельг Р 11/ льс.т в 0 ГОСУДАРСТВЕННЫЙ НОУИТЕТпо иасвретения 1 и отнытип 1 и гннт сссР(71) Рыбинский авиагический институт(5) 1 гяобретецне относится к ицгисл:гтельцой технике и может быть исггользовагго при ггостроегиги надежных.г:гкрог.родессорггьгх систем, Целью ивобретенця является гговыгпение достоверное:и кс:гтроля и:гкроцродессорцой сист - ггьг в прогГессе мункегггоггггроваггил,Устройство содергдгт блокгг 1, 14 постоянной памяти, гу:гьтгггглексор 3,1566332 с етчик 4, схему 5 сравнения, элемецть И 6, 12, 13 и 15; триггер 7 и элемент ИЛИ 10, Устройство обеспечивает кОнтроль микропроцессорных систем с тремя шинами. При этом обцаружнвают 5 ся два типа некорректных ситуаций.Устройство обеспечивает обнаружение нВкорректцых обращений к устройствам контролируемой микропроцессорной сис О тмы, а также обнаружение некорректных ситуаций, связанных с пропуском 1 Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем.Пель изобретения - повышение достоверности контроля микропроцессорной системы в "процессе ее Функциоци рования.На Фиг. 1 изображена структурная схема устройства; на фиг, 2 - временные диаграммы его Функционирования.Устройство для контроля микропроцессорной системы содержит (Фиг.1) первый блок 1 постоянной памяти, первый адресный вход которого соединен С первой группой линий адресного входа 2 устройства, мультиплексор 3, первый управляющий вход которого сое 35 динен с первым выходом первого блока 1 постоянной памяти, последовательно соединенные счетчик 4, схему 5 сравнения, первый элемент И 6 и триггер 7, выход которого является выходом 8 ошибки устройства, а вход сброса соединен с входом сброса счетчика 4 и входом 9 сброса устройства, элемент ИЛИ 10, выход которого соединен с первым информационным входом мультиплексора 3, первый вход - с входом "Подтверждение прерывания", а второйт 1 ц вход - с входом Чтение памяти инФормационного входа 11 устройства, второй инфориационньп вход мультиц плексора 3 соединен с входом Запись в память", четвертьп информационный11 1 вход - с входом Запись в стек , пятый информационньп вход - с входом-55 "Чтение стека", шестой информационныи вход - с входом "Вывод", третий инц Формационный вход :- с входом Ввод", а второй управляющий вход - с входом полностью команд программы или машинных циклов в выполняемой команде, Приналичии любой некорректной ситуацикактивизируется выход ошибки устройства, который может соединяться с входом запроса прерывания процессс,расистемы. В этом случае обеспечиваетсяпереход к выполнению подпрограммыобработки прерывания по ошибке с.целью принятия необходимых действии,2 ил., 3 табл. цЗагрузка данных устройства и вторымадресным входом первого блока 1 по-.стоянной памяти, второй 12 и третий13 элементы И, второй блок 14 постоянной памяти, адресный вход которогосоединен с второй группой адресноговхода 2 устройства, а вход выборкис вторым выходом первого блока 1 постояннойпамяти, третий выход которого соединен с входом стробировапиямультиплексора 3, седьмой ицсяормационный вход которого соединен с ныхо"дом.второго элемента И 12, прямойвход которого соединен с вторым входом первого элемента И б и линией"Чтение памяти" информационного входа 11 устройства, а инверсный вход -с третьим входом первого элемента И 6и линией "Чтение памяти" информационного входа 11 устройства, четвертый элемент И 15, выход которого соединен .с входом синхронизации счетчика 4, информационный вход которого подключен к входу логического нуля, а -счетный вход - к выходу третьего элемента И 13, прямой вход которого соединен с первым входом четвертого эле" мента И 15 и выходом мультиплексора 3, а инверсный вход - с вторым входом четвертого элемента И 15 и первым выходом второго блока 14 постоянной памяти, второй выход которого соединен с вторым входом схемы 5 сравне ния.Устройство обеспечивает контроль наиболее распространенной микропроцессорной системы с тремя шинами: шиной адреса, шиной данных и шиной управления, Чля обеспечения контролямикропроцессорной системы информационный вход 11 предлагаемого устройст13 32 6 Нормальное функционирование контролируемой м;ткроцроце,ссорцой системыСВОДИТСЯ К тэЫ 11 ОЛЦЕ 11 ИЮ КОМаНД ЦРОГРаМ мы, расположеццоц н программной ттамяти. При этом в микропроцессорных системах (например, ца базе микропроцессора ЕР 58 ОИЕЯОА) ттаг",ая команда выполняется н тетепле нескольких ма 5 ш 1111 цьх цикловкаждый из которых состоит из нескольких машинных тактов.Ка;1 дьтй машинный ццкт связан с обращением к внешним по отношению к цротдессору устройствам (ПЗУ ОЗУ, стеклу, 50 УВВ) и, следовательно, тдри нормальномфункционировании системы в кажчом мапптнцом цикле должен генерироватьсяодин управляющий сигнал, строго соотнетстн иптий ;стрсйтстну к которОтуосуществляется обгашение.В состав шинн управления типовоймикропроцессорной системь входят следующие сигналы, осуществляющие обращения к ее устройствам: "Чтение ца 5 151ва подключается к управляющей шине,а адресный вход 2 - к адресной шинеконтролируемой системы, вход сброса9 - к входу сброса микропроцессора,а выход сигнала ошибки 8 может подключаться к входу запроса прерываниямикропроцессора или использоватьсядругим образом.В общем случае контролируемая микропроцессорная система содержит блокпостоянной памяти (ПЗУ), блок оперативной памяти (ОЗУ), в которой организуется стек, и устроцстна ннода-вывода (УВВ), На стадии программирования программист должен распределитьзону адресного пространства микропроцессора и закреттить за каждым из устройств системы определенную адреснуюзону. При этом, как правило, частьадресного пространства остается цеиспользованной.Пля обращения к конкретномуустроцстну микроттроцессор формирует цашине адреса соответствующий код,обеспечивающий активацию выбранногоустройства, и генерирует соответствующий управляющий сигцал, т 1 ля упрощения селекции выбираемого устротц тнараспределение адресов осуществляетсятаким образом, чтобы по старшим разрядам адреса можно было бы оттределить устройство, к которому осуществляется обращение. Еоличестно используемых для этого старших разрядонопределяется минимальным объемом адресного ттространстдэа, закрепляемогоза каким-либо устройством микропроцессорной системы. Пусть, например,для ицдентификации выбираемого устройства системы использовано 5 разрядов:А, Ат, А 1, А 1, А тэ адресной ши 1ны, и зоны адресного пространствараспределены н соответствии с табл. 1,При таком составе контролируемой микропроцессорной системы устройство, ккоторому осуществляется обращение,может быть указано двухразрядцым кодом. Перекодирование входного кодана старших разрядах шины 2 адреса вкод, указывающий тип ныбираемого устройства, осуществляется блоком 1 постоянной памяти. Для этого в нем посоответствующим адресам хранятся кодыустройств микропроцессорной систеьтьт.Пусть код ПЗУ 00, код ОЗУ 01, кодстека 10, а код УРВ 11,В качестве младптего адресного сигнала блока 1 постоянной памяти исполь 5 10 15 20 25 30 35 зуется управляющий сигнал "тагрузк;дданных", указыдэаюпптт 1 направленце переДаЧИ ИНттОРтатн тттт ППтЦЕ ДаЦЦЬтХ КОЦтролируемой микропроцессорной системы.При равенстве этогт сигнал логическому нулю ннформац:я цо шине даццыхпередается из микропроцессора новнешние устройства, а ири равенствелогической единице - из внешних устройств н микропроцессор. Очевидно,что обращение к программному ПЗУ вмикроцроцессорной системе возможнолишь при единичном значении сигналаЗагрузка данных". Обращение к ПЗУпрн нулевом значении этого сигналасвттдетельстнует о нарушении Ьуттктдттоциронацття котттрс.тттруеттой системы.Обращения к осталдным устройствамМИКРОттРО 11 ЕССоРттОтт СЦСТЕМЫ ЛНЛЯЮтСЯкорректными при любом логическом значении сигцала "Вагтдузка данных", Обращение к неттсттолтзс наццой зоне атдресного цространт гна всегда некорректно ц свидетельствует о нарушениифункццоццровация контролируемой сцстемьт, Чля выявления рассмотренныхнекорректных ситуаций используетсядоно.тттителд,цый одцоразрядцьпт выходбчока 1 постоянной памяти, появление уровня логической единицы ца которомуказывает ца наличие н коцтролируемоц микропроцессорной системенекорректной ситуации такого типа.Таблица истт:тттэости блока 1 постояннойпамяти представлена н табл. 2, 15 б 6332 8"Вывод", "Чтение стекаЗапись в стек", "Подтверждение прерывания". Для обращения к. внешним устройствам5 все эти сигналы стробируются соответствующими строб-сигналами микропроцессора "Прием" или "Выдача". Кроме этих сигналов в состав шины управления входят сигналы "Чтение первого байта команды" (М 1) и "Загрузка дан ных", которые используются в нестробируемом виде.Нарушение соответствия между тином устройства, к которому осуществляется обращение по шине адреса, и активным управляющим сигналом в шине управления является некорректной ситуацией, Очевидно, что непоявление ожидаемого управляющего сигнала при обращении и некоторому устройству системы также является нарушением процесса нормального фубкционирования контролируемой системы. Для обнаружения некорректных ситуаций в конт ролируемой системе необходимо прежде всего сопоставить тип устройства, к которому осуществляется обращение в текущий момент времени, с типом управляющего сигнала в момент обращения и зафиксировать факт его активирования, Это осуществляется мультиплексором 3 и счетчиком 4 и реализуется следующим образом. Тип выбранного устройства одно 35 значно определяется кодом с первого выхода блока 1 постоянной памяти, Разряды этого кода поступают на управляющий вход мультиплексора 3. На один40 из управляющих входов мультиплексора 3 поступает сигнал "Загрузка данных" с шины управления, указывающий направление передачи информации по шине данных контролируемой системы. Напри 45 мер, в микропроцессорной системе на базе микропроцессора КР 580 ИК 80 Л в качестве сигнала Загрузка данных" целесообразно использовать управляющий сигнал "Запись-вывод . Использование этого сигнала позволяет отличить обращения к одному и тому же устройству контролируемой системы (например, ОЗУ, стеку, УВВ) для чтения и записи информации. Таким образом, код, поступающий на управляющий вход мульти плексора 3, обеспечивает выбор его соответствующего информационного вхо" дачто осуществляет настройку этого мультиплексора на прием соответствующего управляющего сигнала, используемого для обращения к внешним устройствам.Соответствие устройств с учетом принятого кодирования (табл. 2) и управляющих сигналов в контролируемой системе приведено в табл, 3.Настройка мультиплексора 3 обеспечивает то, что ожидаемый управляющий сигнал в момент обращения к некоторому устройству контролируемой системы всегда появляется на выбранном информационном входе мультиплексора 3 и проходит на его выход, В случае нарушения соответствия между типом устройства и управляющим сигналом активный уровень появляется на невыбранном информационном входе мультиплексора 3, и сигнал на его выходе не формируется. В случае, если при обращении к устройству контролируемой системы ожидаемый управляющий сигнаЛ не появляется, то выход мультиплексора 3 также не активируется. В случае обращения к неиспользуемой зоне адресного пространства активируется третий выход блока 1 постоянной памяти (табл. 2), запирающий мультиплексор 3 по входу стробирования. При этом какой бы управляющий сигнал не появился на информационных входах мультиплексора 3, он не пройдет на его выход. Отсюда следует, что при корректном выполнении текущего машинного цикла обращения к какому-либо устройству контролируемой системы, на выходе мультиплексора 3 всегда формируется активный сигнал, а при некорректном выполнении сигнал на выходе мультиплексора 3 не формируется.При этом факт появления сигнала на выходе мультиплексора 3 всегда фиксируется в счетчике 4 путем изменения его состояния. Суммирование входных сигналов в счетчике 4 осуще- . ствляется по какому-либо модулю (например, модулю 256), что определяется разрядностью этого счетчика. При некорректных обращениях к контролируемой системе состояние счетчика 4 не изменяется. Отсюда следует, что состояние счетчика 4 постоянно отражает предысторию процесса Функционирования контролируемой сисгемы по обращению к ее устройствам в течение длительного интервала времени. Оче 15 гт 6 3 32О О15 20 25 ЭД 40 видно, что чем больше разрядность этого счетчика, т.е, больше модуль суммирования входйых сигналов, темболее глубокая предыстория процесса накапливается в нем.Для обеспечения контроля в предлагаемом устроцстве каждой командепрограммы, исполняемой контролируемой системой, ставится в соответствиенекоторое ко 1 трольное число, Это числвычисляется заранее как сумма но тому же модулю, что и реализуемый счетчиком 4, количества машинцых циклов всех команд, нредшествуюгих данной команде. Контрольные числа еге до работы устройства размещаются в блоке14 постоянной памяти. Выход этого блока активируется сигналом выборки с выхода блока 1 постоянной памяти лишь в моменты обращения к программнолу ПЗУ (табл. 1). При этом адресный вход блока 14 постоянной памяти подключен к тем же младыим разрядам шины адреса контролируемой системы, что и программное ПЗУ, ц адресуется синхронно с цим. Контрольные числа записываются в ячейки блока14 постоянной памяти по адресам, цо которьм в программном ПЗУ расположены первые байты команд.В процессе функционирования контролируемой системы контрольые чсла извлекаются из блока 14 постоянной памяти и сравниваются с состоягнем счетчика 4, Если результат суммировация совпадает с контрольным числом, то делается вывод О нормальном функционировании контролируемой системы. В противном случае фиксируетсл нарушение нормального функционирования системы, Сигнал, свидетельствующий о состоянии процесса Функционирования контролируемой системы формируется на выходе с.хемы 5 сравнения и оценивается в машин;ых циклах чтения первого байта команды из программного ПЗУ. Это обеспечивается стробированием выходного сигнала схемы 5 сравнения сигналами "Чтение первого байта команды" (М 1) и "Чтение памяти" с помощью элемента И 6.Рассмотрим работу предлагаемого устройства на некотором шаге функционирования контролируемой сиатемы (фиг. 2). Пусть в результате исполнения предыдущих шагов в счетчике 4 цай копилось некоторое число, поступаю. щее на один вход схемы 5 сравнения. В процессе реализации текущего шага на адресный вход 2 поступает адресустройства вкропроцессорцой системы,к которому будет осущееевляться обрашецце в текущем машинном цикле, Постаршим разрядам кода адреса выбирается информационццй вход мультиплексора3, соответсгвующий Ожидаемому управляющему сигналу. При появлении этогосигнала он проходит через открытыйв этот момент элемент И 13 ца счетный. вход счетчика 4, увеличивая поспаду его состояние на единицу, Одновременно пе младшим разрядам кодаадрсса из блока 14 постоянной памятиизвлекается какое-то число, посту-пающее ца другой вход схемы сравнения.Если гекуг 111 1 а 11111 ии цикл це является циклом выборки первого байта коман-,ды, то это число может быть произвольцьг, В этом случае схема 5 сравнения обнаружвает неравенство чиселца ее входах и формирует ца выходеедицицныц логический уровень. Однаков этот момент Опибка не оценивается(конъюнкция сигналов М 1 и "Чтение.памяти" равна нулю, и элемент И 6закрыт), что предотвращает фиксациюложной ошибки в триггере 7., Лцалогц"цым Образо. устройство функционируетво всех 1 ашццых циклах, це являющихся мапияшин циклами выборки перВОГО б 111 та кс 111 дн, Прц этом црц Обрагеццц к ОЗУ цд гение Осуществляется доцолц.тельгый контроль ца Отсутствие сигнала Ч 1, так как чтениеинг 1)орм 11111 и из ЙЗ. в Озможно лишь цринулевом зцачеццц этого сигнала. ЭтоОбеспечивается тем, что лишь прцМ 1 = 0 элемент П 12 открыт и сигнал ."Чтение памяти" проходит на выходмультиплексора 3, фиксируясь в счетчике 4,В машицц 1 х циклах выборки первого байта команды мультиплексор 3 также настраивается ца прием ожидаемого уцравляющего сигала Чтение памятии ц (или Подтвеожде 1:е прерывания"), Однако цз блока 14 постоянной памятив этот момент времени извлекается вполне определенное контрольное число, Если это контрольное число совпад;1- ет" с состоянием счетчика 4, то ца выходе схемь 5 сравнения формируется нулевой уровень, запирающгй элемент 1-И о, Поэгому в момент оценки состояния процесса в контролируемой спстеьй счгнал ца т:.1 ходе элемента И 6 це появляется (фиг. 2) и ошибка це фцк15 бб 332 10 20 2530 35 40 45 50 55 сируется, т.е. триггер 7 остаетсяв исходном нулевом состоянии, установленном через вход 9 сброса передначалом работы устройства. По спадусигнала " Чтение памяти" ("Подтверждение прерывания") г.остояние счетчика 4 увеличивается ца единицу так же,как.и во всех остальных маппшцыхциклах,Нарушение нормального функционирования контролируемой микропроцессорной системы может быть вызвано,йнримвр, сбоями программного счетчйка, счетчика машинных циклов, укаэртелей косвенных адресов микропроцессора, а также отказом линий в адресной и управляющей шинах системы.Зто может приводить к пропуску целыхкоманд илц машинных циклов в однойкоманде, попыткам извлечения командгаз зоны ОЗУ, нспыткам записи чиселв зону ПЗУ и телПредлагаемое устройство обеспеЧивает выявление подобных причин нарушения процесса функционирования,контролируемой системы. Действительно,при пропуске целого количества команд1программы в результате сбоя прогр.ммного счетчика микропроцессора илц .йекоторогс количества машинных цикловв одной команде в результате сбоя егоСчетчика машинных циклов состояниечетчика 4 в момент очередной оценкисостояния процесса будет не равноКонтрольному числу, извлекаемому изблока 14 постоянной памяти. При сбояхуказателей косвенного адреса, отка:зах линий шин адреса и управлениявозникает несоответствие между адресными и управляющими сигналами. Вэтом случае в момент оценки состоянияпроцесса состояние. счетчика 4 такжене будет равно контрольному числу,извлекаемому из блока 14. Во всехслучаях на выходе схемы сравненияустанавливается единичный уровень,открывающий элемент И 6, В результатеэтото в момент оценки состояния процесса в контролируемой системе на выходе элемента И 6 появляется сигнал,устанавливающйй триггер 7 в единичное состояние, что приводит к активированию выхода ошибки устройстваи фиксации нарушения процесса нормального функционирования в контролируемой системе.Описанным образом устройство функционирует только при воспроизведении линейных участков программы,. пе содержащих точек слияния ветвей, В этом случае каждой команде из программногоПЗУ может быть поставлено в соответствие только одно контрольное число,Однако реальные программы всегда имеют гораздо более сложные ветвящиеся и циклические структуры и содержат точки слияния ветвей, В этих точк .х значения контрольных чисел зависят от того, по какой ветви была выполнена программа, В общем случае контрольные числа при прохождении разлцчных ветвей не совпадают, Это приьодцт к тому что каждой точке слияния ветвей должно быть поставлено в соответствие несколько контрольных чисел, Зи числа должны выбираться в конце реалцза:. ции соответствующих ветвей программы и размещаться по одному адресу блока 14 постоянной памяти, что певсзмсжцс. При невыполнении же этого требования устройство зафиксировалс бы нарушение процесса функциснирсвания контролируемой системы, хотя такового нет.Пдя устранения этого противоречия в.предлагаемом устройстве точки слияния ветвей программы отмечаются нуле-. выми контрольными чцсламц, а перед их реализацией осуществляется сброс предыстории процесса контроля, Ллл этого в блоке 14 постоянной памяти для каждой такоц точки по адресу, цс которому в программном ПЗУ храните; первый байт команды, общей для всех объединяемых в данной точке ветвей программы, размещается нулевое контрольное число. При этом по всем адресам, пс которым в программном ПЗУ хранятся команды, предшествующие по всем ветвям точке слияния, в разряд блока 14 постоянной памяти, управляющий первым его выходом, записывается логическая "единица", что не влияет на значения остальных разрядов выходных слов блока 14 по этим адресам. По всем остальным адресам в этом разряде записывается логический "нуль", что обеспечивает открытое состояние элемента И 13 при выполнении линейных участков программы.В результате этого при выпсленци контролируемой системой команды, предшествующей по любой ветви точке слияние ветвей, на первом выходе блока 14 постоянной памяти появляется уровень логической "единицы"ЦЫОДОЦ СОТОГО 0 СОС ЦС.111 С ЦТОР 011груПО хОДР схси сраццс 151 цторай ц третий ць,ходы перцого блокапостоянной ца.ятп соединены с ходомвыаарк 1 втарага блана пастаяц 10 йпамяти и с цхсд."Ом стробцроцация муль-типлексора, входы устройстг для подключения к цьг.:Одам признаков чтенияпа 1 ят 11 и чтеця:; ар вага б 1 йтл еОмЯды контролируемой системы соединенысоответственно с прямым и иццерсц.м 15013 элемента И 13 и отпирание элемента И 15. Контроль состояния процесса функционирования системы в этом случае осуществляется обычным образом путем сравнения контрольного числа с выхода блока 14 постоянной памяти с состоянием счетчика 4. Однако Очередной импульс с выхода мультиплексора 3 поступит не на счетчнь 1 вход, а на вход синхронизгции счетчика 4, чта приведет к записи в него по спаду управляющего сигнала нулевага числа с его информационного входа, При выполнении команды, соответствующей точке слияния ветвей, из блока 14 постоянной памяти на один вход схемы 5 сравнения паступт нулевое контрольное число, а ца другой - нулевое числа, отражающее состояние счетчика 4, 2 О Вследствие равенства этих чисел схема 5 сравнения формирует нулеоп цьходнай,сигнал, чта обеспечит запцрацце элемента И б и предотвратит фиксацию ложной ошибки цри реализации тачек 25 слияния ветвей программы, выполняемой контролируемой системой.При обнаружении любой ошибки ц контролируемой микропроцессорной системе устанавливается ц единичное состояние триггер 7, чта обеспечивает появление акт нага уровня цг выходе 8 ошибки устройства.Выход 8 Ошибки устройства мажет соединяться с входом запроса преры- вания микропроцесс.орцай сцс.темы. В этом случае цри цозццкцоцеццц Ошибки цыцалцецие текущей программы прерывается, и система переходит к выполнению программы обработки прерывания по синтаксической ошибке, Программа40 обработки прерывания по ошибке может предусматривать восстацоление процесса, нарушенного сбоем, может меть диагностический харгктер (выявление причин ошибки) или, ц простейшем с.лучае, Обеспечив;1 ть Остапов цыруше 11 Огс . процесса. Одпацремсцпо с поцьплепсм достоверности контроля роцесса функционирования микропроцессорной системы предлааемае устройства имеет более простую техническую реализацию. Действительно, па сравнению с известным 01 а содержит ца три функциональных элемента меньше, а также имеет более простую структуру с меньшим 55 количеством связей.Формула и з а б р е т е ц и яУстройство для контроля микропроцессорной системы, содержащее первый 214блок постоянной памяти, мультиплексор, счетчик, схему сравнения, первый, второй и третий элементы 11, элемент ИЛИ, триггер, причем вход уст ройства для подключения к адресному выходу контролируемой системь соединен с группой адресных входов первого блока постоянной памяти, первый выход которого соединен с перым управляющим входом мльтиплексора, вход сброса устройства соединен с входами установки в "О" триггера и счетчика, группа информационных выходов которого соединена с первой группой входов схемы сравнения, выход неравенства которой соединен с первым входом первого элемента И, выход первого элемента И соединен с единичным входом триггера, прямой выход которого является выходом ошибки устройства, входы устрайстна для папключешя к. выходам признаков цодтверждегця прерывания ц чтения памяти контрол;руемай системы соединены соответственна с первьмц ц вторыми вхадамц элемент ИЛИ, выход которого соединен с первым информационным вхапом мульти:лексара, входы устройства для подключения к выходам признаков записи в память, ввота, записи в стек, чтения Стека, вывода и ".агрузкц данныхконтролируемой системы соединены саответственно с вторым, третьим, четвертым, пятым ц Гестым пформаццонцымп входами и вторым управляютим входо 1 му тпплскс сГ ВхОд устрОЙстчдля подключен 51 к выхолу загрузки;иых контра:цруемой системы соединен с адресным хоам 1 арага блокапостоянной памяти, 0 т л и ч а ю -щ е е с я тем, чта, с целью 1 Овыцения дастоцерпастц контра.я микропроцессорной системы, ц устройствовцеданы второй блок постоянной имяти ц четвертый элемент И, причемадресный вход устрсястца соединен садресным входам второго блока 1 остояцОй пгья ГГ 11111 1 нфа 111 ццаццьх1566332 6 в 1 одами второго элемента И, выход информационный вход счетчика соединен которого соединен с, седьмым информа- с шиной нулевого потенциала устройст" ционным входом мультиплексора, входы ваустройства для подключения к выходам5Таблиа лица 1 признаков чтения памяти и чтения первого байта команды контролируемой Адресный массив системы соединены соответственно свторым и третьим входами первого АА А А АЮф тЪ11 лемента И, выход мультиплексора соеинеи с прямым входом третьего эле- О О 0 0 О ПЗУ мента И и первым входом четвертого 0 1лемента И, выход которого соединен 1 . 0 0 0 0 ОЗУвходом синхронизации счетчика, вы О 1 0 ход второго блока постоянной памяти 15 1 0 1 0 1 Соединен с вторым входом четверто 0 1 1 О го элемента И и инверсным входом 1 1 1 1 О третьего элемента И, выход которого 1 1 1 1 1 УВВ соединен со счетным входом счетчика,Устройства микропроцессорнойсистемы СтекНе использовано 20 Таблица 2 гходы блока 1 постоянной Примечаниесные входы Зона ад ресного простра памят ый вход Вт рвый выд (кодращения) Третийвыход(обращение на 2 ад- вх К ПЗУ ПЗУ ОЗУ 00000В01111 корректнаятуация 1. 00 0 0 1 100 О О 0 0 1 10101 10101 1111111111 те О испольваннаяна 0 Некорректнаситуация 1 10 О1/66332 Таблица 3 Ожидаемый управляющий сигнал Второйвход (пЗа Первыйвход (кодобращения) входу грузкаданных ) Некорре "Чтение О О ПЗУ 1 О Стек УВЯ Составитель Ы,СигалсРедактор В.Данко Техред. И.Ходанич Корректор А.Обручар Тираж 562 Подписрственного комитета по.изобретениям 11303/, Москва, Ж/, Раушская на 2 ЗаказВБИИПИ НТ ССС ткрытиям и д. 4// о ский комбинат "Патент", г. Ужгород, ул, Гагарина, 1 роизводственно-издат Выбранное Кол на управлаолих устройство входах мультиплексистемы сора 3 О 1 О 1 О 1 Выбираемый иЬормацнопый вход мультиплексора 3, соответствующий его упрввляюг .му 2 3 4 / 6 3 твержде иЗапись "Чтение ЗаписьЧтение "Вывод "Ввод" ктная ситуация памяти. или Подние прерывания" в памчть11памяти

СмотретьЗаявка

4454676, 05.07.1988

РЫБИНСКИЙ АВИАЦИОННЫЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ

КОМАРОВ ВАЛЕРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: микропроцессорной, системы

Опубликовано: 23.05.1990

Код ссылки

<a href="https://patents.su/9-1566332-ustrojjstvo-dlya-kontrolya-mikroprocessornojj-sistemy.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля микропроцессорной системы</a>

Предыдущий патент: Регулятор температуры

Следующий патент: Цифровой функциональный генератор

Случайный патент: 156367