Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

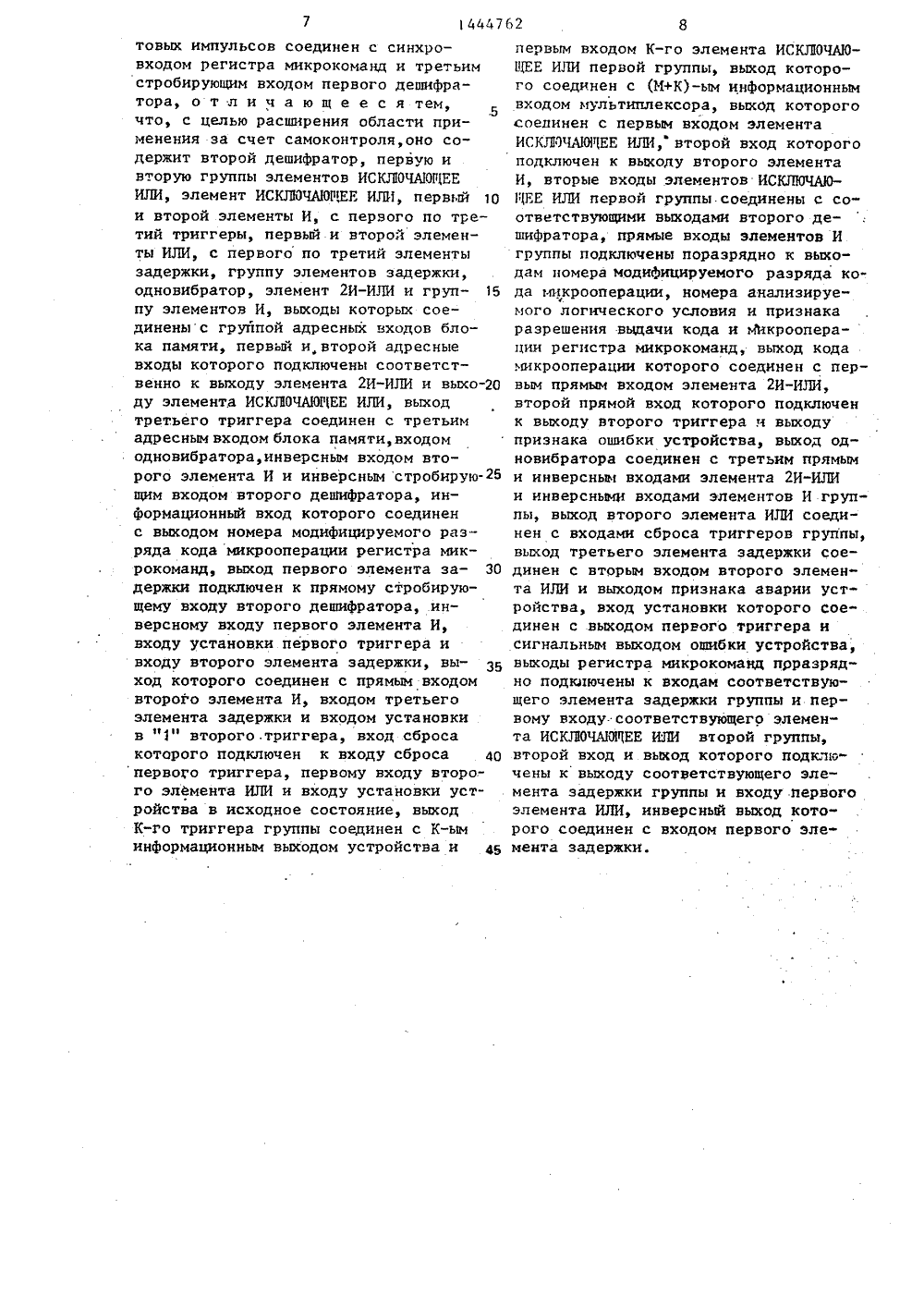

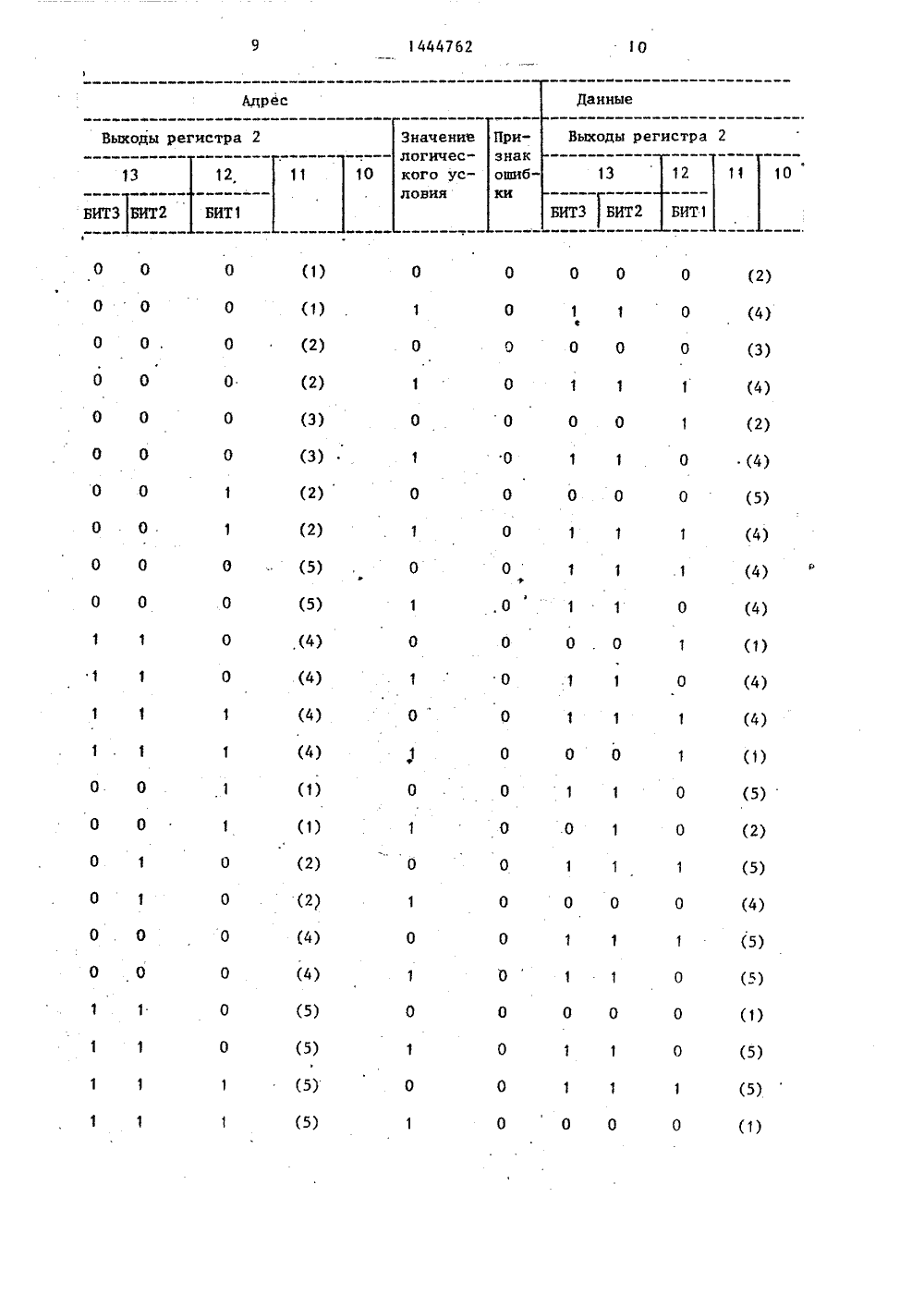

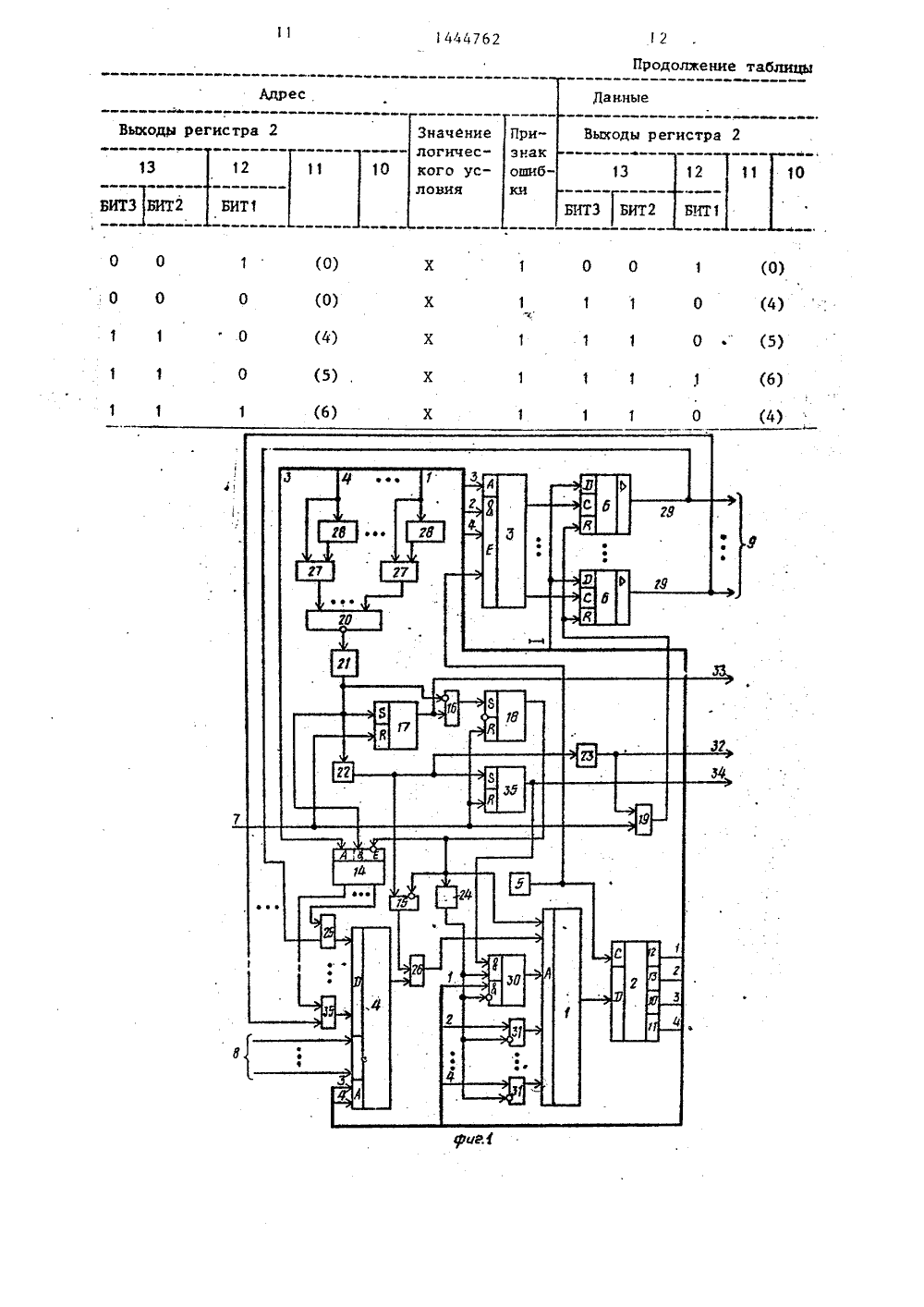

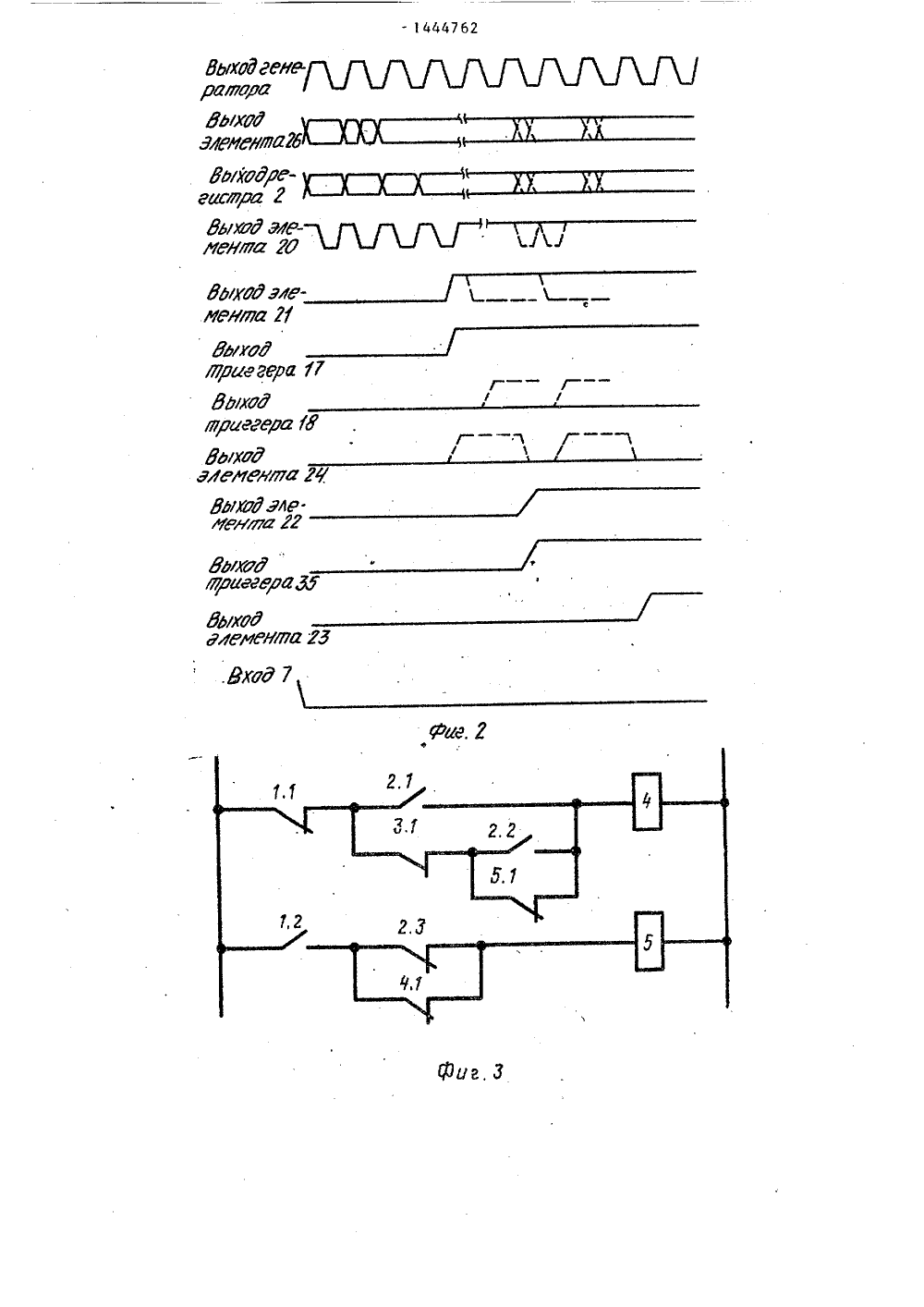

(5 ОПИСАНИЕ, ИЗОБРЕТЕН Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ый ом ева(57) Изобре вычислитель к программн ческим обор использован ение относит ой техники,му управлениюдованием, и при построе я к областиименнотехнологиожет бытьнии програмСУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(21) (22) (46) (71) завод (72) (53) (56) техн 1981А В 12 4250982/24-2402,04.8715.12.88, Бюл.Московский автим, И.А,ЛихачВ.И.Хохлов и А681,3(088.8)Мейздаология ис. 162торское6476,(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ мируемых контроллеров, Цель изобретения - расширение области применения за счет самоконтроля. Устройство микропрограммного управления содержит блок памяти, регистр микро- команд, дешифраторы, мультиплексор, генератор тактовых импульсов, группу триггеров, группы элементов ИСКЗЮЧАЮЩЕЕ ИЛИ, элемент ИСКЗЮЧАИЩЕЕ ИЛИ, элементы И, триггеры, элементы ИЛИ, элементы задержки, группу элементов задержки, одновибратор, элементы 2 И-ИЛИ, группу элементов И. Устрой ство позволяет идентифицировать три приоритетных уровня ошибки, переходить к выполнению микропрограммыпо обработке аварийного режима или .осуществлять экстренное отключение устройства, а такжеобеспечивает сигнализацию йаличия и уровня ошибки.4 ил., 1 табл.Изобретение относится к вычислительной технике, а именно к программному управлению технологическим оборудованием, и может быть использованопри построении программируемых устройств управления.Цель изобретейия - расширение области применения устройства за счетсамоконтроля, 10На фиг.1 изображена структурнаясхема предлагаемого устройства нафиг.2 - временные диаграммы работыустройства, иллюстрирующие взаимноерасположение сигналов на выходах блоков устройства; на фиг.3 - переключ . -тельная схема, изображенная в видедиаграммы релейной символики, нафиг.4 - блок-схема алгоритма работыустройства. 20Устройство содержит блок 1 памяти, регистр 2 микрокоманд, первый дешифратор 3, мультиплексор 4, генератор 5 импульсов, группу триггеров 6,вход 7 начальной установки устройства, вход 8 логических условий устройства, информационный выход 9 устрой-ства, выход 10 номера модифицируемого разряда кода микрооперации, выход11 номера анализируемого логическогоусловия, выход 12 кода микрооперации, выход 13 признака разрешения выдачи кода микрооперации, второй дешифратор 14, второй 15 и первый 16элементы И, первый 17 и второй 18триггеры, второй 19 и первый 20 элементы ИЛИ, первый 21, второй 22 и тре.тий 23 элементы задержки, одновибратор 24, первую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25, элемент ИСИПОЧАЮЩЕЕИЛИ 26 вторую группу ИСКДОЧАЮЩЕЕИЛИ 27, группу элементов 28 задержки, выходы 29 триггеров группы, элемент 2 И-ИЛИ 30, группу элементовИ 31, выход 32 признака аварии, выход 33 признака ошибки и выход 34 ти-па ошибки.Устройство работает следующим образом,Значения логических условий поступают через вход 8 устройства и циклически анализируются. Вычисленные ввиде кода микрооперации значения функ.ций запоминаются в триггерах 6 и поступают на выход 9 устройства. В каждом такте микрокоманда из. блока 1 памяти загружается в регистр 2 микро-команд. Адрес следующей микрокомандыформируется в соответствии со значением (О или 1) анализируемого аргумента - логического условия или промежуточного результата вычисления(фракции), подаваемого через мультиплексор 4 и элемент ИСКЛОЧАЮЩЕЕИЛИ 26 на третий адресный вход блока 1 памяти и содержимого регистра 2микрокоманд, поступающего на адресные входы блока 1 памяти, Если анализируемый аргумент входит в вычисляемую булевую функцию с инверсией иравен "1" или входит без инверсии иравен "0", то из блока 1 памяти выбирается следующая микрокоманда, соответствующая аргументу, входящему вдизъюнкцию к анализируемой части функции, Если такая дизъюнкция отсутствует, то выбирается следующая микрокоманда, инициализирующая через первый,дешифратор 3 установку в "О" соответствующего триггера 6 группы, Еслианализируется аргумент, входяп 1 ий ввычисляемую булевую функцию с инверсией и равный "О" или входящий беэинверсии и равный "1", то из блока 1памяти выбирается следующая микроко,манда, соответствующая аргументу,входящему в конъюнкцию к анализируемойчасти функции. Если таковая конюнкция отсутствует, то выбирается сле-дующая микркоманда, инициализирующая через дешифратор 3 установку в" 1" соответствуюЩего триггера б группы,Если выполняется микрокоманда, инициализирующая установки триггеров 6группы в состояние У илуто выход триггера б контролируетсячерез элемент ИСКЛОЧАЮЩЕЕ ИЛИ 25 первой группы, мультиплексор 4 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26. Если состояние триггера 6 группы совпадает сжелаемым, то выбирается следующаямикрокоманда, соответствующая проверке аргумента для вычисления очередного кода микрооперации, Если состояние триггера 6 группы не совпадает сжелаемым, то снова выбирается микрокоманда, соответствующая требуемойустановке,Выбранная микрокоманда в следующемтакте загружается в регистр 2 микрокоманд, и вышеуказанный процесс возобновляется.Запись в регистр 2 микрокоманд может инициализировать по положительному фронту импульсов с генератора 5,а запись кода микрооперации в триг 3 14447 гер 6 группы - по отрицательному фронтуПеред началом работы устройства на вход 7 начальной установки подает.5 ся импульс установки в исходное состояние, длительность которого превышает максимально возможное время, необходимое для вычисления кода микро- операции, при этом осуществляется сброс триггеров 6 группы, а также с первого по третий триггеров устройства (фиг.2).В случае нормального функционирования 0 с выхода первого элемента 15 21 задержки обеспечивает блокировку второго дешифратора 14, при этом низкие уровни сигналов на выходах последнего, поступая на одни входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 25 первой группы, 2 О дают возможность для работы этих элементов в режиме повторения сигналов на их других входах. Сигнал "О" с выхода второго элемента 22 задержки поступае через второй элемент И 15 25. на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, обеспечивая прохождение сигнала с мультиплексора 4 на блок 1 памяти без инверсии, Сигнал "О" с выхода третьего триггера 18 через одновибратор 24 ЭО поступает на входы элементов 2 И-ИЛИ ЗО и И 31,обеспечивая беспрепятственное прохождение информации с выхода ре - гистра 2 микрокоманд на входы блока 1 памяти.В случае нарушения работы устройства (например, из-за нарушения контактов разъемных соединений, связываЮщих узлы устройства, выхода из строя триггеров 6 группы, регистра 2 40 ; микрокоманд, мультиплексора 4, генератора 5 и т.п.) информация на выходе регистра 2 микрокоманд перестает сменяться, Обеспечение фиксации одной и той же информации в регистре 2 45 микрокоманд может быть, осуществлено программно, т.е, в результате повторения циклов выбора одной и той же микрокоманды при неудовлетворительной инициализации циклов записи очередно О го кода микрооперации в триггеры 6 группы. При этом на выходах элементов ИСКЛЮЧА 10 ЩЕЕ ИЛИ 27 второй группы перестают появляться импульсы, осуществляющие через элемент ИЛИ 20 сброс 55 первого элемента 21 задержки. Элемент 21 задержки обеспечивает задержку сигнала высокого уровня на время (несколько циклов генератора 5),62 4обеспечивающее достоверное определение нарушения в работе устройства и имеет малое время восстановления. Элементы 28 задержки группы настроены на время задержки, равное половине длительности периода генератора 5, обеспечивающее формирование на выходе элемента ИЛИ 20 импульса, перекрывающего по длительности время восстановления элемента 21 задержки. Появление "1" на выходе элемента 21 задержки фиксируется в триггере 17 установкой его в состояние "1" и установкой сигнала "1" на выходе 33 признака ошибки устройства. Единичный сигнал с выхода элемента Ъ 1 задержки разрешает работу дешифратора 14, который обеспечивает перевод элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 первой группы, соответствующего выходу устройства, определяемому номером модифнцируемого разряда кода микрооперации, в режим инвертирования входной информации. При этом по переключению выходов регистра 2 микрокоманд судят о наличии ошибки первого ряда (например, перегорание одного из предохранителей). Если переключение регистра 2 микрокоманд не прошло через время, превышающее длительность одного цикла генератора 5, то срабатывает второй элемент 22 задержки и через элемент И 15 элемент ИСКЛЮЧА 1011 ЕЕ ИЛИ 26 переводится в режим инвертирования входной информации. Если и после этого переключение регистра 2 микрокоманд, свидетельствующее о наличии ошибки второго рода, не произошло через время, превышающее длительность цикла генератора 5, то срабатывает третий элемент 23 задержки, в результате чего на выходе 32 устройства появляется сигнал "1", сигнализирующий об аварии, через элемент ИЛИ 19 осуществляется сброс триггеров 6 группы и обеспечивается отключение устройства от объекта управления.Если была зафиксирована ошибка первого или второго рода, т.е. произошло переключение регистра 2 микрокоманд то на выходе элемента ИЛИ 20 формируется импульс, сбрасывающий с первого по третий элементы задержки, в результате чего на выходе элемента И 16 появляется "1", устанарливающая триггер 18, При этом в триггере 35 фиксируется тип ошибки: "О"5 14447 ошибка первого рода ИЛИ "1" - ошибка второго рода. Единица с выхода триггера, 18 блокирует через дешифратор 14 и элемент И 15 переключение элементов ИСКДОЧА 10 ЩЕЕ ИЛИ 2 б в режим5 инвертирования и осуществляет запуск одновибратора 24; формирующего импульс, длительность которого превышает длительность периода генератора 5, Указанный импульс, поступая на элементы 2 И-ИЛИ 30 и И 31, обеспечивает формирование вектора (следующего адреса микрооперации), соответствующего роду ошибки, Дальнейшая обработ ка микропрограммы осуществляется в зависимости от рода Ьшибки. Тип ошибки может быть считан с выхода 34 устройства.Проиллюстрируем работу устройства при реализации булевых функций, представленных в виде диаграммы .релейной символики (Фиг.З).Идентификационный номер контактов (аргументов) и катушек реле (функ ций) указан на диаграмме (фиг.З) цифрой, стоящей перед точкой. Этот номер занимает поля 10 и 11 микрокоманд. Пусть в процессе вычислений аргумент анализируется на более восьми раз, ЗО тогда разрядность поля 12 микрокоманды равны 3. Очередность проверки аргумента с одним идентификационным номером в про, 35 цессе обработки микропрограммы указаны на диаграмме (фиг.З) цифрами, стояпщми после точки. При реализации переключательной схемы (фиг,З) в случае нормального функционирования устрой" ство будет работать по алгоритму (Фиг.4), логические блоки которого вы-, полняют следующие действия:проверяют логическое условие 1 наравенство "0",45проверяют логическое условие 2иа равенство "0","проверяют логическое условие 3на равенство "0";проверяют значение функции 4 наравенство "0",проверяют значение функции 5 наравенство "0";устанавливают значение функции 4равным "1";55устанавливают значение 5 равным11 и,устанавливают значение функции 4равным "0"; б 26устанавливают значение функции 5равным "0".В таблице представлен пример программирования блока 1 памяти по пе- . реключательной схеме (фиг,З) где 1 - логическая единица0 - логический ноль;Х - безразличное состояние;К)- идентификационный номер аргумента или функции.В данном примере в случае ошибки второго рода обеспечивается программная блокировка изменения состояния регистра 2 микрокоманд и тем самым генерация сигнала "Авария". В случае ошибки первого рода иницианализируется отключение Функций 4 и 5 и включение функций 6 (на диаграмме (фиг.З) не показана), с помощью которой может быть осуществлено отключение вводного контактора питания системы управления "стоящего" на самоблокировке и снятия питающих напряжений,Формула изобретения Устройство микропрограммного управления, содержащее блок памяти, регистр микрокоманд, первыи дешифратор, генератор тактовых импульсов и группу триггеров, причем выход блока памяти подключен к информационному входу регистра микрокоманд, синхровход которого подключен к выходу генератора тактовых импульсов, вход К-го логического условия устройства подключен к К-му.информационному входу мультиплексора (К,И, где И - число логических условий устройства, выход номера модифицируемого разряда кода микрооперации регистра микро- команд подключен к информационному входу первого дешифратора и к перво- , му управляющему входу мультиплексора, выход номера анализируемого логи,ческого условия регистра микрокоманд подключен к первому стробирующему входу первого дешифратора и второму управляющему входу мультиплексора, выход кода микрооперации регистра микрокоманд подключен к информационным входам триггеров группы, выход признака разрешения выдачи кода микро" операции регистра микрокоманд подключен к второму стробирующему входу первого дешифратора, К-й выход которого подключен к синхровходу К-го триггера группы, выход генератора так 14447 б 2товых импульсов соединен с синхровходом регистра микрокоманд и третьимстробирующим входом первого дешифратора, о т л и ч а ю щ е е с я тем,что, с целью расширения области применения за счет самоконтроля,оно содержит второй дешифратор, первую ивторую группы элементов ИСКЛЮЧАЮЩЕЕИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый 10и второй элементы И, с первого по третий триггеры, первый и второй элементы ИЛИ, с первого по третий элементызадержки, группу элементов задержки,одновибратор, элемент 2 И-ИЛИ и группу элементов И, выходы которых соединеныс груйпой адресных входов блока памяти, первый ивторой адресныевходы которого подключены соответственно к выходу элемента 2 И-ИЛИ и выхо ду элемента ИСКЛОЧАЮЩЕЕ ИЛИ, выходтретьего триггера соединен с третьимадресным входом блока памяти, входомодновибратора,инверсным входом второго элемента И и инверсным стробирую щим входом второго дешифратора, информационный вход которого соединенс выходом номера модифицируемого разряда кода микрооперации регистра микрокоманд, выход первого элемента задержки подключен к прямому стробирующему входу второго дешифратора, инверсному входу первого элемента И,входу установки первого триггера ивходу второго элемента задержки, выход которого соединен с прямым входомвторого элемента И, входом третьегоэлемента задержки и входом установкив "1" второго, триггера, вход сбросакоторого подключен к входу сброса 40первого триггера, первому входу второго элемента ИЛИ и входу установки устройства в исходное состояние, выходК-го триггера группы соединен с К-ыминформационным выходом устройства и первым входом К-го элемента ИСКЛОЧАЮЩЕЕ ИЛИ первой группы, выход которого соединен с (И+К)-ым информационнымвходом мультиплексора, выход которогосоединен с первым входом элементаИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которогоподключен к выходу второго элементаИ, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы соединены с соответствующими выходами второго дешифратора, прямые входы элементов Игруппы подключены поразрядно к выходам номера модифицируемого разряда кода микрооперации, номера анализируемого логического условия и признакаразрешения выдачи кода и ьФкрооперации регистра микрокоманд, выход кодамикрооперации которого соединен с первым прямым входом элемента 2 И-ИЛИ,второй прямой вход которого подключенк выходу второго триггера и выходупризнака ошибки устройства, выход одновибратора соединен с третьим прямыми инверсным входами элемента 2 И-ИЛИи инверсными входами элементов И группы, выход второго элемента ИЛИ соединен с входами сброса триггеров группы,выход третьего элемента задержки соединен с вторым входом второго элемента ИЛИ и выходом признака аварии устройства, вход установки которого сое"динен с выходом первого триггера исигнальным выходом ошибки устройства,выходы регистра микрокоманд прразрядно подключены к входам соответствующего элемента задержки группы и первому входу соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы,второй вход и выход которого подключены к выходу соотВетствующего элемента задержки группы и входу первогоэлемента ИЛИ, инверсный выход кото"рого соединен с входом первого элемента задержки.444762 1 О Адрес Данные Вьиоды регистра 2 ПризнакошибЗначение логичес 13 кого условия 0 0 0 0 0 0 0 О 0 О 1 ф 0 0 1 1 О 0 1 1 О О14447 б 2 Продолжение таблицы Адрес Лакные Значениелогического условия Выходы регистра 2 Признакошиб 10 13 12 10 БИТ- 1444762дювдггю. ОЮЖРЯУ Жаа ЗМекенаа 26Ржй 7 дрггаюю Г ,Й/ЯР ЯРФРФяа РР Л./1444762 оставитель А,Афанасьев ехред Л,Олийнык Корректор И.Муска актор А.Реви 82/48 одписно а Производственно-полиграфическое предприятие, г. Ужгород,оектная Тираж 704 ВНИИПИ Государстве по делам изобрет 113035, Москва, Ж"35, ого комитета СССРий и открытййаушская наб.,-д, 4/5

СмотретьЗаявка

4250982, 02.04.1987

МОСКОВСКИЙ АВТОМОБИЛЬНЫЙ ЗАВОД ИМ. И. А. ЛИХАЧЕВА

ХОХЛОВ ВЛАДИМИР ИВАНОВИЧ, АНДЕРСОН АЛЕКСАНДР ИОСИФОВИЧ

МПК / Метки

МПК: G06F 9/00

Метки: микропрограммного

Опубликовано: 15.12.1988

Код ссылки

<a href="https://patents.su/9-1444762-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для умножения частоты

Следующий патент: Устройство для обслуживания запросов

Случайный патент: Электролит меднения