Устройство для вычисления систем логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

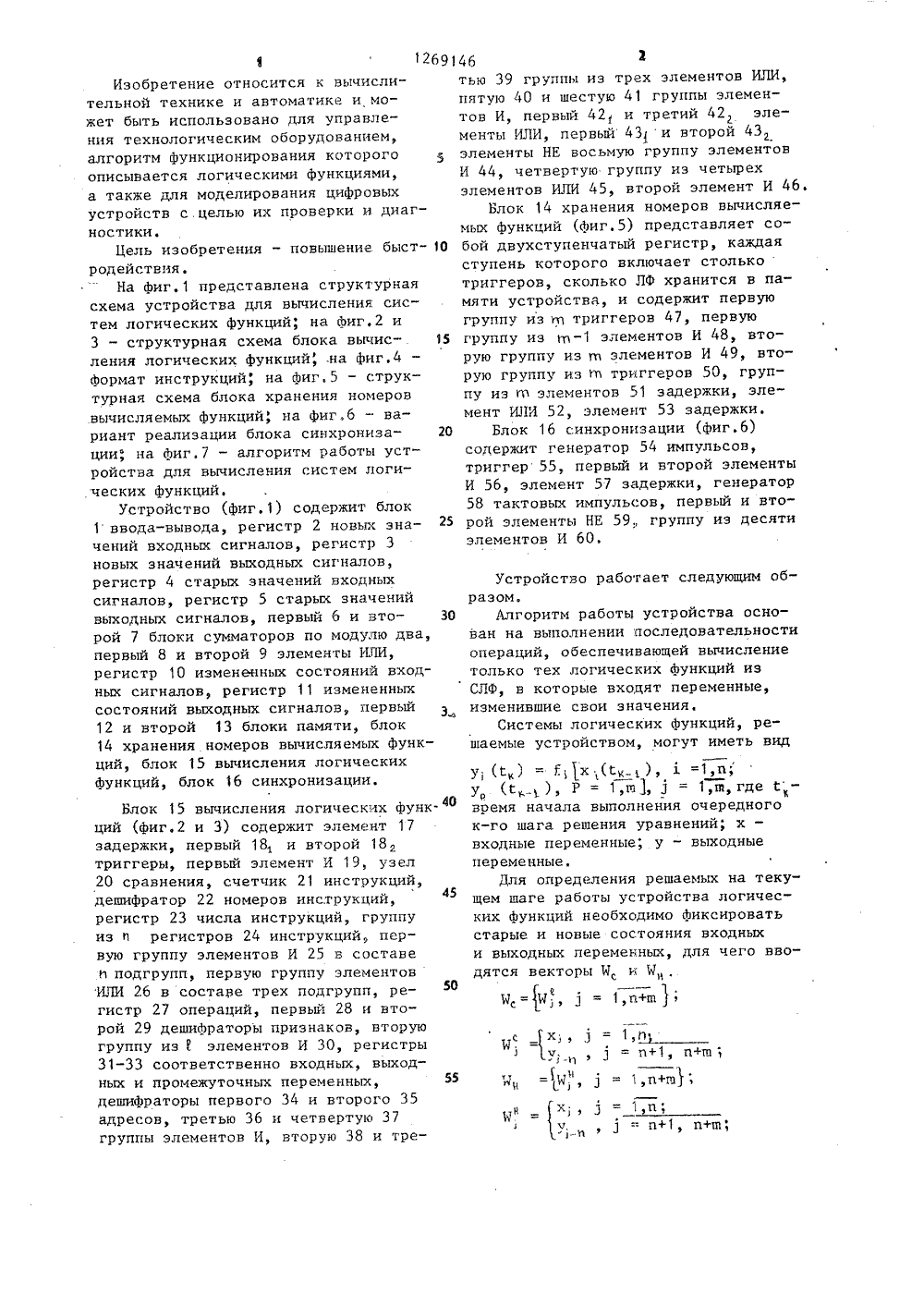

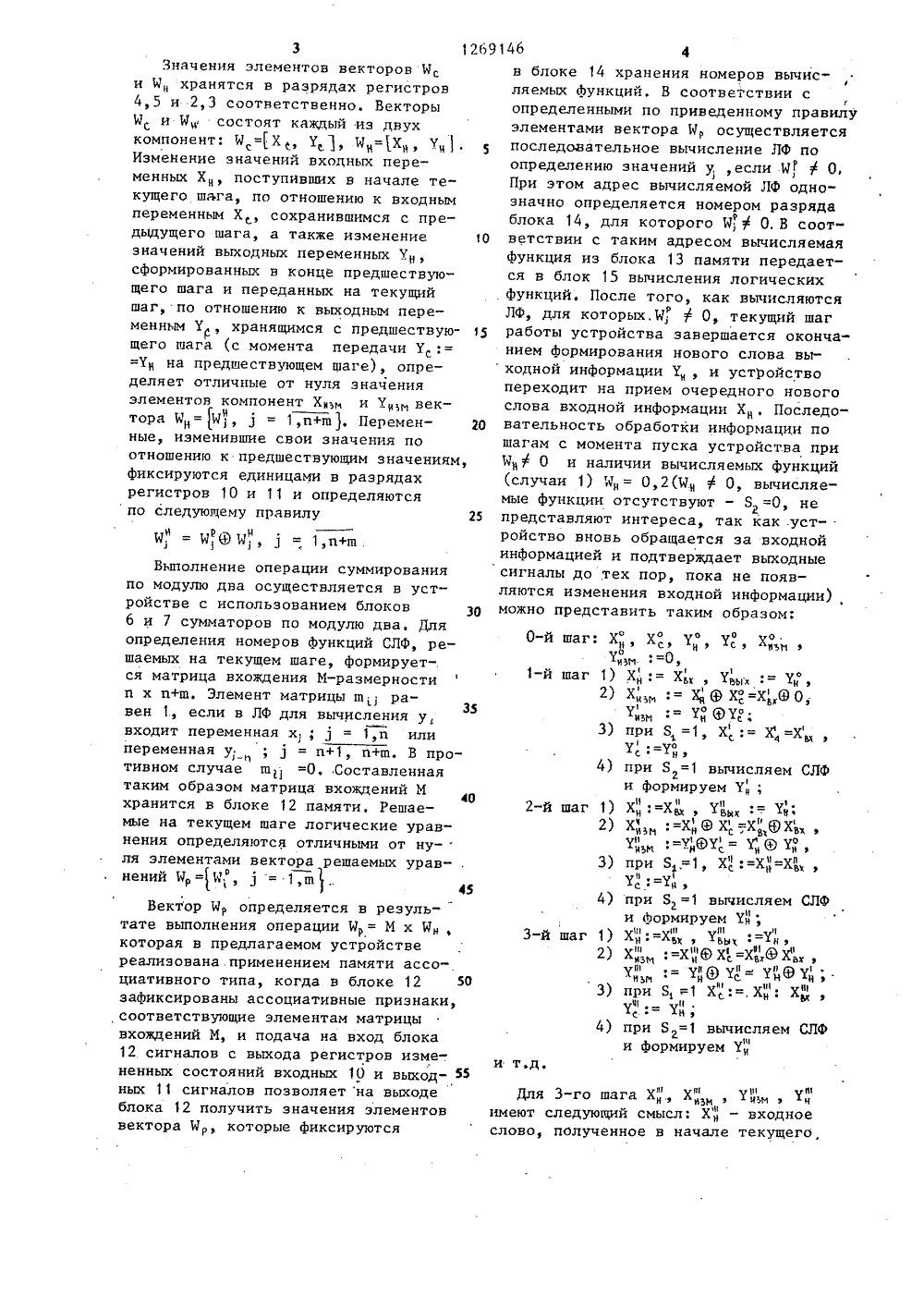

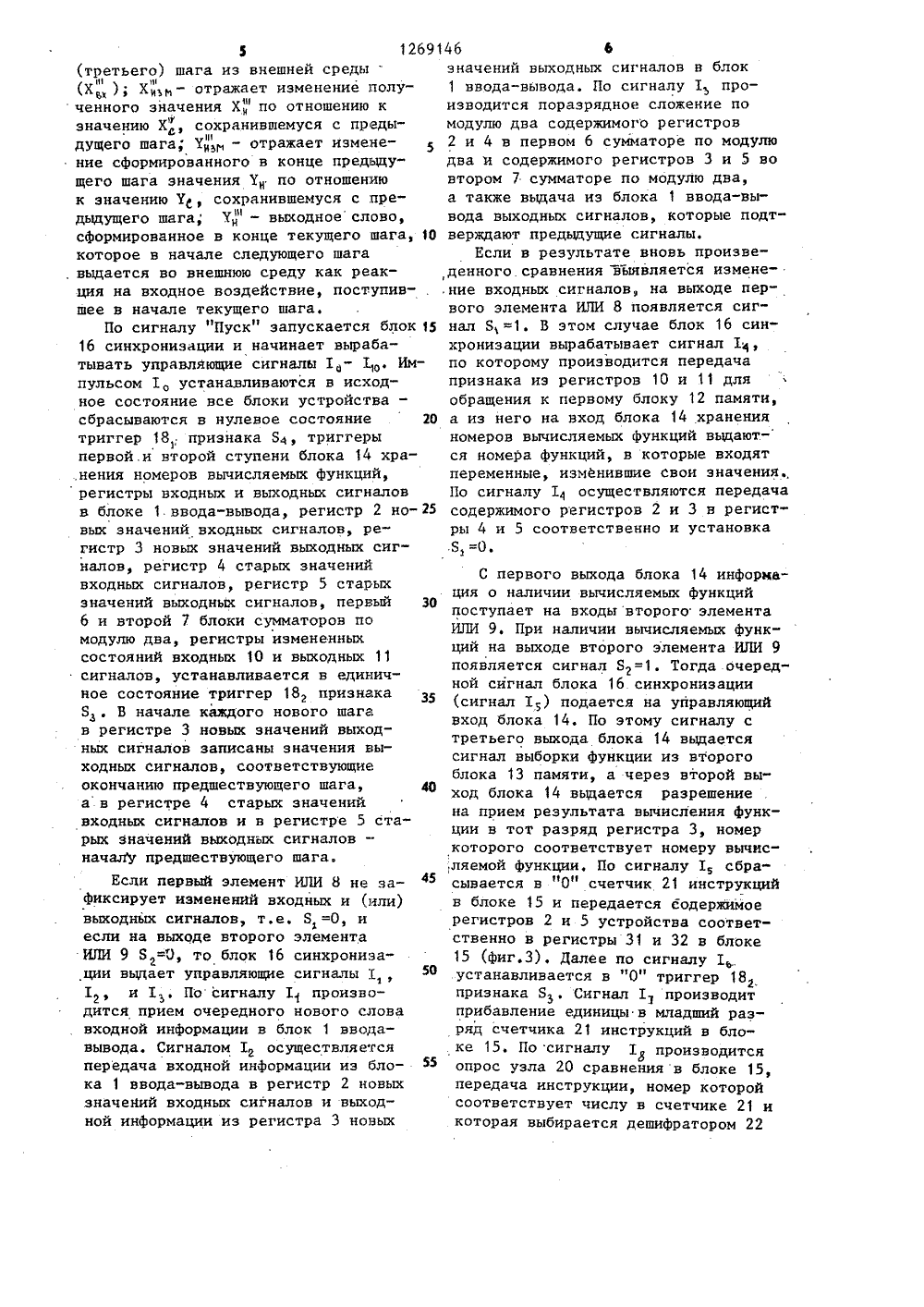

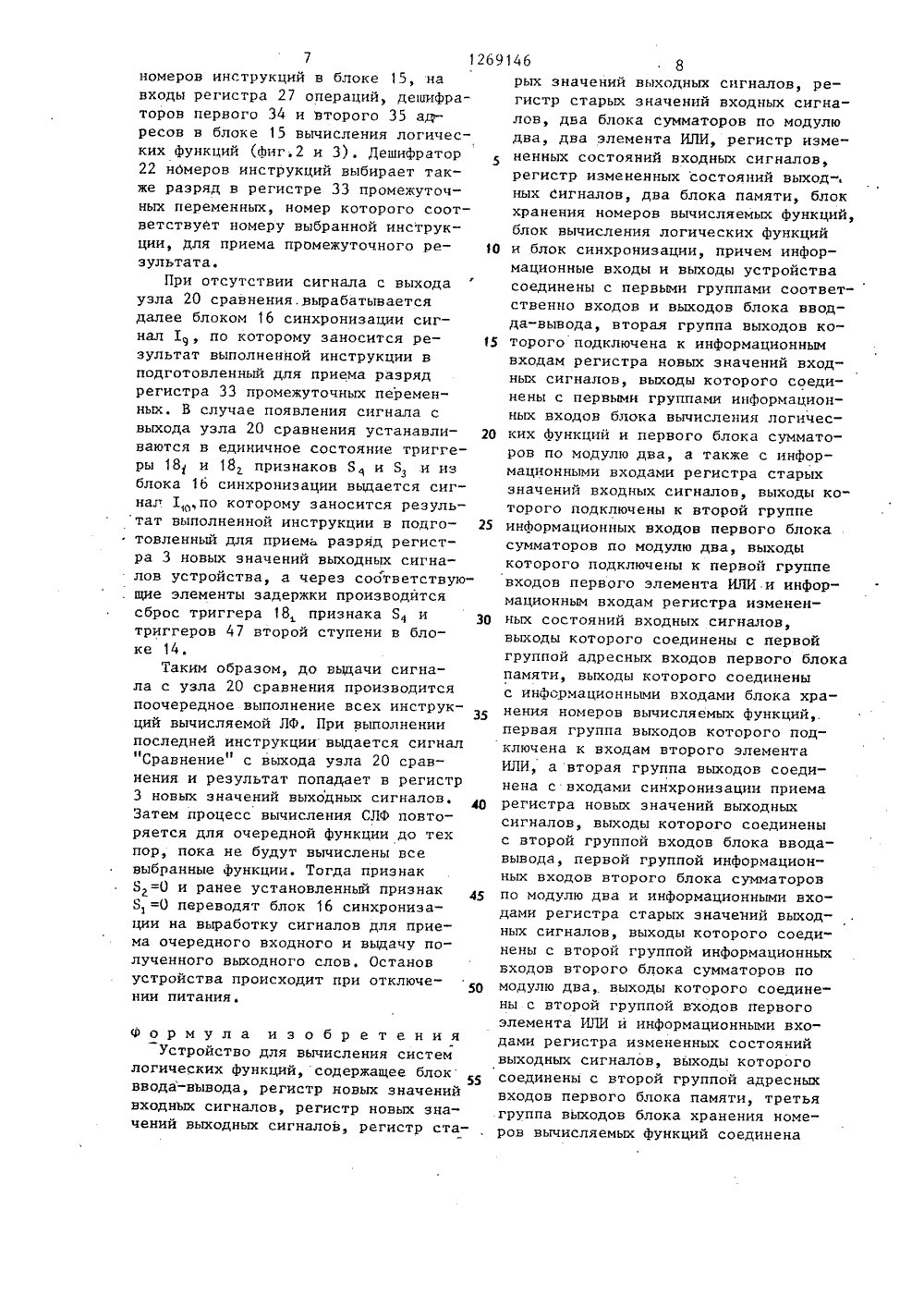

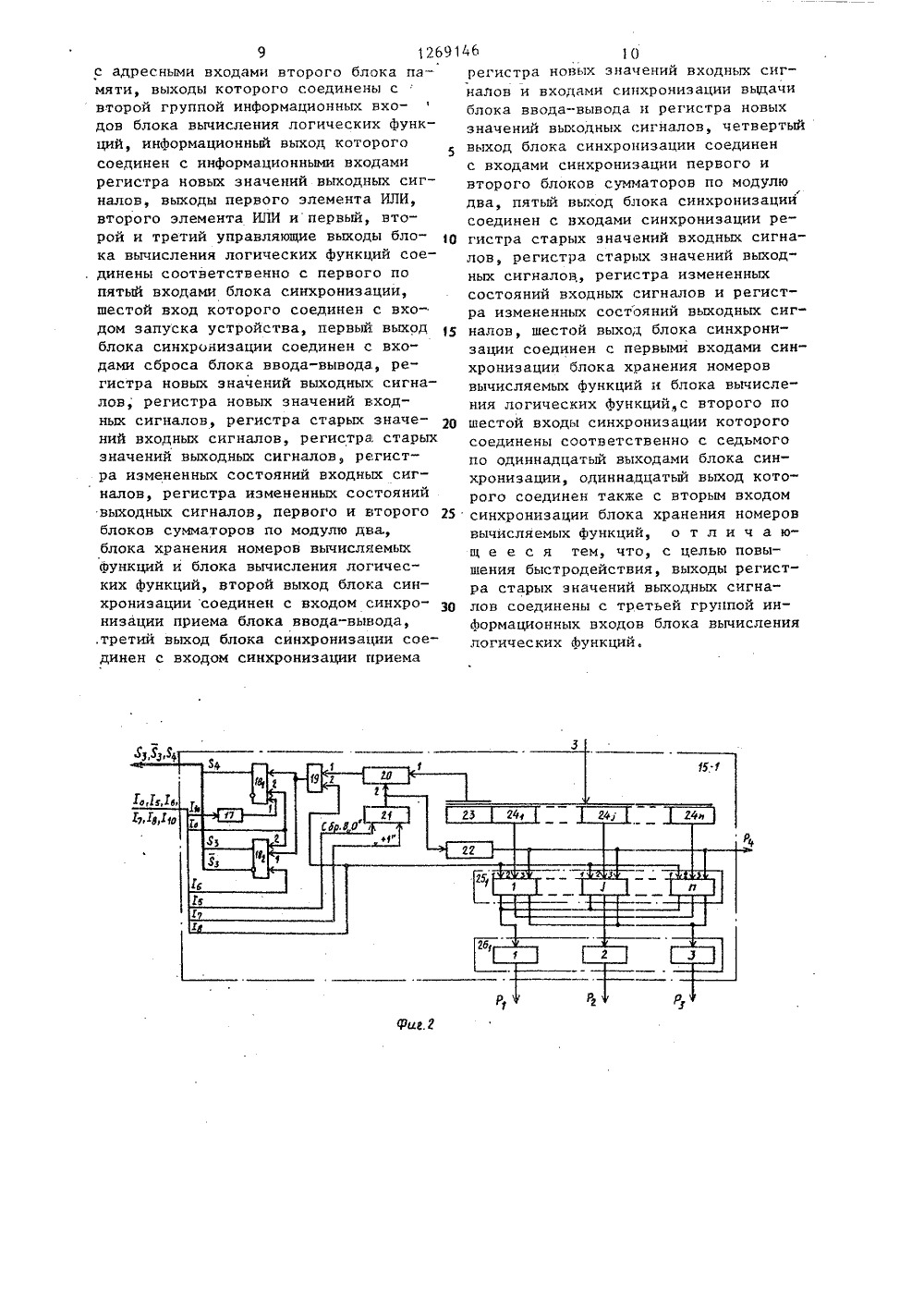

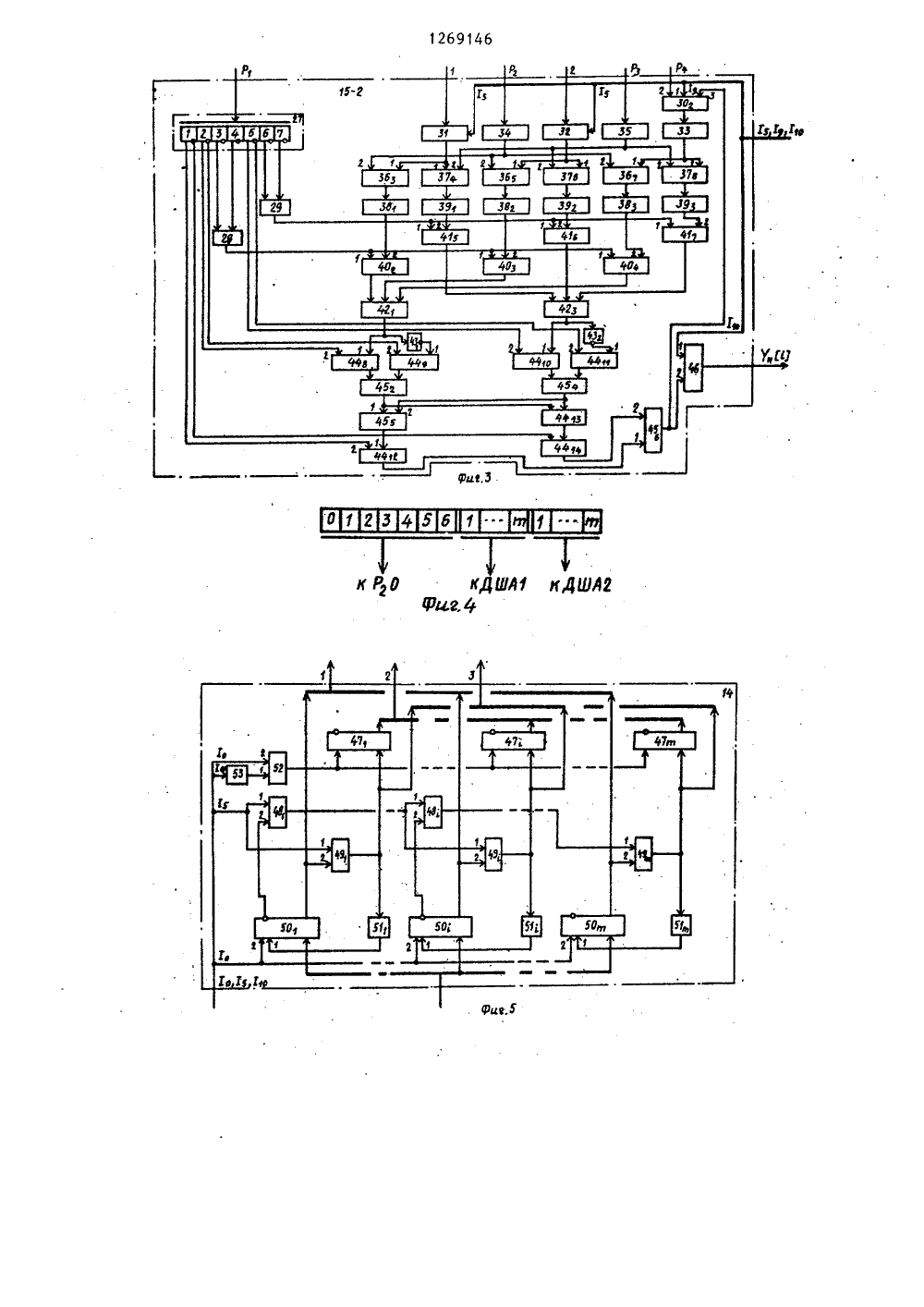

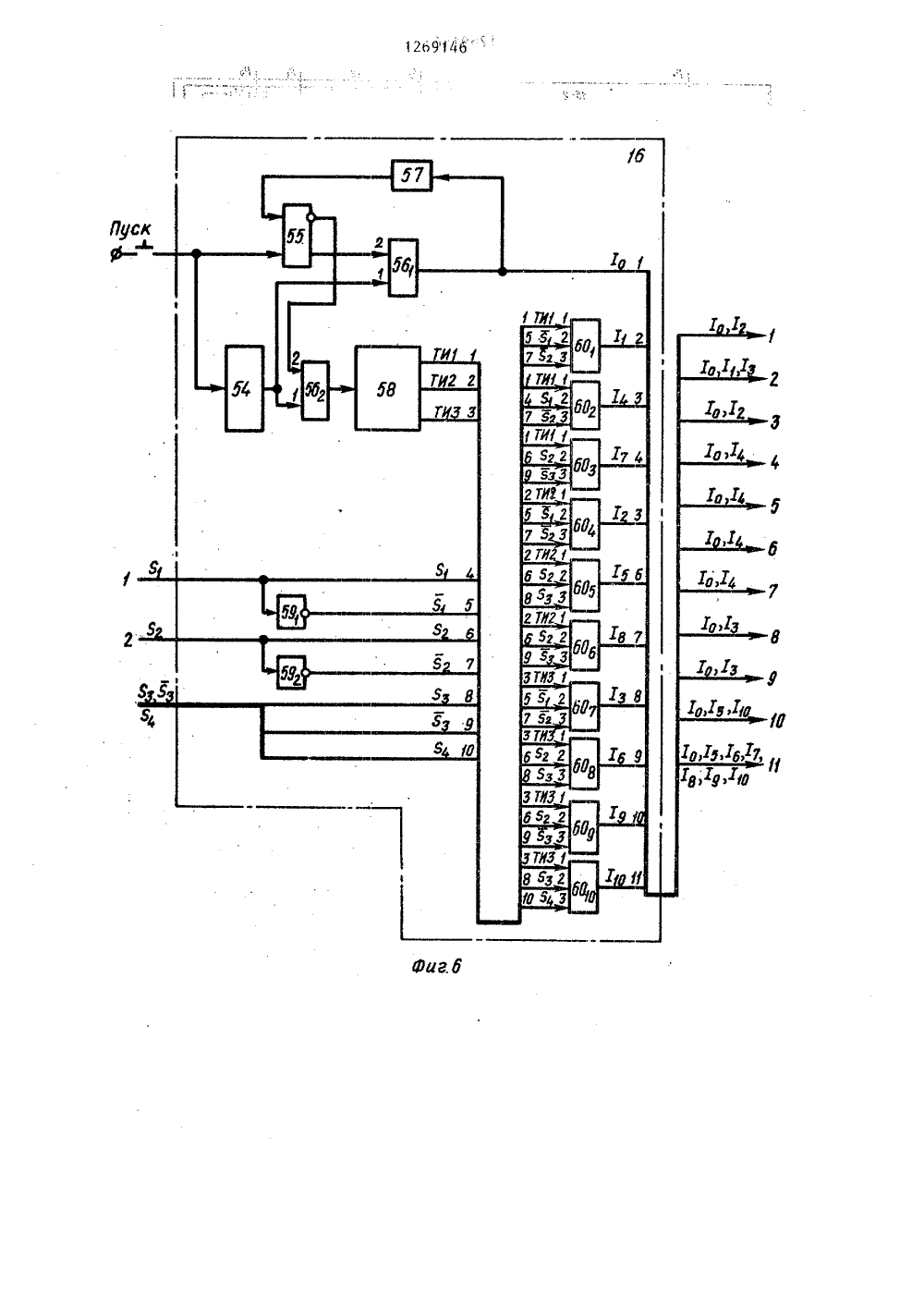

(21) (22) (46) 3514634/24-2426.11.8207.11.86. Бюлогилевский мтут ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТВ У 41(56) Авторское свидетельство СССРМ 732878, кл. С 06 Р 15/20, 1980,Авторское свидетельство СССР1 е 1164724, кл. С 06 Р 15/20, 1981.(54) УСТРОЙСТВО Ди ВЫЧИСЛЕНИЯ СИС, ТЕМ ЛОГИЧЕСКИХ ФУНКЦИЙ(57) Изобретение относится к вычислительной технике и может быть использовано для управления технологическим оборудованием, алгоритм функционирования которого описывается логическими функциями, а также для моделирования цифровых устройств с целью их проверки и диагнос тики. Цель изобретения - повышение быстродействия, Устройство содержитблок 1 ввода-вывода, регистр 2 новых значений входных сигналов, регистр 3 новых значений выходных сигналов, регистр 4 старых значений " входных сигналов, регистр 5 старых значений выходных сигналов, два блока .6,7 сумматоров по модулю два, два элемента ИЛИ 8,9, регистр 10 измененных состояний входных сигналов, регистр 11 измененных состояний выходных сигналов, два блока 12, 13 памяти блок 14 хранения номеров вычисляемых функций, блок 15 вычисления логических функций, блок 16 синхронизации. Цель изобретения достигается за счет соединения. выходов регистра старых значений выходных сигналов с,третьей группой информационных входов блока вычисления логических функций, 7 ил.- -и т 1 м "н =К х;, З = 1 п;Р Изобретение относится к вычислительной технике и автоматике и может быть использовано для управления технологическим оборудованием,алгоритм функционирования которогоописывается логическими Функциями,а также для моделирования цифровыхустройств с целью их проверки и диагностики,Цель изобретения - повышение быст Ородействия.На фиг,1 представлена структурнаясхема устройства для вычисления систем логических функций; на Фиг.2 и3 - структурная схема блока вычисления логических функцийна фиг,4Формат инструкций; на фиг.5 - структурная схема блока хранения номероввычисляемых функций, на фиг.6 - вариант реализации блока синхронизации, на Фиг.7 - алгоритм работы устройства для вычисления систем логических функций.Устройство (Фиг.1) содержит блок1 ввода-вывода, регистр 2 новых значений входных сигналов, регистр Эновых значений выходных сигналов,регистр 4 старых значений входныхсигналов, регистр 5 старых значенийвыходных сигналов, первый 6 и второй 7 блоки сумматоров по модулю два,первый 8 и второй 9 элементы ИЛИ,регистр 10 измененных состояний входных сигналов, регистр 11 измененныхсостояний выходных сигналов, первый12 и второй 13 блоки памяти, блок14 хранения номеров вычисляемых функций, блок 15 вычисления логическихфункций, блок 16 синхронизации,Блок 15 вычисления логических функ.4 О ций (Фиг.2 и Э) содержит элемент 17 задержки, первый 18, и второй 18 триггеры, первый элемент И 19, узел 20 сравнения, счетчик 21 инструкций, дешифратор 22 номеров инструкций, регистр 23 числа инструкций, группу из и регистров 24 инструкций, первую группу элементов И 25 в составе н подгрупп, первую группу элементов ИЛИ 26 в составе трех подгрупп, регистр 27 операций, первый 28 и второй 29 дешифраторы признаков, вторую группу из 1 элементов И 30, регистры 31-33 соответственно входных, выходных и промежуточных переменных, 55 дешифраторы первого 34 и второго 35 адресов, третью 36 и четвертую 37 группы элементов И, вторую 38 и тре 146 2тью 39 группы из трех элементов ИЛИ,пятую 40 и шестую 41 группы элементов И, первый 42 и третий 42 элементы ИЛИ, первый 43 и второй 43элементы НЕ восьмую группу элементовИ 44, четвертую группу из четырехэлементов ИЛИ 45, второй элемент И 46.Блок 14 хранения номеров вычисляемых функций (Фиг,5) представляет собой двухступенчатый регистр, каждаяступень которого включает столькотриггеров, сколько ЛФ хранится в памяти устройства, и содержит первуюгруппу из т триггеров 47, первуюгруппу из вэлементов И 48, вторую группу из в элементов И 49, вторую группу из о триггеров 50, группу из го элементов 51 задержки, элемент ИЛИ 52, элемент 53 задержки.Блок 16 синхронизации (фиг.6)содержит генератор 54 импульсов,триггер 55, первый и второй элементыИ 56, элемент 57 задержки, генератор58 тактовых импульсов, первый и второй элементы НЕ 59 группу из десятиэлементов И 60,Устройство работает следующим образом.Алгоритм работы устройства основан на выполнении последовательностиопераций, обеспечивающей вычислениетолько тех логических Функций изСЛФ, в которые входят переменные,изменившие свои значения,Системы логических Функций, решаемые устройством, могут иметь вид У=х,(к, ),=1,п Ур И,1), Р = 1 рь, 3 = 1 п,где С- время начала выполнения очередного к-го шага решения уравнений; х - входные переменные; у - выходные переменные,Для определения решаемых на текущем шаге работы устройства логических функций необходимо фиксировать старые и новые состояния входных и выходных переменных, для чего вводятся векторы И и И.146 12 б 9 10 20 30 0-й 1-й 40 2-й 3-й и т.д. 3Значения элементов векторов Ис и Ч хранятся в разрядах регистров 4,5 и 2,3 соответственно. Векторы И и Ун состоят каждый из двух компонент: Ч =Х , Ус, Ин= 1.Хн, Ун 15 Изменение значений входных переменных Хн, поступивших в начале текущего шага, по отношению к входным переменным Хс, сохранившимся с предыдущего шага, а также изменение значений выходных переменных Ун, сформированных в конце предшествующего шага и переданных на текущий шаг, по отношению к выходным переменным У , хранящимся с предшествую щего шага (с момента передачи У =Ун на предшествующем шаге), определяет отличные от нуля значения элементов компонент Хиъы и Унзм Век тора й 1 = М;, 1 = 1,п+щ), Переменные, изменившие свои значения по отношению к предшествующим значениям, фиксируются единицами в разрядах регистров 10 и 11 и определяются по следующему правилу 25М, =ИВА, 1 =,1 п+щ. Выполнение операции суммирования по модулю два осуществляется в устройстве с использованием блоков 6 и 7 сумматоров по модулю два. Для определения номеров функций СЛФ, решаемых на текущем шаге, формируется матрица вхождения М-размерности и х и+ш. Элемент матрицы щра 3 вен 1, если в Лф для вычисления у, входит переменная х, 1 = 1,п или переменная у,; 1 = и+1, и+ш. В противном случае щ =О. Составленная таким образом матрица вхождений М хранится в блоке 12 памяти. Решаемые на текущем шаге логические уравнения определяются отличными от нуля элементами вектора решаемых урав- .ений й 1 Ы ,1 = 1,щ Вектор И определяется в результате выполнения операции И = М х Ин, которая в предлагаемом устройстве реализована. применением памяти ассоциативного типа, когда в блоке 12 50 зафиксированы ассоциативные признаки, соответствующие элементам матрицы вхождений М, и подача на вход блока 12. сигналов с выхода регистров изме-. ненных состояний входных 10 и выход ных 11 сигналов позволяет на выходе блока 12 получить значения элементов вектора Ч, которые фиксируются в блоке 14 хранения номеров вычисляемых функций. В соответствии сг определенными по приведенному правилу элементами вектора И, осуществляется последовательное вычисление ЛФ по определению значений у ,если УО,1При этом адрес вычисляемой ЛФ однозначно определяется номером разряда блока 14, для которого И, Ф О, В соот" ветствии с таким адресом вычисляемая функция из блока 13 памяти передается в блок 15 вычисления логических функций. После того, как вычисляются Лф, для которых,И Ф О, текущий шаг работы устройства завершается окончанием формирования нового слова выходной информации У, и устройство переходит на прием очередного нового слова входной информации Хн, Последовательность обработки информации по шагам с момента пуска устройства при он0 и наличии вычисляемых функций (случаи 1) 11 н = 0,2(Ун Ф О, вычисляемые функции отсутствуют - Б =О, не представляют интереса, так как уст- . ройство вновь обращается за входной информацией и подтверждает выходные сигналы до тех пор, пока не появляются изменения входной информации), можно представить таким образом: шаг: Х, Хс, У УсХныУИМ 11 1шаг 1) Х:= Хь, ьых:= й эХиыч:= Хн Ю Хс=Х,О,уньыуй с3) при Б =1, Х:= Х =Хсун ь4) при Б =1 вычисляем СЛФ21и формируем У;н, н Н, 1,шаг 1) Хн:=Хввы = н3) при Б=1 Хс Хн 1 Хьнсн э4) при Б =1 вычисляем СЛФ21,и формируем Ун ,111, 1 Ншаг 1) Хн:=Хь 11вы =,нЯ 1 Ц 13 ) при Б, = 1 Х с : = . Хн : Хь111. Н .с:= й;4) при Б =1 вычисляем СЛФи формируем унн имеют следующий смысл: Х 1 - входное слово, полученное в начале текущего,146 Ь 20 5 1269 (третьего) шага из внешней среды 11 111(Хь ); Хи - отражает изменение полученного значения Х" по отношению к значению Х", сохранившемуся с преды 11дущего шага; Уц - отражает изменение сформированного в конце предыдущего шага значения У по отношению к значению У, сохранившемуся с предыдущего шагау унш - выходное слово, сформированное в конце текущего шага, О которое в начале следующего шага , выдается во внешнюю среду как реакция на входное воздействие, поступившее в начале текущего шага.По сигналу Пуск запускается блок 15 16 синхронизации и начинает вырабатывать управляющие сигналы 1- 1, . Импульсом 1 устанавливаются в исходное состояние все блоки устройства - сбрасываются в нулевое состояние триггер 18 признака Я 4 триггеры первой.и второй ступени блока 14 хра,нения номеров вычисляемых функций, регистры входных и выходных сигналов в блоке 1 ввода-вывода, регистр 2 но вых значений входных сигналов, регистр 3 новых значений выходных сигналов, регистр 4 старых значений входных сигналов, регистр 5 старых значений выходных сигналов, первый 30 6 и второй 7 блоки сумматоров по модулю два, регистры измененныхсостояний входных 10 и выходных 11 сигналов, устанавливается в единичное состояние триггер 18 признака Я . В начале каждого нового шага в регистре 3 новых значений выходных сигналов записаны значения выходных сигналов, соответствующиеокончанию предшествующего шага, 40а в регистре 4 старых значений входных сигналов и в регистре 5 старых значений выходных сигналов - началу предшествующего шага.Если первый элемент ИЛИ 8 не зафиксирует изменений входных и (или)выходных сигналов, т.е. Я =О, ифесли на выходе второго элементаИЛИ 9 Я =О, то блок 16 синхронизации выдает управляющие сигналы 112 и 1 ь По сигналу 11 производится прием очередного нового словавходной информации в блок 1 вводавывода, Сигналом 1 осуществляетсяпередача входной информации из блока 1 ввода-вывода в регистр 2 новыхзначений входных сигналов и выходной информации из регистра 3 новых значений выходных сигналов в блок1 ввода-вывода. По сигналу 1 производится поразрядное сложение помодулю два содержимого регистров2 и 4 в первом 6 сумматоре по модулюдва и содержимого регистров 3 и 5 вовтором 7 сумматоре по модулю два,а также выдача иэ блока 1 ввода-вывода выходных сигналов, которые подт"верждают предыдущие сигналы,Если в результате вновь проиэве,денного сравнения выявляется изменение входных сигналов, на выходе первого элемента ИЛИ 8 появляется сигнал Я, =1. В этом случае блок 16 синхронизации вырабатывает сигнал 14,по которому производится передачапризнака иэ регистров 10 и 11 дляобращения к первому блоку 12 памяти,а из него на вход блока 14 храненияномеров вычисляемых функций выдаются номера функций, в которые входятпеременные, изменившие свои значения.,По сигналу 1 осуществляются передачасодержимого регистров 2 и 3 в регистры 4 и 5 соответственно и установкаЯ, =О. С первого выхода блока 14 информация о наличии вычисляемых функций поступает на входы второго элемента ИЛИ 9. При наличии вычисляемых функций на выходе второго элемента ИЛИ 9 появляется сигнал Я=1. Тогда очередной сигнал блока 16. синхронизации (сигнал 15) подается на управляющий вход блока 14. По этому сигналу с третьего выхода блока 14 выдается сигнал выборки функции из второго блока 13 памяти, а через второй выход блока 14:выдается разрешение на прием реэупьтата вычисления функции в тот разряд регистра 3, номер которого соответствует номеру вычис" ляемой функции. По сигналу 1, сбрасывается в "О" счетчик 21 инструкций в блоке 15 и передается содержимое регистров 2 и 5 устройства соответственно в регистры 31 и 32 в блоке 15 (фиг.3). Далее по сигналу 1,. устанавливается в "О" триггер 182- признака Я. Сигнал 1 производит прибавление единицы в младший разряд счетчика 21 инструкций в блоке 15. По сигналу 1 производится8опрос узла 20 сравнения в блоке 151передача инструкции, номер которойсоответствует числу в счетчике 21 и которая выбирается дешифратором 221269146 5 1 О 20 30 35 7номеров инструкций в блоке 15, на входы регистра 27 операций, дешифраторов первого 34 и второго 35 адресов в блоке 15 вычисления логических Функций (Фиг,2 и 3). Дешифратор 22 нОмеров инструкций выбирает также разряд в регистре 33 промежуточных переменных, номер которого соответствует номеру выбранной инструкции, для приема промежуточного результата.При отсутствии сигнала с выхода узла 20 сравнения. вырабатывается далее блоком 16 синхронизации сиг - нал 1 з, по которому заносится результат выполненной инструкции в подготовленный для приема разряд регистра 33 промежуточных переменных. В случае появления сигнала с выхода узла 20 сравнения устанавливаются в единичное состояние триггеры 18 и 18 признаков Я и Я, .и из блока 16 синхронизации выдается сигнал 1по которому заносится результат выполненной инструкции в подго товленный для приема разряд регистра 3 новых значений выходных сигналов устройства, а через соответствую. щие элементы задержки производится сброс триггера 18, признака Я и триггеров 47 второй ступени в блоке 14.Таким образом, до выдачи сигнала с узла 20 сравнения производится поочередное выполнение всех инструкций вычисляемой ЛФ. При выполнении последней инструкции выдается сигнал "Сравнение" с выхода узла 20 сравнения и результат попадает в регистр 3 новых значений выходных сигналов. Затем процесс вычисления СЛФ повторяется для очередной функции до тех пор, пока не будут вычислены все выбранные функции. Тогда признак Я =0 и ранее установленный признак 45 Ь, =0 переводят блок 16 синхронизации на выработку сигналов для приема очередного входного и выдачу полученного выходного слов. Останов устройства происходит при отключении питания. 8рых значений выходных сигналов, регистр старых значений входных сигналов, два блока сумматоров по модулю два, два элемента ИЛИ, регистр измененных состояний входных сигналов, регистр измененных состояний выходных сигналов, два блока памяти, блок хранения номеров вычисляемых функций, блок вычисления логических функций и блок синхронизации, причем информационные входы и выходы устройствасоединены с первыми группами соответственно входов и выходов блока вводда-вывода, вторая группа выходов которого подключена к информационным входам регистра новых значений входных сигналов, выходы которого соединены с первыми группами информационных входов блока вычисления логических функций и первого блока сумматоров по модулю два, а также с информационными входами регистра старыхзначений входных сигналов, выходы которого подключены к второй группеинформационных входов первого блока сумматоров по модулю два, выходыкоторого подключены к первой группевходов первого элемента ИЛИ и информационным входам регистра измененных состояний входных сигналов,выходы которого соединены с первойгруппой адресных входов первого блокапамяти, выходы которого соединеныс информационными входами блока хранения номеров вычисляемых функций,.первая группа выходов которого подключена к входам второго элемента ИЛИ, а вторая группа выходов соединена с входами синхронизации приемарегистра новых значений выходныхсигналов, выходы которого соединеныс второй группой входов блока вводавывода, первой группой информационных входов второго блока сумматоровпо модулю два и информационными входами регистра старых значений выходных сигналов, выходы которого соединены с второй группой информационныхвходов второго блока сумматоров помодулю два, выходы которого соединены.с второй группой входов первогоэлемента ИЛИ и информационными вхо55 Ф о р м у л а изобретенияУстройство для вычисления систем логических функций, содержащее блок ввода-вывода, регистр новых значений входных сигналов, регистр новых значений выходных сигналов, регистр стадами регистра измененных состояний выходных сигналов, выходы которого соединены с второй группой адресных входов первого блока памяти, третья группа выходов блока хранения номеров вычисляемых функций соединена9 12691 с адресными входами второго блока памяти, выходы которого соединены с второй группой информационных входов блока вычисления логических функций, информационный выход которого5 соединен с информационными входами регистра новых значений выходных сигналов, выходы первого элемента ИЛИ, второго элемента ИЛИ и первый, второй и третий управляющие выходы бло- щ ка вычисления логических Функций сое. динены соответственно с первого по пятый входами блока синхронизации, шестой вход которого соединен с входом запуска устройства, первый: выход блока синхронизации соединен с входами сброса блока ввода-вывода., регистра новых значений выходных сигналов, регистра новых значений входных сигналов, регистра старых значений входных сигналов, регистра старых значений выходных сигналов, регистра измененных состояний входных сигналов, регистра измененных состояний выходных сигналов, первого и второго 25 блоков сумматоров по модулю два, блока хранения номеров вычисляемых Функций и блока вычисления логических Функций, второй выход блока синхронизации соединен с входом синхронизации приема блока ввода-вывода, .третий выход блока синхронизации соединен с входом синхронизации приема 46 1 Орегистра новых значений входных сигналов и входами синхронизации выдачи блока ввода-вывода и регистра новых значений выходных сигналов, четвертый выход блока синхронизации соединен с входами синхронизации первого и второго блоков сумматоров по модулю/ два, пятый выход блока синхронизации соединен с входами синхронизации регистра старых значений входных сигналов, регистра старых значений выходных сигналов, регистра измененных состояний входных сигналов и регистра измененных состояний выходных сигналов, шестой выход блока синхронизации соединен с первыми входами синхронизации блока хранения номеров вычисляемых функций и блока вычисления логических Функцийс второго по шестой входы синхронизации которого соединены соответственно с седьмого по одиннадцатый выходами блока синхронизации, одиннадцатый выход которого соединен также с вторым входом синхронизации блока хранения номеров вычисляемых функций, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, выходы регистра старых значений выходных сигналов соединены с третьей группой информационных входов блока вычисления логических функций.-ПфнеЬчислена г.7 оставитель А, Чекановехред М. Ходанич Коррек И. Муска едактор шкина 671 Заказ 603ВН одписно ого комитета СССРений и открытийРаушская наб., д. 4/ прият Проектная,Ужгор Производственно-полиграфическое 8/52 Т ИИПИ Государствепо делам изобр 13035, Москва, Ж 557-Пф Ь числена,дучена пронежуточнаялеРененная,олуцено значение быкода сигнала.

СмотретьЗаявка

3514634, 26.11.1982

МОГИЛЕВСКИЙ МАШИНОСТРОИТЕЛЬНЫЙ ИНСТИТУТ

КУКЛИН ГРИГОРИЙ ВАСИЛЬЕВИЧ, ПАВУЧУК ВЛАДИМИР ПАВЛОВИЧ

МПК / Метки

МПК: G06F 17/16

Метки: вычисления, логических, систем, функций

Опубликовано: 07.11.1986

Код ссылки

<a href="https://patents.su/9-1269146-ustrojjstvo-dlya-vychisleniya-sistem-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления систем логических функций</a>

Предыдущий патент: Микропроцессорное вычислительное устройство

Следующий патент: Устройство для предварительной обработки операндов переменной длины

Случайный патент: Устройство для определения прочности и сцепления токопроводящих пленок с токонепроводящимоснованием