Устройство для контроля программируемых логических матриц

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

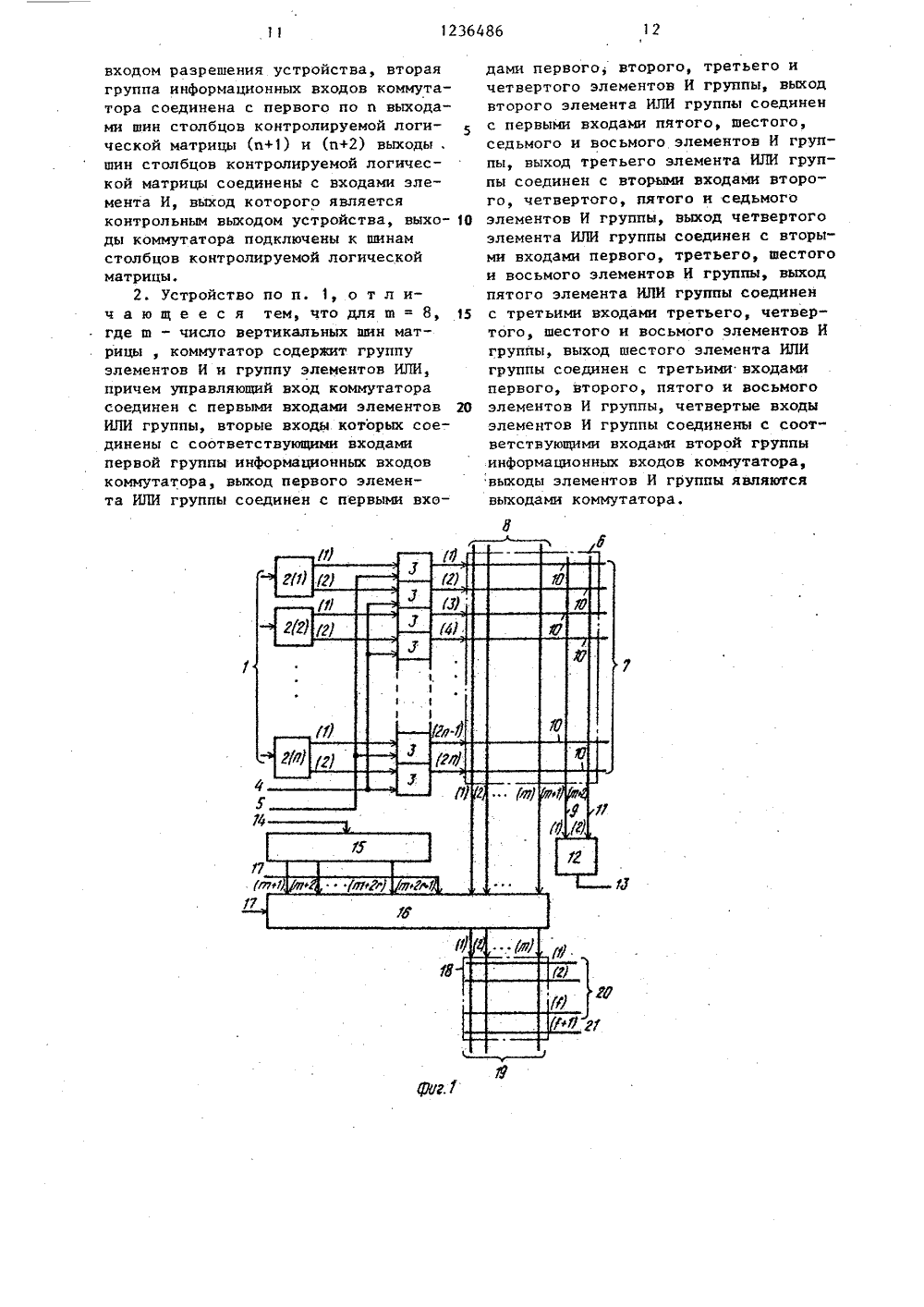

(51) 4 Р 11 2 ЕНИ ТВ о ысотем,Пуен 9 00 АРственный комитет ссс ЛАМ ИЗОбРЕТЕНИЙ И ОТНРЫТ ПИСАНИЕ ИЗ АВТОРСКОМУ СВИДЕТЕ(71) Институт проблем моделирования в энергетике АН УССР(56) Основы технической диагностики /Под ред. П,П,Пархоменко, М.: Энергия, 1976, с, 46411-йЬ 1 псегпаТ 1 опа 1 Бувровув оп Рао 1 С То 1 егап СоврпсЫ 87 цпе, 24-26, 1981, р. 44-46.(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПРОИИРУЕИЫХ ЛОГИЧЕСКИХ МАТРИЦ(57) Изобретение относится к цифрвычислительной технике и может бьиспользовано для проектирования вконадежных дискретных устройств.Цизобретения - повышение быстродейвия.устройства. Цель достигаетсячто в устройство, содержащее групдешифраторов, введены группа элемтов ИЛИ, коммутатор, элемент И. 1ф-лы, 5 ил, 12364Изобретение относится к цифровойвычислительной технике, в частностик вычислительным устройствам, содержашим некоторые вспомогательные элементы для обнаружения и определения 5местоположения неисправных элементовпутем выполнения вычислительной операции с заранее известным результатом, и может быть использовано дляпроектирования высоконадежных дискретных устройств, а именно быстродействующих устройств управления, которые могут быть использованы в любыхобластях народного хозяйства.Целью изобретения является повыше"ние быстродействия.На фиг. 1 приведена функциональнаясхема устройства, на фиг. 2 - схемакоммутаторами, на фиг. 3-5 - таблицытест-наборов Т 1, Т 2, ТЗ.20Устройство содержит вход 1 заданиятеста, группу 2 дешифраторов, группу 3 элементов ИЛИ, вход 4 разрешения контроля четных шин строк, вход 5разрешения контроля нечетных ванстрок, матрица 6 элементов И, шины 7строк матриц элементов И, шины 8столбцов матрицы элементов И, перваядополнительная шина 9, место 10 соединения шин строк и шин столбцов не- З 0выплавленными плавкими связями, вторая дополнительная шина 11, элемент И 12, контрольный выход 13 тактовый вход 14 устройства, счетчик 15,коммутатор 16, управляющий вход 17, З 5матрица 18 элемента ИЛИ, шины 19столбцов матрицы элементов ИЛИ, шины 20 строк матрицы элементов ИЛИ,выход 21 дополнительной шины матрицыэлементов И 3%, элементы ИЛИ 22, элементы И 23.Устройство работает следующим образом,В рабочем режиме на вход 17 подается сигнал, соответствующий значению логической единицы, который переключает коммутатор 16 в режим прямойпередачи информации с входа на выход.На вход 4 и на вход 5 подаются сигналы, соответствующие значению логнческого нуля, за счет чего сигналы навыходах блока 3 повторяют значениясигналов на его входах. Устройствоработает в следующей последовательности. На вход 1 подаются значения входных переменных х, дешифраторы входныхсигналов 2 (1)-2(п) Формируют прямыен инверсные значения сигналов входных 86 2переменных (х и х соответственно),Прямые и инверсные значения сигналоввходных переменных х поступают на 2 пвходов блока 3, Так как на входы разрешения контроля поданы сигналы, соответствующие логическому нулю, топрямые и инверсные значения сигналоввходных переменных х без измененияпоступают на выходы блока 3 и далеена шины 7, матрица 6 формирует шконьюктивных термов от прямых и инверсных значений входных переменных х,соответствующие шины 7 которых имеютневыплавленные плавкие связи.10 вточках пересечения с шинами столбцовматрицы 6. Значения полученных термовс шин 8 поступают на 1-е входы коммутатора 16, Так как на вход 17 подано значение сигнала, соответствующегологической единице, то значение термов, полученные в матрице 6, без изменений проходят на выходы коммутатора 16 и поступают на шины матри-.цы 18, которая формирует на выходах 20функции представляющие собой дизьюнкции тех коньюктивных термов, шины 19которых имеют невыплавленные плавкиесвязи 10 в точках пересечения с выходными шинами 20, т.е. устройствореализует систему булевых функций,состоящую из Г Функций, каждая изкоторых вычисляется в соответствиис формулой щ Г, = 7(Л х) рЭс М:1Э где Г, - -я выходная функция из системы булевых функций, реализуемойпредлагаемым устройством,номер функции в системе булевых функций, реализуемой предлагаемым устройством, (1=1,2Г),1." - число Функций в системе булевыхфункций, равное числу выходов матрицы 18,лх - парафазное значение к-й входной переменной,к - номер переменной х в коньюктивном терме, к = 1,2п;п - число входных переменных х,равное количеству входов 1 устройства;номер коньюктивного терма,входящего в Г функцию,ш - максимальное число коньюктивных терман, дизьюнкция которыхсоставляет функцию Г;, ш равно количеству вертикальных шин 8 матрицы 6.123 В тестовом режиме обнаружение неисправностей основного и дополнителього оборудования выполняется в следующей последовательности. Сначала подаем тест-набор Т 1 (фигЗ), х = 5е входные переменные (= 1,2п) подаются на 1-е входы 1 (1=1,2п) входная переменная Ч, - на вход 5, входная переменная У - на вход 4, входная переменная У - на вход 17, входная переменная У - на вход 14.После подачи теста А 1 из тест-набора Т 1 на всех шинах 7, если они исправны, устанавливается уровень напряжения, соответствующий значению 5 логической " 1" и, соответственно, на выходе элемента И 12 - также логическая1". Если хотя бы одна шина 7 имеет неисправность типа сопя 0, то значение сигнала на выходе элемента И 12 соответствует логическому "О".В результате подачи теста А 2 из тест набора Т 1, если шины 7 исправны, на нечетных шинах 7 устанавливается значение логической " 1", а на чет ных - значение логического "О" и на выходе элемента И 12 - значение логи - ческого "О". Значение сигнала на выходе элемента И 12, соответствующего логической "1", обнаруживает кратную 30 неисправность типа "четные шины 7 имеют неисправности сопзй "1".При подаче теста АЗ из тест-набора Т 1, если шины 7 исправны, на них устанавливается значение логической " 1" и на выходе элемента И 12 - также логической " 1", В случае наличия одиночнойлибо кратной неисправности типа сопя "О" шин 7 на выходе элемента И 12 устанавливается значение 4 о логического "О"..При подаче теста А 4 из тест-набо-, ра Т 1, если шины 7 исправны, на них устанавливается значение логической "1" и на выходе элемента И 12 - так же логическая "1". В случае наличия одиночной либо кратной неисправности типа сопз "О" шин 7 на выходе элемента И 12 устанавливается значение логического "О".50При подаче теста А 5 из тест-набора Т 1, если шины 7 исправны, на нечетных шинах устанавливается значение логического О, а на четных - значение логической "1" и на выходе 55 элемента И 12 - значение сигнала, соответствующего логическому "О". Значение сигнала на выходе элемента И 12 1 О 6486 4соответствующее логической "1", указывает на наличие кратной неисправности типа "все нечетные шины 7 имеют неисправности сопзй "1".При подаче теста А 6 из тест-набора Т 1, если шины 7 исправны, на нихустанавливается значение логической"1" и на выходе элемента И 12 - также логическая . Если одна или несколько шин 7 имеют неисправность типа сопз "О", на выходе элементаИ 12устанавливается значение логического "О".Таким образом, на контрольном выходе 13 (выходе элемента И 12) приподаче тест-набора Т 1 обнаруживаютсявсе неисправности типа сопвй "0",неисправность "четные шины 7 имеютнеисправность типа сопзС , неисправность "нечетные шины 7 имеют неисправность типа сопз "1", другиенеисправности типа сопз "1" обнаруживаются на тест-наборе ТЗ.Для работы устройства в матрицуИ 6 должны быть введены две дополнительные шины столбцов, так как в одной шине нельзя оставлять невыправленными плавкие связи одновременнов 1 и в (+1)-й шинах 7 (1=1,3,5,7): в каждом коньюкторе шины 7.матрицы И состояние плавких перемычек может быть одним из трех - перемычка 1 расплавлена, перемычка (+1)расплавлена, перемычкии (+1) расплавлены. В матрице 18 ИЛИ ограничений на состояние плавких перемычекв одной шине нет.Для наглядности возьмем программируемую логическую матрицу небольших размеров: с числом входов п=5,термов ш=8, выходов Г = 2,Подача на шины 19 матрицы 18 ИЛИтест-.набора Т 2 (фиг. 4) заявки организуется путем переключения счетчика 15 последовательно в состояниясоответствующие двоичному значениючисел 1-8 и организацией связей междуэлементами ИЛИ 22 и элементами И 23в коммутаторе 16 (фиг. 3, "О"),Организация связей между элементами ИЛИ 22 и элементами И 23 выполняется в соответствии с формулойМ, =2 К+Ргде И; - номера элементов И группы,входы которых соединены с выходом.д-гоэлемента ИЛИ группы,Р2 К - количество элементов Игруппы, подключенных к выходу -го( - 1) - для нечетных элементов2группы ИЛИ, С - относительный номерэлемента И группы в расчетной группе К; г = 0,1,2, , (2 - 1) дляр=О, С =О,дляр= 1,=О, 1 5для р = 2, г = 0,1,2,3 и т,д.).При подаче тест-набора Т 2 на выходе 21 при исправном счетчике 15получается последовательность иэ шсигналов, соответствующих значению 2 Ологической " 1". В случае наличия неисправности типа сопзг "О" какого-либо разряда счетчика 15 в этой выходной последовательности появляютсясигналы, соответствующие логическоПри подаче тест-набора Т 2 в случаеотсутствия в счетчике 15 неисправностей типа сопвГ "0" на выходе 21 наблюдают последовательность из восьми 30единиц: 1 1 1 1 1 1 1 1. При наличиинеисправности типа сопзг 0 первоговыхода счетчика 15 (прямой выход первого разряда) на выходе 21 наблюдаютпоследовательность: О 1 0 1 0 1 0 1, 35при наличии неисправности типа сопят"О" второго выхода счетчика 15 (ин -версный выход триггера первого разряда) на выходе 21 наблюдают последовательность: 1 О 1 О 1 0 1 О; при Юаналогичной неисправности третьеговыхода счетчика - последовательность:1 0 О 1 1 0 О 1; при аналогичной неисправности четвертого выхода счетчика - последовагельность: 01 1 0 0 1 1 0 45при аналогичной неисправностипятого вьиода счетчика - последова. -тельность; 1 1О О 0 0 1, прианалогичной неисправности шестого выхода счетчика - последовательность: 5 О000111.10. Таким образом, при подаче тест- набора Т 2 на выходе 21 обнаруживаются все неисправности счетчика 15 55 типа сопзС "0", неисправности типа сопят "1" обнаруживаются на выходах 20 устройства. Пусть данное контролепригодное программируемое логическое устройство в рабочем режиме реализует систему булевых Функций Г - х х, х х х 4 ч х х хчх,х 7 хх,х,;Е - ххх тххх чххчххугЧх,х хЕсли в устройстве отсутствуют неисправности, то при тестировании егоуниверсальным тест-набором наблюдаютследующие последовательности значений сигналов на выходах устройства.На выходе 13: при подаче Т 1 наблюдают последовательность 101101, приподаче Т 2 - последовательность111111111 при подаче ТЗ - последовательность из 80 нулей (для каждоготеста В из тест-набора Т 2 подаетсявесь тест-набор ТЗ - 10 тестов).На выходах 20 (1). при подаче Т 1наблюдают последовательность 111000,при подаче Т 2 - последовательность110101 О при подаче ТЗ для В, изТ 2 (обозначим ТЗ В) - последовательность 0101011111 при подачеТЗ В - последовательность 0111100111при подаче ТЗ Б - 0000000000, приподаче ТЗ Б - последовательность0110111110; при подаче ТЗ Б 0000000000 при подаче ТЗ Б11110 11110; при подаче ТЗ В0110111011, при подаче ТЗ В0000000000,На вьиодах 20 (2); при подаче Т 1наблюдаем последовательность 111101,при подаче Т 2 - 10 101101, при подаче ТЗ В, - 0101011111, при подаче ТЗ Б - 0000000000; при подачеТЗ В - 1001111101, при подаче ТЗ В0000000000, при подаче ТЗ В111100111; при подаче ТЗ Б1111011110, при подаче ТЗВ0000000000, при подаче ТЗ 3101110110.1На выходе 21: при подаче Т 1111101", при подаче теста Т 211111111, при подаче ТЗ В,010101111, при подаче ТЗ Б011100111; при подаче ТЗ Вз1001111101; при подаче ТЗ В 4,0110111110, при подаче ТЗ В111 О 10111; при подаче ТЗ В1111011110, при подаче ТЗ В -О 10111011; при подаче ТЗ Б1011110110.Списки нулей и единиц дают следующую информацию: на тест-наборе Т 2 таблицу связей матрицы 18 ИЛИ (единица в списке указывает на наличие невыплавленной плавкой связи 10), на тест-наборе ТЗ - таблицы связей матриц И 6 и ИЛИ 18 (если при подаче ТЗВ в списке все нули, то связь1в матрице 18 ИЛИ в точке пересечения О 1-й вертикальной шины 19 матрицы ИЛИ с рассматриваемой выходной шиной 20 (3) отсутствует, если список состоит из нулей и единиц, то такая связь имеется, а в матрице 6 и на -и вертикальной шине 8 матрицы И невыплавленные плавкие связи 10 имеются в точточках пересечения с промежуточнымгоризонтальными шинами 7, номера которых соответствуют номерам нулей всписке,Рассмотрим списки на выходе 20( 1),На наборе Т 2 единицы указывают наналичие невыплавленных плавких свя 25зей 10 в матрице 18 ИЛИ в точках пересечения выходной горизонтальнойшины 20 ( 1) с первой, второй, четвертой, шестой и седьмой вертикальными шинами 19 матрицы ИЛИ. При подаче ТЗ В, ТЗ Ви ТЗВ 8 - в спискахна выходе 20 (1) все нули, следовательно, в матрице 18 ИЛИ невыплавленных плавких связей 10 нет в точкахпересечения первой шиной 20 (1) стретьей, пятой и восьмой вертикальны-З 5ми шинами 19 матрицы ИЛИ, т.е. естьтакие связи в точках пересечения первой шиной 20 (1) с первой, второй,четвертой, шестой и седьмой вертикальными шинами 19 матрицы (термы 40функции Г, системы булевых функций(1) реализованы на первой, второй,четвертой, шестой и седьмой вертикальных шинах 8 матрицы И) - информациясовпадает с полученной на тест-набаре Т 2 и описанному выше. Наличие нулей в списках при подаче ТЗВ ТЗ В,гфТЗ В 4, ТЗ В, ТЗ В указывает на на. личие невыплавленных плавких связей 10 в матрице 6 И соответственно 50первой, второй, четвертой, шестой иседьмой вертикальных шинах .8 матрицы И, Например, при подаче ТЗВ,список на выходе 20 (1) имеет видО 01011111. Это означает, что на пер вой вертикальной шине 8 матрицы Иневыплавленные лавкие связи, 10 имеются в точках пересечения с первой,третьей и пятой шинами 7; при подаче ТЗ В список имеет вид: 0111100111. Это означает, что на второй вертикальной шине 8 матрицы И имеются не- выплавленные плавкие связи 10 в точках пересечения с первой, шестой и седьмой шинами 7.Рассмотрим как меняются спискипри наличии неисправностей в устройстве. Допустим в результате тестирования получены следующие списки на выходах устройства.На первом дополнительном выходе 13: при Т 1 - 000000, при Т 2 - 00000000, при ТЗ - 80 нулей.На выходе 20 ( 1): при Т 1 - 111000, при Т 2 - 00000100, ТЗ В, - ОООООООООО,ТЗ Вг - 000000000, при ТЗ В - 000000000, при ТЗ В 4 - 0000000000, при ТЗ В - 0000000000, при ТЗ В 1111011110, при ТЗ В - 0000000000, при ТЗ В 0000000000.На выходе 20 (2): при Т - 111101, при Т 2 - 00101101, при ТЗ В0000000000, при ТЗ В г - 0000000000, при ТЗВ. - 001111101, при ТЗ В - 0000000000, при ТЗф В - 1111010111, при ТЗ В - 1111011110, при ТЗ Вт - 0000000000, при ТЗВв - 1011110110.На выходе 21: 11101 - при подаче Т 1, при Т 2 - 00101101, при ТЗ В0000000000, при ТЗ Вг - 0000000000, при ТЗ В - 100111 101, при ТЗ В 4 0000000000, при ТЗВ 5 - 111010111, при ТЗ В 6 - 1111011110, при ТЗ В 0000000000, при ТЗ В - 1011110110.Сравнение списков на выходах исправного и неисправного устройств позволяет сделать следующие выводы.Одновременное изменение 1 и 0 в списках выхода 13 на тест-наборах Т 1 и Т 2, в списках выхода 20 (1) на тест-наборах Т 2, ТЗВ ТЗ В, ТЗ В 4, ТЗВ 7, в списках выхода 20 (2) на тест в набор Т 2, ТЗВ, в списках выхода 21 на тест-наборах Т 2, ТЗ В, ТЗ В, ТЗ В 4, ТЗ В свидетельствует о наличии в устройстве неисправности тика сопяТ "0", связанной с первой, второй, четвертой, седьмой вертикальными шинами 19 матрицы ИЛИ и одновременно влияющей на выход 13. Такой неисправностью может быть только неисправность типа сока "0" первой шины 7, так как только первая шина 7 связана и с выходом 13, и с первой, второй, четвертой, седьмой вертикаль 1236486 10ными шинами 9 матрицы ИЛИ (через коммутатор 16) .Второй внешний дополнительный вход 5, элемент 3 (1) ИЛИ, дешифратор 2 (1) входных сигналов и первый основной вход устройства через первую шину 7 также связаны с выходом 13 и с 1, 2, 4, 7-й вертикальными шинами 19 матрицы ИЛИ. Но неисправность 1 О типа сапами "0" любого из перечисленного оборудования дала бы другие списки. Так, неисправность типа сопзТ "0" входа 5 на первом тесте из тест-набора Т 1 дала бы логический "О" на выходе 20 (2), а в нашем случае в списке выхода 20 (2) при подаче тесь боара Т 1 на первом месте стоит логическая "1". Неисправность сопзй "0" входов-выхода группы 3 элементов ИЛИ 2 О (1), входа-выхода дешифратора 2 (1) входных сигналов, первого основного входа устройства на выходе 13 в списках тест-набора Т 1 уже на первом тесте из Т 1 дала бы 1, а не О, как в 25 нашем случае.Затем подачей сигналов, соответствующих логической единицы на вход 14, устанавливают на шинах 19 столбцов значения сигналов соответствующие ЗО тесту В 1 из тест-набора Т 2 (фиг, 4) и подают все 2 п тестов тест-набора ТЗ (фиг, 5).Затем подачей сигналов, соответствующих логической единице на вход 14,З 5 устанавливают на шинах 19 столбцов значения сигналов, соответствующие тесту В 2 из тест-набора Т 2 и подают все 2 п тестов тест-набора ТЗ, затем устанавливают на шинах 19 столбцов 4 О значения сигналов, соответствующие тесту ВЗ иэ тест-набора Т 2 и подают все 2 п тестов иэ тест-набора ТЗ и т,д, Наблюдая реакции на 2 пв тестов обнаруживают неисправности матрицы 6 на первом контрольном выходе 13, а неисправности матрицы 18 - на втором контрольном выходе 21 и на основных выходах логической матрицы, так как в тест-наборе Т 2 только одна Ь, -я 5 О переменная ( 1,2,в), подаваемая на соответствующую шину 19 =1,2. . .в) столбцов, имеет значение, соответствующее логической единице,ледовательно, только одна шина 19 55 возбуждена. Входные переменные Х, (1.=1,2в) подаются на входы 1, входная переменная У подается навход 5, входная переменная Уподается на вход 4, переменная С, (х=1,2,,2 п) получается на выходе группы 3 элементов ИЛИ и подается на1-ю шину 7 (1=1,2 2 п) (фиг. 5).Тест-последовательность логического устройства не зависит от реализуемой в рабочем режиме системы булевыхфункций, длина тест-последовательности зависит только от величины ш и п,т.е. от количества шин столбцов матрицы 8 и количества входов 1 соответственно и определяется по формуле8 т + 8 + 8 т 1 8 т 6+в+т т т 1 т+ 2 п в,где Я - длина тест-последовательностти логического устройства,Б - количество тестов в тестг,наборе т 1,Я - количество тестов в тестт.наборе Т 2,Б, - количество тестов в тесттЗнаборе ТЗ;в - количество вертикальныхшин 8,и - количество входов 1. Формула изобретения1. Устройство для контроля программируемых логических матриц, содержащее группу дешифраторов, входы которых являются входами задания теста устройства, о т л и ч а ю - щ е е с я тем, что, с целью повыше ния быстродействия, в него введены счетчик, группы элементов ИЛИ, коммутатор, элемент И, причем первые выходы дешифраторов группы соединены с первыми входами нечетных элементов ИЛИ группы, вторые входы которых соединены с входом разрешения контроля нечетных шин строк контролируемой логической матрицы, вторые выходы дешифраторов группы соединень,с первыми входами четных элементов ИЛИ группы вторые входы которых соединены с входом разрешения контроля четных шин строк контролируемой логической матрицы, выходы элементов ИЛИ группы подключены к шинам строк контролируемой логической матрицы, счетный вход счетчика соединен с тактовым входом устройства, группа выходов счетчика соединена с первой группой информационных входов коммутатора, управляющий вход которого являетсявходом разрешения устройства, втораягруппа информационных входов коммутатора соединена с первого по и выходами шин столбцов контролируемой логической матрицы (и+1) и (и+2) выходы,шин столбцов контролируемой логической матрицы соединены с входами элемента И, выход которого являетсяконтрольным выходом устройства, выходы коммутатора подключены к шинамстолбцов контролируемой логическойматрицы,2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что для ш = 8, 15где ш - число вертикальных шин матрицы , коммутатор содержит группуэлементов И и группу элементов ИЛИ,причем управляющий вход коммутаторасоединен с первыми входами элементов 20ИЛИ группы, вторые входы которых соединены с соответствующими входамипервой группы информационных входовкоммутатора, выход первого элемента ИЛИ группы соединен с первыми входами первого; второго, третьего ичетвертого элементов И группы, выходвторого элемента ИЛИ группы соединенс первыми входами пятого, шестого,седьмого и восьмого элементов И группы, выход третьего элемента ИЛИ группы соединен с вторыми входами второго, четвертого, пятого и седьмогоэлементов И группы, выход четвертогоэлемента ИЛИ группы соединен с вторыми входами первого, третьего, шестогои восьмого элементов И группы, выходпятого элемента ИЛИ группы соединенс третьими входами третьего, четвертого, шестого и восьмого элементов Игруппы, выход шестого элемента ИЛИгруппы соединен с третьими входамипервого, второго, пятого и восьмогоэлементов И группы, четвертые входыэлементов И группы соединены с соответствующими входами второй группыинформационных входов коммутатора,выходы элементов И группы являютсявыходами коммутатора.1236486 Тес% ииБЮ ТГ тавитель С,Стремин Ред М.Ходанич Кор ор В.Бутяга Т Волкова Редакт.Тираж 671сударственного комитета СССам изобретений и открытийосква, Ж, Раушская наб.,одписное аказ 3092/52 ВНИИПИ по д13035,4/ оизводственн играфическое предприятие, г.ужгород, ул.Проектная, 4

СмотретьЗаявка

3654176, 11.10.1983

ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ГУЛЯЕВ ВАСИЛИЙ АНАТОЛЬЕВИЧ, БАБИЧ ЛИДИЯ ИВАНОВНА

МПК / Метки

МПК: G06F 11/26

Метки: логических, матриц, программируемых

Опубликовано: 07.06.1986

Код ссылки

<a href="https://patents.su/9-1236486-ustrojjstvo-dlya-kontrolya-programmiruemykh-logicheskikh-matric.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля программируемых логических матриц</a>

Предыдущий патент: Устройство для контроля схем сравнения

Следующий патент: Устройство для контроля хода программы

Случайный патент: Устройство для исследования влажных образцов в растровом электронном микроскопе