Устройство контроля микропроцессорных блоков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

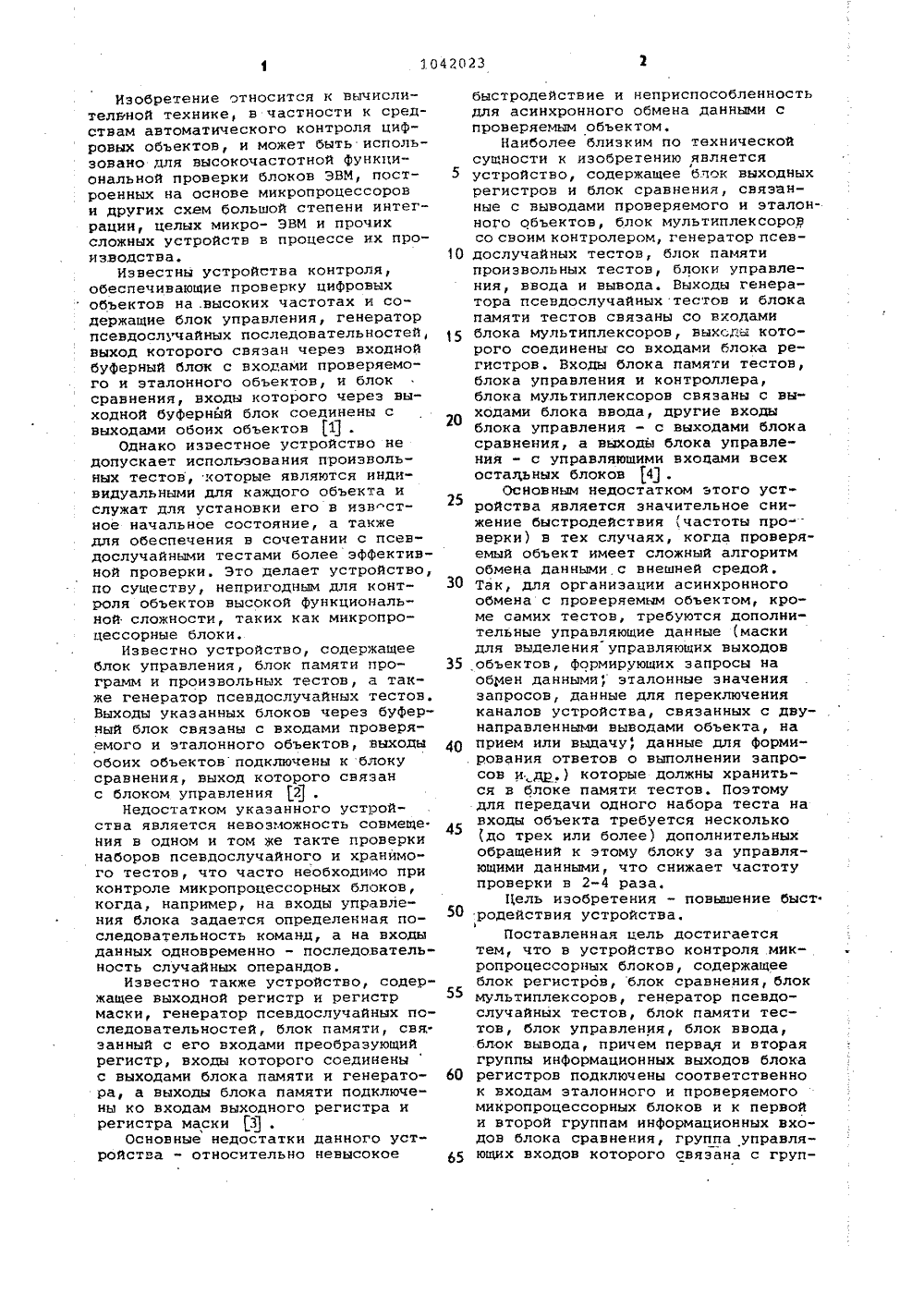

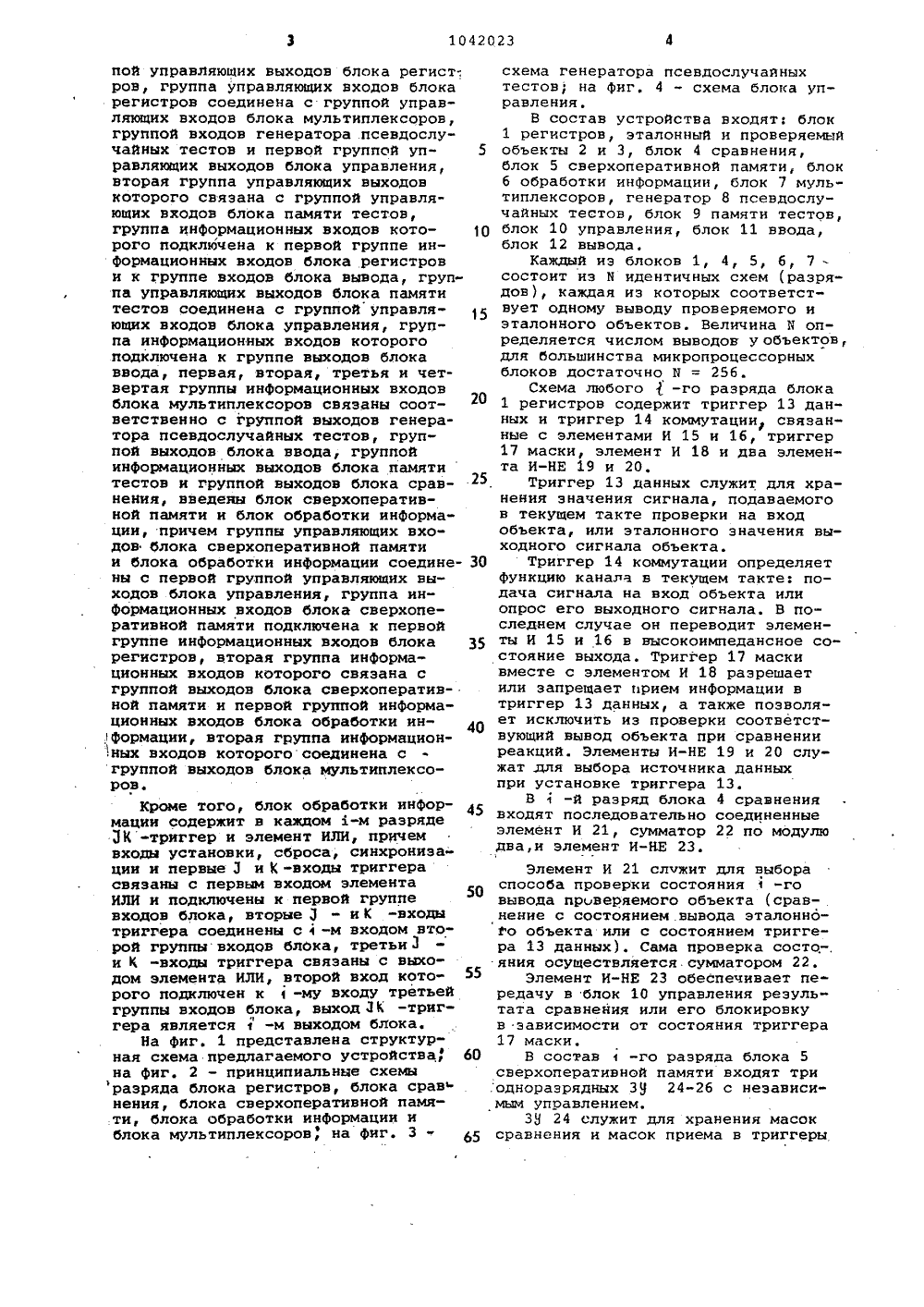

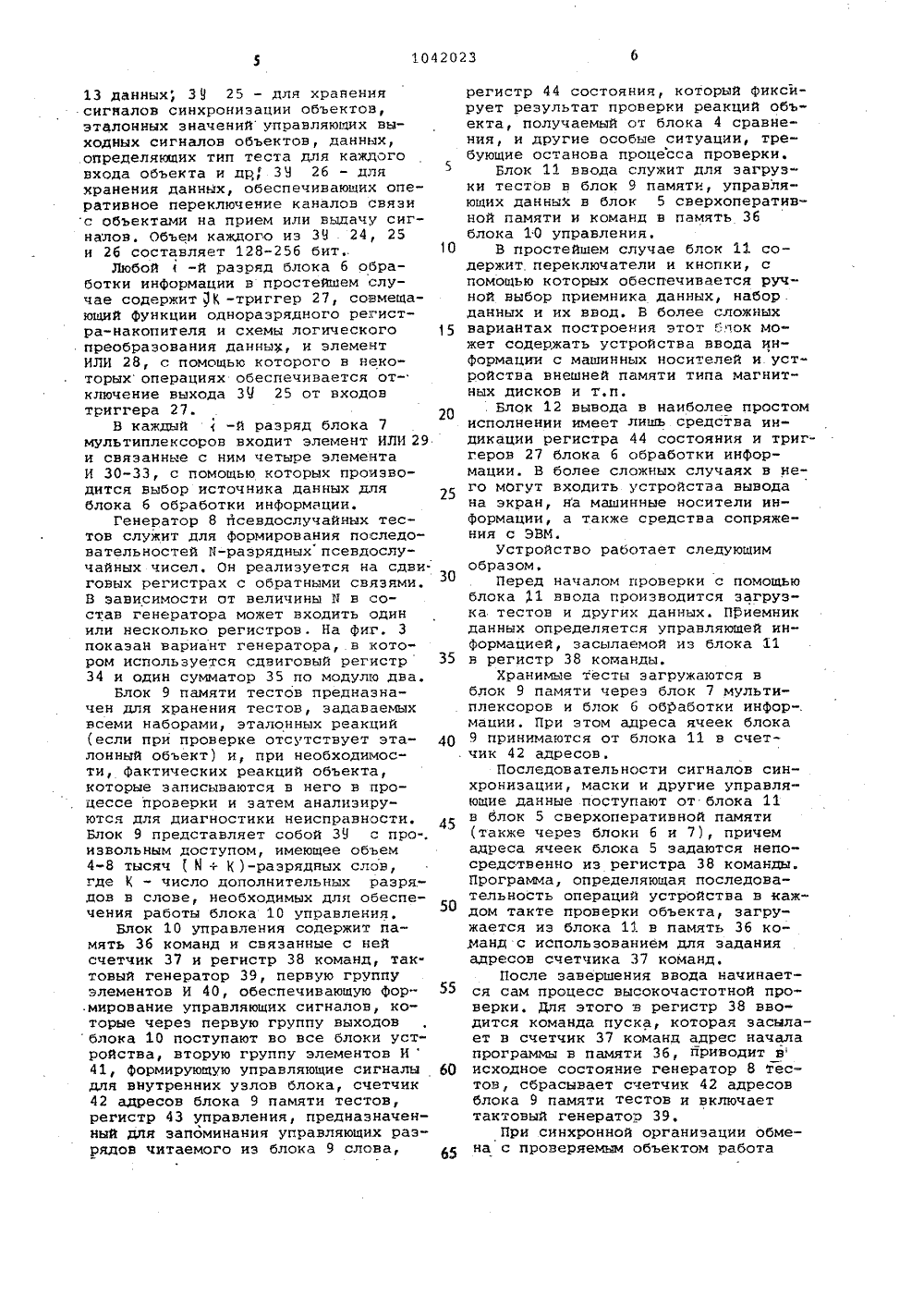

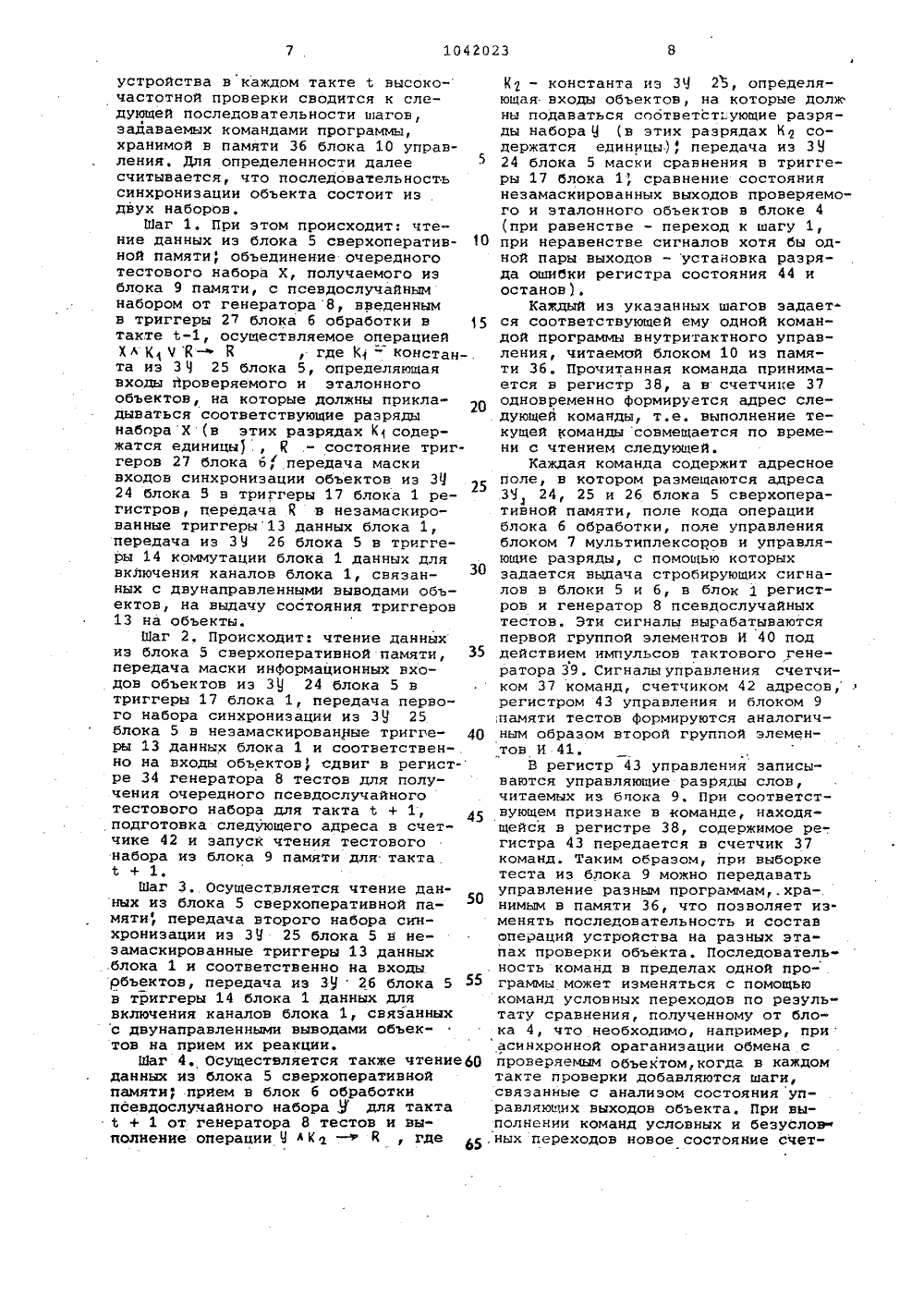

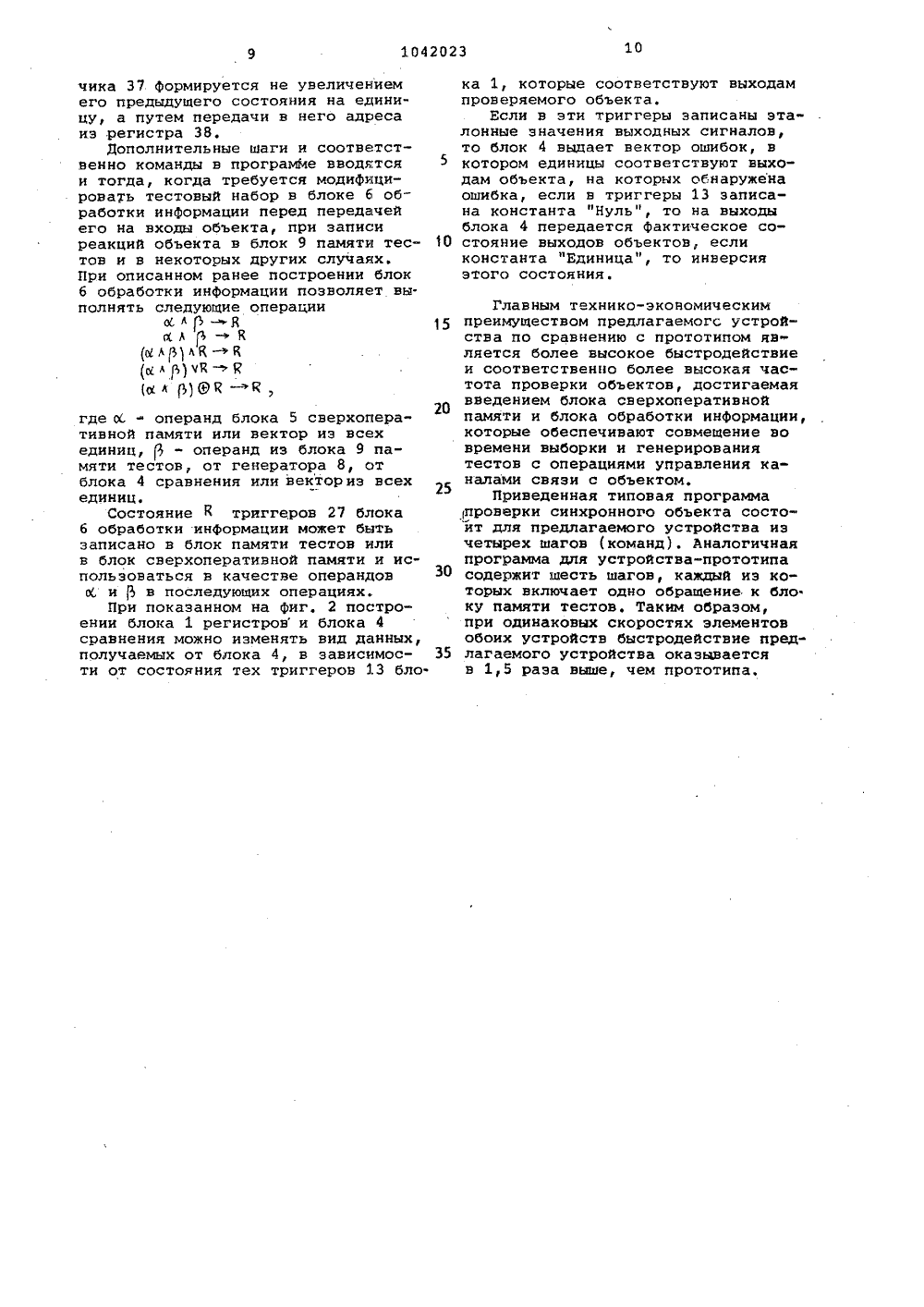

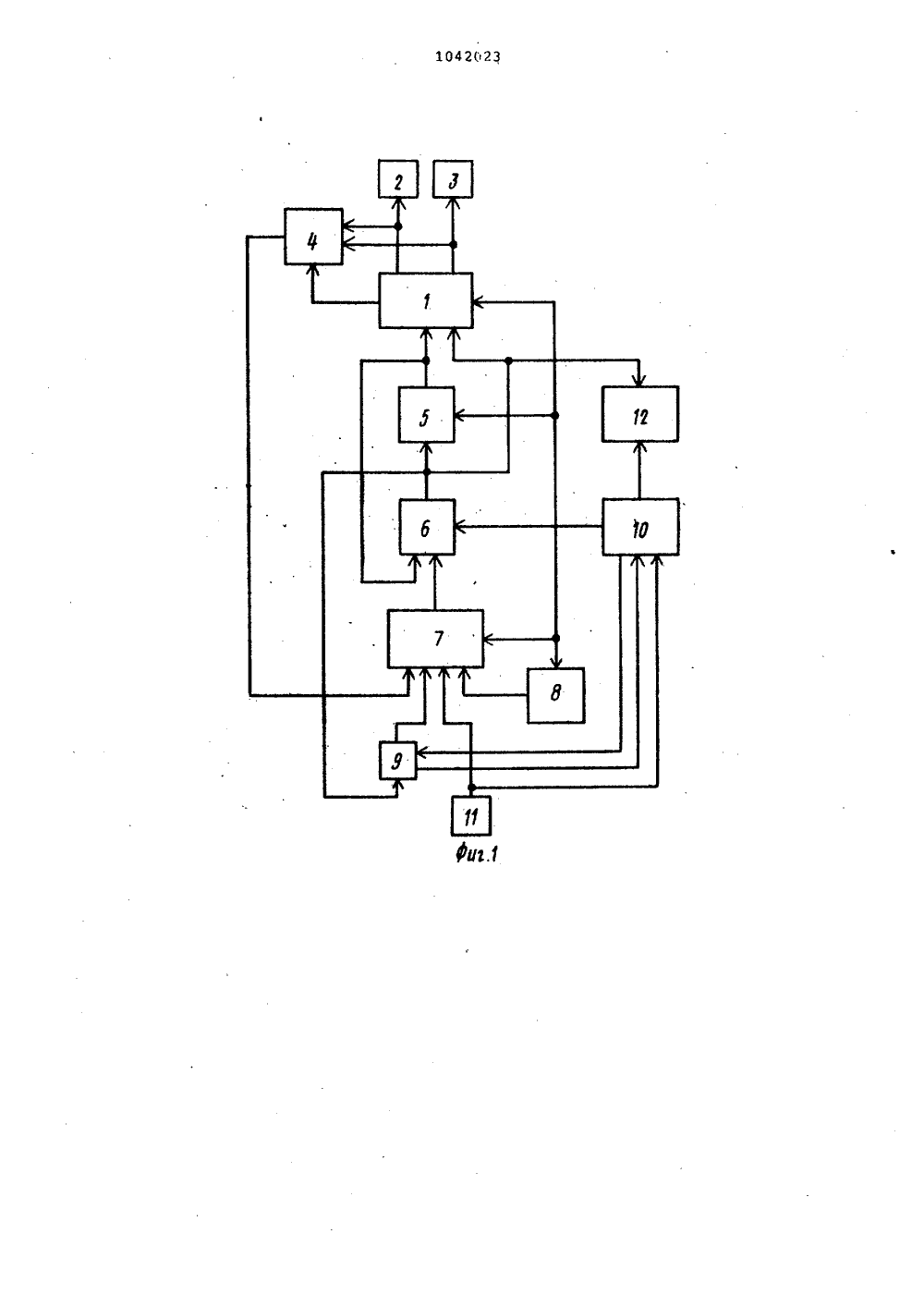

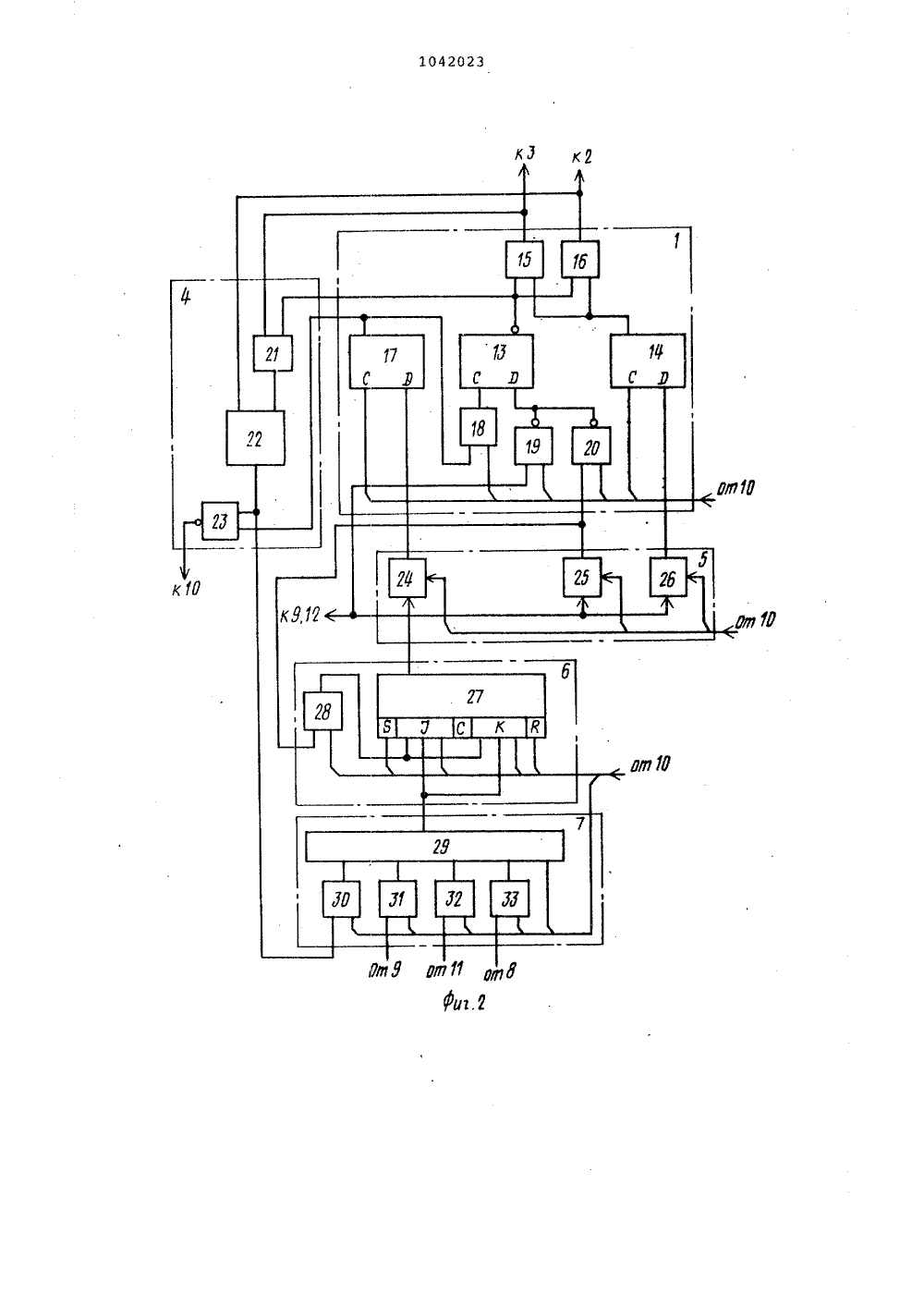

(51) Я ИСАНИЕ ИЗОБРЕТ Бюл.ев,СССР974. СССР памяра ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(71) Институт электронных управляющих машин(54)(57) 1. УСТРОЙСТВО КОНТРОЛЯМИКРОПРОПЕССОРНЫХ БЛОКОВ, содержащее блок регистров, блок сравнения,блок мультиплексоров, генераторпсевдослучайных тестов, блок памятитестов, блок управления, блок ввода,блок вывода, причем первая и втораягруппы информационных выходов блокарегистров подключены соответственнок входам эталонного и проверяемогомикропроцессорных блоков и к первойи второй группам информационныхвходов блока сравнения, группа управляющих входов которого связанас группой управляющих выходов блокарегистров, группа управляющих входовблока регистров соединена с группойуправляющих входов блока мультиплексоров, группой входов генераторапсевдослучайных тестов и первой группой управляющих выходов блока управления, вторая группа управляющих выходов которого связана с группой управляющих входов блока памяти тестов,группа информационных входов кото, рого подключена к первой группе информационных входов блока регистрови к группе входов блока вывода, группа управляющих выходов блока титестов соединена с группой уп вляЯО 1 Щ 2923. А ющих входов блока управления, группа информационных входов которого подключена к группе выходов блока ввода, первая, вторая, третья и четвертая группы информационных входов блока мультиплексоров связаны соответственно с группой выходов генератора псевдослучайных тестов, группой выходов блока ввода, группой информационных выходов блока памяти тестов и группой выходов блока сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в устройство введены блок сверхоперативной памяти и блок обработки информации, причем группы управляющих входов блока сверхопеФ ративной памяти и блока обработки информации соединены с первой груп- рр пой управляющих выходов блока управ- %Ф Р ления, группа информационных входов Св блока сверхоперативной памяти подключена к первой группе информационных входов блока регистров, вторая Е группа информационных входов которого связана с группой выходов блока сверхоперативной памяти и первой группой информационных входов блока обработки информации, вторая группа инфор мационных входов которого соединена с группой выходов бло:а мультиплексоров.2; Устройство по и. 1, о т л и- ч а ю щ е е с я тем, что блок обработки информации содержит в каждом 1 -м разряде ЭК -триггер и элемент ИЛИ, причем входы установки, сброса, синхронизации и первые 3 и-входы триггера связаны с первым входом элемента ИЛИ и подключены к первой группе входов блока, вторые 3 - и К -входы триггера соединены с-м входом второй группы входов блока, третьи ) - и К -входы триггера связаны с выходом элемента ИЛИ, второй вход которого подключен к 1 -му входу третьей группы входов блока, выход 3 К -триггера являетсяИзобретение относится к вычислительной технике, в частности к средствам автоматического контроля цифровых объектов, и может быть использовано для высокочастотной функциональной проверки блоков ЭВМ, построенных на основе микропроцессорови других схем большой степени интеграции, целых микро- ЭВМ и прочихсложных устройств в процессе их производства.Известны устройства контроля,обеспечивающие проверку цифровыхобъектов на .высоких частотах и содержащие блок управления, генераторпсевдослучайных последовательностей,выход которого связан через входнойбуферный блок с входами проверяемого и эталонного объектов, и блоксравнения, входы которого через выходной буферный блок соединены свыходами обоих объектов Ц .Однако известное устройство недопускает использования произвольных тестов, которые являются индивидуальными для каждого объекта ислужат для установки его в известное начальное состояние, а такжедля обеспечения в сочетании с псевдослучайными тестами более эффективной проверки. Это делает устройство,по существу, непригодным для контроля объектов высокой функциональной сложности, таких как микропроцессорные блоки,Известно устройство, содержащееблок управления, блок памяти программ и произвольных тестов, а также генератор псевдослучайных тестов,Выходы указанных блоков через буферный блок связаны с входами проверяемого и эталонного объектов, выходыобоих объектовподключены к блокусравнения, выход которого связанс блоком управления 12Недостатком укаэанного устройства является невозможность совмеще.ния в одном и том же такте проверкинаборов псевдослучайного и хранимого тестов, что часто необходимо приконтроле микропроцессорных блоков,когда, например, на входы управления блока задается определенная последовательность команд, а на входиданных одновременно - последовательность случайных операндов.Известно также устройство, содержащее выходной регистр и регистрмаски, генератор псевдослучайных последовательностей, блок памяти, связанный с его входами преобразующийрегистр, входы которого соединеныс выходами блока памяти и генератора, а выходы блока памяти подключены ко входам выходного регистра ирегистра маски 13) .Основные недостатки данного устройства - относительно невысокое быстродействие и неприспособленностьдля асинхронного обмена данными спроверяемым объектом.Наиболее близким по техническойсущности к изобретению является5 устройство, содержащее блок выходныхрегистров и блок сравнения, связанные с выводами проверяемого и эталонного объектов, блок мультиплексоровсо своим контролером, генератор псев 10 дослучайных тестов, блок памятипроизвольных тестов, блоки управления, ввода и вывода, Выходы генератора псевдослучайных тестов и блокапамяти тестов связаны со входамиблока мультиплексоров, выходы которого соединены со входами блока регистров. Входы блока памяти тестов,блока управления и контроллера,блока мультиплексоров связаны с выходами блока ввода, другие входыблока управления - с выходами блокасравнения, а выходы блока управления - с управляющими входами всехостальных блоков 4) .Основным недостатком этого устройстэа является значительное снижение быстродействия (частоты про".верки) в тех случаях, когда проверяемый объект имеет сложный алгоритмобмена данными,с внешней средой,30 так, для организации асинхронногообмена с проверяемым объектом, кроме самих тестов, требуются дополнительные управляющие данные (маскидля выделения управляющих выходов35 объектов, формирующих запросы наобмен данными," эталонные значениязапросов, данные для переключенияканалов устройства, связанных с двунаправленными выводами объекта, наприем или выдачу данные для форми. рования ответов о выполнении запросов и др,) которые должны храниться в блоке памяти тестов. Поэтомудля передачи одного набора теста навходы объекта требуется несколько(до трех или более) дополнительныхобращений к этому блоку за управляющими данными, что снижает частотупроверки в 2-4 раза.Пель изобретения - повышение быст.50 родействия устройства,Поставленная цель достигаетсятем, что в устройство контроля микропроцессорных блоков, содержащееблок регистров, блок сравнения, блокмультиплексоров, генератор псевдослучайных тестов, блоК памяти тестов, блок управления, блок ввода,блок вывода, причем первая и втораягруппы информационных выходов блока60 регистров подключены соответственнок входам эталонного и проверяемогомикропроцессорных блоков и к первойи второй группам информационных входов блока сравнения, группа управля 65 ющих входов которого связана с груп 1042023пой управляющих выходов блока регнст ров, группа управляющих входов блока регистров соединена с группой управляющих входов блока мультиплексоров, группой входов генератора псевдослучайных тестов и первой группой управляющих выходов блока управления, вторая группа управляющих выходов которого связана с группой управляющих входов блока памяти тестов, группа информационных входов которого подключена к первой группе информационных входов блока регистров и к группе входов блока вывода, груп па управляющих выходов блока памяти тестов соединена с группой управляющих входов блока управления, группа информационных входов которого подключена к группе выходов блока ввода, первая, вторая, третья и четвертая группы информационных входов блока мультиплексоров связаны соответственно с группой выходов генератора псевдослучайных тестов, группой выходов блока ввода, группой информационных выходов блока памяти тестов и группой выходов блока сравнения, введены блок сверхоперативной памяти и блок обработки информации, причем группы управляющих входов блока сверхоперативной памяти и блока обработки информации соедине ны с первой группой управляющих выходов блока управления, группа информационных входов блока сверхоперативной памяти подключена к первой группе информационных входов блока регистров, вторая группа информационных входов которого связана с группой выходов блока сверхоперативной памяти и первой группой информационных входов блока обработки ин,формации, вторая группа информационных входов которого соединена с группой выходов блока мультиплексоров.Кроме того, блок обработки информации содержит в каждом 1-м разряде 3 К -триггер и элемент ИЛИ, причем входы установки, сброса, синхрониза ции и первые 3 и-входы триггера связаны с первым входом элемента ИЛИ и подключены к первой группе входов блока, вторые 3 - и К -входы триггера соединены с-м входом второй группывходов блока, третьи 3 и К -входы триггера связаны с выходом элемента ИЛИ, второй вход кото рого подключен к-му входу третьей группы входов блока, выход 3 К -триггера является 1 -м выходом блока.На фиг. 1 представлена структурная схема предлагаемого устройстваф на фиг, 2 - принципиальные схемы разряда блока регистров, блока срав нения, блока сверхоперативной памяти, блока обработки информации и блока мультиплексоров, на фиг, 3 556065 ра 13 данных). Сама проверка состо.-,яния осуществляется сумматором 22.Элемент И-НЕ 23 обеспечивает передачу в блок 10 управления результата сравнения или его блокировку в зависимости от состояния триггера 17 маски.В состав 1 -го разряда блока 5сверхоперативной памяти входят триодноразрядных 3 24-26 с независимым управлением.ЗЦ 24 служит для хранения масоксравнения н масок приема в триггеры схема генератора псевдослучайныхтестов; на фиг, 4 - схема блока управления.В состав устройства входят: блок1 регистров, эталонный н проверяемый5 объекты 2 и 3, блок 4 сравнения,блок 5 сверхоперативной памяти, блок6 обработки информации, блок 7 мультиплексоров, генератор 8 псевдослучайных тестов, блок 9 памяти тестов,10 блок 10 управления, блок 11 ввода,блок 12 вывода.Каждый из блоков 1, 4, 5, 6, 7 состоит из Б идентичных схем (разрядов), каждая из которых соответствует одному выводу проверяемого иэталонного объектов. Величина И определяется числом выводов у объектов,для большинства микропроцессорныхблоков достаточно Б = 256.Схема любого-го разряда блока1 регистров содержит триггер 13 данных н триггер 14 коммутации связанфные с элементами И 15 и 16, триггер17 маски, элемент И 18 и два элемента И-НЕ 19 и 20.25, Триггер 13 данных служит для хранения значения сигнала, подаваемогов текущем такте проверки на входобъекта, или эталонного значения выходного сигнала объекта.- 30 Триггер 14 коммутации определяетфункцию канала в текущем такте: подача сигнала на вход объекта илиопрос его выходного сигнала. В последнем случае он переводит элеменЗ 5 ты И 15 и 16 в высокоимпедансное состояние выхода. Триггер 17 маскивместе с элементом И 18 разрешаетили запрещает прием информации втриггер 13 данных, а также позволя 40 ет ю из проверки соответствующий вывод объекта при сравненииреакций. Элементы И-НЕ 19 и 20 служат для выбора источника данныхпри установке триггера 13,В 1 -й разряд блока 4 сравнения45 входят последовательно соединенныеэлемент И 21, сумматор 22 по модулюдва,и элемент И-НЕ 23,Элемент И 21 слчжит для выбораспособа проверки состояния 1 -го вывода проверяемого объекта (сравнение с состоянием вывода эталонного объекта нли с состоянием тригге 104202325 13 данных; З 25 - для хранения сигяалон синхронизации объектов, эталонных значений управляющих выходных сигналон объектов, данных, определяющих тип теста для каждого входа объекта и дрф 39 26 - для хранения данных, обеспечивающих оперативное переключение каналов связи с объектами на прием или выдачу сигналон, Объем каждого из 39 24, 25 и 26 составляет 128-256 битЛюбой-й разряд блока б обработки информации в простейшем случае содержит 3-триггер 27, сонмещающий функции одноразрядного регистра-накопителя и схемы логического 15 преобразования данных, и элемент ИЛИ 28, с помощью которого н некоторыхоперациях обеспечивается отключение выхода 39 25 от нходон триггера 27. 20В каждый-й разряд блока 7 мультиплексоров входит элемент ИЛИ 29 и связанные с ним четыре элемента И 30-33, с помощью которых производится выбор источника данных для блока б обработки информации.Генератор 8 йсевдослучайных тестов служит для формирования последовательностей И-разрядных псевдослучайных чисел. Он реализуется на сдви. гоных регистрах с обратными связями. В зависимости от величины И в состав генератора может входить один или несколько регистров. На фиг. 3 показан вариант генератора, в котором используется сдниговый регистр35 34 и один сумматор 35 по модулю два,Блок 9 памяти тестов предназначен для хранения тестов, задаваемых всеми наборами, эталонных реакций (если при проверке отсутствует эта О лонный объект) и, при необходимости, фактических реакций объекта, которые записываются н него н процессе проверки и затем анализируются для диагностики неисправности. Блок 9 представляет собой 39 с про-. извольным доступом, имеющее обьем 4-8 тысяч ( Н + 1)-разрядных слон, где- число дополнительных разря.- дов в слове, необходимых для обеспечения работы блока 10 управления.Блок 10 управления содержит память 36 команд и связанные с ней счетчик 37 и регистр 38 команд, тактовый генератор 39, первую группу элементов И 40, обеспечивающую Фор мирование управляющих сигналон, которые через первую группу выходовблока 10 поступают во все блоки устройства, вторую группу элементов И41, Формирующую управляющие сигналы 60 для внутренних узлов блока, счетчик 42 адресов блока 9 памяти тестов, регистр 43 управления, предназначенный для запоминания управляющих раэрядон читаемого иэ блока 9 слова,регистр 44 состояния, который Фиксирует результат проверки реакций объекта, получаемый от блока 4 сравнения, и другие особые ситуации, требующие останона процесса проверки.Блок 11 ввода служит для загрузки тестов н блок 9 памяти, управляющих данныХ в блок 5 снерхоперативной памяти и команд в память 36блока 10 управления,В простейшем случае блок 11 содержит переключатели и кнопки, спомощью которых обеспечивается ручной ныбор приемника данных, набор,данных и их ввод. В более сложныхвариантах построения этот блок может содержать устройства ввода информации с машинных носителей и устройства внешней памяти типа магнитных дисков и т.п.Блок 12 вывода в наиболее простомисполнении имеет лишь средства индикации регистра 44 состояния и триггерон 27 блока б обработки информацииВ более сложных случаях в него могут входить устройства вывода на экран, на машинные носители информации, а также средства сопряжения с ЭВИ.Устройство работает следующим образом.Перед началом проверки с помощьюблока 11 ввода производится загрузка тестон и других данных. ПРиемникданных определяется управляющей информацией, эасылаемой из блока 11в регистр 38 команды.Хранимые тесты загружаются вблок 9 памяти через блок 7 мультиплексоров и блок б обработки инфор-.мации. При этом адреса ячеек блока9 принимаются от блока 11 в счетчик 42 адресов,Последовательности сигналон синхронизации, маски и другие управляющие данные поступают от блока 11в блок 5 сверхоперативной памяти(также через блоки б и 7), причемадреса ячеек блока 5 задаются непосредственно из регистра 38 команды.Программа, определяющая последовательность операций устройстна в каждом такте проверки объекта, загружается иэ блока 11 н память Зб ко.манд с использованием для заданияадресон счетчика 37 команд,После завершения ввода начинается сам процесс высокочастотной проверки, Для этого н регистр 38 внодится команда пуска, которая засылает в счетчик 37 команд адрес начала программы в памяти 36, приводит в исходное состояние генератор 8 тестов, сбрасывает счетчик 42 адресон блока 9 памяти тестов и включает тактовый генератор 39,При синхронной органиэации обмена с проверяемым объектом работаустройства в каждом такте С высокочастотной проверки сводится к следующей последовательности шагов,задаваемых командами программы,хранимой н памяти 36 блока 10 управления. Для определенности далее5считывается, что последовательностьсинхронизации объекта состоит из .двух наборов.Шаг 1. При этом происходит: чтение данных иэ блока 5 сверхоперативной памяти, объединение очередноготестового набора Х, получаемого иэблока 9 памяти, с псевдослучайнымнабором от генератора 8, введеннымв триггеры 27 блока б обработки в 15такте С, осуществляемое операциейХл К, чК- К где М констан-.та иэ 325 блока 5, определяющаявходы йроверяемого и эталонногообъектов, на которые должны прикладываться соответствующие разрядынабора Х (н этих разрядах 1( содержатся единицы)., К . - состояние триггеров 27 блока 6 передача маскивходов синхронизации объектов иэ З24 блока 9 в триггеры 17 блока 1 регистров, передачав незамаскированные триггеры 13 данных блока 1,передача иэ 3 9 26 блока 5 в триггеры 14 коммутации блока 1 данных длявключения каналов блока 1, связанных с двунаправленными выводами объектов, на выдачу состояния триггеров13 на объекты.Шаг 2. Происходит: чтение данныхиэ блока 5 сверхоперативной памяти, З 5передача маски информационных входов объектов иэ З 24 блока 5 нтриггеры 17 блока 1, передача первого набора синхронизации из З 25блока 5 в незамаскированные триггеры 13 данных блока 1 и соответствен-.но на входы объектов, сдвиг в регист-ре 34 генератора 8 тестов для получения очередного псевдослучайноготестового набора для такта С + 1,подготовка следующего адреса в счетчике 42 и запуск чтения тестовогонабора из блока 9 памяти для такта.С + 1,Шаг 3. Осуществляется чтение данных из блока 5 сверхоперативной памяти, передача второго набора синхронизации иэ 39 25 блока 5 в незамаскированные триггеры 13 данныхблока 1 и соответственно на входырбъектов, передача из З 26 блока 5в триггеры 14 блока 1 данных длявключения каналов блока 1, связанныхс двунаправленными выводами объектов на прием их реакции,Шаг 4. Осуществляется также чтениебцданных из блока 5 сверхоперативнойпамяти; прйем в блок б обработкипсевдослучайного набора 3 для такта+ 1 от генератора 8 тестов и выполнение операции Ч А К -й , где И - константа из ЗЧ 2 Ъ, определяющая входы объектов, на которые должны подаваться соотнетстующие разряды набора(в этих разрядах К содержатся единицы), передача иэ 3 924 блока 5 маски сравнения н триггеры 17 блока 1, сравнение состояниянезамаскированных выходов проверяемого и эталонного объектов н блоке 4 (при равенстве - переход к шагу 1,при неравенстве сигналов хотя бы одной пары выходов - установка разряда ошибки регистра состояния 44 и останов),Каждый иэ укаэанных шагов задается соответствующей ему одной командой программы внутритактного управления, читаемой блоком 10 из памяти 36, Прочитанная команда принимается в регистр 38, а в счетчике 37 одновременно формируется адрес следующей команды, т.е. выполнение текущей команды совмещается по времени с чтением следующей.Каждая команда содержит адресноеполе, в котором размещаются адреса ЗЧ 24, 25 и 26 блока 5 сверхоперативной памяти, поле кода операции блока 6 обработки, поле управления блоком 7 мультиплексоров и управляющие разряды, с помощью которых задается выдача стробирующих сигналон в блоки 5 и б, в блок 1 регистров и генератор 8 псевдослучайных тестов. Эти сигналы вырабатываются первой группой элементов И 40 под действием импульсов тактового генератора 39. Сигналы управления счетчиком 37 команд, счетчиком 42 адресов,регистром 43 управления и блоком 9 ;памяти тестов формируются аналогичным образом второй группой элементов И 41В регистр 43 управления записываются управляющие разряды слов, читаемых из блока 9. При соответствующем признаке и команде, находящейся в регистре 38, содержимое ре-. гистра 43 передается в счетчик 37 команд. Таким образом, при выборке теста иэ блока 9 можно передавать управление разным программам,.хранимым в памяти 36, что позволяет из.менять последовательность и состав операций устройства на разных этапах проверки объекта. Последовательность команд н пределах одной программы может изменяться с помощью команд услонных переходов по результату сравнения, полученному от блока 4, что необходимо, например, приасинхронной ораганизации обмена спроверяемым объектом, когда в каждом такте проверки добавляются шаги, связанные с анализом состояния управляющих выходов объекта. При выполнении команд условных и безусловных переходов новое состояние счет 1042023 10чика 37 Формируется не увеличениемего предыдущего состояния на единицу, а путем передачи в него адресаиз регистра 38,Дополнительные шаги и соответственно команды в програьйе вводятсяи тогда, когда требуется модифицировать тестовый набор в блоке б обработки информации перед передачейего на входы объекта, при записиреакций объекта в блок 9 памяти тестов и в некоторых других случаях,При описанном ранее построении блок6 обработки информации позволяет выполнять следующие операцииоСдЪ- КсКЛ Ъ- К() ККс л РОК - .,где 0 С - операнд блока 5 сверхоперативной памяти или вектор иэ всех единиц," операнд из блока 9 памяти тестов, от генератора 8, от блока 4 сравнения или векториз всех единиц.Состояние К триггеров 27 блока 6 обработки информации может быть записано в блок памяти тестов или в блок сверхоперативной памяти и использоваться в качестве операндов о(, ив последующих операциях,.При показанном на фиг, 2 построении блока 1 регистров и блока 4 сравнения можно изменять вид данных, получаемых от блока 4, в зависимости от состояния тех триггеров 13 блока 1, которые соответствуют выходампроверяемого объекта.Если в эти триггеры записаны эталонные значения выходных сигналов,то блок 4 выдает вектор ошибок, вкотором единицы соответствуют выходам объекта, на которых обнаруженаошибка, если в триггеры 13 записана константа "Нуль", то на выходыблока 4 передается Фактическое со стояние выходов объектов, есликонстанта "Единица", то инверсияэтого состояния. Главным технико-экономическимпреимуществом предлагаемогс устройства по сравнению с прототипом является более высокое быстродействиеи соответственно более высокая частота проверки объектов, достигаемаяО введением блока сверхоперативнойпамяти и блока обработки информации,которые обеспечивают совмещение вовремени выборки и генерированиятестов с операциями управления каналами связи с объектом,Приведенная типовая программапроверки синхронного объекта состоит для предлагаемого устройства изчетырех шагов (команд). Аналогичнаяпрограмма для устройства-прототипаЗО содержит шесть шагов, каждый иэ которых включает одно обращение к блоку памяти тестов. Таким образом,при одинаковых скоростях элементовобоих устройств быстродействие пред 35 лагаемого устройства окаэнваетсяв 1,5 раза выше, чем прототипа.1042023 Х ЯКУ,ОфЮСоставитель И. СаронТехредМ.,Ге)ргель орректор 0 Тиго Редактор елемеш Подписи илиал ППП "Патентф, г. ужгород, ул. Проектная,з 7129/49 Тираж 706 ВНИИПИ Государственного коми по делам изобретений и от 113035, Москва, Ж, Раушск

СмотретьЗаявка

3421787, 16.02.1982

ИНСТИТУТ ЭЛЕКТРОННЫХ УПРАВЛЯЮЩИХ МАШИН

СЕРГЕЕВ БОРИС ГЕОРГИЕВИЧ, БЕРЕЗОВ ЕВГЕНИЙ ПЕТРОВИЧ, ЧУЧМАН ВЛАДИМИР ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 11/22

Метки: блоков, микропроцессорных

Опубликовано: 15.09.1983

Код ссылки

<a href="https://patents.su/9-1042023-ustrojjstvo-kontrolya-mikroprocessornykh-blokov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство контроля микропроцессорных блоков</a>

Предыдущий патент: Устройство для обнаружения сбоев информации дисплея

Следующий патент: Многоканальное резервированное устройство

Случайный патент: Вибрационное сито