Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

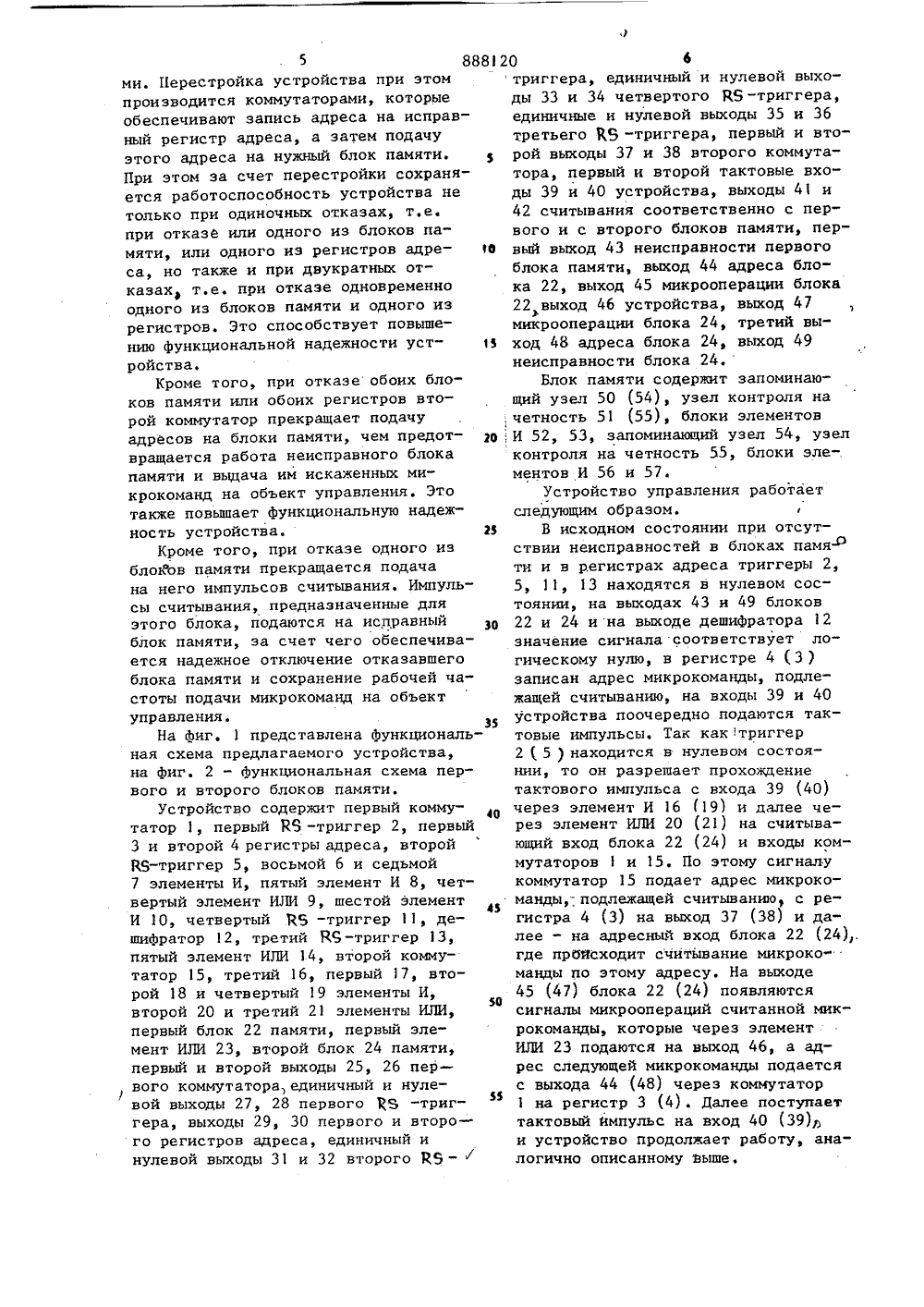

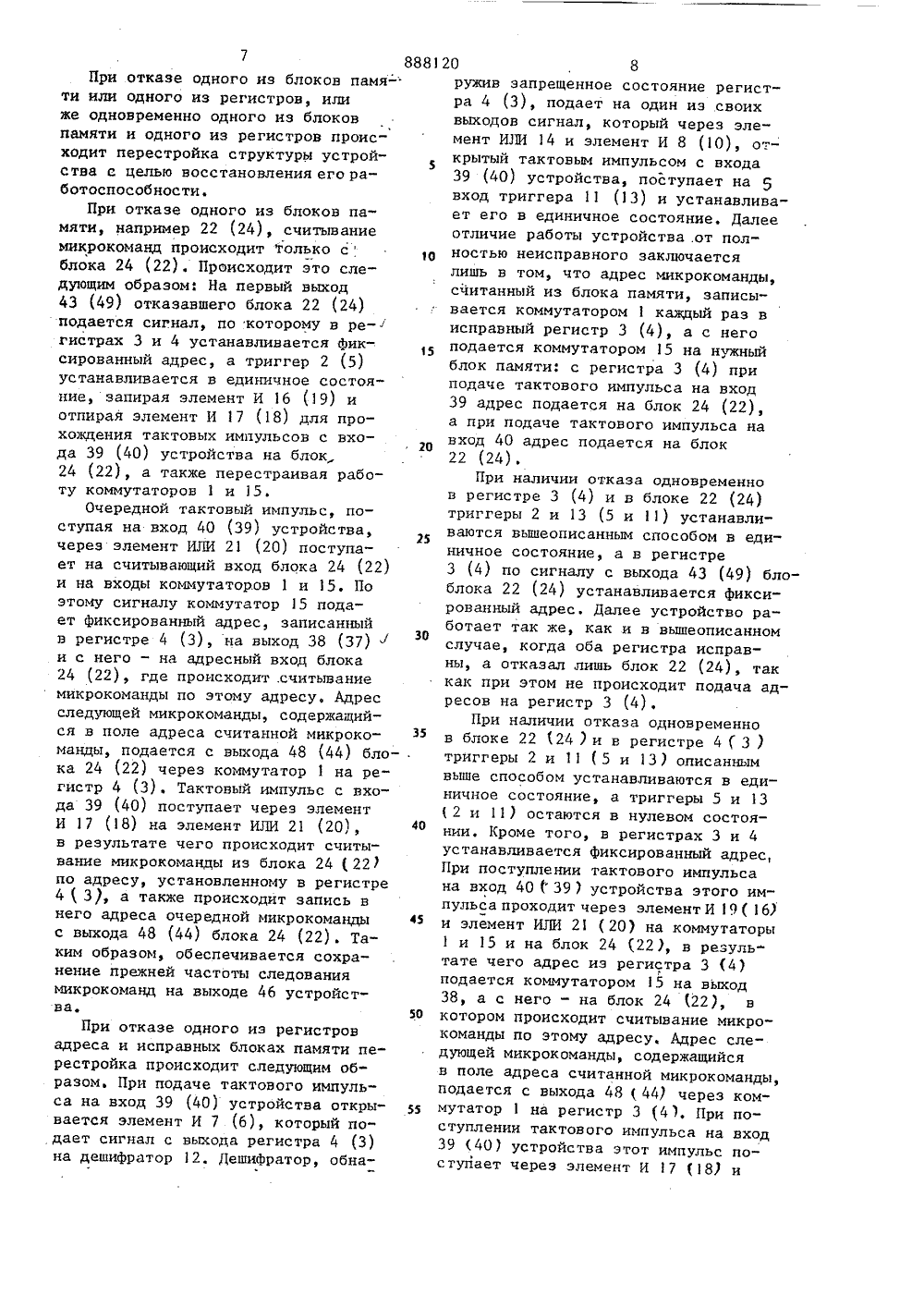

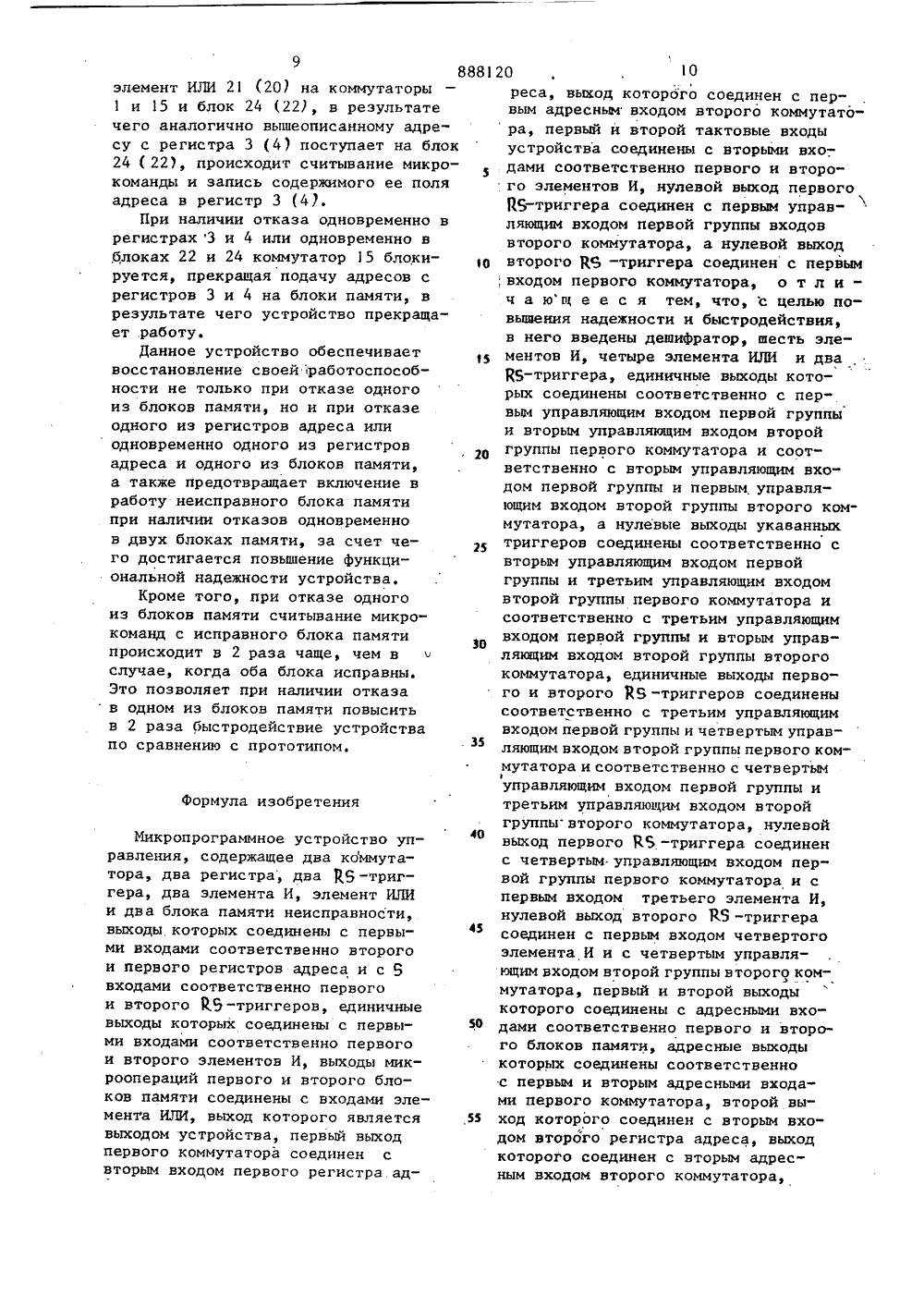

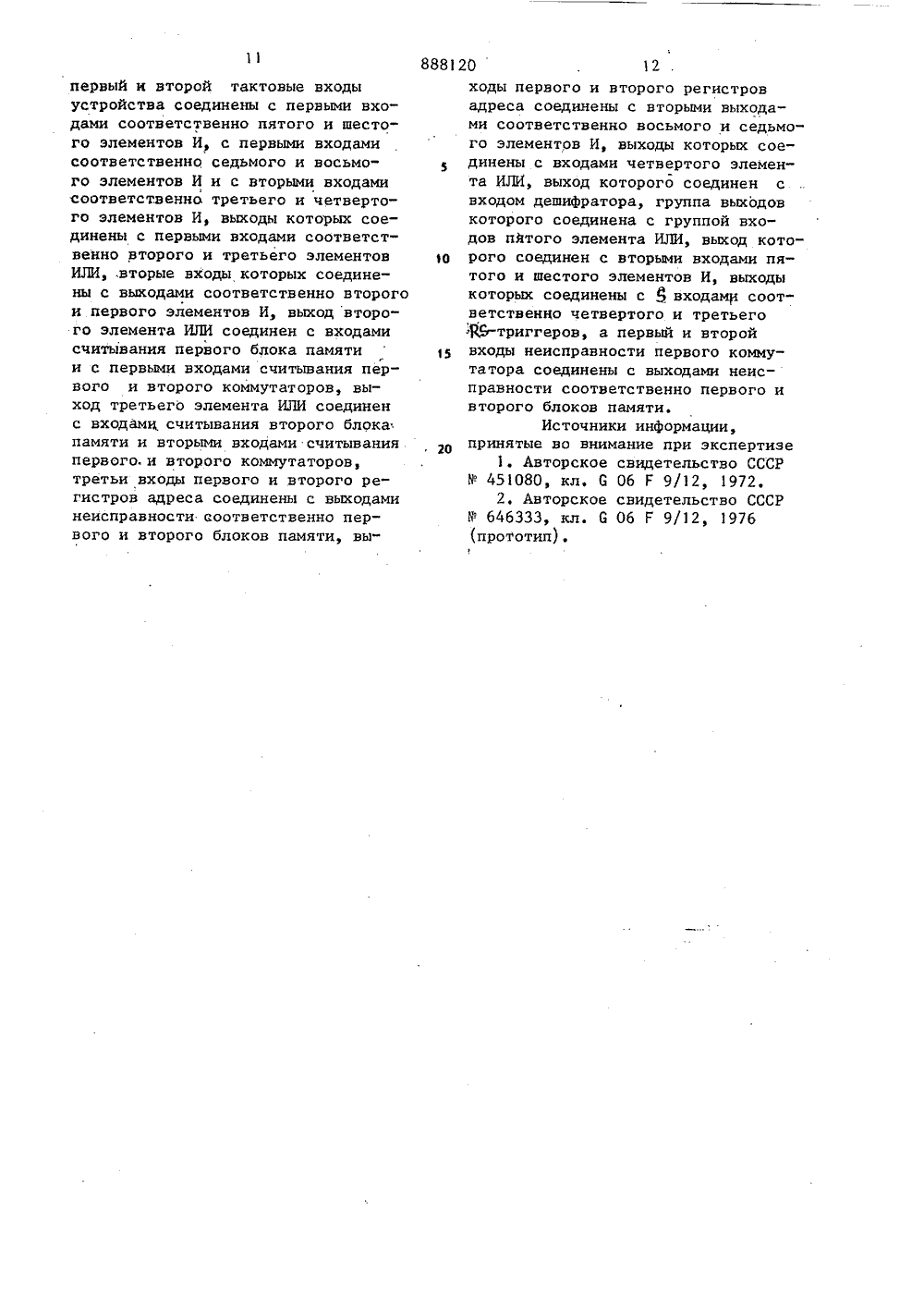

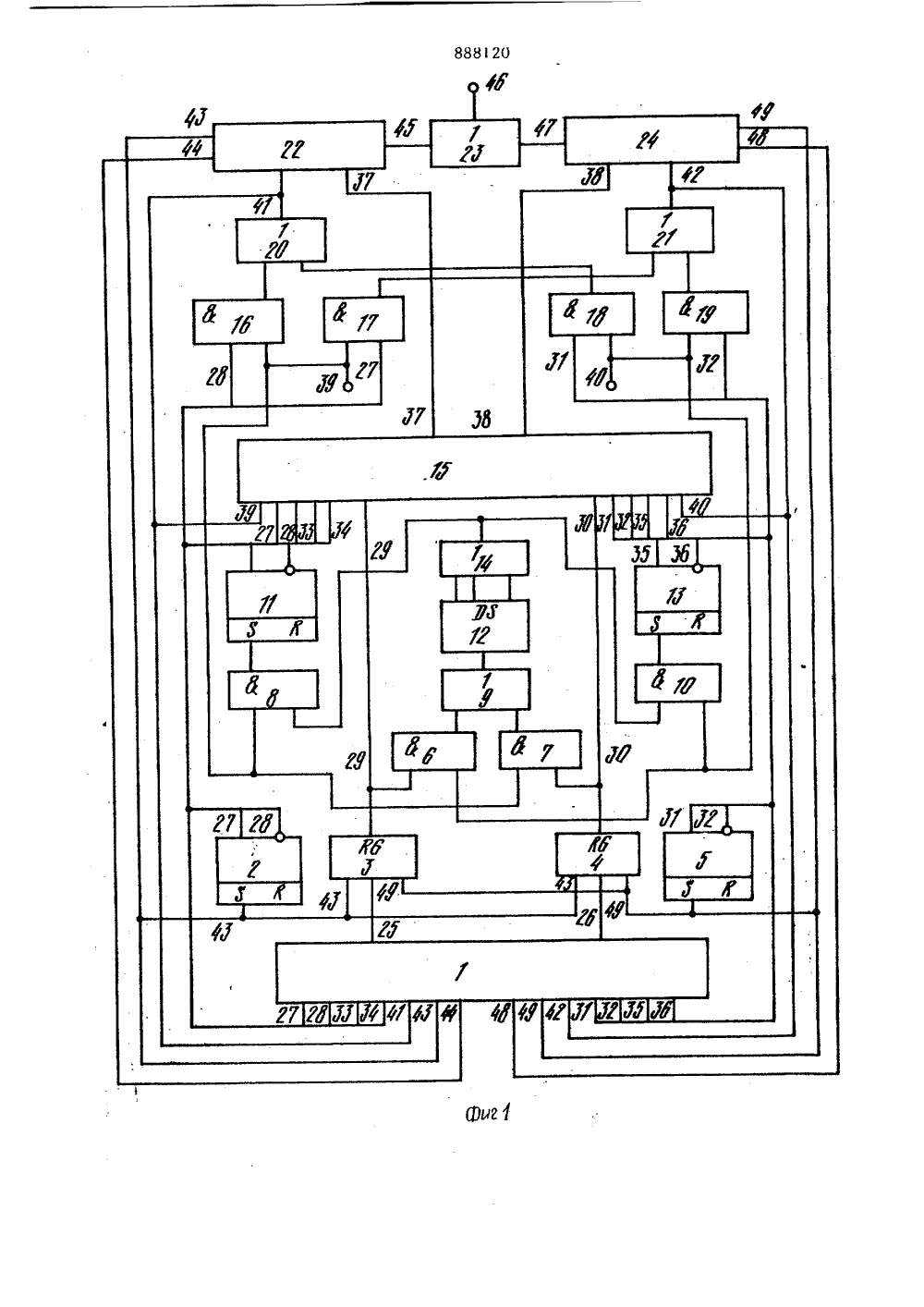

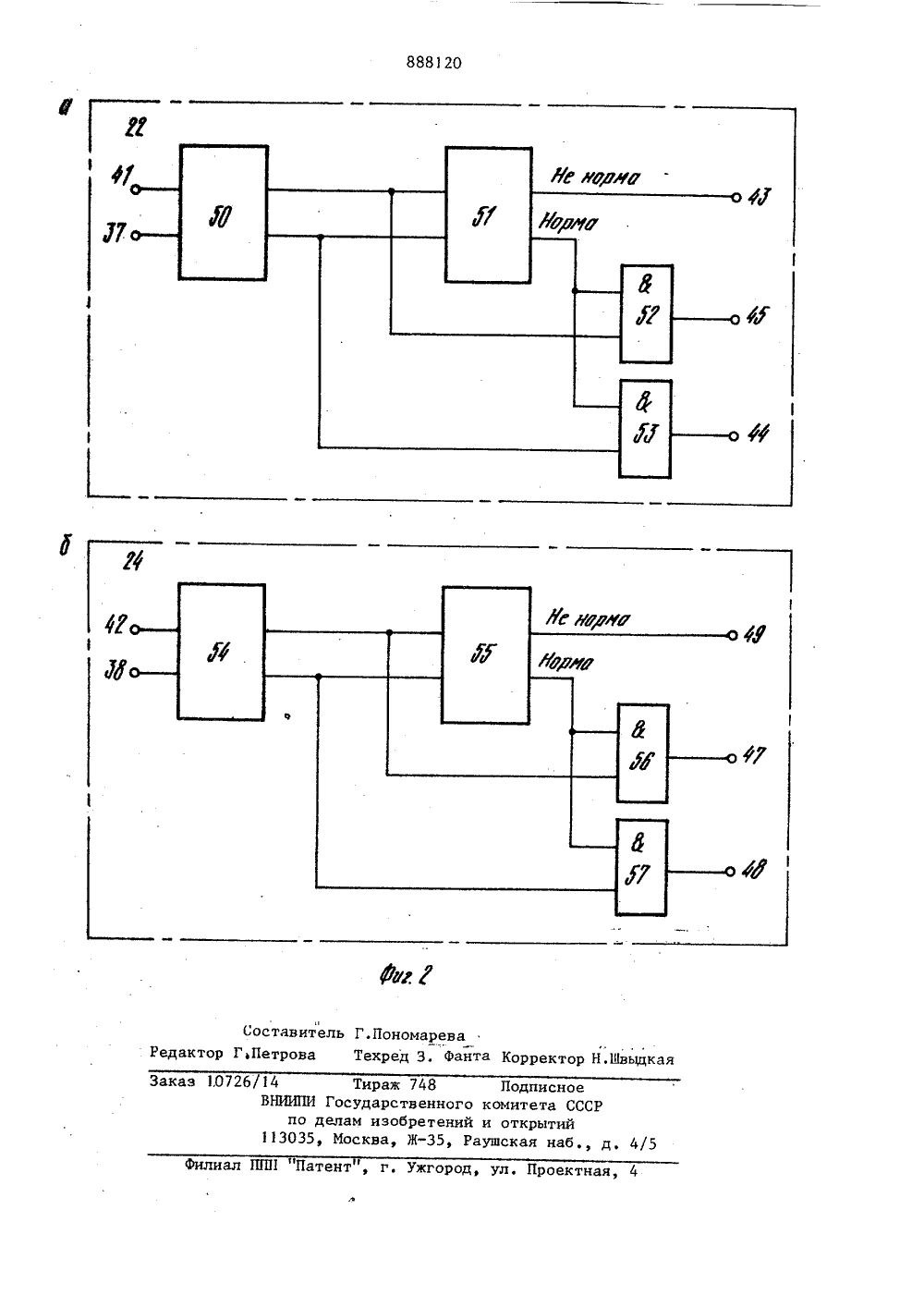

Н.К.Байда, И.П.Барбаш, И.И.Корниенко, Э.Н.Корчак,Г.Н.Тимонькин, С.Н.Ткаченко, М.П.Тк В С Х 2) Авторы изобретен 7) Заявитель ИЯ 54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО Изоб вычислител к устройстИзвестн ство управ запоминающ выадреса,гера (КБ а я адежозможвосстановл ности автоматическог ния работоспособност какого-либо элемента ри отказе тройства. аибо ческои с ляется п н т У т п т е е ение относится к циФровойьной технике, в частностивам управления ЦВМ.о микропрограммное устройления 1 11, содержащее дваих блока, два регистраа элемента И, два тригриггера), два коммутатора Недостатком этого устрой яется низкая Функциональна ость, вызванная отсутствие лее близким решением по техущности к изобретениюерестраиваемое микропроустройство управления 12. ойство содержит два блока два регистра адреса, два управления (В 5-триггера ), ента И и два коммутатора. Недостатками данного устройства вляются низкая Функциональная наежность и низкое быстродействие.Целью изобретения является по шение надежности и быстроде ия устройства.Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее два блока памяти, два коммутатора, два регистра адреса, два КЯ"триггера, два элемента И и элемент ИЛИ, причем выходы неисправности первого и второго блоков памяти соединены с первыми входами соответственно второго и первого регистров адреса и с Я входами соответственно пер вого и второго К 5 -триггеров, единичные выходы которых соединены с первыми входами соответственно первого и второго элементов И, выходы микроопераций первого и второго блоков памяти соединены с входами элемента ИЛИ, выход которого5 является выходом устройства, первый выход первого коммутатора соединен с вторым входом первого регистра адреса, выход которого соединен с первым адресным входом второго коммутатора, первый и второй тактовые входы устройства соединены с вторыми входами соответственно первого и второго элементов И, нулевой выход первого К 6 -триг О гера соединен с первым управляющим входом первой группы входов второго коммутатора, нулевой выход второго Щ-триггера соединен с первым входом первого коммутатора, введены дешифратор, два К 5-триггера, шесть элементов И и четыре элемента ИЛИ причем единичные выходы третьего и четвертого Й 5 -триггеров соединены соответственно с первым управляющим входом первой группы и вторым управляющим входом, второй группы первого коммутатора и соответственно с вторым управляющим входом первой группы и первым управляющим входом второй25 группы второго коммутатора, нулевые выходы третьего и четвертого К 5-триггеров соединены соответственно с вторым управляющим входом первой группы и третьим управляющим входом вто 30 рой группы первого коммутатора и соответственно с третьим управляющим входом первой группы и вторым управляющим входом второй группы второго коммутатора, единичные выходы первого и второго К 6-триггеров соединены соот 35 ветственно с третьим управляющим входом первой группы и четвертым управляющим входом второй группы первого коммутатора и соответственно с четвертым управляющим входом первой группы и третьим управляющим входом второй группы второго коммутатора, нулевой выход первого ЯБ -триггера соединен с четвертым управляющим входом первой группы первого коммутатора и с первым вхо- ф 5 дом третьего элемента И, нулевой выход второго Я 6 -триггера соединен с первым входом четвертого элемента И и с четвертым управляющим входом второй группы второго коммутатора, первый и 50 второй выходы которого соединены с адресными входами соответственно первого и второго блоков памяти, адресные выходы которых соединены соответственно с первым и вторым адресными входами первого коммутатора, второй выход которого соединен с вторым входом второго регистра адреса, выход которого соединен с вторым адресным входом второго коммутатора, первый и второй тактовые входы устройства соединены с первыми входами соответственно пятого и шестого элементов И, с первыми входами соответственно седьмого и восьмого элементов И и с вторыми входами соответственно третьего и четвертого элементов И, выходы которых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, вторые входы которых соединены с выходами соответственно второго и первого элементов И, выход второго элемента ИЛИ соединен с входами считывания первого блока памяти и с первыми входами считывания первого и второго коммутаторов, выход третьего элемента ИЛИ соединен с входами считывания второго блока памяти и вторыми входами считывания первого и второго коммутаторов, третьи входы первого и второго регистров адреса соединены с выходами неисправности соответственно первого и второго блоков памяти, выходы первого и второго регистров адреса соединены с вторыми входами соответственно восьмого и седьмого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, выход которого соединен с входом дешифратора, группа выходов которого соединена с группой входов пятого элемента ИЛИ, выход которого соединен с вторыми входами пятого и шестого элементов И, выходы которых соединены с Я входами соответственно четвертого и третьего Кб-триггеров, первый и второй входы неисправности первого коммутатора соединены с выходами неисправности соответственно первого и второго блоков памяти.Сущность"изобретения состоит в повышении Функциональной надежности устройства за счет обеспечения перестройки его структуры при отказе одного из регистров адреса и предотвращения включения в работу отказавшего ранее блока памяти, а также в повышении быстродействия устройства при работе с отказавшим одним блоком памяти за счет сохранения рабочей частоты выдачи микрокоманд на объект управления из другого блока памяти,Отказы регистров адресов обнаруживаются дешифратором и фиксируются дополнительно введенными для этой цели третьим и четвертым Р 5-триггера50 5 888 ми. Перестройка устройства при этом производится коммутаторами, которые обеспечивают запись адреса на исправный регистр адреса, а затем подачу этого адреса на нужный блок памяти. При этом за счет перестройки сохраняется работоспособность устройства не только при одиночных отказах, т.е. при отказе или одного из блоков памяти, или одного из регистров адре е са, но также и при двукратных отказах, т.е. при отказе одновременно одного из блоков памяти и одного из регистров. Это способствует повышению Функциональной надежности уст з ройства.Кроме того, при отказе обоих блоков памяти или обоих регистров второй коммутатор прекращает подачу адресов на блоки памяти, чем предот- щ вращается работа неисправного блока памяти и выдача им искаженных микрокоманд на объект управления. Это также повышает Функциональную надежность устройства. гюКроме того, при отказе одного из блойэв памяти прекращается подача на него импульсов считывания. Импульсы считывания, предназначенные для этого блока, подаются на исправный блок памяти, за счет чего обеспечивается надежное отключение отказавшего блока памяти и сохранение рабочей частоты подачи микрокоманд на объект управления.На Фиг. 1 представлена Функциональная схема предлагаемого устройства, на Фиг. 2 - Функциональная схема первого и второго блоков памяти.Устройство содержит первый коммутатор 1, первый ЙЯ -триггер 2, первый3 и второй 4 регистры адреса, второй Щ-триггер 5, восьмой 6 и седьмой7 элементы И, пятый элемент И 8, четвертый элемент ИЛИ 9, шестой элемент И 10, четвертый Я 5 -триггер 11, дешиФратор 12, третий Щ -триггер 13, пятый элемент ИЛИ 14, второй коммутатор 15, третий 16, первый 17, второй 18 и четвертый 19 элементы И, второй 20 и третий 21 элементы ИЛИ, первый блок 22 памяти, первый элемент ИЛИ 23, второй блок 24 памяти, первый и второй выходы 25, 26 пер/вого коммутатора единичный и нулеИвой выходы 27, 28 первого 75 -триггера, выходы 29, 30 первого и второ - го регистров адреса, единичный инулевой выходы 31 и 32 второго Р 5 -20 бтриггера, единичный и нулевой выходы 33 и 34 четвертого К 5 -триггера,единичные и нулевой выходы 35 и 36третьего К 5 -триггера, первый и второй выходы 37 и 38 второго коммутатора, первый и второй тактовые входы 39 и 40 устройства, выходы 41 и42 считывания соответственно с первого и с второго блоков памяти, первый выход 43 неисправности первогоблока памяти, выход 44 адреса блока 22, выход 45 микрооперации блока22 выход 46 устройства, выход 47микрооперации блока 24, третий выход 48 адреса блока 24, выход 49неисправности блока 24,Блок памяти содержит запоминающий узел 50 (54), узел контроля на: И 52, 53, запоминающий узел 54, узелконтроля на четность 55, блоки элементов И 56 и 57.Устройство управления работаетследующим образом.В исходном состоянии при отсутствии неисправностей в блоках памя-ти и в регистрах адреса триггеры 2,5, 11, 13 находятся в нулевом состоянии, на выходах 43 и 49 блоков22 и 24 и на выходе дешиФратора 12значение сигнала соответствует логическому нулю, в регистре 4 ( 3 )записан адрес микрокоманды, подлежащей считыванию, на входы 39 и 40устройства поочередно подаются тактовые импульсы. Так как триггер2 1, 5 ) находится в нулевом состоянии, то он разрешает прохождениетактового импульса с входа 39 (40)через элемент И 16 119) и далее через элемент ИЛИ 20 (21) на считывающий вход блока 22 (24) и входы коммутаторов 1 и 15По этому сигналукоммутатор 15 подает адрес микрокоманды,-подлежащей считыванию с регистра 4 (3) на выход 37 (38) и далее - на адресный вход блока 22 (24),.где прбйсходит считывание микрокомаиды по этому адресу. На выходе45 (47) блока 22 (24) появляютсясигналы микроопераций считанной микрокоманды, которые через элементИЛИ 23 подаются на выход 46, а адрес следующей микрокоманды подаетсяс выхода 44 (48) через коммутатор1 на регистр 3 (4). Далее поступаеттактовый ймпульс на вход 40 (39)ди устройство продолжает работу, аналогично описанному Выше.20 7 8881При отказе одного из блоков памя- ти или одного из регистров, или же одновременно одного из блоков памяти и одного из регистров происходит перестройка структуры устройства с целью восстановления его работоспособности.При отказе одного из блоков памяти, например 22 (24), считывание микрокоманд происходит только с блока 24 (22). Происходит это следующим образом На первый выход 43 (49) отказавшего блока 22 (24) подается сигнал, по которому в ре-гистрах 3 и 4 устанавливается Фиксированный адрес, а триггер 2 (5) устанавливается в единичное состояние, запирая элемент И 16 (19) и отпирая элемент И 17 (18) для прохождения тактовых импульсов с входа 39 (40) устройства на блок 24 (22), а также перестраивая работу коммутаторов 1 и 15.Очередной тактовый импульс, поступая на вход 40 (39) устройства, через элемент ИЛИ 21 (20) поступает на считывающий вход блока 24 (22) и на входы коммутаторов 1 и 15. По этому сигналу коммутатор 15 подает Фиксированный адрес, записанный в регистре 4 (3), на выход 38 (37)30 и с него - на адресный вход блока 24 (22), где происходит .считывание микрокоманды по этому адресу. Адрес следующей микрокоманды, содержащийся в поле адреса считанной микрокоманды, подается с выхода 48 (44) бло- . ка 24 (22) через коммутатор 1 на регистр 4 (3). Тактовый импульс с входа 39 (40) поступает через элемент И 17 (18) на элемент ИЛИ 21 (20), 40 в результате чего происходит считывание микрокоманды из блока 24 ( 22) по адресу, установленному в регистре 43), а также происходит запись в него адреса очередной микрокоманды 45 с выхода 48 (44) блока 24 (22). Таким образом, обеспечивается сохранение прежней частоты следования микрокоманд на выходе 46 устройства. 50При отказе одного иэ регистров адреса и исправных блоках памяти перестройка происходит следующим образом. При подаче тактового импульса на вход 39 (40) устройства откры" 55 вается элемент И 7 (6), который подает сигнал с выхода регистра 4 (3) на дешифратор 12. Дешифратор, обна 20 8 ружив запрещенное состояние регистра 4 (3), подает на один иэ своих выходов сигнал, который через элемент ИЛИ 14 и элемент И 8 (О), открытый тактовым импульсом с входа 39 (40) устройства, поступает на 5 вход триггера 11 (13) и устанавливает его в единичное состояние, Далее отличие работы устройства .от полностью неисправного заключается лишь в том, что адрес микрокоманды, считанный из блока памяти, записывается коммутатором 1 каждый раз в исправный регистр 3 (4), а с него подается коммутатором 15 на нужный блок памяти: с регистра 3 (4) при подаче тактового импульса на вход 39 адрес подается на блок 24 (22), а при подаче тактового импульса на вход 40 адрес подается на блок 22 (24) .При наличии отказа одновременно в регистре 3 (4) и в блоке 22 (24) триггеры 2 и 13 (5 и 11) устанавливаются вышеописанным способом в единичное состояние, а в регистре 3 (4) по сигналу с выхода 43 (49) блоблока 22 (24) устанавливается фиксированный адрес. Далее устройство работает так же, как и в вьппеописанном случае, когда оба регистра исправны, а отказал лишь блок 22 (24), так как при этом не происходит подача адресов на регистр 3 (4).При наличии отказа одновременно в блоке 22 (24 ) и в регистре 4 ( 3 ) триггеры 2 и 11 ( 5 и 13 ) описанным выше способом устанавливаются в единичное состояние, а триггеры 5 и 132 и 11) остаются в нулевом состоянии, Кроме того, в регистрах 3 и 4 устанавливается Фиксированный адрес, При поступлении тактового импульса на вход 40 (" 39 ) устройства этого импульса проходит через элемент И 19 ( 16) и элемент ИЛИ 21 (20) на коммутаторы 1 и 15 и на блок 24 (22), в резуль" тате чего адрес из регистра 3 (4) подается коммутатором 15 на выход 38, а с него - на блок 24 (22), в котором происходит считывание микро- команды по этому адресу. Адрес следующей микрокоманды, содержащийся в поле адреса считанной микрокоманды, подается с выхода 4844) через коммутатор 1 на регистр 3 (4 1. При поступлении тактового импульса на вход 39 (40) устройства этот импульс поступает через элемент И 17 (18) и30 8881элемент ИЛИ 21 (20) на коммутаторы1 и 15 и блок 24 (22), в результатечего аналогично вышеописанному адресу с регистра 3 (4) поступает на блок24 ( 22), происходит считывание микрокоманды и запись содержимого ее поляадреса в регистр 3 (4).При наличии отказа одновременно врегистрах 3 и 4 или одновременно в,блоках 22 и 24 коммутатор 15 блокируется, прекращая подачу адресов срегистров 3 и 4 на блоки памяти, врезультате чего устройство прекращает .работу.Данное устройство обеспечиваетвосстановление своей работоспособности не только при отказе одногоиз блоков памяти, но и при отказеодного из регистров адреса илиодновременно одного из регистровадреса и одного из блоков памяти,а также предотвращает включение вработу неисправного блока памятипри наличии отказов одновременнов двух блоках памяти, за счет чего достигается повышение функциональной надежности устройства,Кроме того, при отказе одногоиз блоков памяти считывание микрокоманд с исправного блока памятипроисходит в 2 раза чаще, чем вслучае, когда оба блока исправны.Это позволяет при наличии отказав одном из блоков памяти повыситьв 2 раза Гыстродействие устройствапо сравнению с прототипом.20 10 реса, выход которого соединен с первым адресным входом второго коммутатора, первый и второй тактовые входы устройства соединены с вторыми входами соответственно первого и второго элементов И, нулевой выход первого Д 5-триггера соединен с первым управляющим входом первой группы входов второго коммутатора, а нулевой выход второго Щ -триггера соединен с первымвходом первого коммутатора, о т л ич а ю щ е е с я тем, что, с целью повышения надежности и быстродействия,в него введены дешифратор, шесть элементов И, четыре элемента ИЛИ и дваЯ 5-триггера, единичные выходы которых соединены соответственно с перчвыч управляющим входом первои группы и вторым управляющим входом второй группы первого коммутатора и соответственно с вторым управляющим входом первой группы и первым управляющим входом второй группы второго коммутатора, а нулевые выходы укаванных триггеров соединены соответственно с вторым управляющим входом первой группы и третьим управляющим входом второй группы первого коммутатора и соответственно с третьим управляющим входом первой группы и вторым управляющим входом второй группы второго коммутатора, единичные выходы первого и второго Я 5 -триггеров соединены соответственно с третьим управляющим входом первой группы н четвертым управляющим входом второй группы первого ком40 50 Формула изобретения Микропрограммное устройство управления, содержащее два коммутатора, два регистра, два Р,5 -триггера, два элемента И, элемент ИЛИ и два блока памяти неисправности, выходы которых соединены с первыми входами соответственно второго и первого регистров адреса и с 9 входами соответственно первого и второго К 5 -триггеров, единичные выходы которых соединены с первыми входами соответственно первого и второго элементов И, выходы микроопераций первого и второго блоков памяти соединены с входами элемента ИЛИ, выход которого является выходом устройства, первый выход первого коммутатора соединен с вторым входом первого регистра.адмутатора и соответственно с четвертым3управляющим входом первой группы итретьим управляющим входом второйгруппы второго коммутатора, нулевойвыход первого 8.5 -триггера соединенс четвертым управляющим входом первой группы первого коммутатора и спервым входом третьего элемента И,нулевой выход второго Р 5 -триггерасоединен с первым входом четвертогоэлемента И и с четвертым управляющим входом второй группы второго коммутатора, первый и второй выходыкоторого соединены с адресными входами соответственно первого и второго блоков памяти, адресные выходыкоторых соединены соответственнос первым и вторым адресными входами первого коммутатора, второй выход которого соединен с вторым входом второго регистра адреса, выходкоторого соединен с вторым адресным входам второго коммутатора, первый н второй тактовые входыустройства соединены с первыми входами соответственно пятого и шестого элементов И, с первыми входамисоответственно седьмого и восьмого элементов И и с вторыми входамисоответственно третьего и четвертого элементов И, выходы которых соединены с первыми входами соответственно второго и третьего элементовИЛИвторые входы которых соединены с выходами соответственно второгои первого элементов И, выход второго элемента ИЛИ соединен с входамисчитывания первого блока памятии с первыми входами считывания первого и второго коммутаторов, выход третьего элемента ИЛИ соединенс входами, считывания второго блокапамяти и вторыми входами считыванияпервого.и второго коммутаторов,третьи входы первого и второго регистров адреса соединены с выходаминеисправности соответственно первого и второго блоков памяти, вы 888120ходы первого и второго регистровадреса соединены с вторыми выходами соответственно восьмого и седьмого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, выход которого соединен свходом дешифратора, группа выходовкоторого соединена с группой входов пятого элемента ИЛИ, выход кото рого соединен с вторыми входами пятого и шестого элементов И, выходыкоторых соединены с Я входамн соответственно четвертого и третьего45 гтриггеров, а первый и второйвходы неисправности первого коммутатора соединены с выходами неисправности соответственно первого ивторого блоков памяти.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРВ 451080, кл. С 06 Г 9/12, 1972.2, Авторское свидетельство СССРР 646333, кл. О 06 Е 9/12, 1976888120 Составитель Г.Пономареваактор ГПетрова Техред 3. Фанта Корректор Н,Швыдк и филиал ППП "Патент , г. Ужгород, ул. Проектна аказ 1,0726/14 Тираж 748 ВНИИПИ Государственно по делам изобретен 113035, Москва, Ж, Подписноемитета СССРоткрытийская наб ., д .

СмотретьЗаявка

2900412, 28.03.1980

ПРЕДПРИЯТИЕ ПЯ А-7160

БАЙДА НИКОЛАЙ КОНСТАНТИНОВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, КОРНИЕНКО ИВАН ИОСИФОВИЧ, КОРЧАК ЭДУАРД НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.12.1981

Код ссылки

<a href="https://patents.su/8-888120-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Вероятностное устройство для решения конечно-разностных уравнений

Следующий патент: Устройство для формирования исполнительных адресов

Случайный патент: Генератор импульсов тока