Формирователь тестов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1552185

Авторы: Андроник, Гремальский

Текст

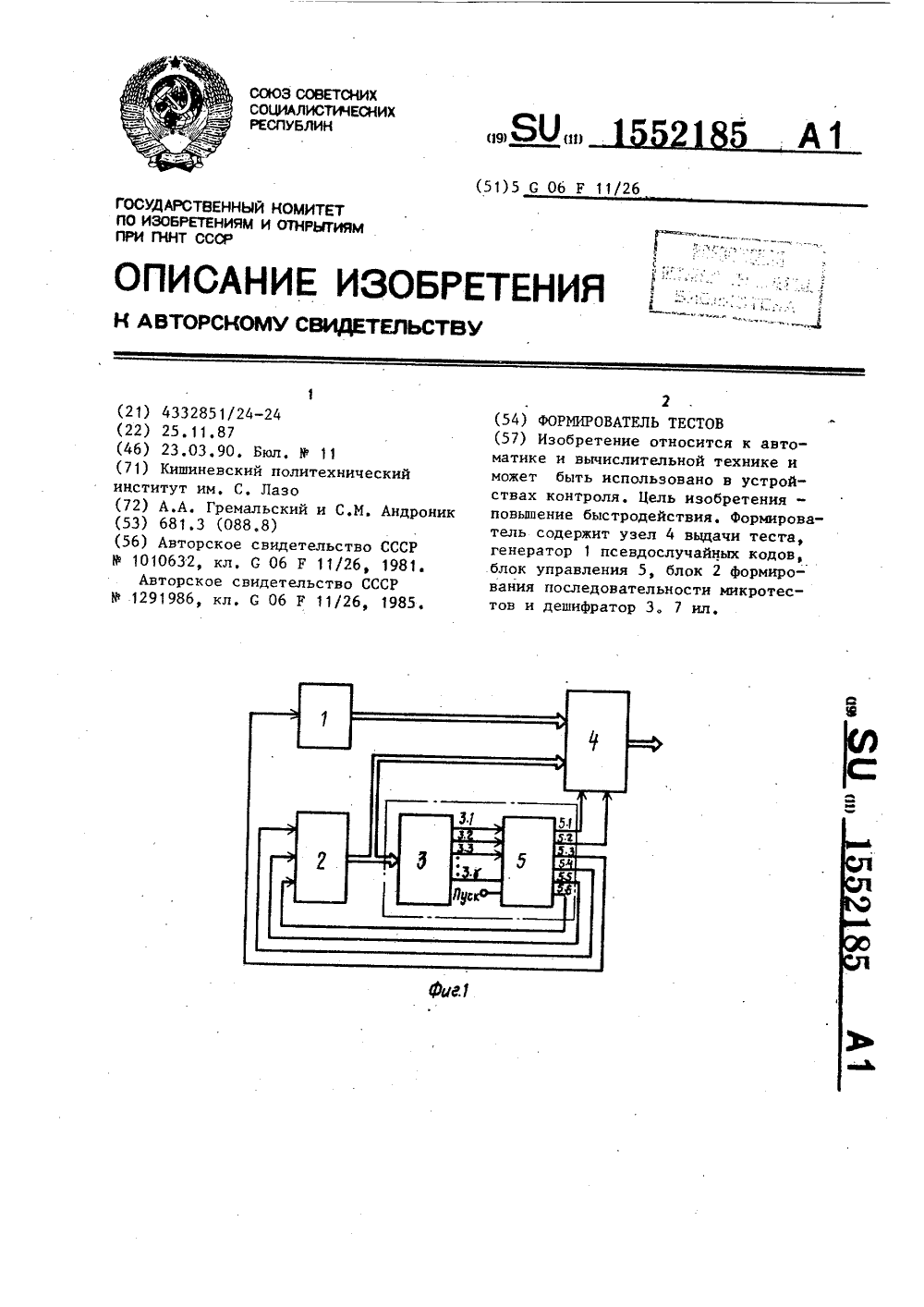

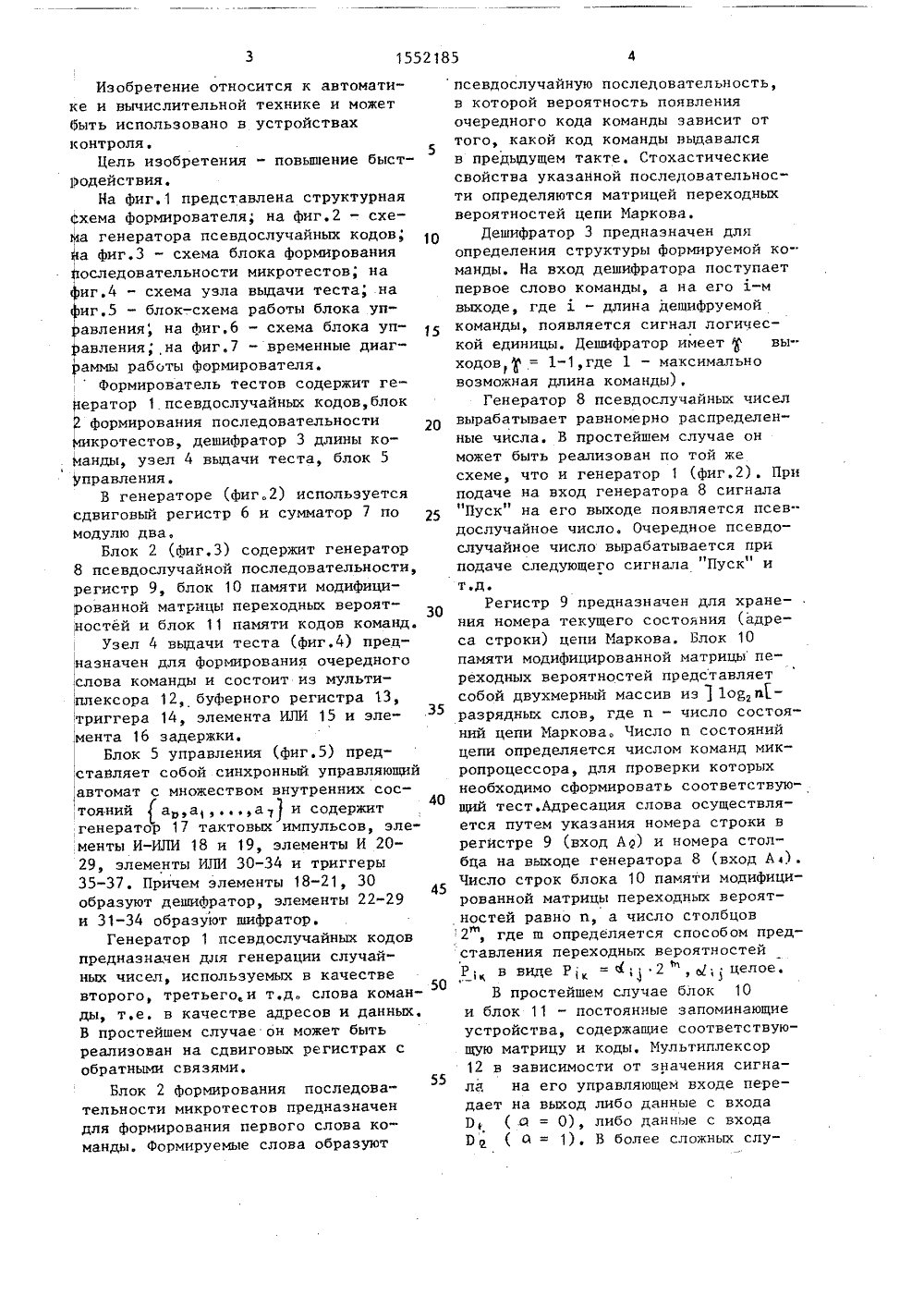

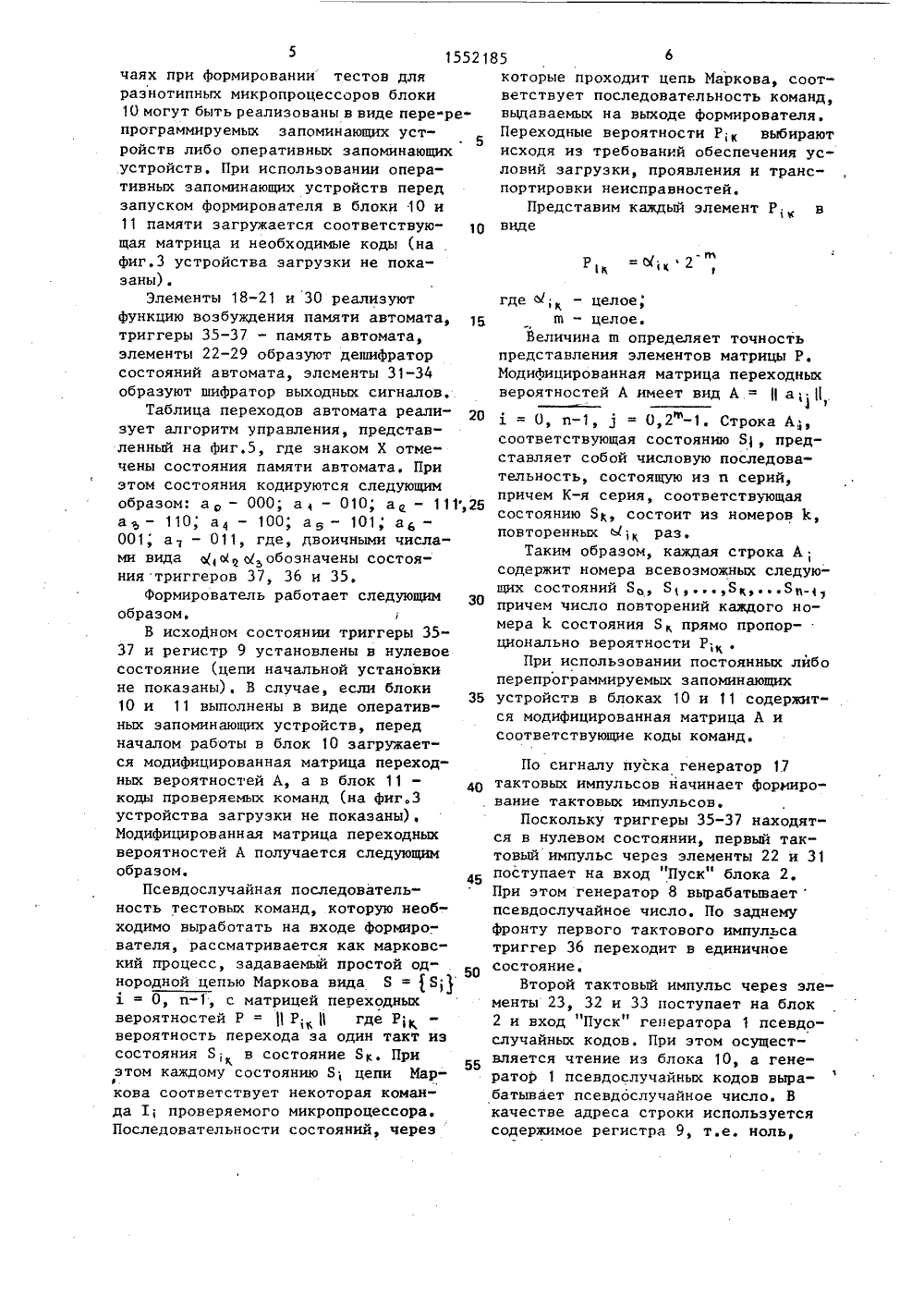

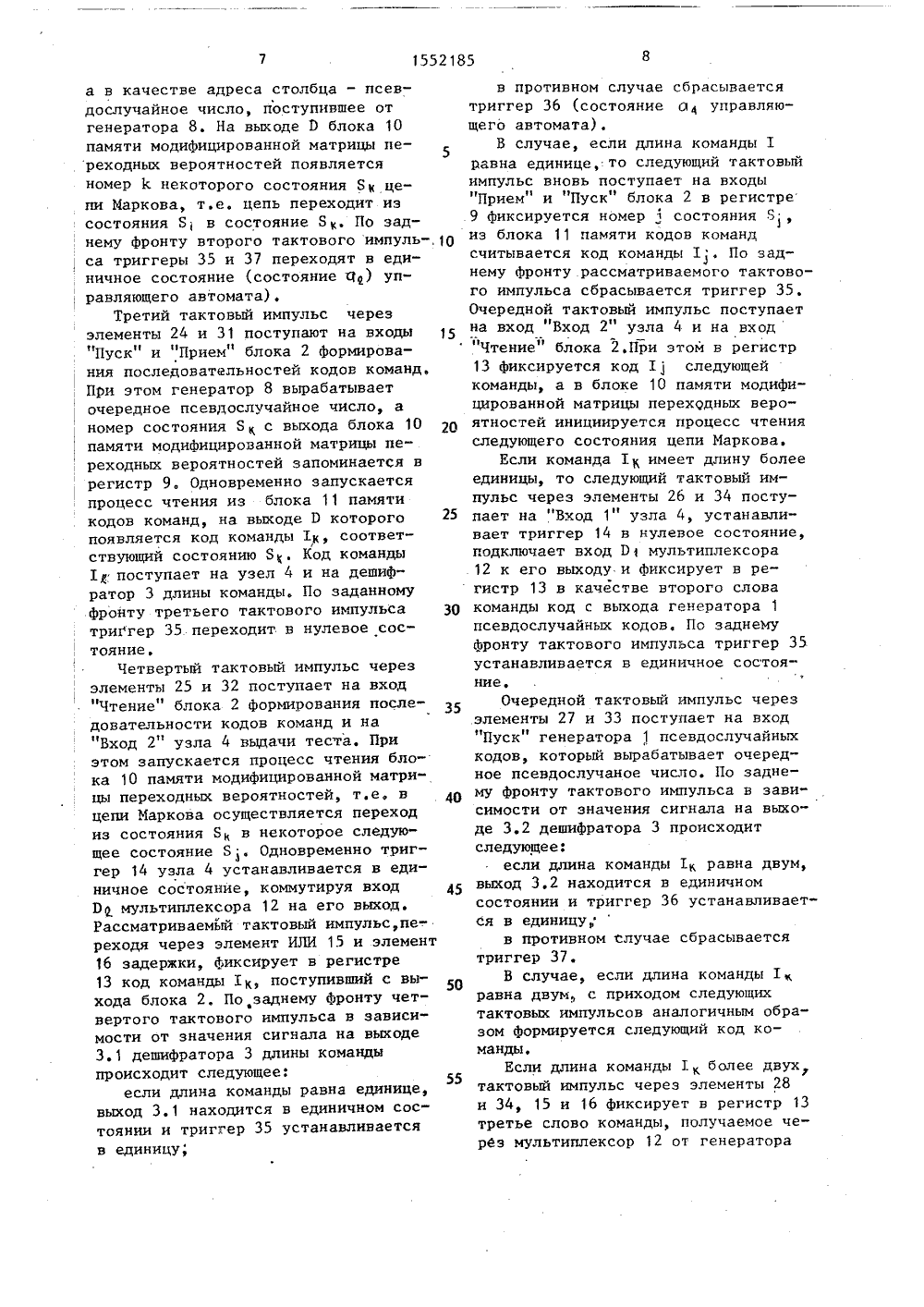

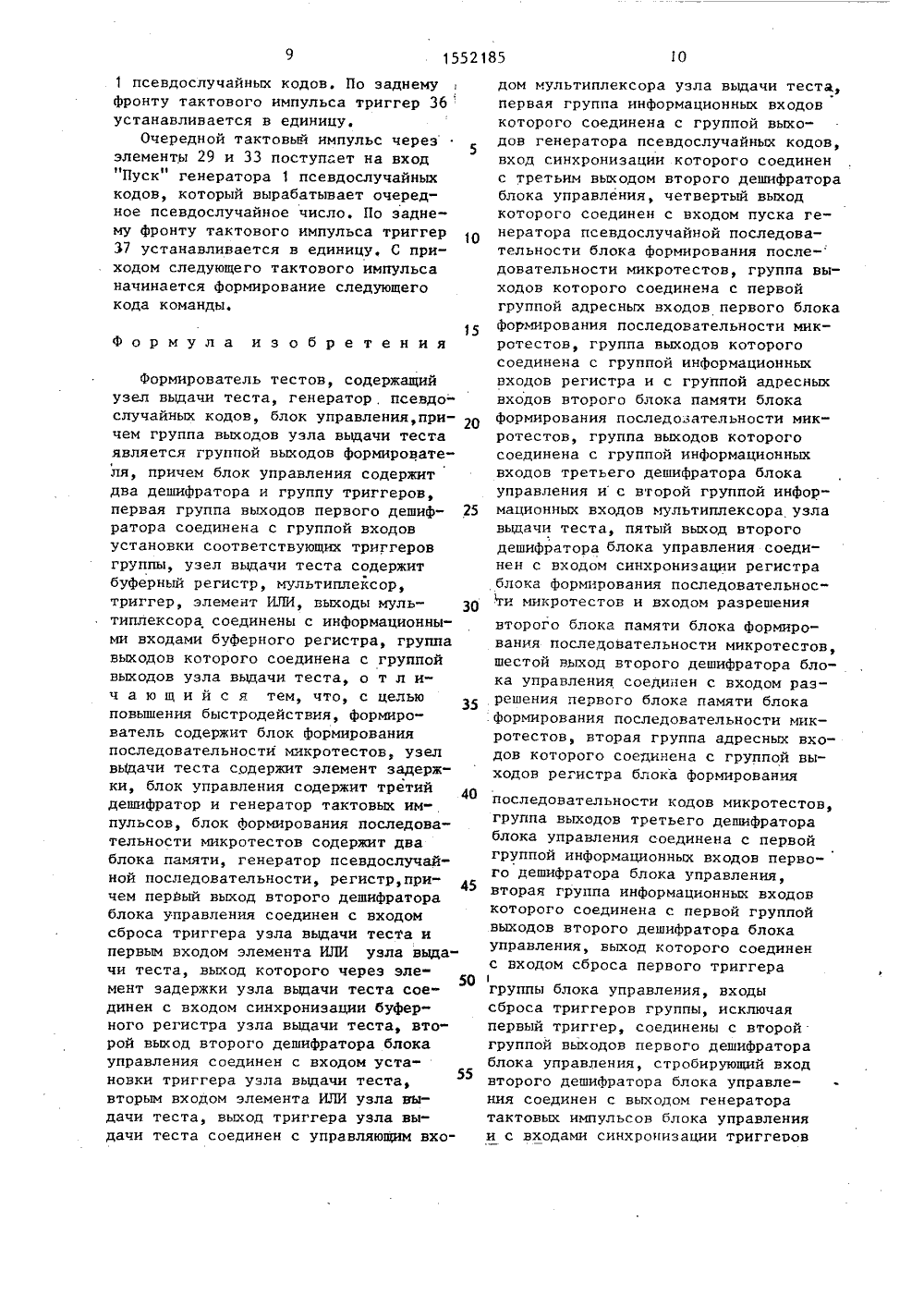

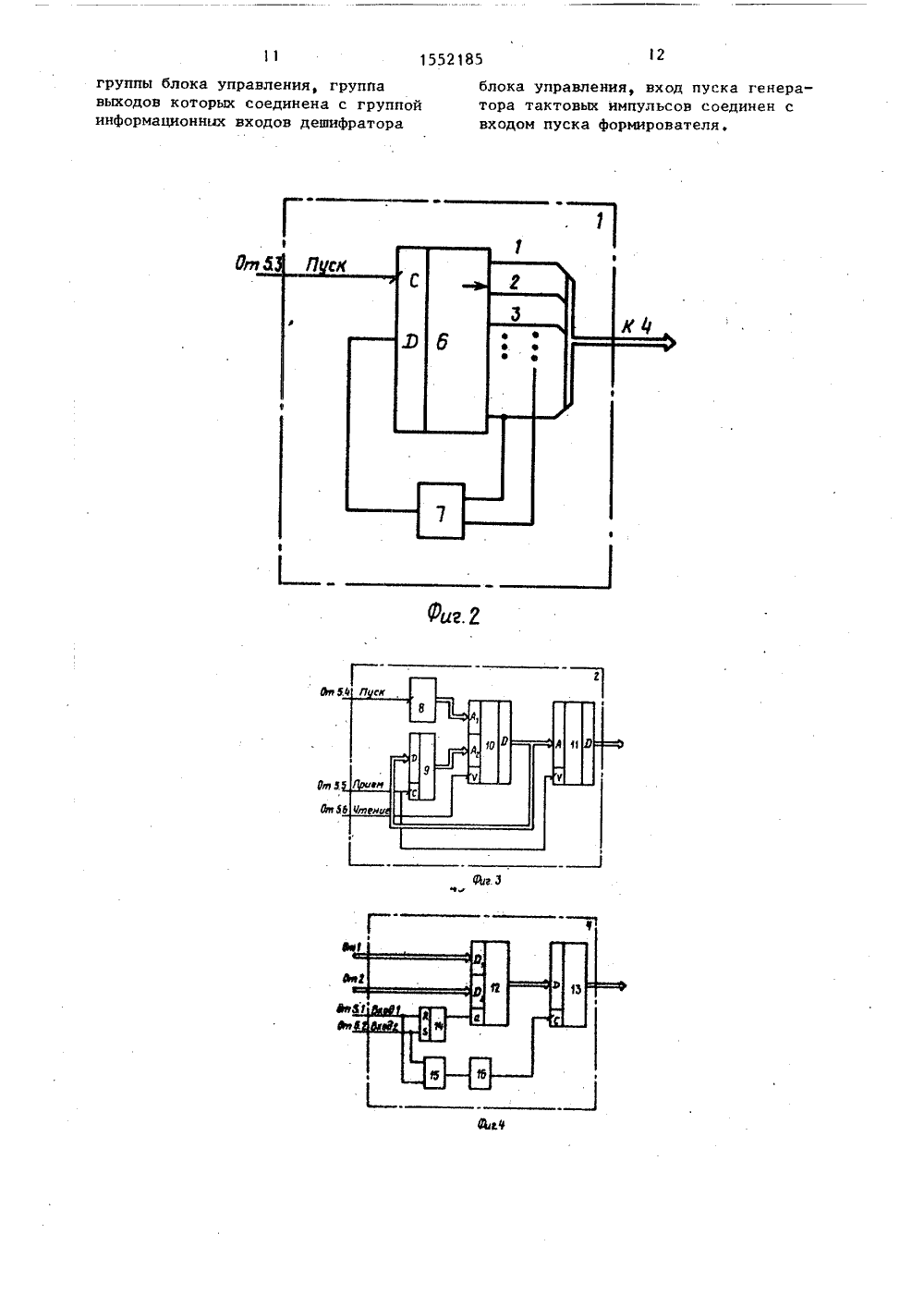

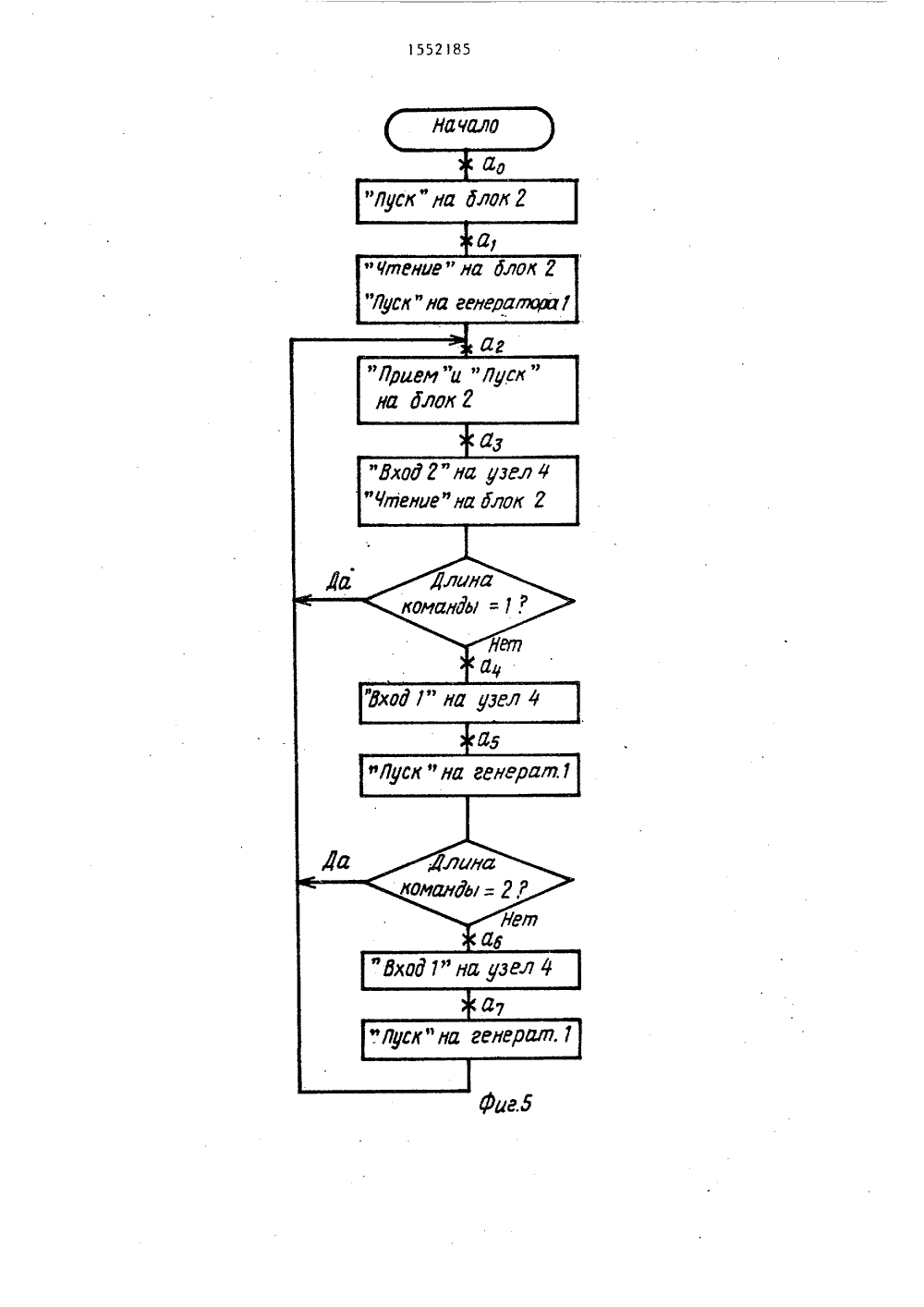

СОЮЗ СОВЕТСНИ ОЦИАЛИСТИЧЕСНРЕСПУБЛИН 9) 111 1) 5 С 06 Р 11/26/4 С НИ ническ С.М. Андрони ьство СССР1/26, 1981.тво СССР1/26, 1985. ОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯПРИ ГННТ СССР А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1(57) Изобретение относится к автоматике и вычислительной технике иможет быть использовано в устройствах контроля. Цель изобретения -повышение быстродействия. Формирователь содержит узел 4 выдачи теста,генератор 1 псевдослучайных кодов,блок управления 5, блок 2 формирования последовательности микротестов и дешифратор 3, 7 ил.Изобретение относится к автоматике и вычислительной технике и можетбыть использовано в устройствахконтроля5Цель изобретения - повышение быстродействия.На Фиг.1 представлена структурнаяхема формирователя; на Фиг.2 - схеа генератора псевдослучайных кодов;а фиг,З - схема блока формированияпоследовательности микротестов, наиг.4 - схема узла выдачи теста,.наиг,5 - блок-,схема работы блока упиавления, на Фиг.б - схема блока упавления, на Фиг.7 - временные диагаммы работы формирователя.Формирователь тестов содержит генератор 1 псевдослучайных кодов, блокФормирования последовательностимикротестов, дешифратор 3 длины коИанды, узел 4 выдачи теста, блок 5правления.В генераторе (Фиг,2) используетсясдвиговый регистр 6 и сумматор 7 помодулю два,Блок 2 (фиг.З) содержит генератор8 псевдослучайной последовательности,регистр 9, блок 10 памяти модифицированной матрицы переходных вероятностей и блок 11 памяти кодов команд.Узел 4 выдачи теста (фиг,4) предназначен для формирования очередногослова команды и состоит из мультиплексора 12, буферного регистра 13,триггера 14, элемента ИЛИ 15 и элемента 16 задержки.Блок 5 управления (фиг.5) представляет собой синхронный управляющийавтомат с множеством внутренних сос 40тояний ааа 7 и содержитгенератор 17 тактовых импульсов, элементы И-ИЛИ 18 и 19, элементы И 2029, элементы ИЛИ 30-34 и триггеры35-37, Причем элементы 18-21, 30образуют дешифратор, элементы 22-29и 31-34 образуют шифратор.Генератор 1 псевдослучайных кодовпредназначен для генерации случайных чисел, используемых в качестве50второго, третьего,и т,д слова команды, т.е. в качестве адресов и данных.В простейшем случае он может бытьреализован на сдвиговых регистрах собратными связями,55Блок 2 Формирования последовательности микротестов предназначендля формирования первого слова ко"манды. Формируемые слова образуют псевдослучайную последовательность,в которой вероятность появленияочередного кода команды зависит оттого, какой код команды выдавалсяв предыдущем такте. Стохастическиесвойства указанной последовательности определяются матрицей переходныхвероятностей цепи Маркова.Дешифратор 3 предназначен дляопределения структуры формируемой команды. На вход дешифратора поступаетпервое слово команды, а на его д-мвыходе, где х - длина дешифруемойкоманды, появляется сигнал логической единицы, Дешифратор имеетвыходов,= 1-1,где 1 - максимальновозможная длина команды),Генератор 8 псевдослучайных чиселвырабатывает равномерно распределенные числа. В простейшем случае онможет быть реализован по той жесхеме, что и генератор 1 (фиг,2). Приподаче на вход генератора 8 сигналаПуск на его выходе появляется псевдослучайное число. Очередное псевдослучайное число вырабатывается при11 11подаче следующего сигнала Пуск ит.д.Регистр 9 предназначен для хранения номера текущего состояния (адреса строки) цепи Маркова. Блок 10памяти модифицированной матрицыпереходных вероятностей представляетсобой двухмерный массив из 1 1 оц,вразрядных слов, где и - число состояний цепи Маркова. Число и состоянийцепи определяется числом команд микропроцессора, для проверки которыхнеобходимо сформировать соответствующий тест. Адресация слова осуществляется путем указания номера строки врегистре 9 (вход Ар) и номера столбца на выходе генератора 8 (вход А).Число строк блока 10 памяти модифицированной матрицы переходных вероятностей равно и, а число столбцов2, где ш определяется способом представления переходных вероятностейР;в виде Р= с;2, ;целое,В простейшем случае блок 10и блок 11 - постоянные запоминающиеустройства, содержащие соответствующую матрицу и коды. Мультиплексор12 в зависимости от значения сигнала на его управляющем входе передает на выход либо данные с входаО, ( .а = О), либо данные с входа0( О = 1). В более сложных слу5 15521чаях при формировании тестов дляразнотипных микропроцессоров блоки10 могут быть реализованы в виде пере "репрограммируемых запоминающих уст 5ройств либо оперативных запоминающихустройств. При использовании оперативных запоминающих устройств передзапуском формирователя в блоки 10 и11 памяти загружается соответствующая матрица и необходимые коды (нафиг.3 устройства загрузки не показаны),Элементы 18-21 и 30 реализуютфункцию возбуждения памяти автомата,триггеры 35-37 - память автомата,элементы 22-29 образуют дешифраторсостояний автомата, элементы 31-34образуют шифратор выходных сигналов,Таблица переходов автомата реализует алгоритм управления, представленный на фиг.5, где знаком Х отмечены состояния памяти автомата. Приэтом состояния кодируются следующимобразом: а- 000; а- 010; ар - 111;25аь - 110; а 4 - 100; ав - 101; а -001; а - 011, где, двоичными числами вида о(,Ы о обозначены состояния триггеров 37, 36 и 35.Формирователь работает следующим ЗОобразом.В исходном состоянии триггеры 3537 и регистр 9 установлены в нулевоесостояние (цепи начальной установкине показаны). В случае, если блоки3510 и 11 выполнены в виде оперативных запоминающих устройств, передначалом работы в блок 1 О загружается модифицированная матрица переходных вероятностей А, а в блок 11коды проверяемых команд (на фиг.3устройства загрузки не показаны),Модифицированная матрица переходныхвероятностей А получается следующимобразом.Псевдослучайная последовательность тестовых команд, которую необходимо выработать на входе формирователя, рассматривается как марковс"кий процесс, задаваемый простой од- .нородной цепью Маркова вида Б = (Яд = О, п, с матрицей переходныхвероятностей Р = 11 Р; 11 где Рк,вероятность перехода за один такт изсостояния Я; в состояние Як. Приэтом каждому состоянию Б; цепи Мар 55кова соответствует некоторая команда 1; проверяемого микропроцессора.Последовательности состояний, через 85 6которые проходит цепь Маркова, соответствует последовательность команд,выдаваемых на выходе формирователя.Переходные вероятности Р; выбираютисходя из требований обеспечения условий загрузки, проявления и транспортировки неисправностей,Представим каждый элемент Р; ввидеРк ок2где Ы;к - целое,щ - целое.Величина ш определяет точностьпредставления элементов матрицы Р.Модифицированная матрица переходныхвероятностей А имеет вип А. 11 а й= О, п, З = 0,2 -1. Строка А;,Фсоответствующая состоянию Б 1, представляет собой числовую последовательность, состоящую из и серий,причем К-я серия, соответствующаясостоянию Бк, состоит из номеровповторенных Ы;к раз.Таким образом, каждая строка А;содержит номера всевозможных следуюШИХ СОСтояНИЙ Ят,р БррБКрБб причем число повторений каждого номера 1 состояния Бпрямо пропорционально вероятности Р;,При использовании постоянных либоперепрограммируемых запоминающихустройств в блоках 10 и 11 содержится модифицированная матрица А исоответствующие коды команд.По сигналу пуска генератор 17 тактовых импульсов йачинает формирование тактовых импульсов.Поскольку триггеры 35-37 находятся в нулевом состоянии, первый тактовый импульс через элементы 22 и 31 поступает на вход "Пуск" блока 2.При этом генератор 8 вырабатываетпсевдослучайное число. По заднему фронту первого тактового импульса триггер 36 переходит в единичное состояние.Второй тактовый импульс через элементы 23, 32 и 33 поступает на блок 2 и вход "Пуск" генератора 1 псевдо" случайных кодов. При этом осуществляется чтение из блока 10, а генератор 1 псевдослучайных кодов вырабатывает псевдослучайное число. В качестве адреса строки используется содержимое регистра 9, т.е, ноль, 1552185а в качестве адреса столбца - псевдослучайное число, поступившее от генератора 8. На выходе 0 блока 10 памяти модифицированной матрицы переходных вероятностей появляется номер К некоторого состояния Би цепи Маркова, т.е. цепь переходит из состояния Б; в состояние Б . По заднему Фронту второго тактового импульса триггеры 35 и 37 переходят в единичное состояние состояние 4) управляющего автомата).Третий тактовый импульс через элементы 24 и 31 поступают на входы "Пуск" и "Прием" блока 2 Формирования последовательностей кодов команд, При этом генератор 8 вырабатывает очередное псевдослучайное число, а номер состояния Бс выхода блока 10 памяти модифицированной матрицы переходных вероятностей запоминается в регистр 9. Одновременно запускается процесс чтения из блока 11 памяти кодов команд, на выходе Э которого появляется код команды 1 к, соответствующий состоянию Б. Код команды 1 поступает на узел 4 и на дешифратор 3 длины команды, По заданному фронту третьего тактового импульса триггер 35 переходит в нулевое состояние.Четвертый тактовый импульс через элементы 25 и 32 поступает на вход "Чтение" блока 2 формирования последовательности кодов команд и на "Вход 2" узла 4 выдачи теста. При этом запускается процесс чтения блока 10 памяти модифицированной матри" цы переходных вероятностей, т.е, в цепи Маркова осуществляется переход из состояния Б в некоторое следующее состояние Б . Одновременно триггер 14 узла 4 устанавливается в единичное состояние, коммутируя вход Э мультиплексора 12 на его выход. Рассматриваемйй тактовый импульс,переходя через элемент ИЛИ 15 и элемент 16 задержки, Фиксирует в регистре 13 код команды 1, поступивший с выхода блока 2, По заднему Фронту четвертого тактового импульса в зависи" мости от значения сигчала на выходе 3.1 дешифратора 3 длины команды происходит следующее:если длина команды равна единице, выход 3.1 находится в единичном состоянии и триггер 35 устанавливается в единицу, в противном случае сбрасываетсятриггер 36 (состояние а управляющего автомата),В случае, если длина команды 1равна единице, то следующий тактовыйимпульс вновь поступает на входы"Прием" и "Пуск" блока 2 в регистре9 фиксируется номер 1 с.остояния Б 10 из блока 11 памяти кодов командсчитывается код команды 1, По зад 3нему Фронту рассматриваемого тактового импульса сбрасывается триггер 35,Очередной тактовый импульс поступает 15 20 25 30 35 40 45 50 55 на вход "Вход 2" узла 4 и на вход"Чтение" блока 2.При этом в регистр13 Фиксируется код 1 следующейкоманды, а в блоке 10 памяти модифицированной матрицы переходных вероятностей инициируется процесс чтенияследующего состояния цепи Маркова.Если команда 11 имеет длину болееединицы, то следующий тактовый импульс через элементы 26 и 34 поступает на "Вход 1" узла 4, устанавливает триггер 14 в нулевое состояние,подключает вход Э 1 мультиплексора12 к его выходу и Фиксирует в регистр 13 в качестве второго словакоманды код с выхода генератора 1псевдослучайных кодов. По заднемуфронту тактового импульса триггер 35устанавливается в единичное состояние,Очередной тактовый импульс черезэлементы 27 и 33 поступает на вход"Пуск" генератора 1 псевдослучайныхкодов, который вырабатывает очередное псевцослучаное число, По заднему фронту тактового импульса в зави"симости от значения сигнала на выходе 3,2 дешифратора 3 происходитследующее:если длина команды 1 равна двум,выход 3,2 находится в единичномсостоянии и триггер 36 устанавливает"ся в единицув противном случае сбрасываетсятриггер 37,В случае, если длина команды 1равна двум с приходом следующихтактовых импульсов аналогичным образом формируется следующий код команды.Если длина команды 1более двухтактовый импульс через элементы 28и 34, 15 и 16 фиксирует в регистр 13третье слово команды, получаемое через мультиплексор 12 от генератора1 псевдослучайных кодов. По заднему фронту тактового импульса триггер Збустанавливается в единицу.Очередной тактовый импульс через элементы 29 и 33 поступает на вход "Пуск" генератора 1 псевдослучайных кодов, который вырабатывает очередное псевдослучайное число. По заднему фронту тактового импульса триггер З 7 устанавливается в единицу, С приходом следующего тактового импульса начинается формирование следующего кода команды.5Формула изоСретения Формирователь тестов, содержащийузел выдачи теста, генератор, псевдослучайных кодов, блок управления,причем группа выходов узла выдачи тестаявляется группой выходов формирователя, причем блок управления содержитдва дешифратора и группу триггеров,первая группа выходов первого дешифратора соединена с группой входовустановки соответствующих триггеровгруппы, узел вьдачи теста содержитбуферный регистр, мультиплексор,триггер, элемент ИЛИ, выходы мультиплексора соединены с информационными входами буферного регистра, группавыходов которого соединена с группойвыходов узла выдачи теста, о т л ич а ю щ и Й с я тем, что, с целью 35повышения быстродействия, формирователь содержит блок формированияпоследовательности микротестов, узелвыдачи теста содержит элемент задержки, блок управления содержит третий 4 Одешифратор и генератор тактовых импульсов, блок формирования последовательности микротестов содержит дваблока памяти, генератор псевдослучайной последовательности, регистр,причем перйый выход второго дешифратораблока управления соединен с входомсброса триггера узла выдачи теста ипервым входом элемента ИЛИ узла выдачи теста, выход которого через элемент задержки узла выдачи теста соединен с входом синхронизации буферного регистра узла выдачи теста, второй выход второго дешифратора блокауправления соединен с входом установки триггера узла вьдачи теста,55вторым входом элемента ИЛИ узла выдачи теста, выход триггера узла выдачи теста соединен с управляющим входом мультиплексора узла выдачи теста, первая группа информационных входов которого соединена с группой выходов генератора псевдослучайных кодов, вход синхронизации которого соединен с третьим выходом второго дешифратора блока управления, четвертый выход которого соединен с входом пуска генератора псевдослучайной последовательности Слока формирования после- довательности микротестов, группа выходов которого соединеча с первой группой адресных входов первого блока формирования последовательности микротестов, группа выходов которого соединена с группой информационных входов регистра и с группой адресных входов второго блока памяти Слока формирования последозательности микротестов, группа выходов которого соединена с группой информационных входов третьего дешифратора блока управления и с второй группой информационных входов мультиплексора узла выдачи теста, пятый выход второго дешифратора блока управления соединен с входом синхронизации регистра блока формирования последовательности микротестов и входом разрешениявторого блока памяти блока формирования последовательности микротестов, шестой выход второго дешифратора Слока управления соединен с входом разрешения первого Слока памяти блока формирования последовательности микротестов, вторая группа адресных входов которого соединена с группой выходов регистра блока формированияпоследовательности кодов микротестов,группа выходов третьего дешифратора блока управления соединена с первой группой информационных входов первого дешифратора блока управления, вторая группа информационных входон которого соединена с первой группой выходов второго дешифратора блока управления, выход которого соединен с входом сброса первого триггера 1группы блока управления, входы сброса триггеров группы, исключая первый триггер, соединены с второй группой выходов первого дешифратора блока управления, строСирующий вход второго дешифратора блока управления соединен с выходом генератора тактовых импульсов блока управления и с входами синхронизации триггеровгруппы блока управления, группавыходов которых соединена с группойинформационных входов дешифратора блока управления, вход пуска генератора тактовых импульсов соединен свходом пуска формирователя.1552185 Составитель А, Сиротскаяактор В, Петраш Техред Л,Олийнык Корректо Бкун КН Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 1 аказ 331 ТиражНИИПИ Гасударственного коми113035, Моск 3та по из Ж,Подписноеретениям и открытиям лрушская наб., д, 4/5

СмотретьЗаявка

4332851, 25.11.1987

КИШИНЕВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. С. ЛАЗО

ГРЕМАЛЬСКИЙ АНАТОЛИЙ АЛЕКСАНДРОВИЧ, АНДРОНИК СЕРГЕЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 11/26

Метки: тестов, формирователь

Опубликовано: 23.03.1990

Код ссылки

<a href="https://patents.su/8-1552185-formirovatel-testov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь тестов</a>

Предыдущий патент: Устройство для контроля цифровых узлов

Следующий патент: Устройство для контроля хода программ

Случайный патент: Способ получения бутенов