Устройство моделирования функционирования цифровой радиоэлектронной аппаратуры

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1501031

Авторы: Гришин, Заславский, Капралов, Коновалов, Овечкин, Ольшанский

Текст

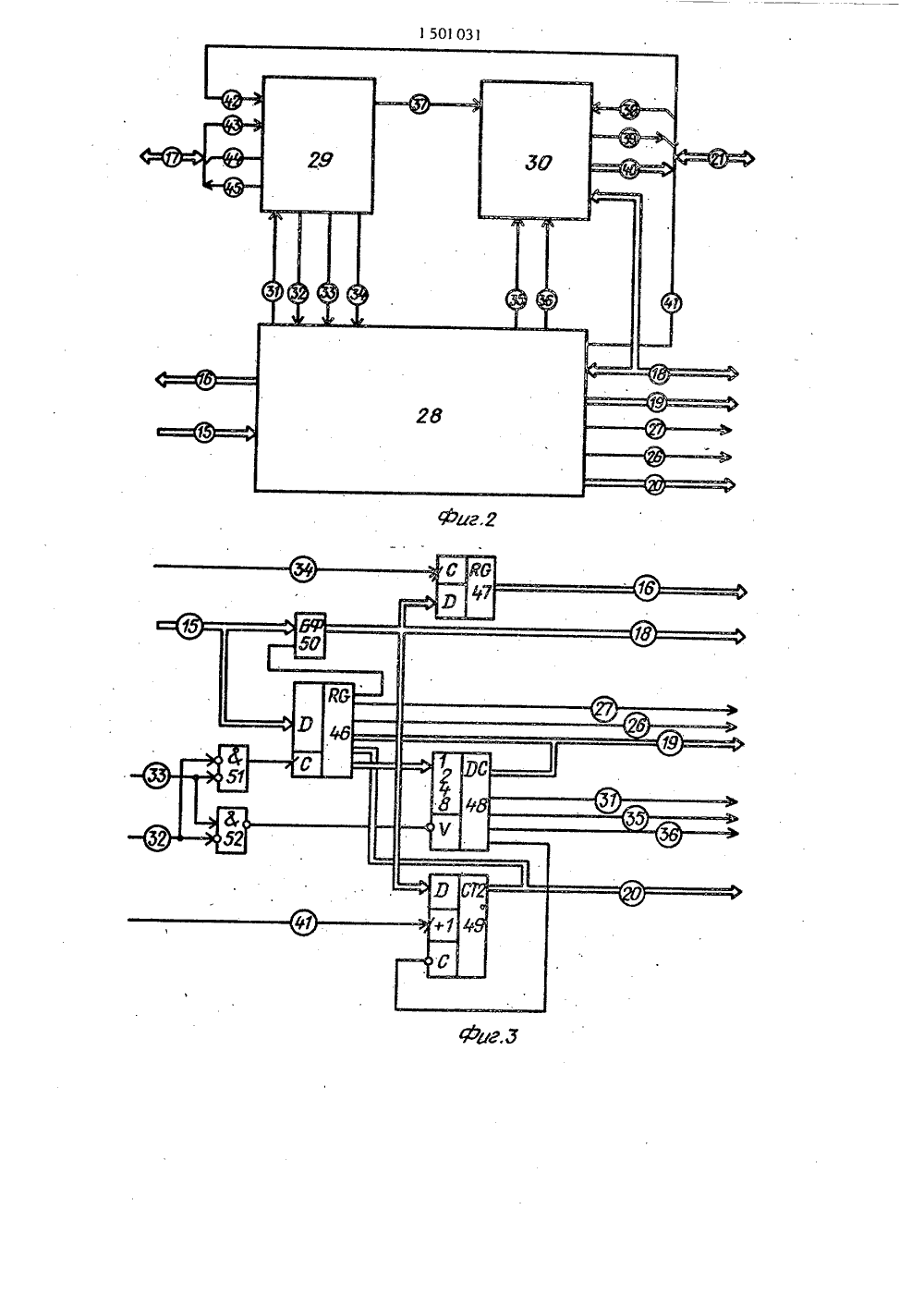

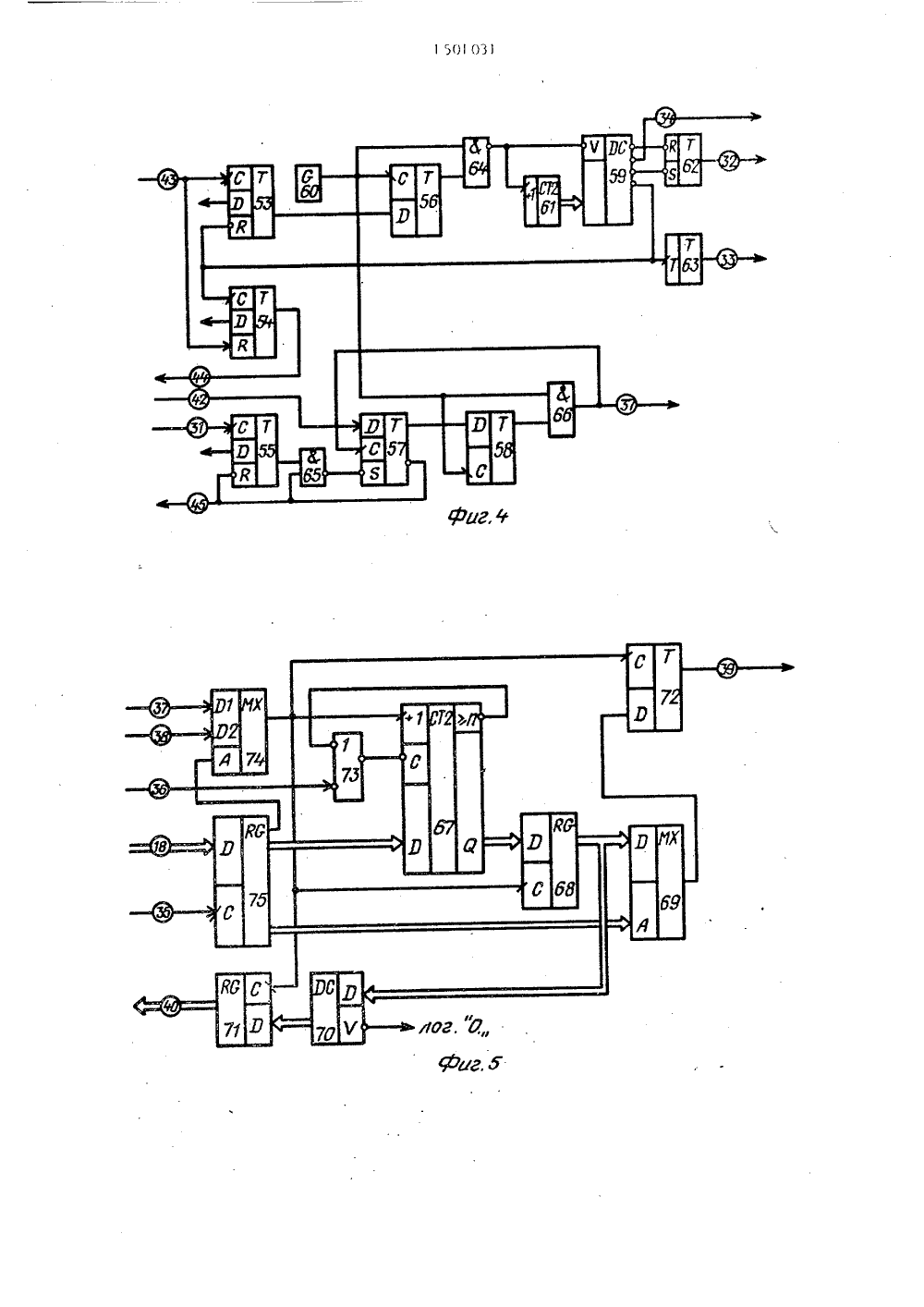

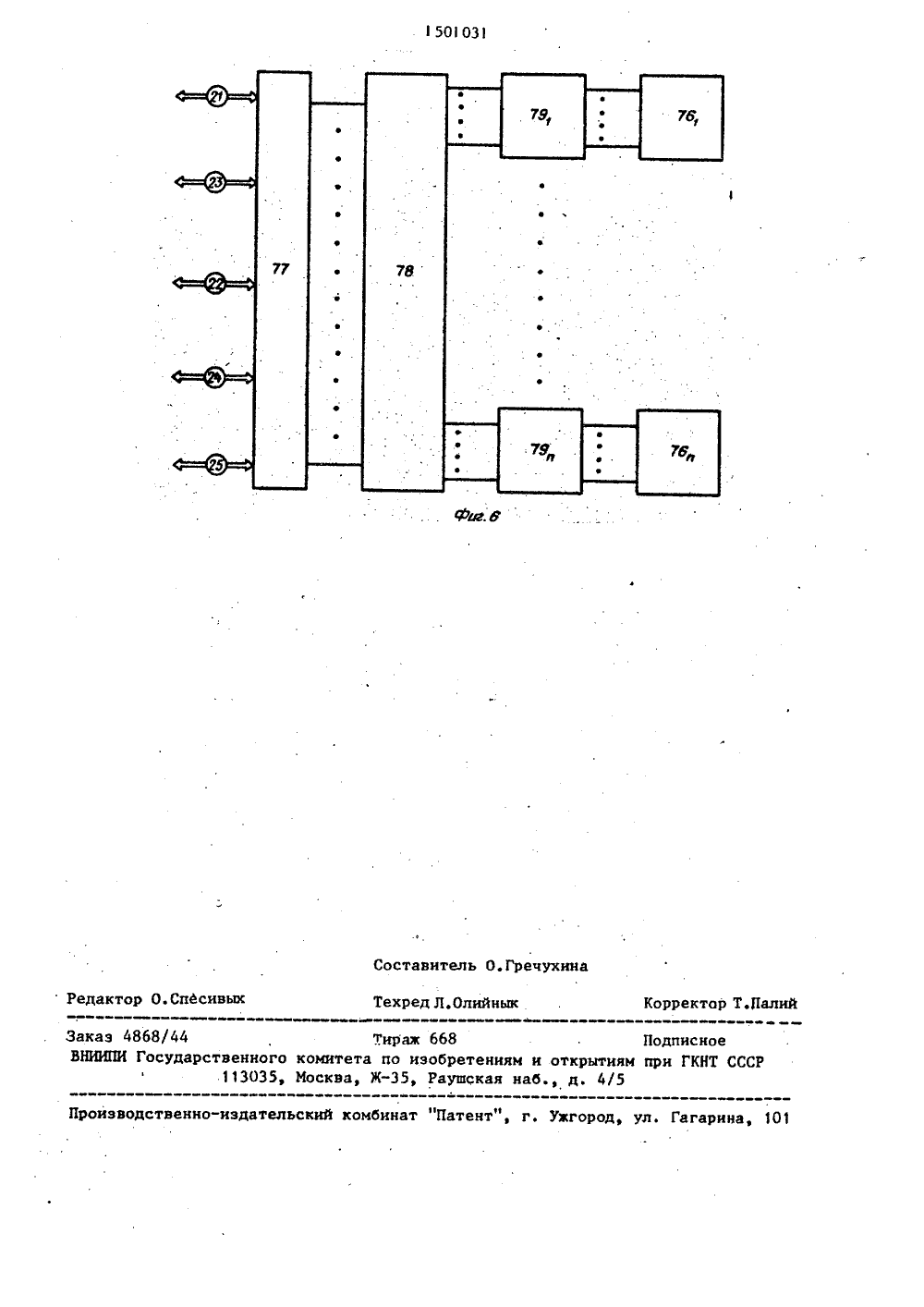

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 09 Р 7 0 ПИСАНИЕ ИЗОБРЕТЕН 0 прало новалов,ришин ии У 130670 тво СССР О, 1975,Р 4 ИЯ ФУНК- ЭЛЕКТРОН ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЧНРЫТИЯМПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВ 306402/24-244,07,865,08,89. Бюл. Р(54) УСТРОЙСТВО МОДЕЛИРЦИОНИРОВАНИЯ ЦИФРОВОЙНОЙ АППАРАТУРЫ (РЭА) 157) Изобретение относится к вычислительной технике и может быть использовано для моделирования схемотехнических решений цифровой РЭА, в томчисле микропроцессорной, а также дляпроектирования заказных и полузаказных БИС и СВИС. Цель изобретения - расширение функциональных возможностейустройства -достигается тем, что вустройство, содержащее блок памяти 1и блок управления 11, дополнительновведены блоки памяти 2-5, пять мультиплексоров 6-10, операционный вычислительный блок 12, блок буферных зле.ментов 13 и блок связи 14. 6 ил.150103 Изобретение относится к областивычислительной техники и может быть использовано для моделирования схемотехнических решений циАровой РЭА, в 5том числе микропроцессорной, а такжедля проектирования заказных и полузакаэных БИС, СБИС,Цель изобретения - раг,гирение Аункциональных возможностей устройства 10за счет возможности моделирования заказных и полузаказных БИС и повышение достоверности моделирования,На Фиг.1 представлена блок-схемаустройства моделирования циАровой 15РЭА; на фиг,2 - блок-схема блока управления; на Аиг.3 - Аункциональнаясхема блока обмена; на Фиг,4 - Аункциональная схема блока синхронизации;на фиг.5 - функциональная схема блока задания временной диаграммы; нафиг,б - блок-схема блока связи,Устройство моделирования циАровойРЭА (Фиг,1) содержит с первого по пятый блоки памяти 1-5, с первого попятый мультиплексоры 6-10, блок управления 11,операционный вычислительный блок 12, блок буАерных 13 элементов, блок 14 связи.Операционный вычислительный блок12 представляет собои управляющуюмикроЭВМ, например "Электроника". На Аиг,1 обозначены инАормационные шины и связи между блоками 15-27, 35Блок 11 управления (Фиг.2) предназначен для Формирования сигналов управ,ления для аппаратуры. системы в соответствии с управляющими воздействиями из блока 12 либо из моделируемого устрой" 40 ства, а также для организации обмена информацией между блоком 12, блоками устройства моделирования цифровой РЭА и моделируемого устройства. Блок 11 управления состоит из блока 28 обме на,блока 29 синхрочастот, блока 30/задания временной диаграммы. Позициями 31-45 обозначены связи между эти" ми блоками.Блок 28 обмена (Фиг,З) предназначен для организации обмена информацией между блоком 12 и блоками 1-5 памяти, а также он определяет один из двух режимов работы блоков памяти: работа с блоком 12 или работа с моделируемым устройством, размещенным в блоке 14 связи.Блок 28 обмена состоит из регистра 46 инструкций, буферного регистра 47,1 4дешифратора 48 инструкцией, счетчика49 адреса буферных усилителей 50,элемента ИЛИ-НЕ 51 и элемента И 52.Блок 29 синхрочастот (Аиг,4)предназначен для Формирования сигналов управления блоками 28 и 30, атакже сигналов управления обменом сблоком 12.Блок 29 синхрочастот состоит изтреггера ПУСК 1 53, триггера 54 готовности, триггера ПУСК 2 55, первоготриггера 56 синхронизации, триггера57, останова, второго триггера 58синхронизации,дешифратора 59 управления,генератора 60 импульсов, счетчика 61 импульсов, триггера 62 длительности триггера 63 управления,элементов И - НЕ 64,65, элементаИ 66,Блок 30 задания временной диаграммы (Аиг,5) предназначен для организации временной диаграммы, заданной дляконкретного моделируемого устройства,размещенного в блоке 14 связи.Блок 30 состоит иэ счетчика 67 импульсов, первого буАерного регистра68, мультиплексора 69, дешифратора70 импульсов, второго буферного регистра 71, триггера 72 такта элемента И 73, мультиплексора 74 частотырвгистра 75 управления,Блок 11 управления работает следующим образом, В результате начальнойустановки триггер ПУСК 1 53, триггерПУСК 2.55, первый триггер 56 синхронизации;триггер 57 останова,второйтриггер 56 синхронизации, триггер57, останова второй триггер 58, синхронизации,счетчик 61 импульсов,триггер 63 управления, устанавливаются всостояние "0", триггер 54 готовности,триггер 62 длительности устанавлива-ются в состояние "1",С целью упрощения Аункциональнойсхемы цепи начальной установки условно не показаны,В результате начальной установкиотсутствуют передача синхрочастотыиз генератора 60 импульсов по шине37 на мультиплексор 74 частоты, Таким образом управляющие сигналы, поступающие по шине 39 и магистрали 40,через магистраль 21 управления вблок 14 связи, не ФормируютсяПо положительному Фронту сигнала,поступающего по шине 43 через магистраль 17 управлени- блока 12,.1501031 Регистр 46 инструкций по сссиссе 27управляет работой бусссерньсх элементов13,Кроме того, регистр 46 инструкцийустанавливает управляющие сигналы наблоки 1,3,4,5 памяти и распределяетмежду ними через дешифратор 48 инструкций по магистрали 19 управленияПри поступлении по спине 42, подключенной к магистрали 21 управления"0", на вход триггера 57 останова запрещается передача синхрочастоты изгенератора 60 импульсов через элементИ на шину 37 и далее на мультиплексор 74 частоты, что приводит к останову временной диаграммы, формируемой блоком 30. Одновременно с инверсного выхода триггера 57 останова пошине 45 формируется управляющий сигнал, предназначенный для блока 12,Запуск блока временной диаграммыосуществляется сигналом, поступающимпо шине 31 на вход триггера ПУСК 1из дешифратора 48 инструкций. По управляющему сигналу, поступающему издешифратора 48 инструкций по шине 35,информация магистрали 18 записываетсяв регистр 75 управления. Содержимое регистра 75 управления управляет работоймультиплексора 74 частоты, а также задает длнтельностьи форму управляющегосигнала, поступающего по шине 39 через магистраль 21 управления в блок14 связи, и определяет число активных управляющих сигналов, поступающих по магистрали 40 через магистраль21 управления в блок 14 связи.Сигнал, поступаюс:;ий по шике 36,подключенный к выходу дешифратораинструкций, производит предварительную загрузку счетчика импульсов информацией из регистра 75 управления,На мультиплексор частоты 74 кромесинхрочастоты генератора 60 импульсов, поступающей по шине 37 из блока29 синхрочастот, по шине 38 можетпоступить синхрочастота иэ блока 14связи.Блок 14 связи предназначен для установки элементов моделирования,ор.ганизации электрических связей межпуними в соответствии с принципиальнойсхемой моделируемого устройства, атакже для подключения моделируемогоустройства к блокам устройства моделирования цифровой РЭА,Блок 14 связи состоит из группыкоммутационных элементов 76, группыгнездовых разъемов 77 связи, а также триггер ПУСК 1 53 устанавливается всостояние "1", что приводит к появлению на шинах 32-34 управляющих сигналов, Одновременно происходит снятие сигнала готовности, поступающегопо шине 44 через магистраль 17 управления,Информация, поступающая из блока12 по информационной магистрали 15, 10записывается отрицательным фронтомсигнала по шине 32 в регистр 46 инструкций.1 икл обмена между блоком 12 и блоком 11 управления завершается переключением в исходное состояние триггера ПУСК 1 53, триггера 54 готовности, триггера 63 управления.Управляющий сигнал, поступающийиз регистра 46 инструкций по шине 26 20на мультиплексоры 6-10,определяет режим работы блоков 1, 2,4,5 памяти - сблоком 12 или смоделируемым устройством, размещенным в блоке 14 связи,В режиме работы блок 12 - блоки 1-5 25памяти обмен информацией между нимиосуществляется через блок 11 управленияСодержимое регистра 46 инструкцийопределяет направление обмена междублоком 12 и блоками 1-5 памяти, Запись информации осуществляется помагистрали 15 через буферные усилители 50, имеющие выходы с тремя состояниями на информационную магистраль 18При чтении информации, поступающей по магистрали 18, выходыбуферных усилителей отключены в третье состояние сигналом из регистра46 инструкций. Информация записьсвается в буферной регистр 47 по переднему фронту сигнала, поступающего издешифратора 59 управления по шине 34,В блок 12 информация считывается избуферного регистра 47 по магистрали 4516.Информация, поступающая по магистрали 18, может быть записана в счетчикадреса блока 2 памяти по низкому уровню сигнала, поступающего из дешифратора 48 и нструкций. Кроме того состояние счетчика 49 адреса блока 2 намяти может инкрементироваться сигналом, поступающим по.шине 41, через магистраль 21 иэ блока связи 14.Сигналы, поступающие по магистрали20 иэ регистра 46 инструкций и счетчика адреса блока 2 памяти, образуют,управление блоком 2 памяти.перенастраиваемого двунаправленногокоммутатора 78, группы гнездовых разьемов 79 связи,Коммутационные элементы 76 предназ. 5начейы для установки в них элементовмоделирования, которыми могут являтьсякак стандартные интегральные микросхемы так и многофункциональные модули, Каждый вывод коммутационных элементов 76 электрически связан с соответствующими контактами соответствующего гнездового разъема 79 связи,Связь блока 14 связи с остальнымиблоками устройства моделирования цифровой РЭА, а также с внешними устройствами осуществляется через группугнездовых разъемов 77, соответствующие контакты которых электрически связаны с магистралями системы моделирования циАровой РЭА и с внешними устройствами (Аиг.1),4 Перенастраеваемый двунаправленный коммутатор 78 осуществляет передачу сигналов между группами разъемов7 и 79 связи в соответствии с принципиальной схемой моделируемого устройства. Перенастраиваемый двунаправленный коммутатор может быть выполненв виде набора проводников с однополюсными вилками,Процесс моделирования в устройстве моделирования циАровой РЭА происходит следующим образом. В коммутационные элементы 76 устанавливаютсяэлементы моделирования данного цифрового устройства, Связи между элементами моделирования осуществляютсяпосредством коммутатора 78 в соответствии с электрической принципиальнойсхемой моделируемого устройства,Внешние сигналы моделируемого устройства через двунаправленный перенастраиваемый коммутатор и группу разъе мов 77 связи могут быть подключены кмагистрали устройства моделированияциАровой РЭА.В устройстве моделирования Цифровой РЭА блоки памяти могут выполнятьроль эммулирующих ЗУ. Например, блок1 памяти - ЗУ микрокоманд (ЗУМК);блок 2 памяти - трассирующее ЗУ (ТЗУ);блок 3 памяти - ЗУ данных (ЗУД);блок 4 памяти - ЗУ команд (ЗУК);блок 5 памяти - ЗУ переадресации (ЗУП).Устройство моделирования цифровойРЭА работает следующим образом. Управляющие сигналы на блоки 1, 3,4,5, памяти могут поступать как излока 11 управления, так и из моделируемого устройства, расположенного в блоке 14 связи. Выбор источников сигналов управления осуществляется мультиплексорами 6,8,9,10сигналом., поступающим по шине 26,ИнАормация в блоки 1,4,5 памятипоступает по инАормационной магистрали 18, ИнАормация с выходов этихблоков через инАормационную магистраль 23 поступает в блок 14 связии далее на моделируемое устройство.Контрольные точки моделируемого устройства могут быть выведены на информационную магистраль 23 и по управляющим сигналам, поступившим по ма-гистрали 20, записаны в блок 2 памяти, Из блока 2 памяти эта информация через инАормационную магистраль18 блок 11 управления, информационную магистраль 16 считана в блок 12.ИнАормация для блока 3 памятичерез мультиплексор 7 может поступать из двух источников; из блокауправления по инАормационной магистрали 18, а также из моделируемогоустройства, расположенного в блоке14 связи, но инйормационной магистрали 23. ИнАормацией, поступающейиз моделируемого устройства, могутбыть промежуточные результаты вычислений, производимых над данными,Управление мультиплексором 7 осуществляется по шине 26,Содержимое блока 3 памяти можетбыть прочитано в блок 12 через буАерный элемент 13, информационнуюмагистраль 18, блок 11 управленияи инАормационную магистраль 16.Синхронизация работы моделируемого устройства и блока управленияосуществляется по магистрали 21 управления.Обмен инАормацией между блоком12 еи блоком 11 управления осуществляется по инАормационным магистралям 15 и 16 и магистрали 17 управления,Устройство моделирования цифровой РЭА может быть связано с внешними вычислительными устройствамичерез информационную магистраль 24и магистраль 25 управления. ЧерезинАормационную магистраль 24 внешнее вычислительное устройство можетбыть подключено к любой точке моде 1501031лируемого устройства, а также к любой магистрали, соединенной с блоком 14 связи,Необходимая синхронизация рабо 5 ты внешнего вычислительного устрой ства с работой устройства моделирования цифровой РЭА и моделируемого устройства осуществляется по магистрали 25 управления, 10Использование устройства моделирования цифровой РЗА обеспечивает моделирование логических и арифметических операций и устройств, построенных на современной элементной базе, в том 15 числе микропроцессорной, имеющей двунаправленные магистрали и внутренние ЗУ различных типов, Кроме того, наличие взаимной синхронизации источников информации позволяет проводить 20 совместное моделирование вновь реализуемых и ранее созданных устройств. Формула изобретения25Устройство моделирования функционирования цифровой радиоэлектронной аппаратуры, содержащее блок управления и первый блок памяти, информационный вход которого соединен с информа ционным входом-выходом блока управления, о т л и ч а ю щ е е с я тем, что с целью расширения функциональных возможностей эа счет возможностимоделирования заказных и полузакаэ ных БИС и повьппения достоверности моделирования, устройство содержит со второго по пятый блоки памяти, с первого по пятый мультиплексоры, операционный вычислительный блок, блок 40 буферных элементов и блок связи инР формационные выходы которого соедине" ны с первыми информационными входами первого, третьего, четвертого и пятого мультиплексоров, ин формационные выходы которых соединены с управляющими входами соответствующих блоков памяти, первый управляющий выход блока управления соединенс управляющими входами с первого попятый мультиплексоров, информационныевходы-выходы блока управления соединены с первыми информационнымивходами второго мультиплексора,информационными входами четвертого ипятого блоков памяти и информационнымивыходами второго блока памяти и блокабуферных элементов, управляющий входкоторого соединен с вторым управляющим выходом блока управления, перваягруппа управляющих выходов блока управления соединена со вторыми информационными входами первого и с третьего по пятый мультиплексоров, втораягруппа управляющих выходов блока управления соединена с управляющимивходами второго блока памяти,информационные входы -выходы блока связи соединены с информационными выходами первого и с третьего по пятый блоков памяти информационными входами второгоблока памяти и информационным входомблока буферных элементов и вторым информационным входом второго мультиплексора,: информационный выход которогосоединен с информационным входом третьего блока памяти, управляющие входывыходы блока управления соединены суправляющими входами-выходами блокасвязи, входы-выходы синхронизации иобмена информацией с внешними устройствами блока связи являются соответствующими входами-вьсодами устройства,информационные выходы, информационныевходы и входи-выходы синхронизацииоперационного вычислительного блокасоединены соответственно с информационными входами, выходами и входами- выходами синхронизации блока управления,зо) оз5 О ОЗ О. Греч Составн Редактор О.Спесивых Техред Л, Олийнык Корректор Т.Палий О Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гага аказ 4868/44ВНИИПИ Государственного к113035М Тираж 668 Подписное тета по изобретениям и открытиям при ГКНТ ССС ва, Ж, Раущская наб., д. 4/5

СмотретьЗаявка

4306402, 24.07.1987

ПРЕДПРИЯТИЕ ПЯ Г-4677

ОВЕЧКИН ЮРИЙ АЛЕКСЕЕВИЧ, КАПРАЛОВ АЛЕКСАНДР ДМИТРИЕВИЧ, ОЛЬШАНСКИЙ ОЛЕГ ВЛАДИМИРОВИЧ, КОНОВАЛОВ ВИКТОР ЮРЬЕВИЧ, ЗАСЛАВСКИЙ ДМИТРИЙ МИХАЙЛОВИЧ, ГРИШИН ГЕОРГИЙ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: аппаратуры, моделирования, радиоэлектронной, функционирования, цифровой

Опубликовано: 15.08.1989

Код ссылки

<a href="https://patents.su/8-1501031-ustrojjstvo-modelirovaniya-funkcionirovaniya-cifrovojj-radioehlektronnojj-apparatury.html" target="_blank" rel="follow" title="База патентов СССР">Устройство моделирования функционирования цифровой радиоэлектронной аппаратуры</a>

Предыдущий патент: Устройство для преобразования последовательного кода в параллельный код

Следующий патент: Арифметико-логический модуль

Случайный патент: Способ изготовления теплоизоляционного материала