Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

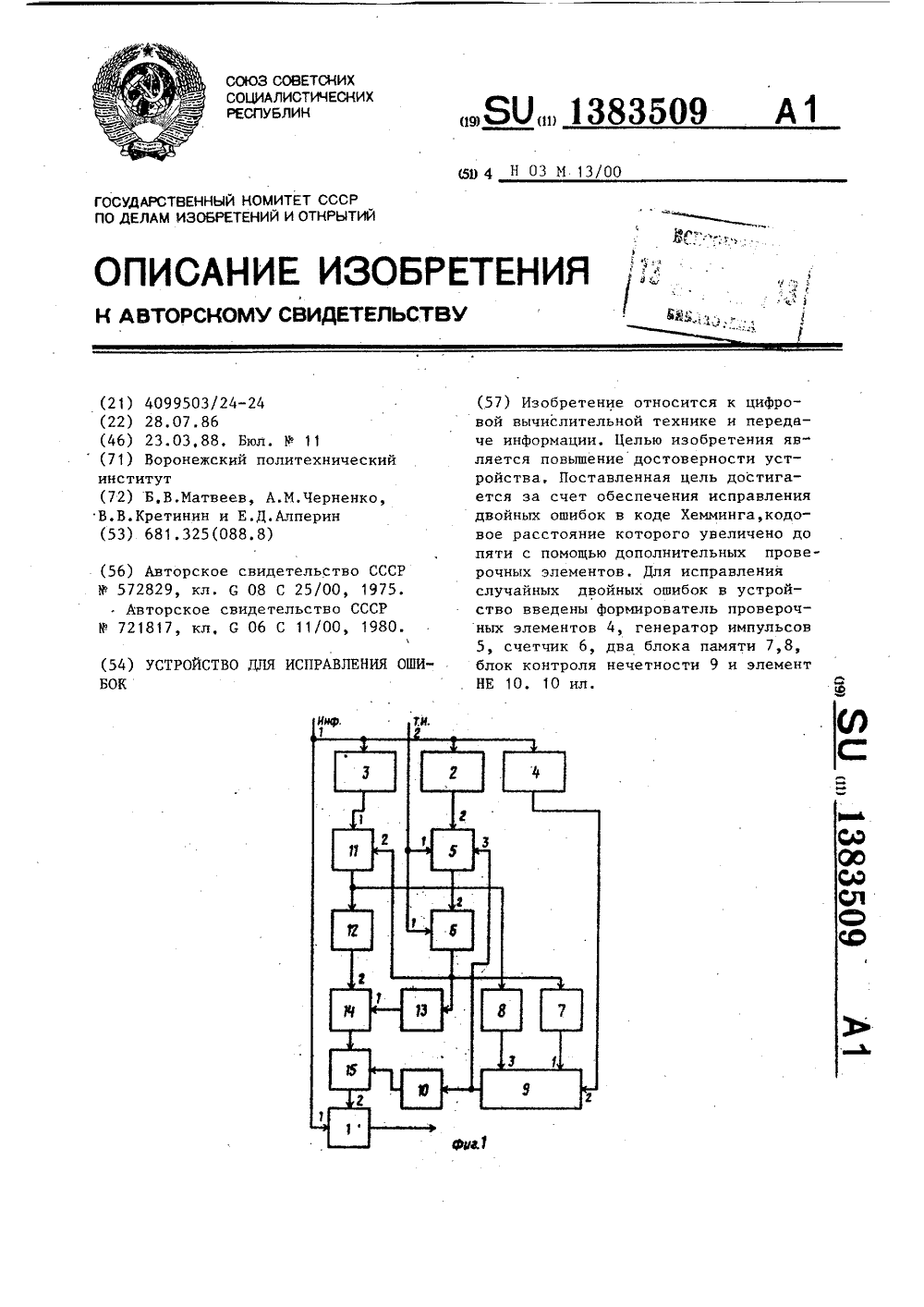

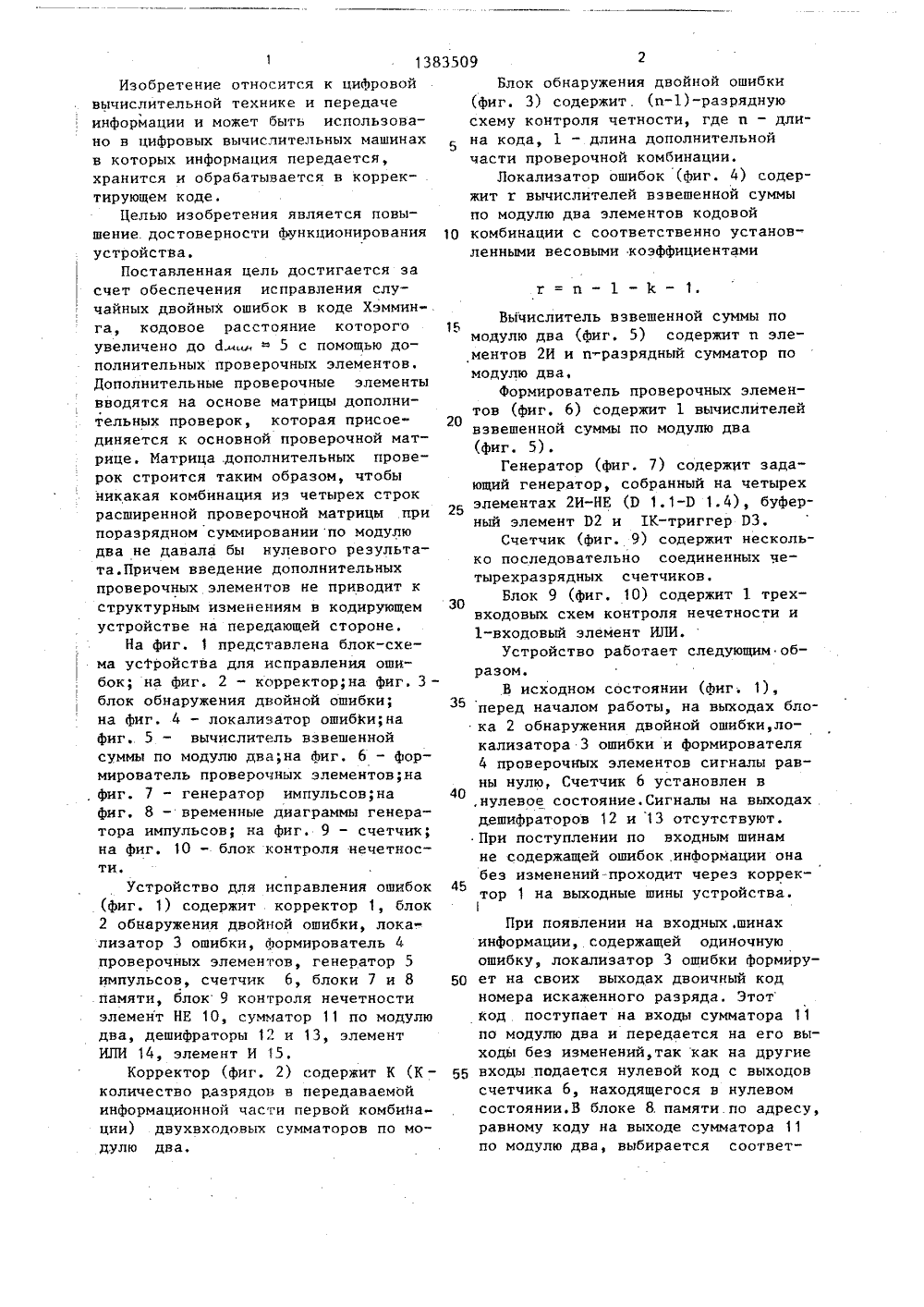

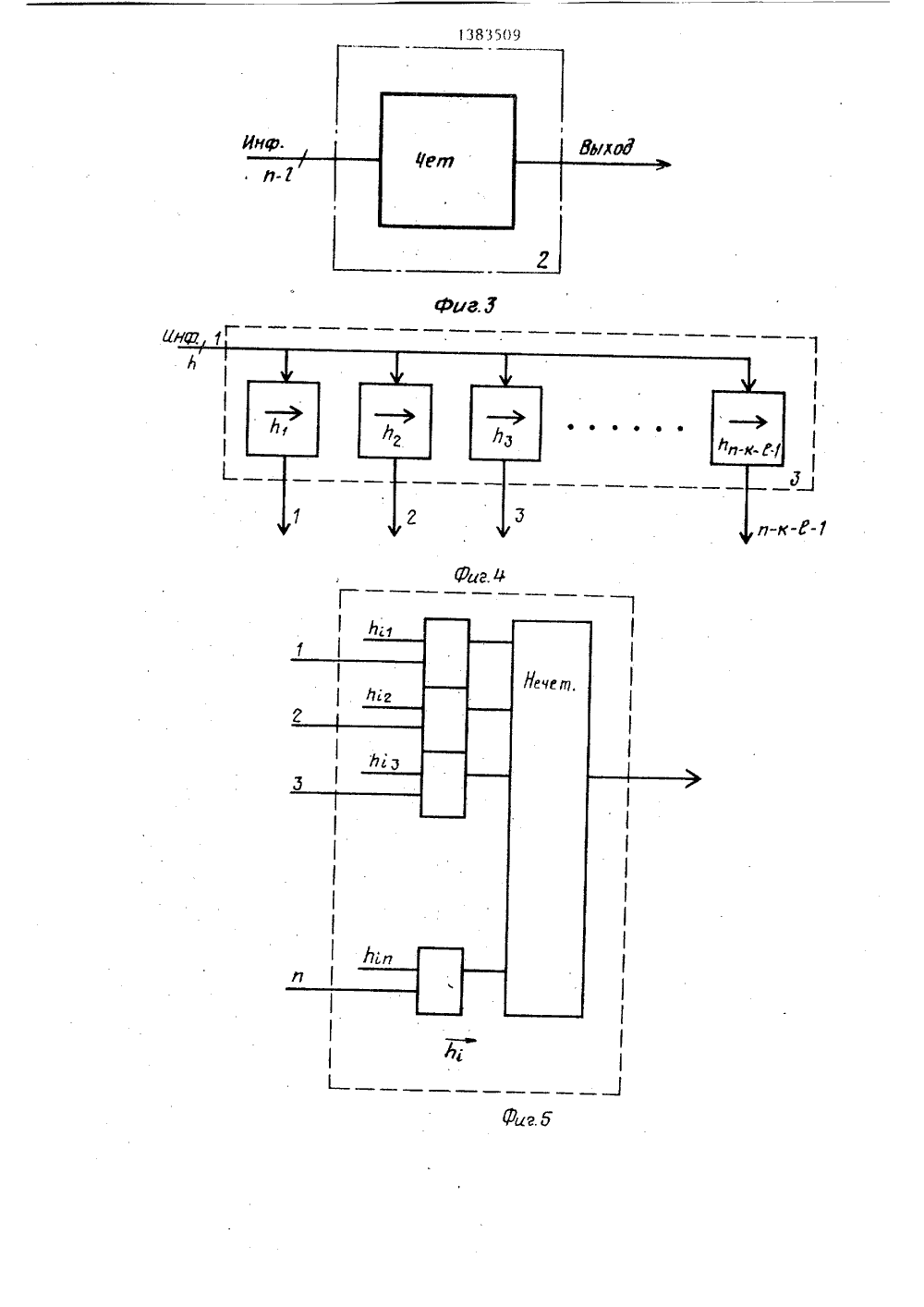

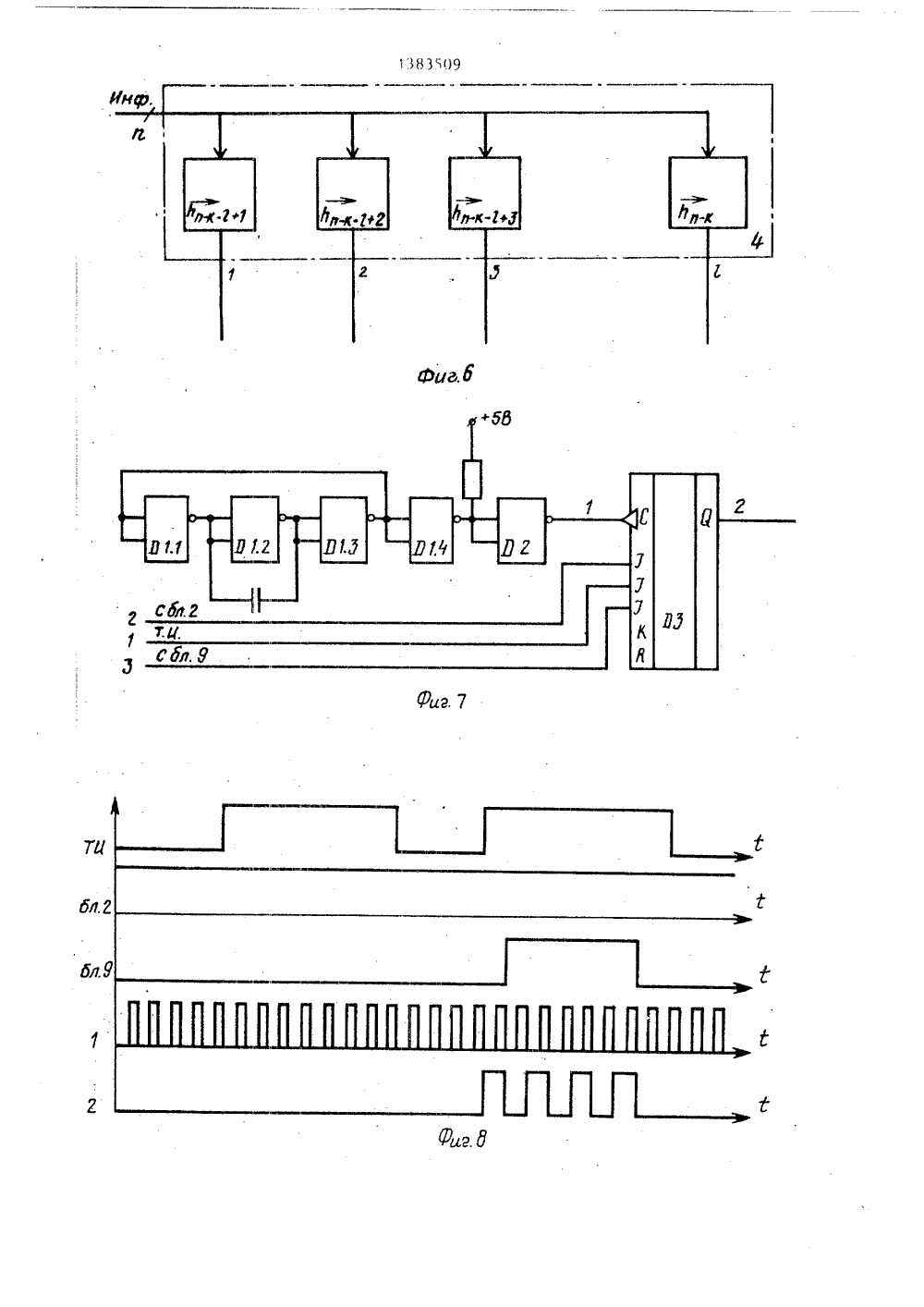

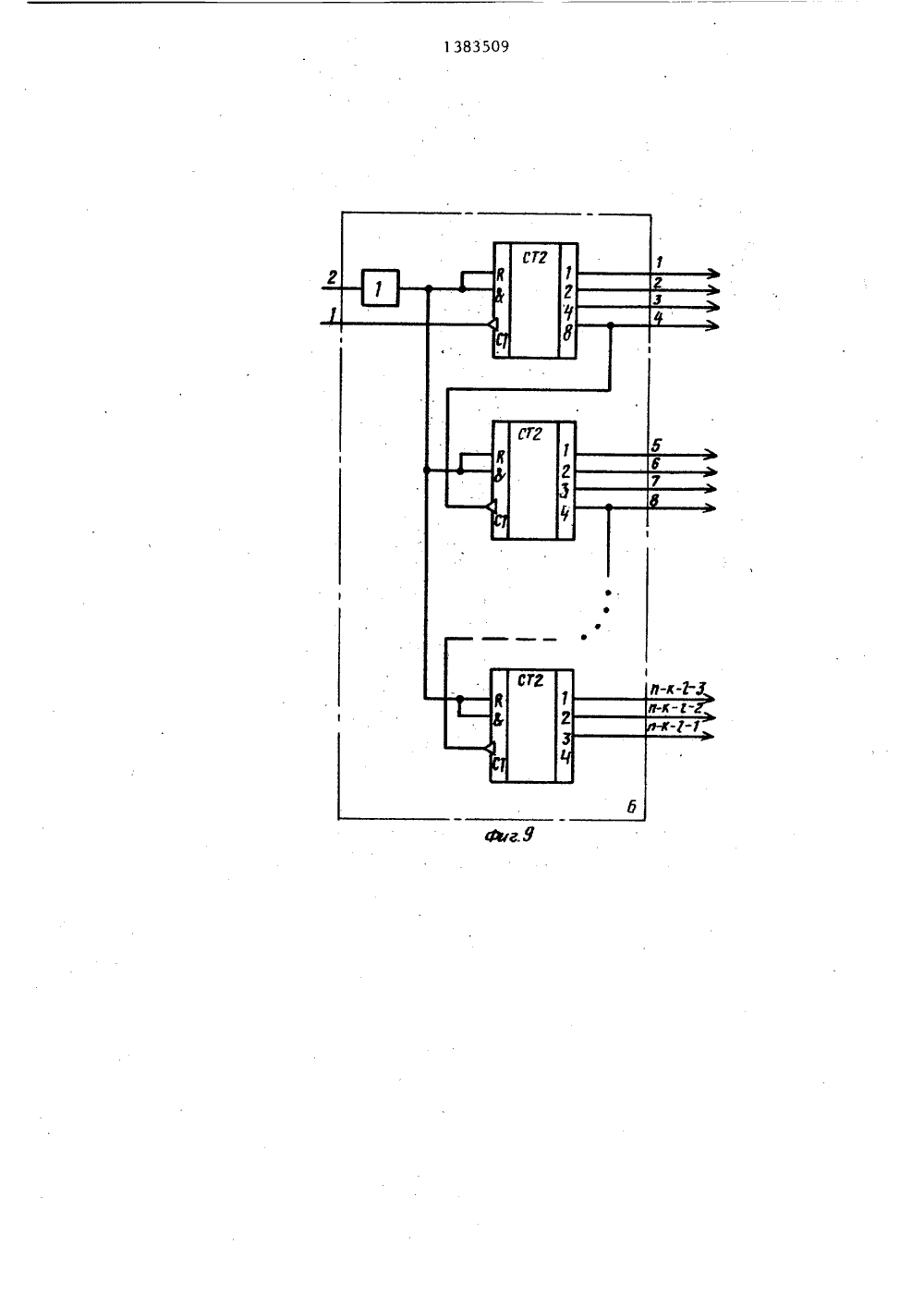

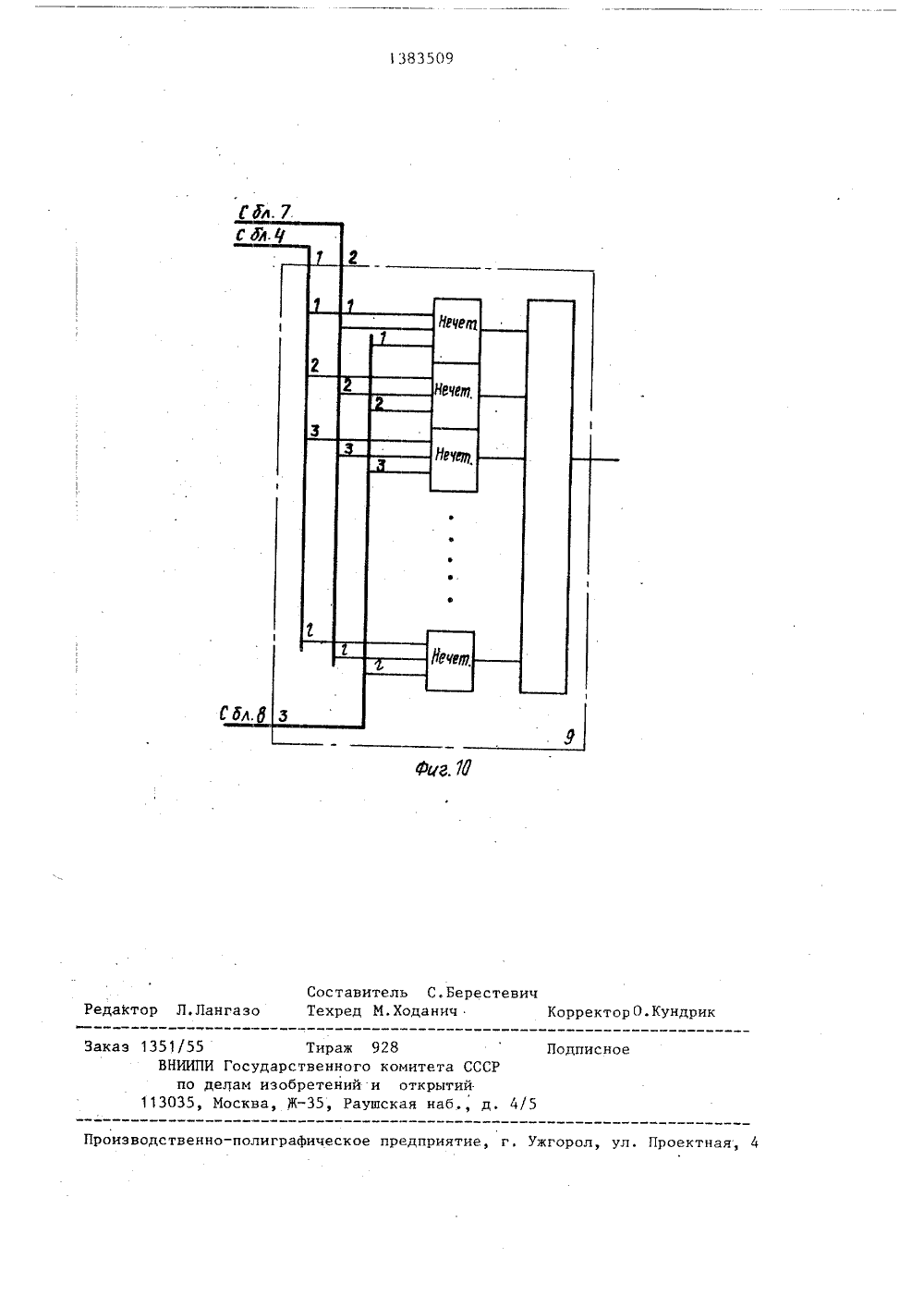

(59 4 Н 03 М 13/00 Е ИЗО ЕНИ ИС ЕТЕПЬСТ К АВТОРСКОМ 3/24-248688, Бюл. Р 11жский политехниче ий атвеев, А.М.Чин и Е.Д.Алле25(088.8) не В,В (53 6) Ав 57282Авторс Ф 721817) УСТР БО 2 ОСУДАРСТВЕННЫЙ КОМИТЕТ ССС О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ(57) Изобретение относится к цифровой вычислительной технике и передаче информации. Целью изобретения является повышение достоверности устройства, Поставленная цель достигается за счет обеспечения исправлениядвойных ошибок в коде Хемминга,кодовое расстояние которого увеличено допяти с помощью дополнительных проверочных элементов, Для исправленияслучайных двойных ошибок в устройство введены формирователь проверочных элементов 4, генератор импульсов5, счетчик 6, два блока памяти 7,8,блок контроля нечетности 9 и элементНЕ 10. 10 ил.1 138Изобретение относится к цифровойвычислительной технике и передачеинформации и может быть использовано в цифровых вычислительных машинахв которых информация передается,хранится и обрабатывается в корректирующем коде.Целью изобретения является ловышение. достоверности функционированияустройства,Поставленная цель достигается засчет обеспечения исправления случайных двойных ошибок в коде Хэмминга, кодовое расстояние которогоувеличено до с5 с помощью дополнительных проверочных элементов.Дополнительные проверочные элементывводятся на основе матрицы дополнительных проверок, которая присоединяется к основной проверочной матрице, Матрица .дополнительных проверок строится таким образом, чтобыникакая комбинация иэ четырех строкрасширенной проверочной матрицы .припоразрядном суммировании по модулюдва не давала бы нулевого результата.Причем введение дополнительныхпроверочных элементов не приводит кструктурным изменениям в кодирующемустройстве на передающей стороне.На фиг.представлена блок-схема усройства для исправления ошибок; на фиг. 2 - корректор;на фиг, 3 -блок обнаружения двойной ошибки;на фиг. 4 - локализатор ошибки;на.фиг. 5 - вычислитель взвешеннойсуммы по модулю два;на фиг. 6 - формирователь проверочных элементов;на, фиг. 7 - генератор импульсов;нафиг, 8 - временные диаграммы генератора импульсов; на фиг. 9 - счетчик;на фиг. 10 - блок контроля нечетности.Устройство для исправления ошибок(фиг. 1) содержит корректор 1, блок2 обнаружения двойной ошибки, локализатор 3 ошибки, формирователь 4проверочных элементов, генератор 5импульсов, счетчик 6, блоки 7 и 8памяти, блок 9 контроля нечеткостиэлемент НЕ 10, сумматор 11 по модулюдва, дешифраторы 12 и 13, элементИЛИ 14, элемент И 5,Корректор (фиг. 2) содержит К (К -количество разрядов в передаваемойинформационной части первой комбинации) двухвходовых сумматоров по модулю два. 3509Блок обнаружения двойной ошибки(фиг. 3) содержит (и)-разряднуюсхему контроля четности, где и - длина кода, 1 - длина дополнительнойчасти проверочной комбинации.Локализатор ошибок (фиг. 4) содержит г вычислителей взвешенной суммыпо модулю два элементов кодовой 10 комбинации с соответственно установленными весовыми коэффициентамиг = п - 1 - 1 -Вычислитель взвешенной суммы по1 Гмодулю два (фиг, 5) содержит п элементов 2 И и и-разрядный сумматор помодулю два,Формирователь проверочных элементов (фиг. 6) содержит 1 вычислителей20взвешенной суммы по модулю два(фиг. 5),Генератор (фиг. 7) содержит задающий генератор, собранный на четырехэлементах 2 И-НЕ Ф 1.1-П .4), буферный элемент 02 и 1 К-триггер РЗ.Счетчик (фиг. 9) содержит несколько последовательно соединенных четырехразрядных счетчиков.30Блок 9 (фиг. 10) содержит 1 трехвходовых схем контроля нечетности и1-входовый элемент ИЛИ.Устройство работает следующим образом.В исходном состоянии (фиг. 1),перед началом работы, на выходах блока 2 обнаружения двойной ошибки,локализатора 3 ошибки и формирователя4 проверочных элементов сигналы равны нулю, Счетчик 6 установлен в40,нулевое состояние. Сигналы на выходахдешифраторов 12 и 13 отсутствуют.При поступлении по входным шинамне содержащей ошибок информации онабез изменений-проходит через коррек 45тор 1 на выходные шины устройства.При появлении на входных .шинахинформации, содержащей одиночную ошибку, локализатор 3 ошибки формиру ет на своих выходах двоичный кодномера искаженного разряда. Этот код поступает на входы сумматора 11 по модулю два и передается на его выходы без изменений,так как на другие 55 входы подается нулевой код с выходовсчетчика 6, находящегося в нулевом состоянии.В блоке 8. памяти.по адресу, равному коду на выходе сумматора 11 по модулю два, выбирается соответ 138350910 15 20 25 30 35 40 45 50 55 ствующая проверочная комбинация и подается на вход блока 9 контроля нечеткости,на втором входе которого установлена проверочная комбинация, сформированная в формирователе 4 в соответствии с дополнительной к коду Хэмминга матрицей. На.третьем входе блока 9 контроля нечетности сигналы отсутствуют, так как в случае одиночной ошибки счетчик 6 находится в нулевом состоянии и блок 7 памяти не работает. Поскольку произошла одна ошибка, проверочные комбинации на входах блока 9 контроля нечеткости совпадают и сигнал на его выходе равен нулю, Единичный сигнал с выхода элемента НЕ 10 отпирает элемент И 15. Одновременно код номера искаженного разряда с выхода сумматора 11.по модулю два расшифровывается дешифратором 12, и в корректоре 1 происходит исправление искаженного разряда путем его инверсии (сложение по модулю два с единичным сигналов с соответствующего выхода де,шифратора). Счетчик 6 остается в нулевом состоянии, и на выходах дешифратора 13 сигналы отсутствуют.При появлении на входах устройства информации, содержащей двойную ошибку, локализатор 3 ошибки в соответствии со способом локализации ошибки в коде Хэмминга формирует на своих выходах двоичный код, равный сумме по модулю два кодов номеров обоих искаженных разрядов, и, следовательно, не соответствующий ни одному из этих разрядов. Единичный сигнал с блока 2 обнаружения двойной ошибки одновременно с единичными сигналами на тактовом входе устройства и выходе блока 9 контроля не- четности разрешает работу генератора 5 и счетчика 6, который на своих . выходах последовательно формирует двоичные коды, соответствующие позициям принятой комбинации, начиная с О до ивключительно (и - количество разрядов в комбинации), согласно проверочной матрице кода Хэмминга, Код с выхода счетчика 6 поступает в блок 7 памяти, где используется для выбора проверочной комбинации, соответствующей данному разряду, а так же сумматора 11 по модулю два, На другой вход сумматора.11 по модулю два поступает код с выхода локализатора 3 ошибки. Результат суммирования на выходе сумматора11 по модулю, являющийся кодом предполагаемого номера позиции второгоискаженного разряда, поступает вблок 8 памяти, где используется длявыбора проверочной комбинации,соответствующей этому разряду. Коды проверочных комбинаций поступают в блок2 контроля нечетности, где поразрядно складываются по модулю два другс другом и с кодом на выходе формирователя 4, который равен сумме помодулю два строк дополнительной матрицы, соответствующих искаженным разрядам, Если номера позиций ошибок определены неверно, то код на входеэлемента ИЛИ блока 9, равный суммепо модулю два кодов четырех строк дополнительной матрицы, отличен отнуля, следовательно, сигнал на выходе блока 9 не равен нулю, элементИ 15 заперт нулевым сигналом с выхода элемента НЕ 10, счетчик 6 продолжает работу. Когда на выходе счет.чика 6 появляется код номера позицииодного из искаженных разрядов, навыходе сумматора 11 по модулю дваформируется код номера позиции второ.го искаженного разряда, сигнал навыходе блока 9 контроля нечетностистановится нулевым, отпирается элемент И 15. Номера обоих искаженных разрядов расшифровываются дешифраторами 12 и 13 и через открытый элемент И 15 поступают в корректор 1, где происходит исправление ошибок. Формула изобретения Устройство для исправления оши-,бок, содержащее локализатор ошибки,вход которого объединен с входом блока обнаружения двойной ошибки ипервым входом корректора и являетсяинформационным входом устроиства,выход локализатора ошибки соединен спервым входом сумматора по модулюдва, выход которого соединен с входом первого дешифратора,выход которого соединен с первым входом элемента ИЛИ, второй дешифратор, выходкоторого соединен с вторым входомэлемента ИЛИ,выход корректора является выходом устройства, о т л и -ч а ю щ е е с я тем,что,с целью повышения достоверности функционирования устройства, в него введенысчетчик, элемент И, формировательпроверочных элементов кода, блокипамяти,элеменг НЕ, блок контроля не 1383509четности и генератор импульсов,первый вход которого объединен с первым входом счетчика и является тактовым входом устройства, выход блокаобнаружения двойной ошибки соединенс входом генератора импульсов, выходкоторого соединен с вторым входомсчетчика, выход которого соединенс вторым входом сумматора по модулю 1 Одва, входом второго дешифратора ивходом первого блока памяти, выходкоторого соединен с первым входомблока контроля нечетности,выход которого соединен с третьим вхоцом генератора импульсов и входом элементаНЕ, выход которого соединен с первымвходом элемента И,выход элементаИЛИ соединен с вторым входом элемента И,выход которого соединен с вто-рым входом корректора, вход формирователя проверочных элементов кода соединен с информационным входом устройства, выход - с вторым входомблока контроля нечетности, третийвход которого соединен с выходом второго блока памяти, вход которогосоединен с выходом сумматора по модулю два,Редак ПодписноСР 9 аказ 1351/55 ВНИИП по 113035, Тираж Государственног елам изобретений Москва, Ж, Ра омитет и открытийщская наб жгорол, ул. Проектная, 4 роизводственно-полиграфическое предприятие,

СмотретьЗаявка

4099503, 28.07.1986

ВОРОНЕЖСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

МАТВЕЕВ БОРИС ВАСИЛЬЕВИЧ, ЧЕРНЕНКО АЛЕКСАНДР МИХАЙЛОВИЧ, КРЕТИНИН ВИКТОР ВАСИЛЬЕВИЧ, АЛПЕРИН ЕВГЕНИЙ ДАНИЛОВИЧ

МПК / Метки

МПК: H03M 13/19

Метки: исправления, ошибок

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/8-1383509-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Преобразователь последовательного кода в параллельный

Следующий патент: Устройство для декодирования манчестерского кода

Случайный патент: Стан многократного волочения проволоки