Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

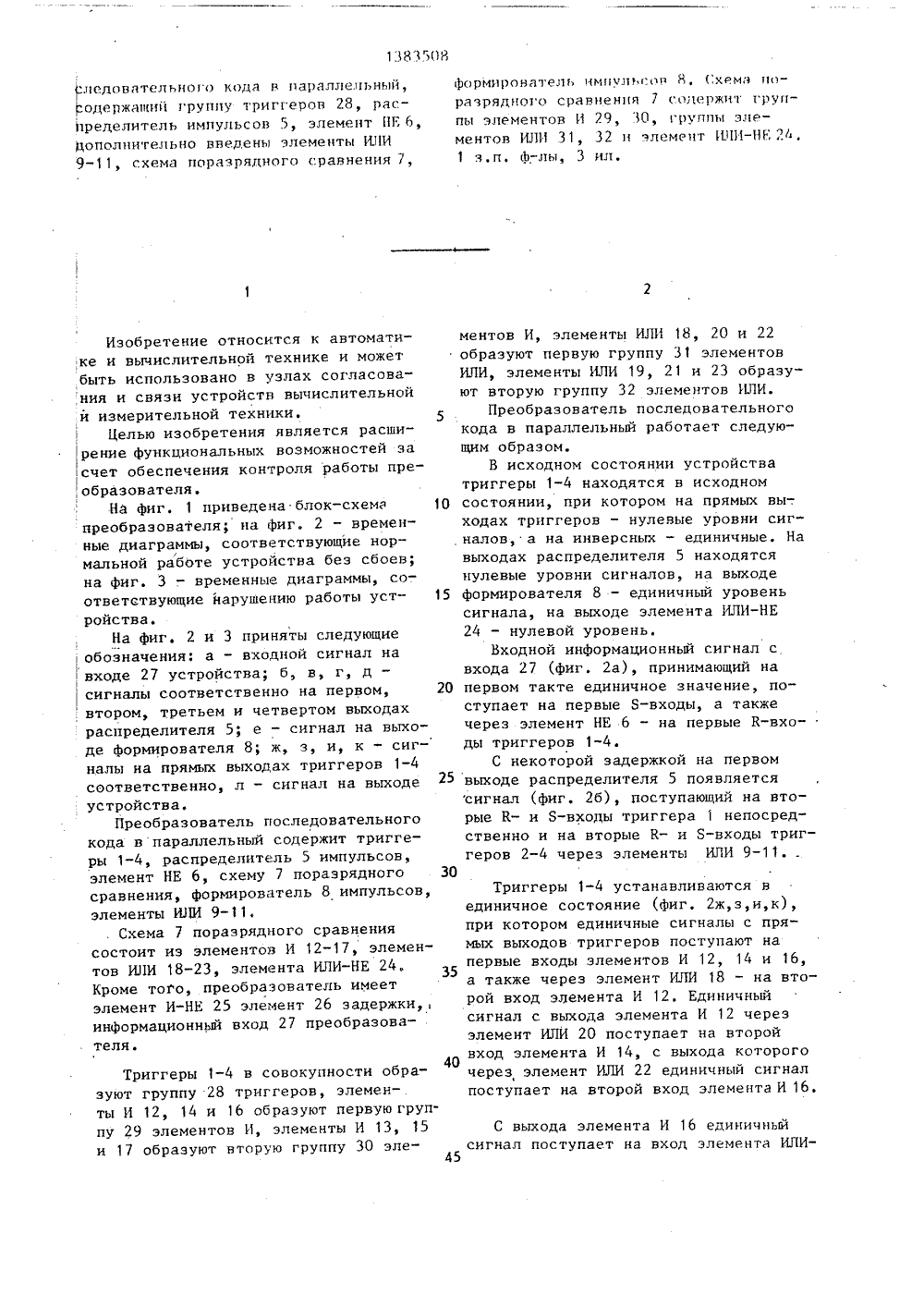

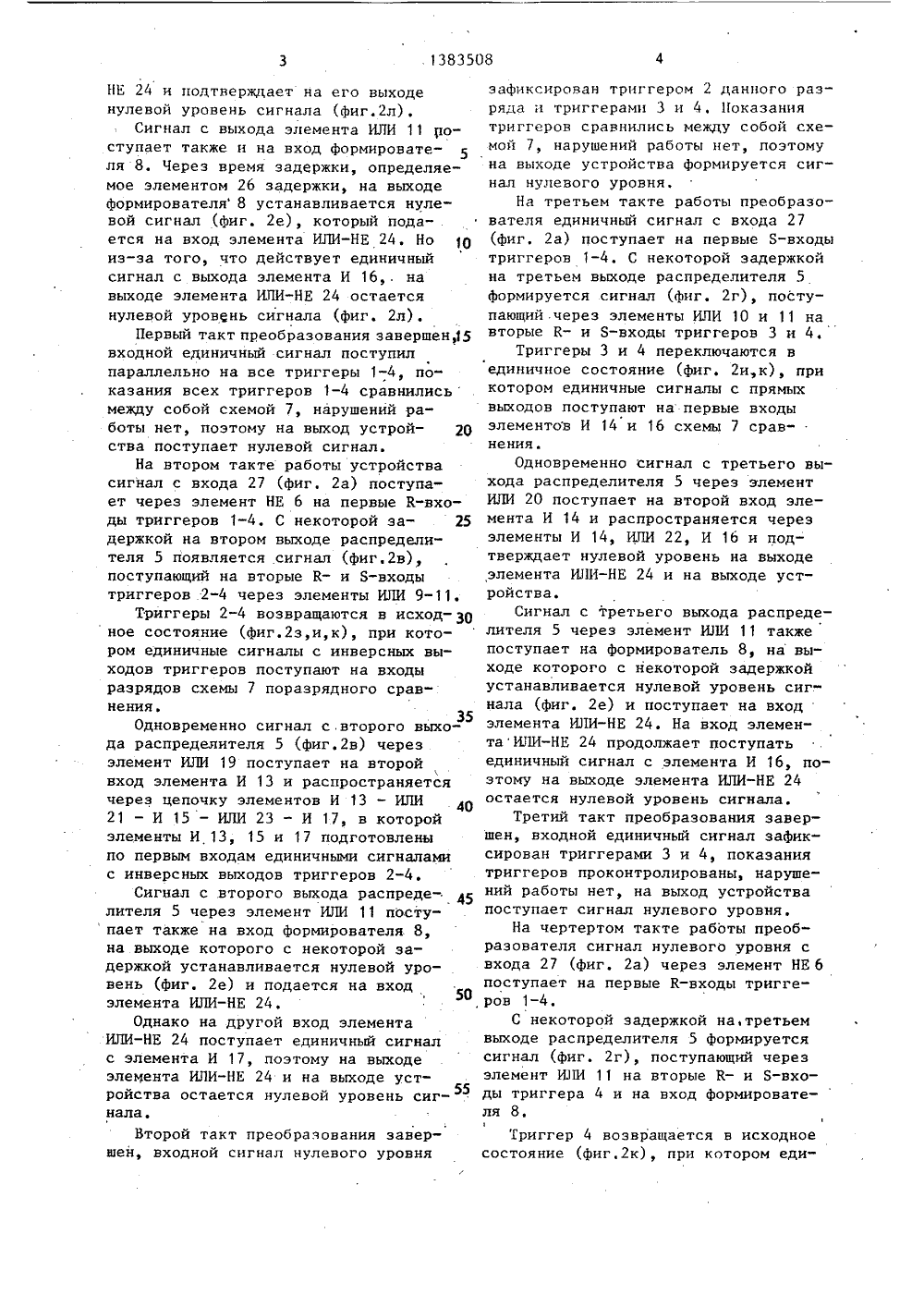

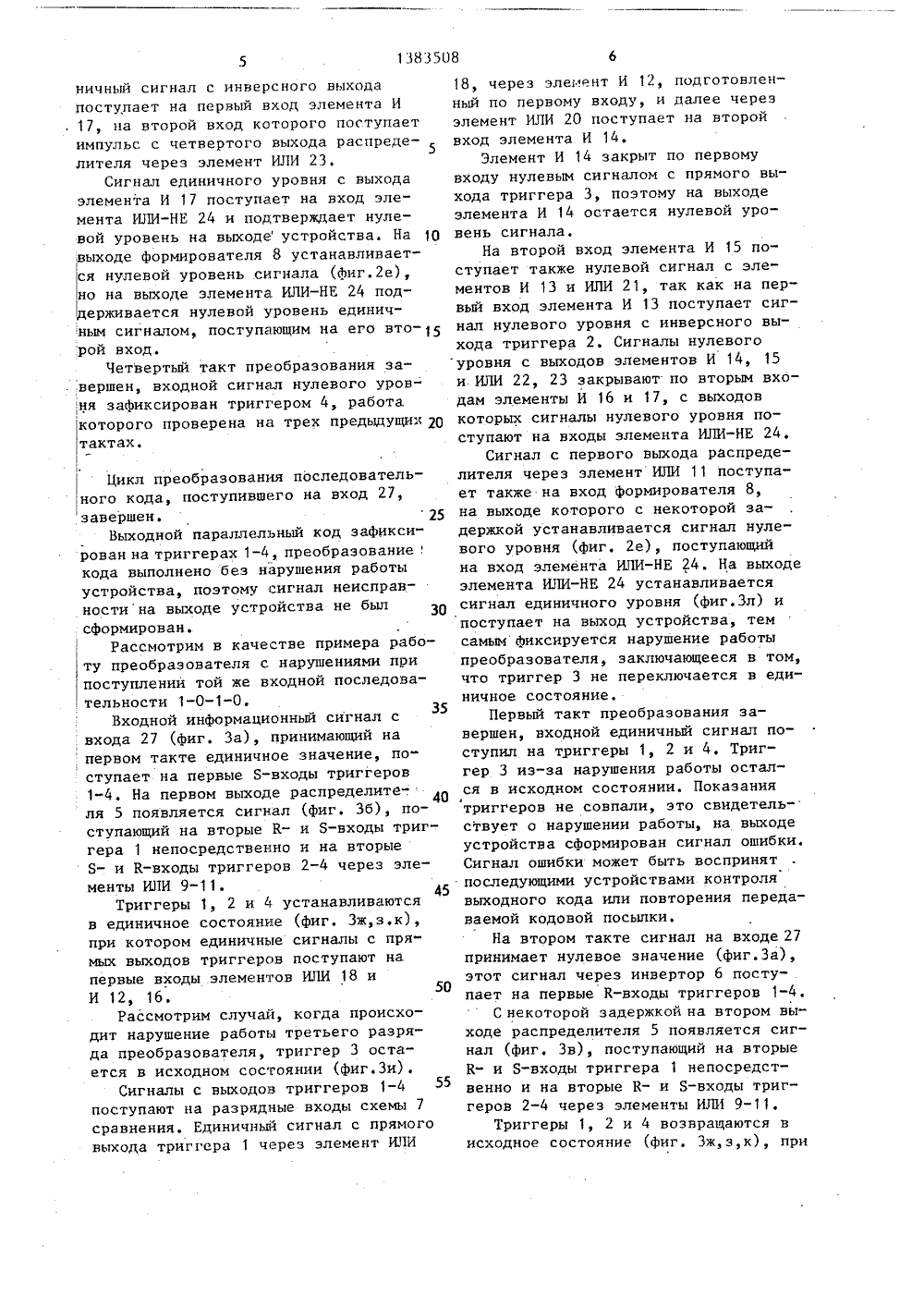

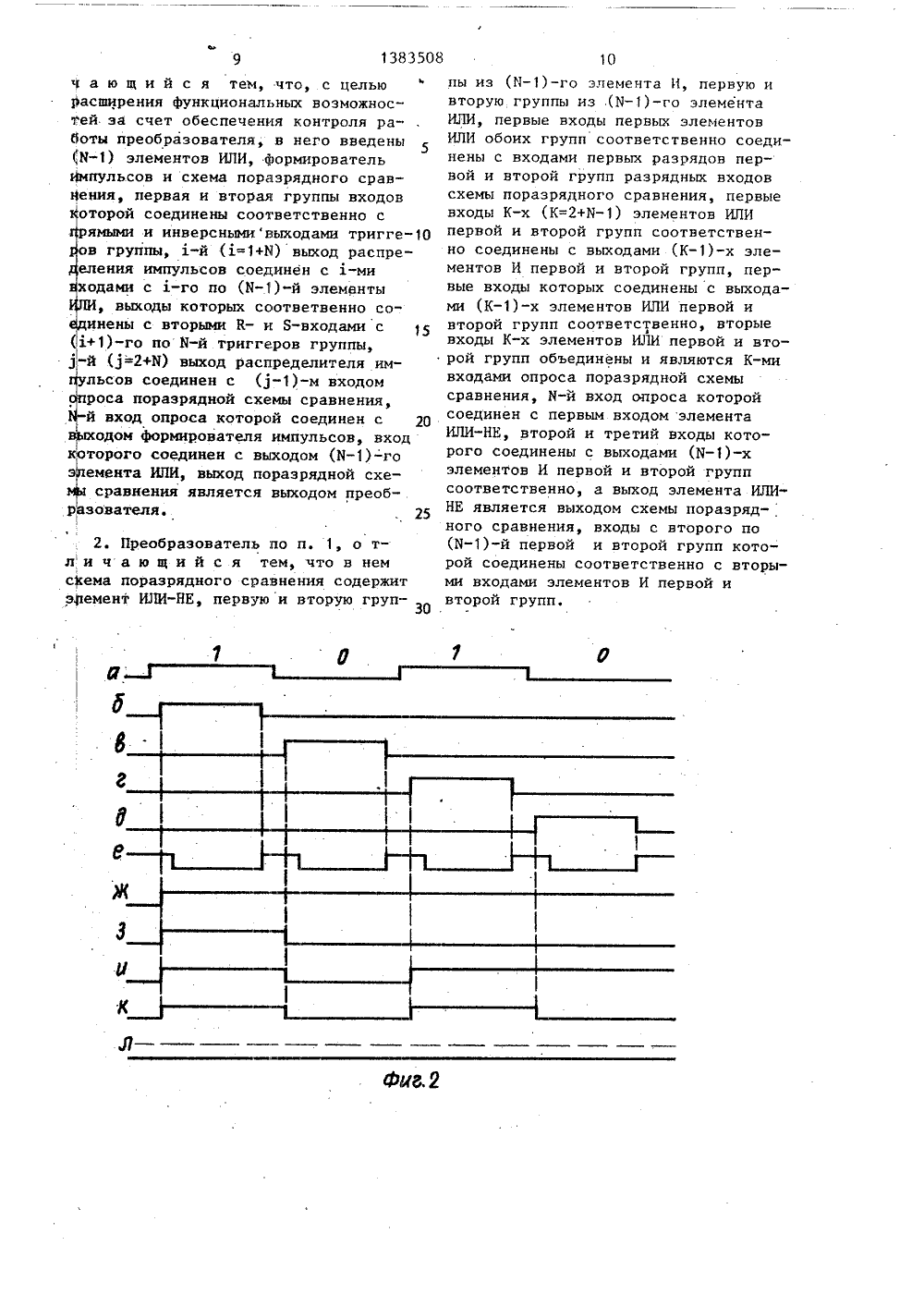

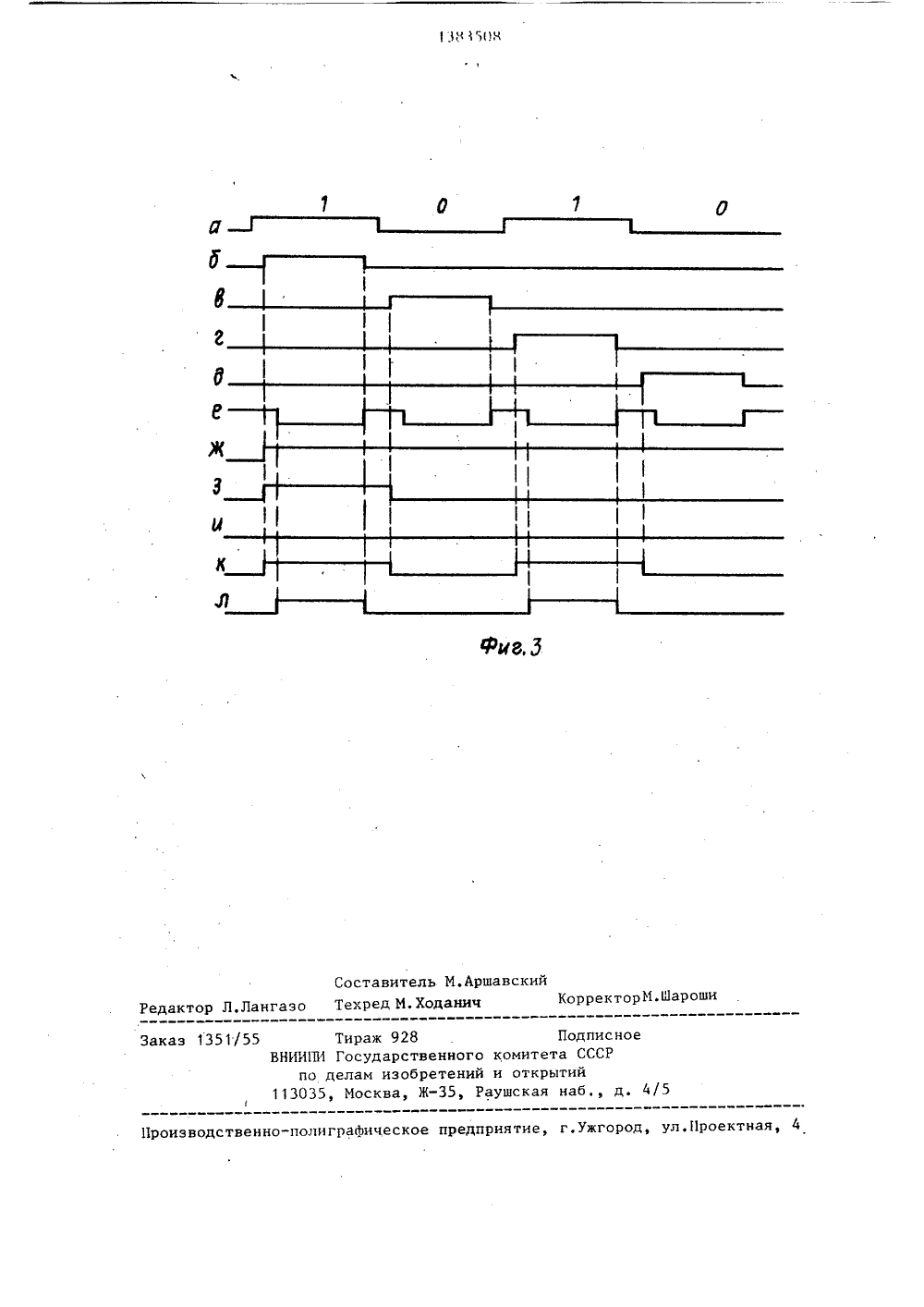

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУ БЛИН А 1(22) 27.10.86 мат и лахЦельние кцион ых можностеи з ч обеспеч ователя контроля работы ипреобразователь по обра АРСТ 8 ЕННЫЙ НОМИТЕТ ССС ЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫ САНИЕ ИЗОБРЕТЕ АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство ССУ 354410, кл. Н 03 М 9/00, 1970Авторское свидетельство СССРУ 628485, кл. Н 03 М 9/00, 1976 1 РЕОБРАЗОВАТЕЛЬ 11 ОСЛЕДОВАТЕЛКОДА В 11 АРАЛЛЕЛЬНЬЗИ Изобретение относится к автое и цифровой вычислительной теи может быть использовано в уз пряжения цифровых устройств.изобретения является расшире18. ( Р Изобретение относится к автоматике и вычислительной технике и можетбыть использовано в узлах согласова. -ния и связи устройств вычислительнойи измерительной техники.5Целью изобретения является расширение функциональных возможностей засчет обеспечения контроля работы пре,образователя,На фиг. 1 приведена блок-схема 1 Опреобразователя; на фиг. 2 - временные диаграммы, соответствующие нормальной работе устройства беэ сбоев;на фиг. 3 в . временные диаграммы, со-.ответствующие нарушению работы устройства.На фиг. 2 и 3 приняты следующиеобозначения: а - вхоцной сигнал навходе 27 устройства; б, в, г д -сигналы соответственно на первом,втором, третьем и четвертом выходахраспределителя 5; е - сигнал на выходе формирователя 8; ж, з, и, к - сиг-налы на прямых выходах триггеров 1-4соответственно, л - сигнал на выходе25устройства,Преобразователь последовательногокода впараллельный содержит триггеры 1-4, распределитель 5 импульсов,элемент НЕ 6, схему 7 поразрядного 30сравнения, формирователь 8 импульсов,элементы ИЛИ 9-11.Схема 7 поразрядного сравнениясостоит из элементов И 12-17, элементов ИЛИ 18-23, элемента ИЛИ-НЕ 24. 3Кроме тоГо, преобразователь имеетэлемент И-НЕ 25 элемент 26 задержкиинформационный вход 27 преобразователя. 20 40Триггеры 1-4 в совокупности образуют группу 28 триггеров, элемен-. ты И 12, 14 и 16 образуют первую группу 29 элементов И, элементы И 13, 15 и 17 образуют вторую группу 30 элеС выхода элемента И 16 единичный сигнал поступает на вход элемента ИЛИ 45(,едовательно о кода в аралеьны, содержаи группу триггеров 28, расределитель импульсов 5, элемент НЕ 6, Дополнительно введены элементы ИЛИ 9-11, схема поразрядного сравнения /,Формирователь нмул) сов Й, (,хем о -разрядного сравненя 7 гоиержг группы элементов И 29, 30,руппы элементов ИЛИ 31, 32 н элемент ИЛИ-НЕ 24.1 з.п. Ф-лы, 3 ил,ментов И, элементы ИЛИ 18, 20 и 22 образуют первую группу 31 элементов ИЛИ, элементы ИЛИ 19, 21 и 23 образуют вторую группу 32 элементов ИЛИ.Преобразователь последовательного кода в параллельный работает следующим образом.В исходном состоянии устройства триггеры 1-4 находятся в исходном состоянии, при котором на прямых вы-. ходах триггеров - нулевые уровни сигналов, а на инверсных - единичные. На выходах распределителя 5 находятся нулевые уровни сигналов, на выходе формирователя 8 - единичный уровень сигнала, на выходе элемента ИЛИ-НЕ 24 - нулевой уровень.Входной информационный сигнал с входа 27 (фиг, 2 а), принимающий на первом такте единичное значение, поступает на первые Б-входы, а также через элемент НЕ 6 - на первые К-входы триггеров 1-4.С некоторой задержкой на первом выходе распределителя 5 появляется сигнал фиг. 2 б), поступающий на вторые К- и Б-входы триггера 1 непосредственно и на вторые К- и Я-входы триггеров 2-4 через элементы ИЛИ 9-11. Триггеры 1-4 устанавливаются в единичное состояние (фиг, 2 ж,з,и,к), при котором единичные сигналы с прямых выходов триггеров поступают на первые входы элементов И 12, 14 и 16, а также через элемент ИЛИ 18 - на второй вход элемента И 12. Единичный сигнал с выхода элемента И 12 через элемент ИЛИ 20 поступает на второй вход элемента И 14, с выхода которого через элемент ИЛИ 22 единичный сигналпоступает на второй вход элемента И 16.НЕ 24 и подтверждает на его выходенулевой уровень сигнала (фиг,2 л).Сигнал с выхода элемента ИЛИ 11 по"ступает также и на вход формирователя 8. Через время задержки, определяемое элементом 26 задержки, на выходеформирователя 8 устанавливается нулевой сигнал (фиг. 2 е), который подается на вход элемента ИЛИ-НЕ 24. Но 1 Оиз-за того, что действует единичныйсигнал с выхода элемента И 16,. навыходе элемента ИЛИ-НЕ 24 остаетсянулевой уровень сигнала (фиг. 2 л),Первый такт преобразования завершен,15входной единичный сигнал поступилпараллельно на все триггеры 1-4, показания всех триггеров 1-4 сравнилисьмежду собой схемой 7, нарушений работы нет, поэтому на выход устрой Оства поступает нулевой сигнал.На втором такте работы устройствасигнал с входа 27 (фиг. 2 а) поступает через элемент НЕ 6 на первые К-входы триггеров 1-4, С некоторой задержкой на втором выходе распределителя 5 появляется сигнал (фиг,2 в),поступающий на вторые К- и 8-входытриггеров 2-4 через элементы ИЛИ 9-11.Триггеры 2-4 возвращаются в исход- Зоное состояние (фиг.2 з,и,к), при котором единичные сигналы с инверсных выходов триггеров поступают на входыразрядов схемы 7 поразрядного сравнения.Одновременно сигнал с.второго выхода распределителя 5 (фиг.2 в) черезэлемент ИЛИ 19 поступает на второйвход элемента И 13 и распространяетсячерез цепочку элементов И 13 - ИЛИ 4 р21 - И 15 - ИЛИ 23 - И 17, в которойэлементы И 13, 15 и 17 подготовленыпо первым входам единичными сигналамис инверсных выходов триггеров 2-4.Сигнал с .второго выхода распределителя 5 через элемент ИЛИ 11 поступает также на вход формирователя. 8,на выходе которого с некоторой задержкой устанавливается нулевой уровень (фиг. 2 е) и подается на входэлемента ИЛИ-НЕ 24,Однако на другой вход элементаИЛИ-НЕ 24 поступает единичный сигналс элемента И 17, поэтому на выходеэлемента ИЛИ-НЕ 24 и на выходе устройства остается нулевой уровень сигнала,Второй такт преобразования завершен, входной сигнал нулевого уровня зафиксирован триггером 2 данного разряда и триггерами 3 и 4. Показаниятриггеров сравнились между собой схемой 7, нарушений работы нет, поэтомуна выходе устройства формируется сигнал нулевого уровня,На третьем такте работы преобразователя единичный сигнал с входа 27(фиг. 2 а) поступает на первые Б-входытриггеров 1-4, С некоторой задержкойна третьем выходе распределителя 5формируется сигнал (фиг, 2 г), поступающий.через элементы ИЛИ 10 и 11 навторые К- и Б-входы триггеров 3 и 4,Триггеры 3 и 4 переключаются вединичное состояние (фиг, 2 и,к), прикотором единичные сигналы с прямыхвыходов поступают на первые входыэлементов И 14 и 16 схемы 7 сравнения.Одновременно сигнал с третьего выхода распределителя 5 через элементИЛИ 20 поступает на второй вход элемента И 14 и распространяется черезэлементы И 14, ИЛИ 22, И 16 и подтверждает нулевой уровень на выходеэлемента И 31 И-НЕ 24 и на выходе устройства.Сигнал с третьего выхода распределителя 5 через элемент ИЛИ 11 такжепоступает на формирователь 8, на выходе которого с некоторой задержкойустанавливается нулевой уровень сигнала (фиг. 2 е) и поступает на входэлемента ИЛИ-НЕ 24. На вход элементаИЛИ-НЕ 24 продолжает поступатьединичный сигнал с элемента И 16, поэтому на выходе элемента ИЛИ-НЕ 24остается нулевой уровень сигнала.Третий такт преобразования завершен, входной единичный сигнал зафиксирован триггерами 3 и 4, показаниятриггеров проконтролированы, нарушений работы нет, на выход устройствапоступает сигнал нулевого уровня,На чертертом такте работы преобразователя сигнал нулевого уровня свхода 27 (фиг. 2 а) через элемент НЕ 6поступает на первые К-входы триггеров 1-4.С некоторой задержкой на,третьемвыходе распределителя 5 формируетсясигнал (фиг. 2 г), поступающий черезэлемент ИЛИ 11 на вторые К- и Б-входы триггера 4 и на вход формирователя 8,Триггер 4 возвращается в исходноесостояние (фиг.2 к), при котором единичный сигнал с инверсного выхода поступает на первый вход элемента И . 17, на второй вход которого поступает импульс с четвертого выхода распреде лителя через элемент ИЛИ 23Сигнал единичного уровня с выхода элемента И 17 поступает на вход элемента ИЛИ-НЕ 24 и подтверждает нулевой уровень на выходе устройства. На 10 выходе формирователя 8 устанавливается нулевой уровень сигнала (фиг.2 е), но на выходе элемента ИЛИ-НЕ 24 поддерживается нулевой уровень единичным сигналом, поступающим на его вто рой вход.Четвертый такт преобразования завершен, входной сигнал нулевого уров;ня зафиксирован триггером 4, работа. которого проверена на трех предыдущих 20 ,тактах.Цикл преобразования последовательного кода, поступившего на вход 27, завершен.25Выходной параллельный код зафиксирован на триггерах 1-4, преобразование, кода выполнено без нарушения работы устройства, поэтому сигнал неисправностина выходе устройства не был сформирован.Рассмотрим в качестве примера работу преобразователя с нарушениями при поступлении той же входной последова-тельности 1-0-1-0.35Входной информационный сигнал с входа 27 (фиг. За), принимающий на первом такте единичное значение, поступает на первые Б-входы триггеров 1-4. На первом выходе распределите-, ля 5 появляется сигнал (фиг. Зб), поступающий на вторые К- и Б-входы триггера 1 непосредственно и на вторые Я- и К-входы триггеров 2-4 через элементы ИЛИ 9-11.45Триггеры 1, 2 и 4 устанавливаются в единичное состояние (фиг. Зж,з.к), при котором единичные сигналы с пря" мых выходов триггеров поступают на. первые входы элементов ИЛИ 18 и И 12, 16.Рассмотрим случай, когда происходит нарушение работы третьего разряда преобразователя, триггер 3 остается в исходном состоянии (фиг.Зи).Сигналы с выходов триггеров 1-4 55 поступают на разрядные входы схемы 7 сравнения. Единичный сигнал с прямого выхода триггера 1 через элемент ИЛИ 18, через элемент И 12, подготовленный по первому входу, и далее черезэлемент ИЛИ 20 поступает на второйвход элемента И 14,Элемент И 14 закрыт по первомувходу нулевым сигналом с прямого выхода триггера 3, поэтому на выходеэлемента И 14 остается нулевой уровень сигнала,На второй вход элемента И 15 поступает также нулевой сигнал с элементов И 13 и ИЛИ 21, так как на первый вход элемента И 13 поступает сигнал нулевого уровня с инверсного выхода триггера 2. Сигналы нулевогоуровня с выходов элементов И 14, 15и ИЛИ 22, 23 закрывают по вторым входам элементы И 16 и 17, с выходовкоторых сигналы нулевого уровня поступают на входы элемента ИЛИ-НЕ 24.Сигнал с первого выхода распределителя через элемент ИЛИ 11 поступает также на вход формирователя 8,на выходе которого с некоторой задержкой устанавливается сигнал нулевого уровня (фиг, 2 е), поступающийна вход элемента ИЛИ-НЕ 24На выходеэлемента ИЛИ-НЕ 24 устанавливаетсясигнал единичного уровня (фиг.Зл) ипоступает на выход устройства, темсамым фиксируется нарушение работыпреобразователя, заключающееся в том,что триггер 3 не переключается в единичное состояние,Первый такт преобразования завершен, входной единичный сигнал поступил на триггеры 1, 2 и 4. Триггер 3 из-за нарушения работы остался в исходном состоянии, Показаниятриггеров не совпали, это свидетельствует о нарушении работы, на выходеустройства сформирован сигнал ошибки,Сигнал ошибкиможет быть воспринятпоследующими устройствами контролявыходного кода или повторения передаваемой кодовой посылки.На втором такте сигнал на входе 27принимает нулевое значение (фиг,За),этот сигнал через инвертор 6 поступает на первые К-входы триггеров 1-4.С некоторой задержкой на втором выходе распределителя 5 появляется сигнал (фиг. Зв), поступающий на вторыеК- и Б-входы триггера 1 непосредственно и на вторые К- и 8-входы триггеров 2-4 через элементы ИЛИ 9-11.Триггеры 1, 2 и 4 возвращаются висходное состояние (фиг. Зж,э,к), прикотором единичные сигналы с инверсных выходов поступают на первые входы элементов ИЛИ 19 и И 13, 17.Сигнал единичного уровня с выхода элементов ИЛИ 19 распространяется через элементы И 13 и ИЛИ 21, далее через элемент, И 15, подготовленный по первому входу единичным сигналом с инверсного выхода триггера 3, и далее через элементы ИЛИ 23 и И 17 на второй вход элемента ИЛИ-НЕ 24, подтверждая нулевой уровень сигнала на его выходе (фиг. Зл).Второй такт преобразования завершен, входной сигнал нулевого уровня зафиксирован триггерами 1-4, показания которых совпали между сббой. На выход устройства поступает сигнал нулевого уровня.20На третьем такте работы преобразователя единичный сигнал с входа 27 (фиг, За) поступает на первые Б-входы триггеров 1-4, С некоторой задержкой на третьем выходе распределителя 5 формируется сигнал (фигЗг), поступающий через элементы ИЛИ 10 и 11 на вторые К- и Б-входы триггеров 3 и 4,Триггер 4 переключается в единичное состояние (фиг. Зк), а триггер 3 из-за нарушения работы остается в исходном состоянии (фиг.Зи), при котором единичный сигнал с его инверсного выхода открывает по первому входу элемент И 15. Импульс с третьего выхода распределителя 5 через эле мент ИЛИ 21, элемент И 15 и элемент ИЛИ 23 поступает на второй вход элемента И 17, но элемент И 17 закрыт по первому входу нулевым сигналом с инверсного выхода триггера 4. Элемент 40 И 1 б также закрыт по второму входу сигналом нулевого уровня с элементов И 14, ИЛИ 22. Поэтому на входах. элемента ИЛИ-НЕ 24 действуют сигналы нулевого уровня. Когда и на третьем45 входе элемента ИЛИ-НЕ 24 с выхода формирователя 8 устанавливается нулевой уровень сигнала (фиг, Зе), то на выходе элемента ИЛИ-НЕ 24 формируется единичный сигнал (фиг. Зл), кото рый поступает на выход 28 устройства и фиксирует возникшее нарушение работы преобразователя,Третий такт преобразования завершен, на вход 27 устройства поступил единичный сигнал, но из-за нарушения работы триггер 3 остался в исходном состоянии, а триггер 4 переключился в единичное состояние, Показания триггеров 3 и 4 не совпали, на выход устройства поступил сигнал нарушения работы устройства.Дальнейшая работа преобразователяпроисходит аналогично.На каждом К-м такте входной сигналзапоминается К-м триггером информационного разряда и (И-К) триггерами последующих разрядов. Показания (И-К+1)триггеров сравниваются между собой,нормальной работе устройства без сбоев и без отказов соответствует совпадение показаний триггеров.Несовпадение показаний триггеровсвидетельствует о нарушении работыэлементов преобразователя, о нарушении, которое выявляется оперативнов процессе основной работы, при этом,сразу же на данном такте преобразова,ния на выход устройства поступаетсигнал неисправности, тем самым влияние нарушения работы может быть нейтрализовано сразу же на данном тактепреобразования.Преобразование первых (И) разрядов всегда происходит с более высокойконтролирующей способностью, т.е. имеется возможность более полно выявитьнарушения работы преобразователя, чемв известном устройстве. Преобразование остальных разрядов (Р+1) в предлагаемом устройстве осуществляется сконтролирующей способностью не хуже,чем в известном,В случае, если входная информацияпредставляется словами переменнойдлины, то при поступлении короткихслов лишние разряды преобразователяиспользуются для дополнительного резервирования информационных разрядови повышают контролирующую способность устройства.формула изобретения1. Преобразователь последовательного кода в параллельный, содержащий распределитель имцульсов и группу иэ И триггеров, где И - число выходных разрядов, причем первые Б-входы триггеров объединены и подключены к информационному входу преобразователя, который через элемент НЕ соединен с первыми К-входами триггеров группы, вторые К- и Б-входы первого триггера группы соединены с первым выходом распределителя импульсов, о т л и1383508 ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей эа счет обеспечения контроля работы преобразователя, в него введены М) элементов ИЛИ, формирователь Импульсов и схема поразрядного сравнения, первая и вторая группы входов которой соединены соответственно сямыми и инверснымивыходами триггеов группы, д-й д=1+И) выход распрееления импульсов соединен с 1-ми ходами с -го по (Б)-й элементы Фвыходы которых соответвенно соединены с вторыми К- и Я-входами с И+1)-го по Н-й триггеров группы, 1-й (1= 2+0) выход распределителя имльсов соединен с Ц)-м входом опроса поразрядной схемы сравнения, й вход опроса которой соединен с 20 выходом формирователя импульсов, вход которого соединен с выходом (0-1)-го э емента ИЛИ, выход поразрядной схесравнения является выходом преобразователя. 25 2. Преобразователь по п. 1, о тли ч а ю щ и й с я тем, что в нем сМема поразрядного сравнения содержит эремент ИЛИ-НЕ, первую и вторую груп 10пы из (И) -го элемента И, первую и вторую группы из (И)-го элемента ИЛИ, первые входы первых элементов ИЛИ обоих групп соответственно соединены с входами первых разрядов первой и второй групп разрядных входов схемы поразрядного сравнения, первые входы К-х (К=2+И) элементов ИЛИ первой и второй групп соответственно соединены с выходами (К)-х элементов И первой и второй групп, первые входы которых соединены с выходами (К)-х элементов ИЛИ первой и второй групп соответственно, вторые входы К-х элементов ИЛИ первой и второй групп объединены и являются К-ми входами опроса поразрядной схемы сравнения, К-й вход опроса которой соединен с первым входом элемента ИЛИ-НЕ, второй и третий входы которого соединены с выходами (И)-х элементов И первой и второй групп соответственно, а выход элемента ИЛИНЕ является выходом схемы поразрядного сравнения, входы с второго по (И)-й первой и второй групп которой соединены соответственно с вторыми входами элементов И первой и второй групп.Составитель М,АршавскийРедактор Л,Лангазо Техред М. Ходанич Кор екторМ.ШарошиРРЗаказ 1351/55 Тираж 928 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 4/5

СмотретьЗаявка

4139167, 27.10.1986

ПРЕДПРИЯТИЕ ПЯ М-5156

ГЛАДКОВ ЮРИЙ ВИКТОРОВИЧ, ЕВСЕЕВ ЕВГЕНИЙ АЛЕКСАНДРОВИЧ, ПЛУЖНИКОВ ЮРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 9/00

Метки: кода, параллельный, последовательного

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/7-1383508-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Дешифратор

Следующий патент: Устройство для исправления ошибок

Случайный патент: Саморазгружающийся стенд для сборки и сварки