Устройство для вычисления логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1367011

Авторы: Кашковский, Сорокин, Устинов

Текст

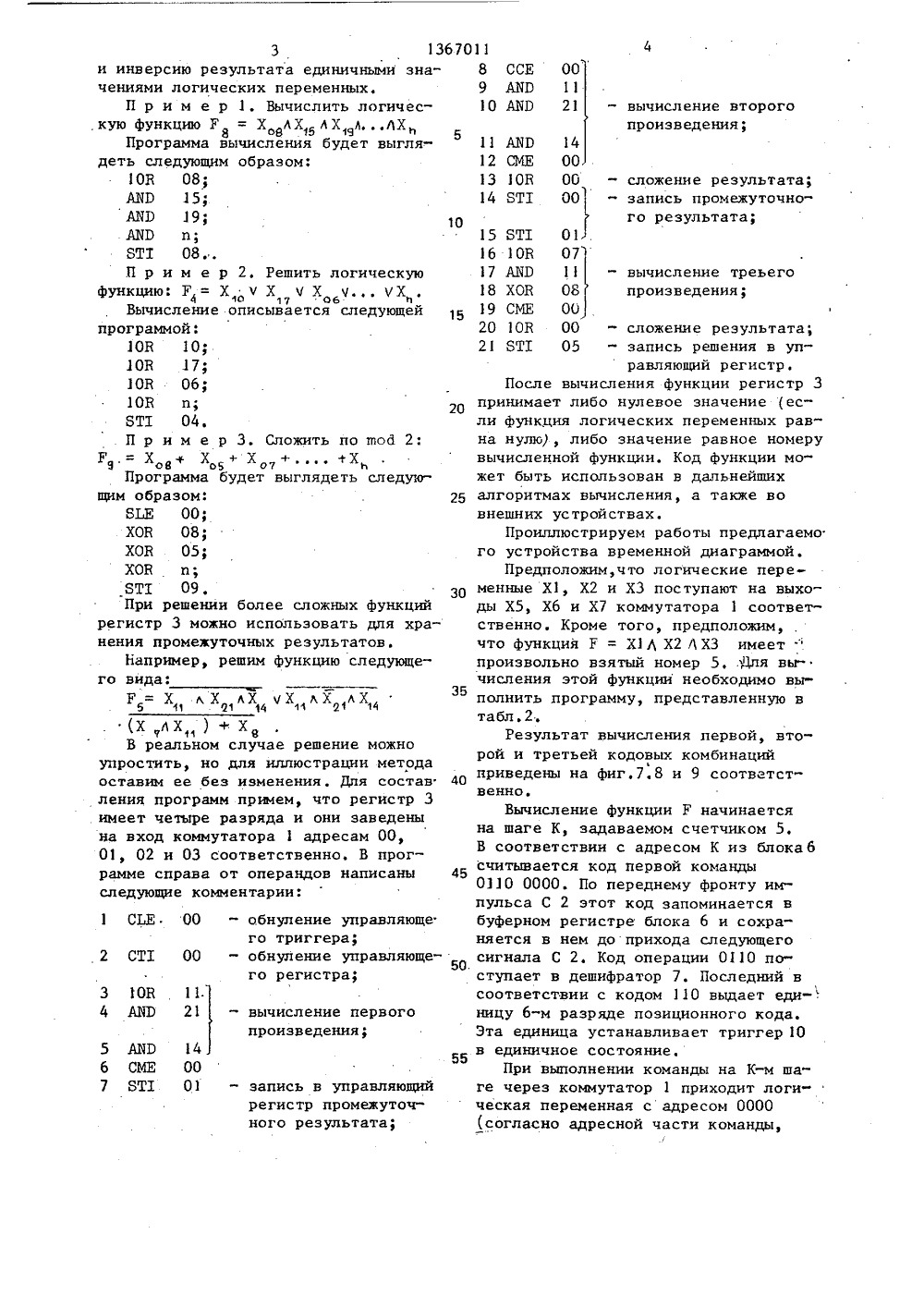

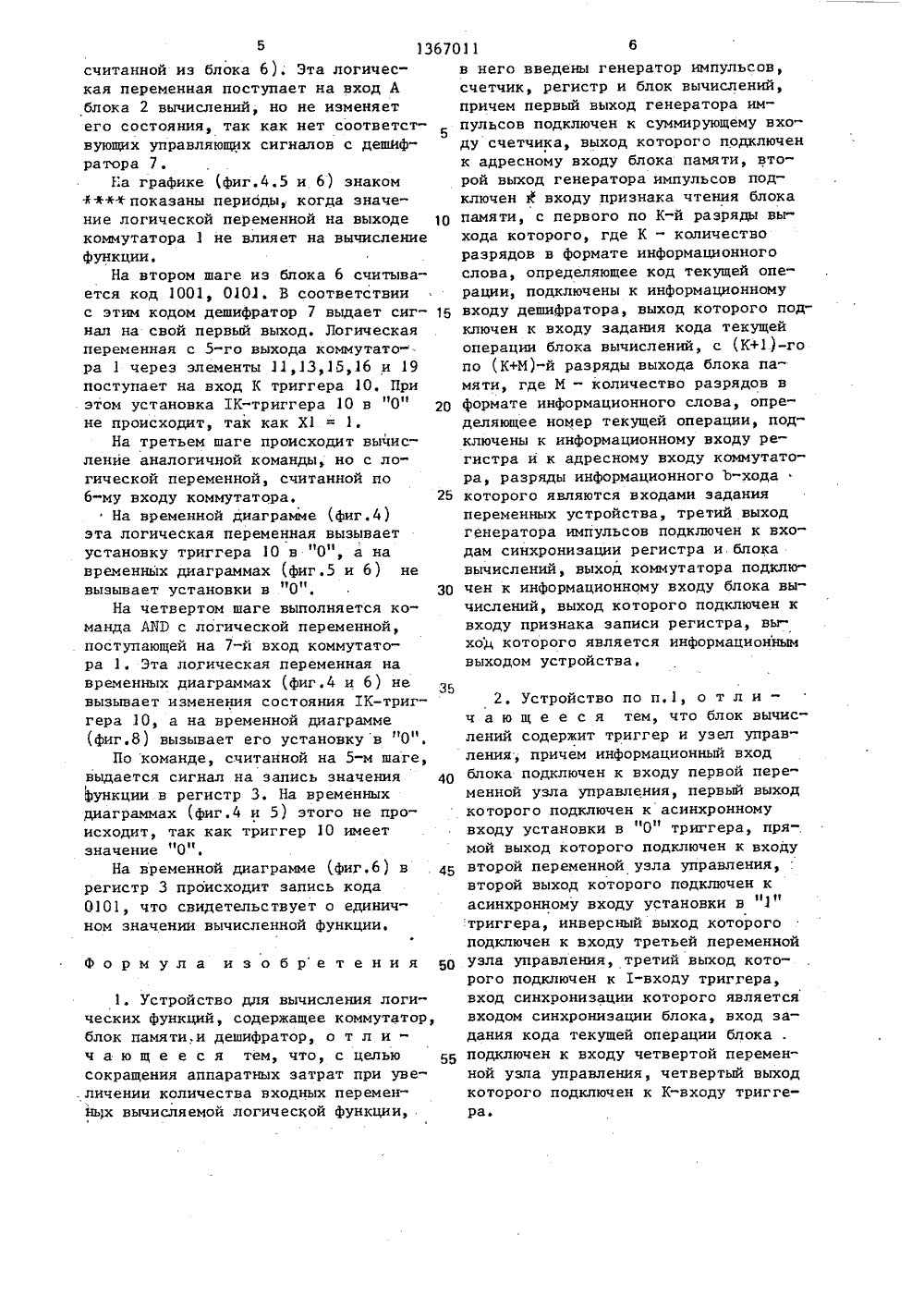

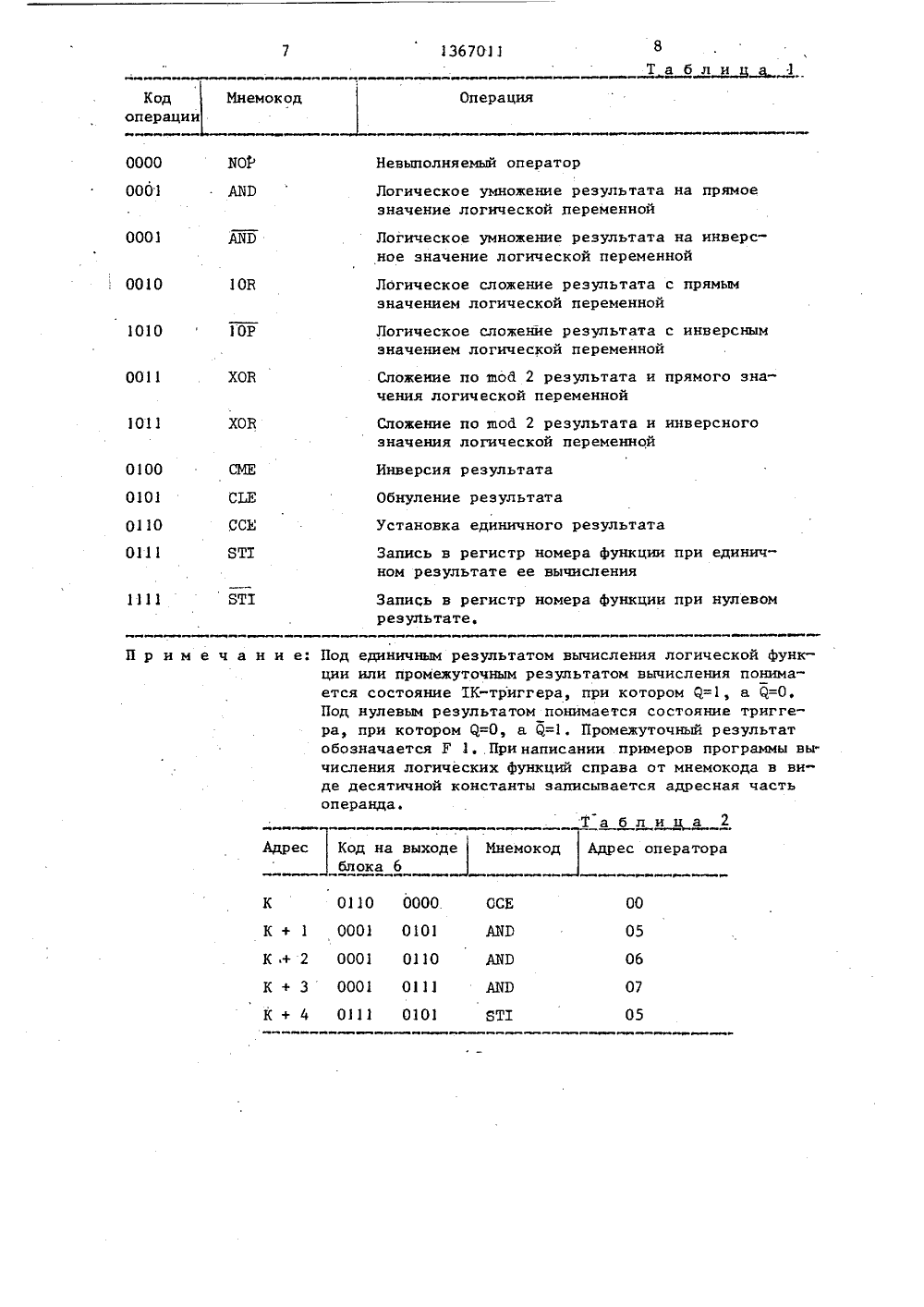

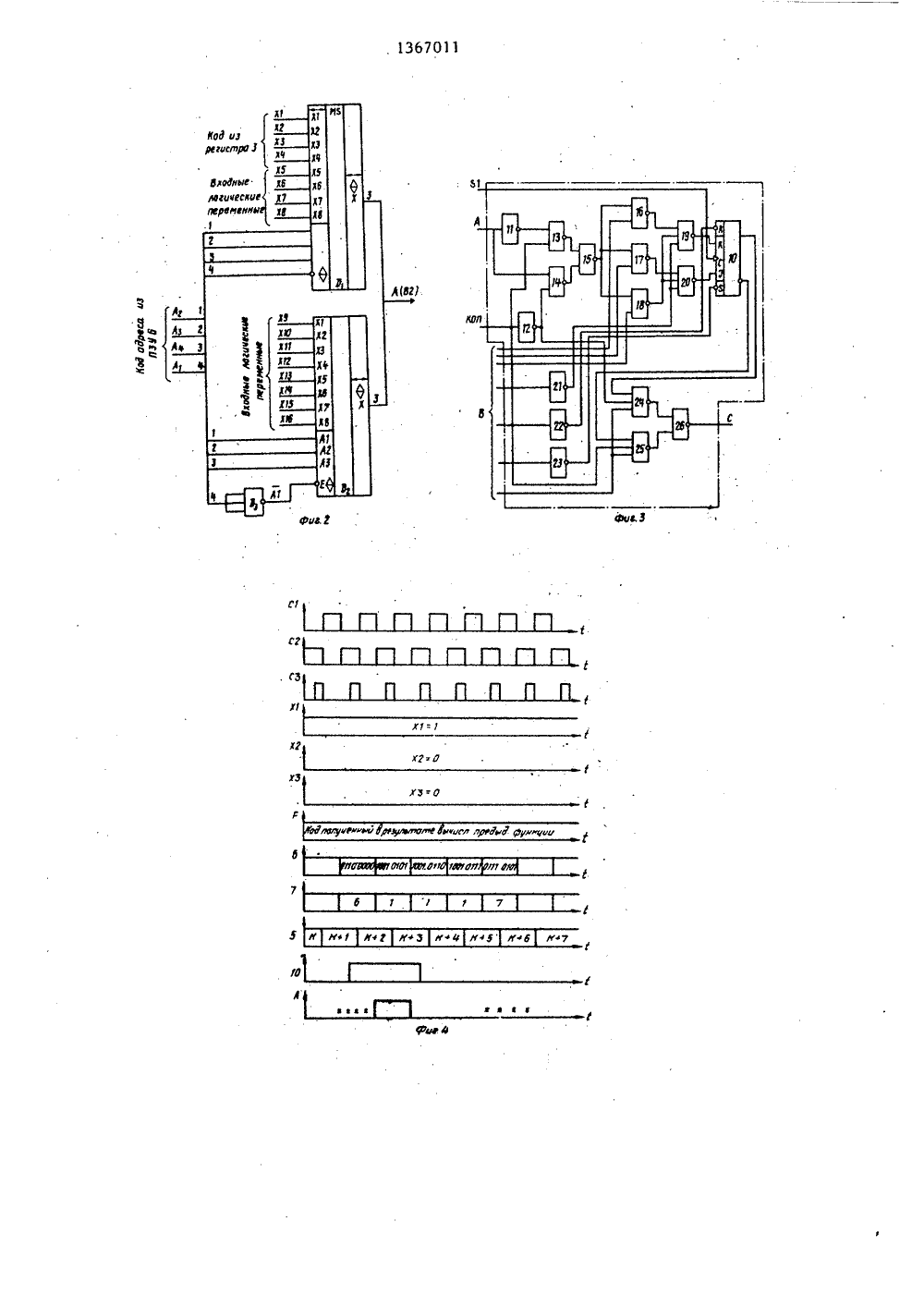

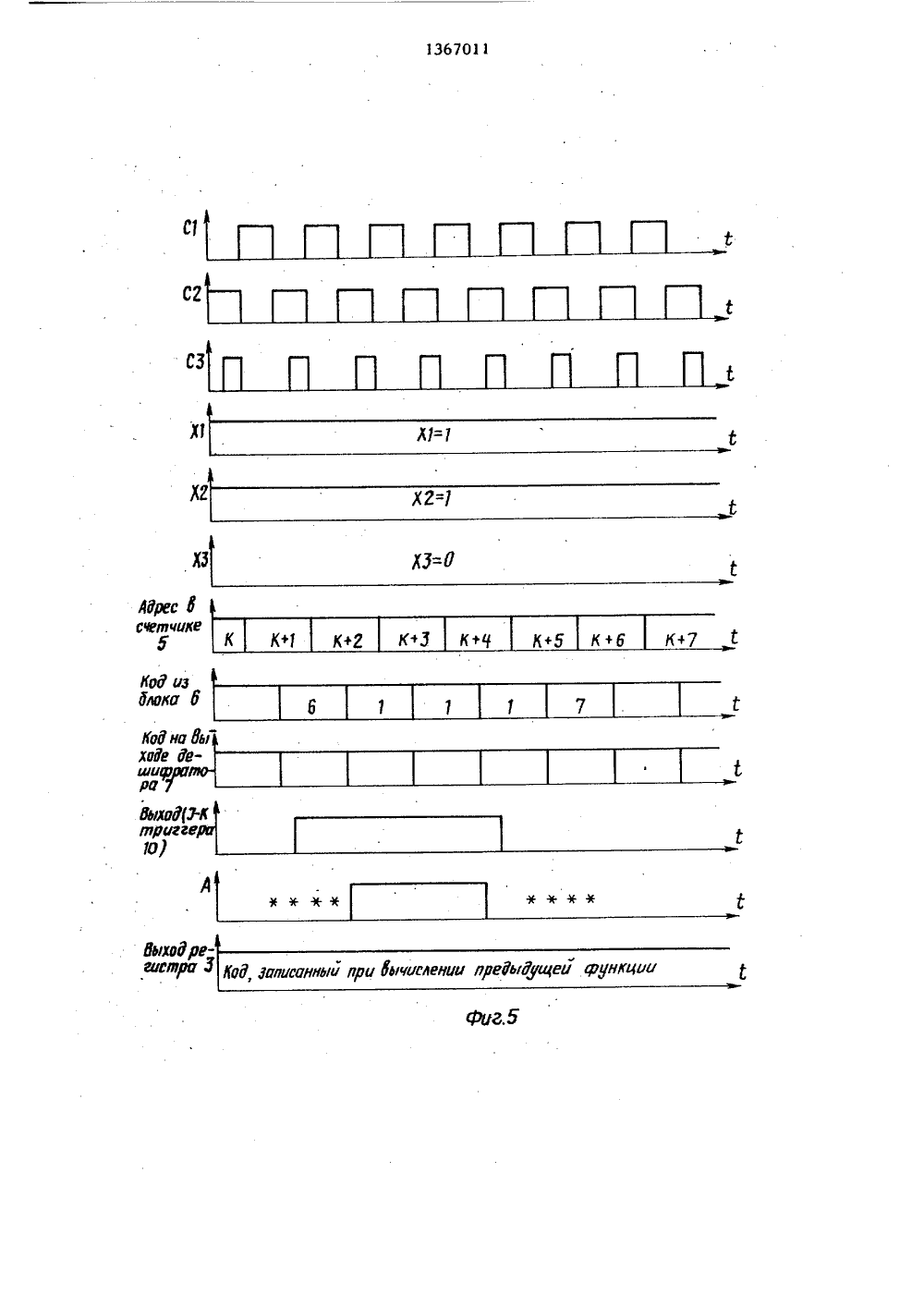

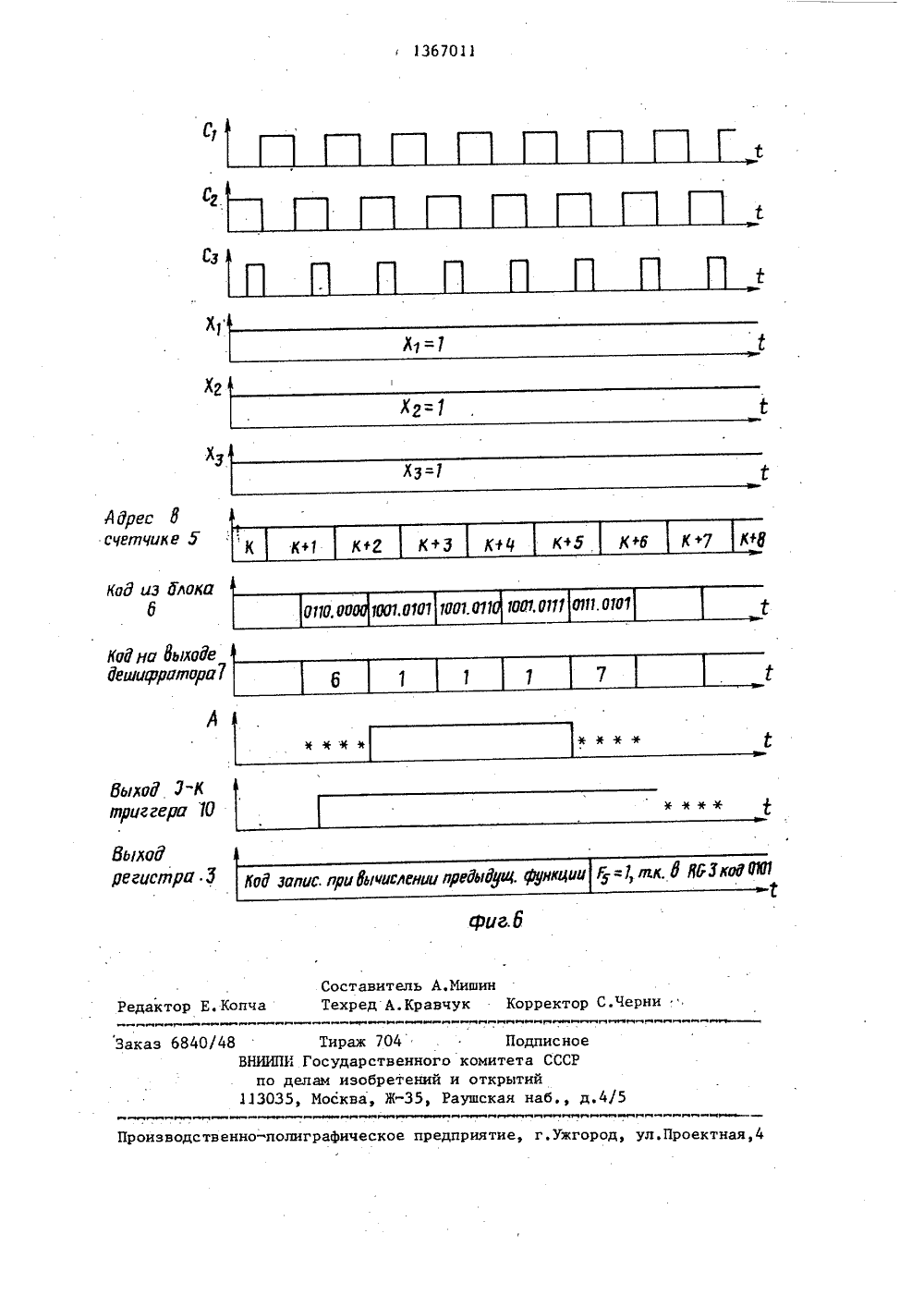

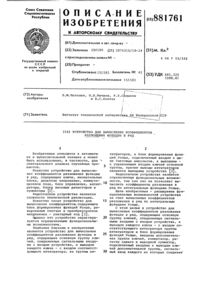

(088.8)ое свидетелС 06 Г 15свидетельс0 06 Р 15 рокин ьство СССР/32, 1974,ЧИСЛЕН 1 И ЛОГИтносится к вычис может быть испол требующичеств вычис жных т многи ис темах пер емеехниказов,й на бо аспоз рту лев систе а такж СУДАРСТВЕННЫЙ НОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ А ВТОРСНОМУ СВИДЕТЕЛЬСТ(54) УСТРОЙСТВО ДЛЯЧЕСКИХ ФУНКЦИЙ(57) Изобретениетельной технике изовано в системахления большого коллогических функцииных, в частностической диагностиквания особых ситтательного аппара мах управления технологическими процессами. Целью изобретения являетсясокращение оборудования при увеличении количества входных переменныхвычисляемой логической функции.Устройство содержит коммутатор 1, блок 2вычислений, регистр 3, генератор 4импульсов, счетчик 5, блок 6 памяти,дешифратор 7, информационный вход 8,информационный выход 9, В блоке 6хранятся команды и применено последовательное решение логических функцийнескольких переменных. Основным узлом для вычисления логических функций является блок 2 вычислений, объемоборудования которого не зависит отколичества входных логических переменных, что позволяет резко снизитьнеобходимый объем блока 6 памяти приувеличении количества входных логических переменных,. 1 з.п.ф-лы,2 табл.136701 35 Изобретение относится к вычислительной технике и может быть использовано в устройствах, требующих решения большого числа сложных логичес 5 ких функций от многих переменных, в частности в устройствах технической диагностики отказов функциональных систем, а также для решения задач в системах управления.10Целью изобретения, является сокращение оборудования при увеличении входных переменных вычисляемой логической функции.На фиг.1 изображена функциональная схема устройства; на фиг,2 - пример функциональной схемы коммутатора; на фиг,З - пример функциональной схемы блока вычислений; на фиг.4 - временная диаграмма вычисления фунКции Р = Х 1 ПХ 2 лХЗ при Х 1=1, Х 2=0, ХЗ=О, где Х - обозначение входной переменной; на фиг,5 - временная диаграмма вычисления функции Р при Х 1=1, Х 2=1 и ХЗ=О; на фиг.6 - временная диаграм ма вычисления функции Р при Х 1 Х 2= =Х 3=1.Устройство содержит коммутатор 1, блок 2 вычислений, регистр 3, генератор 4 импульсов, счетчик 5, блок 6 З 0 памяти, дешифратор 7, информационный вход 8, информационный выход 9.Пример исполнения коммутатора для 16 логических переменных показан на микросхемах Р ,Ви Р, Микросхе 1 фмы В и Р - типа 564 КП 2, Р - типа 564 ЛА 9 или им подобные.На входы Х 1,Х 4 коммутатора подается 4-разрядный код с выхода регистра 3.40На входы А 1,.А 4 поступает 4-разрядный код адреса,с выхода блока 6 памяти, 12 входных логических переменных поступают на входы Х 5,Х 16. Микросхемы П и 0 предназначены для коммутации айалоговых и цифровых сигналов и имеют три состояния по выходу Х: логический уровень сигнала "1"; логический уровень сигнала 0" высокое выходное сопротивление.В состоянии высокого выходного сопротивления выход Х заперт для протекания тока в любом направлении. Для приведения Р или Р в третье состояние необходимо на вход Е микросхемы подать сигнал Р уровня логической единицы.На вход Р микросхемы 0 поступает сигнал А 1, а на вход Е микросхемы 1 2Р - сигнал А 1. Таким образом, при подаче любого кода адреса входной сигнал будет проходить только через одну микросхему Эили ПМикросхема, включенная разрядом А 1, передает на выход в линию А входной сигнал в соответствии с кодом адреса А 2, АЗ, А 4. Таким образом,.по линии А всегда будет проходить один из входных сигналов.Блок 2 вычислений содержит триггер 10 и элементы И-НЕ 11-26 узла управления.Устройство работает следующим образом.Основу вычисления логических функ" ций составляют операции, выполняемые 1 К-триггером 10.Логические переменные в порядке очереди, заданной программой вычисления функции, поступают на вход А блока 2 вычислений, который в соответствии с командой, поданной на его вход В из дешифратора 7, передает эти логические переменные. в прямой;. или инверсном виде на входы 1 и (или) К триггера 10. При этом подача инверсного значения логической переменной на вход К соответствует операции логического умножения данной логической переменной на результат предыдущего вычисления, хранящихся в 1 К-триггере 10. Подача прямого значения логической переменной на вход 1 соответствует операции ИЛИ между данной логической переменной и результатом выполнения предыдущей операции, хранящимся в 1 К-триггере 10, Аналогично подача логической переменной на входы 1 и К . одновременно соответствует операции сложения по шо 6.2. Операции, выполняемые триггером 2,описаны в табл.3. Для удобства этиоперации обозначены мнемокодами,Сущность вычисления с помощью 1 К-триггера 10 заключается в том,что . при выполнении команды 10 В с логической переменной, имеющей единичное значение, результат также примет единичное значение. При выполнении. команды АБО результат будет сброшен, если логическая переменная равна нулю. Сложение по той 2, в свою очередь, представляет из себя подачу логических переменных на счетный вход118 ССЕ 00 9 АБО 11 10 АБО 21 вычисление второгопроизведения; 14 00 11 АБО 12 СМЕ 13 10 В 14 ЯТ 1 01 07 11 08 00 15 БТ 1 16 10 В 17 АБ 1) 8 ХОВ 19 СМЕ 20 10 В 21 ЯТ 1 вычисление треьегопроизведения; 00 - сложение результата;05 - запись решения в управляющий регистр.После вычисления функции регистр 3принимает либо нулевое значение (если функция логических переменных равна нулю), либо значение равное номерувычисленной функции. Код функции может быть использован в дальнейшихалгоритмах вычисления, а также вовнешних устройствах.Проиллюстрируем работы предлагаемого устройства временной диаграммой.Предположим,что логические переменные Х 1, Х 2 и ХЗ поступают на выходы Х 5, Х 6 и Х 7 коммутатора 1 соответственно, Кроме того, предположим,что функция Р = Х 1 Д Х 2 Л ХЗ имеет .произвольно взятый номер 5, .Для вычисления этой функции необходимо выполнить программу, представленную втабл.2,Результат вычисления первой, второй и третьей кодовых комбинаций0 приведены на фиг.7,8 и 9 соответственно.Вычисление функции Р начинаетсяна шаге К, задаваемом счетчиком 5.В соответствии с адресом К из блока 65 считывается код первой команды0110 0000. По переднему фронту импульса С 2 этот код запоминается вбуферном регистре блока 6 и сохраняется в нем до прихода следующегосигнала С 2. Код операции 0110 поступает в дешифратор 7. Последний всоответствии с кодом 110 выдает еди-ницу 6-м разряде позиционного кода.Эта единица устанавливает триггер 10в единичное состояниеПри выполнении команды на К-м шаге через коммутатор 1 приходит логическая переменная с адресом 0000- вычисление первого произведения; 5 АБР 14 6 СМЕ 00 7 БТ 1 01 55 запись в управляющийрегистр промежуточного результата; Э 13670и инверсию результата единичными значениями логических переменных.П р и м е р 1, Вычислить логическую функцию Р = Х лХ лХ лЛХ5Программа вычисления будет выглядеть следующим образом:10 В 08;АБО 15;АБЭ 19;1 ОАБП и;ЯТ 1 08П р и м е р 2. Решить логическуюфункцию. У Х чХ чХ чЧХ.Вычислейие описывается следующейпрограммой:1 ОВ 10;10 В 171 ОВ 06 р10 В и;БТ 1 04.П р и м е р 3. Сложить по шод 2:Программа будет выглядеть следующим образом: 2Я 1 Е 00;ХОВ 08;ХОВ 05;ХОВ и;ЯТ 1 09,3При решении более сложных функцийрегистр 3 можно использовать для хранения промежуточных результатов.Еапример, решим функцию следующего видах,= х вх вх чхвхвх,Я 1 14 11(Х ЛХ,)+ХВ реальном случае решение можноупростить, но для иллюстрации методаоставим ее без изменения, Для состав 4ления программ прыщем, что регистр 3имеет четыре разряда и они заведенына вход коммутатора 1 адресам 00,01, 02 и 03 соответственно. В программе справа от операндов написаны 4следующие комментарии:- обнуление управляюще.го триггера;- обнуление управляюще 50го регистра; 00 - сложение результата; 00 - запись промежуточного результата;5 1367011считанной из блока 6). Эта логическая переменная поступает на вход Аблока 2 вычислений, но не изменяетего состояния, так как нет соответствующих управляющих сигналов с дешифрагора 7,Еа графике (фиг.4.5 и 6) знаком+ показаны периоды, когда значение логической переменной на выходе 10коммутатора 1 не влияет на вычислениефункции,На втором шаге из блока 6 считывается код 1001, 0101. В соответствиис этим кодом дешифратор 7 выдает сигнал на свой первый выход. Логическаяпеременная с 5-го выхода коммутато"ра 1 через элементы 11,13,15,16 и 19поступает на вход К триггера 10, Приэтом установка 1 К-триггера 10 в "0" 20не происходит, так как Х 1 = 1.На третьем шаге происходит вычисление аналогичной команды, но с логической переменной, считанной по6-му входу коммутатора. 25На временной диаграмме (фиг,4)эта логическая переменная вызываетустановку триггера 10 в "0", а навременных диаграммах (фиг.5 и 6) невызывает установки в "0". 30На четвертом шаге выполняется команда АИЭ с логической переменной,поступающей на 7-й вход коммутатора 1. Эта логическая переменная навременных диаграммах (фиг.4 и 6) невызывает изменения состояния 1 К-триггера 10, а на временной диаграмме(фиг.8) вызывает его установку в "0".По команде, считанной на 5-м шаге,выдается сигнал на запись значенияфункции в регистр 3. На временныхдиаграммах (фиг.4 и 5) этого не происходит, так как триггер 10 имеетзначение "О".На временной диаграмме (фиг.6) врегистр 3 происходит запись кода0101, что свидетельствует о единичном значении вычисленной функции,35 40 45 50 55 Формула изобретения 1. Устройство для вычисления логических функций, содержащее коммутатор блок памяти,и дешифратор, о т л ич а ю щ е е с я тем, что, с целью сокращения аппаратных затрат при уве.личении количества входных переменных вычисляемой логической функции,в него введены генератор импульсов,счетчик, регистр и блок вычислений,причем первый выход генератора импульсов подключен к суммирующему входу счетчика, выход которого подключенк адресному входу блока памяти, второй выход генератора импульсов подключен к входу признака чтения блокапамяти, с первого по К-й разряды выхода которого, где К - количестворазрядов в формате информационногослова, определяющее код текущей операции, подключены к информационномувходу дешифратора, выход которого подключен к входу задания кода текущейоперации блока вычислений, с (К+1.)-гопо (К+М)-й разряды выхода блока памяти, где М - количество разрядов вформате информационного слова, определяющее номер текущей операции, подключены к информационному входу регистра и к адресному входу коммутатора, разряды информационного Ь-ходакоторого являются входами заданияпеременных устройства, третий выходгенератора импульсов подключен к входам синхронизации регистра и. блокавычислений, выход коммутатора подключен к информационному входу блока вычислений, выход которого подключен квходу признака записи регистра, выход которого является информационнымвыходом устройства. 2. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок вычислений содержит триггер и узел управления, причем информационный вход блока подключен к входу первой переменной узла управления, первый выход которого подключен к асинхронному входу установки в "0 триггера, пря-, мой выход которого подключен к входу второй переменной узла управления, второй выход которого подключен к асинхронному входу установки в "1 " триггера, инверсный выход которого подключен к входу третьей переменной узла управления, третий выход которого подключен к 1-входу триггера, вход синхронизации которого является входом синхронизации блока, вход задания кода текущей операции блока . подключен к входу четвертой переменной узла управления, четвертый выход которого подключен к К-входу триггера.Операция Мнемокод 0000 Невыполняемый оператор Логическое умножение результата на прямоезначение логической переменной 0001 АБО 0001 Логическое умножение результата на инверсное значение логической переменной 0010 10 В Логическое сложение результата с прямымзначением логической переменной 10 Р 1010 Логическое сложение результата с инверснымзначением логической переменной Сложение по шой 2 результата и прямого значения логической переменной 0011 ХОВ ХОВ Сложение по шой 2 результата и инверсногозначения логической переменной 1011 Инверсия результатаОбнуление результатаУстановка единичного результата 0100 0101 0110 0111 Запись в регистр номера функции при единичном результате ее вычисления Запись в регистр номера функции при нулевомрезультате. Под единичным результатом вычисления логической функции или промежуточным результатом вычисления понимается состояние 1 К-триггера, при котором =1, а 4=0.Под нулевым результатом понимается состояние триггера, при котором Я=О, а Я=1. Промежуточный результатобозначается Р 1. При написании примеров программы вы"числения логических функций справа от мнемокода в виде десятичной константы записывается адресная частьоперанда. Пр им еч ание: Таблица 2 Код на выходе Инемокод Адрес оператораблока 6евтет е веевеетет тв твтв еетеевтев ее е теев ееев ею евввев вб теетеет Адрес 0110 0000. ОСЕ 00 К К + 1 0001 0101 АБЭ К .+ 2 0001 0110 ИП) К + 3 0001 0111 АБО К + 4 0111 0101 ЯТ 1 05 06 07 05136701 1 С 2 Х 1 Х ХЗ цеячцк Код из Йока о хаВ шло РУ йходР- ериле 10) йгходрг гистра1367011 Х д из дл оставитель А.Ми ехред А.Кравчу Е. Коп орректор С,Черни каз 6840 303 Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная Адрес 8четчике Х Код но аыхо дешиуратор Выход,7-Ктриггера 10 Вихооегистр Тираж 704Государственногоделам изобретений5, Москва, Ж, Р Подписноекомитета СССРоткрытийушская наб., д.4/

СмотретьЗаявка

4064320, 10.02.1986

ИРКУТСКОЕ ВЫСШЕЕ ВОЕННОЕ АВИАЦИОННОЕ ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. 50-ЛЕТИЯ ВЛКСМ

КАШКОВСКИЙ ВИКТОР ВЛАДИМИРОВИЧ, СОРОКИН ПАВЕЛ НИКОЛАЕВИЧ, УСТИНОВ ВЛАДИМИР ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: вычисления, логических, функций

Опубликовано: 15.01.1988

Код ссылки

<a href="https://patents.su/8-1367011-ustrojjstvo-dlya-vychisleniya-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логических функций</a>

Предыдущий патент: Многофункциональный логический модуль

Следующий патент: Операционное устройство

Случайный патент: Крутильные весы