Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

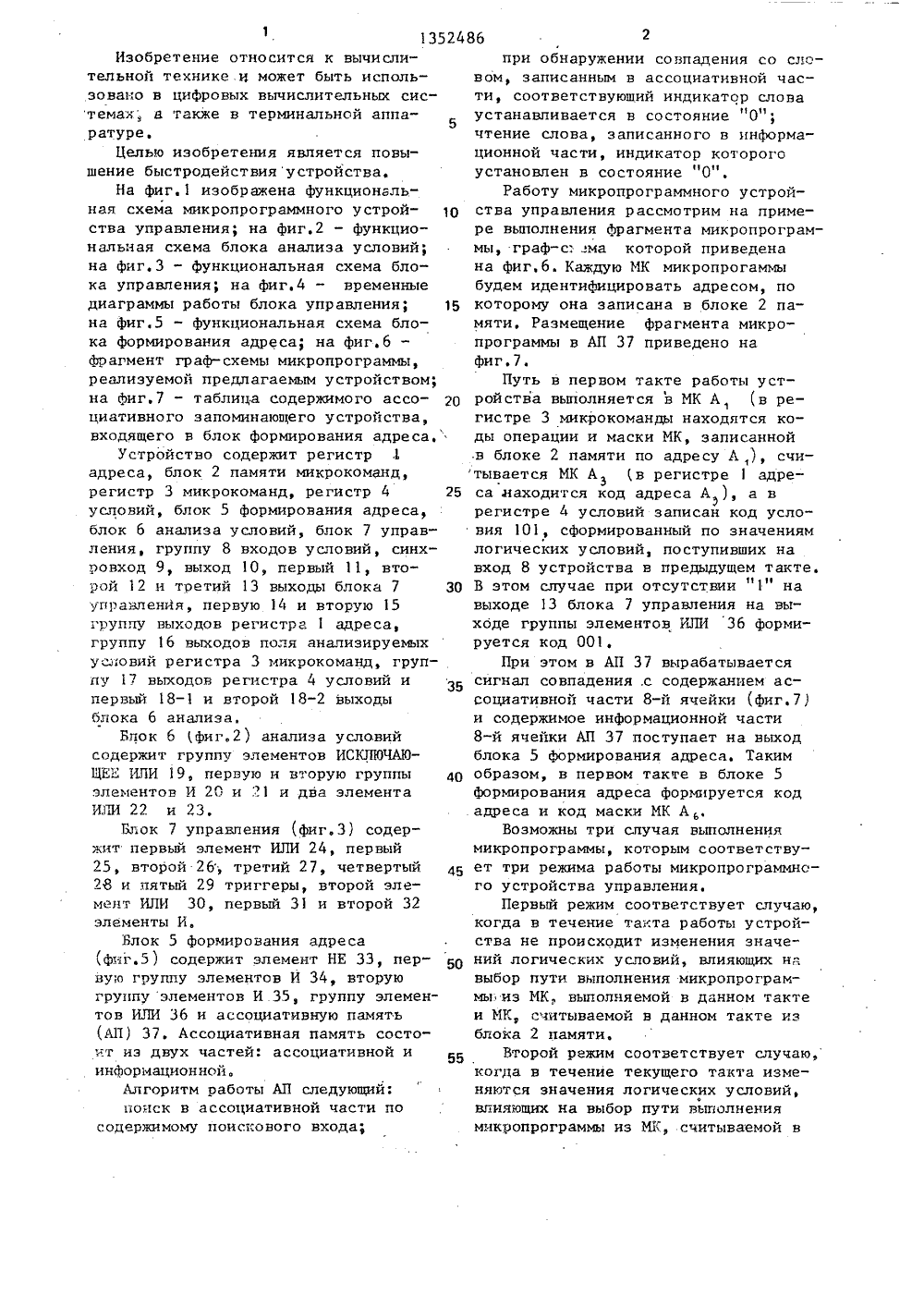

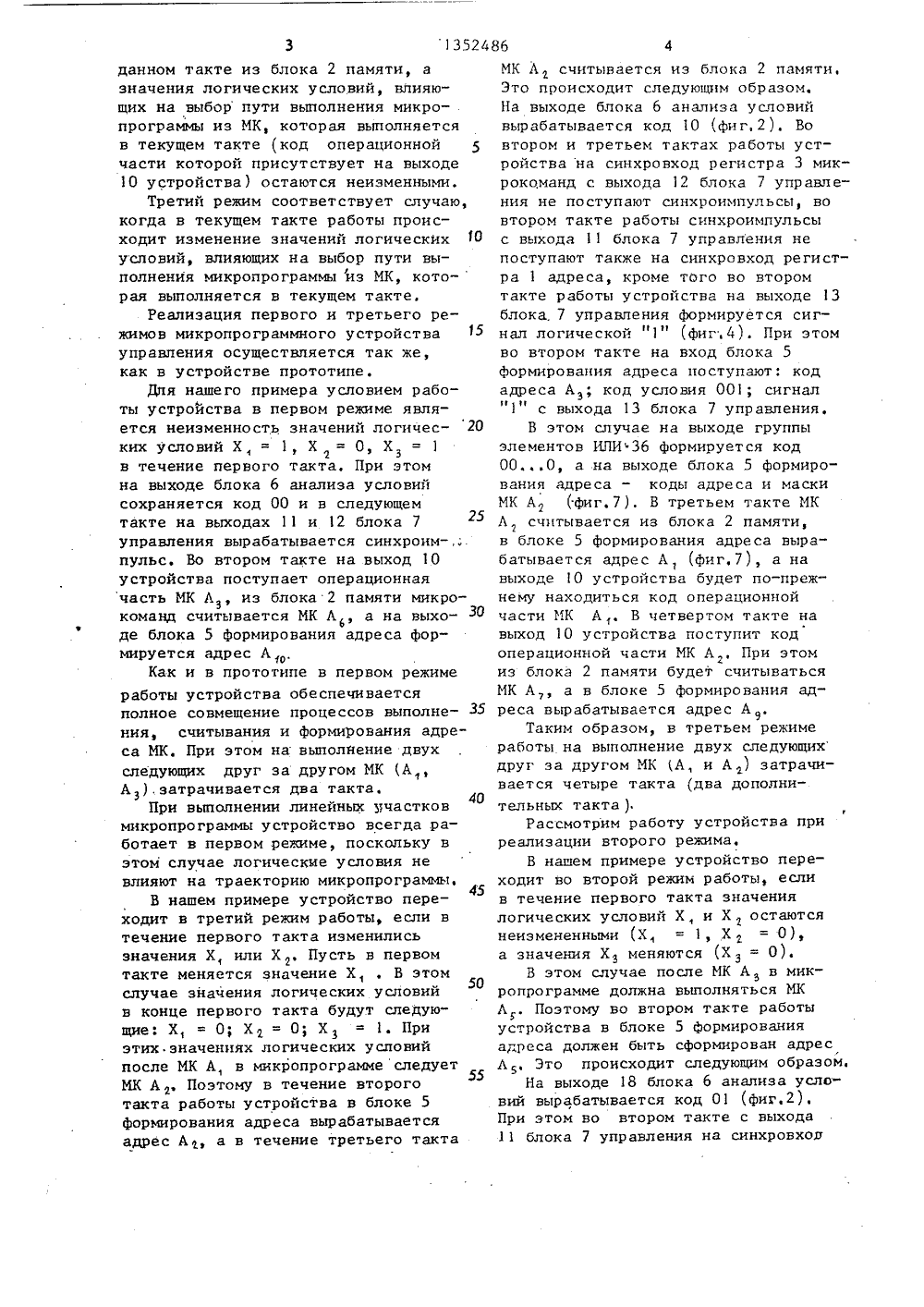

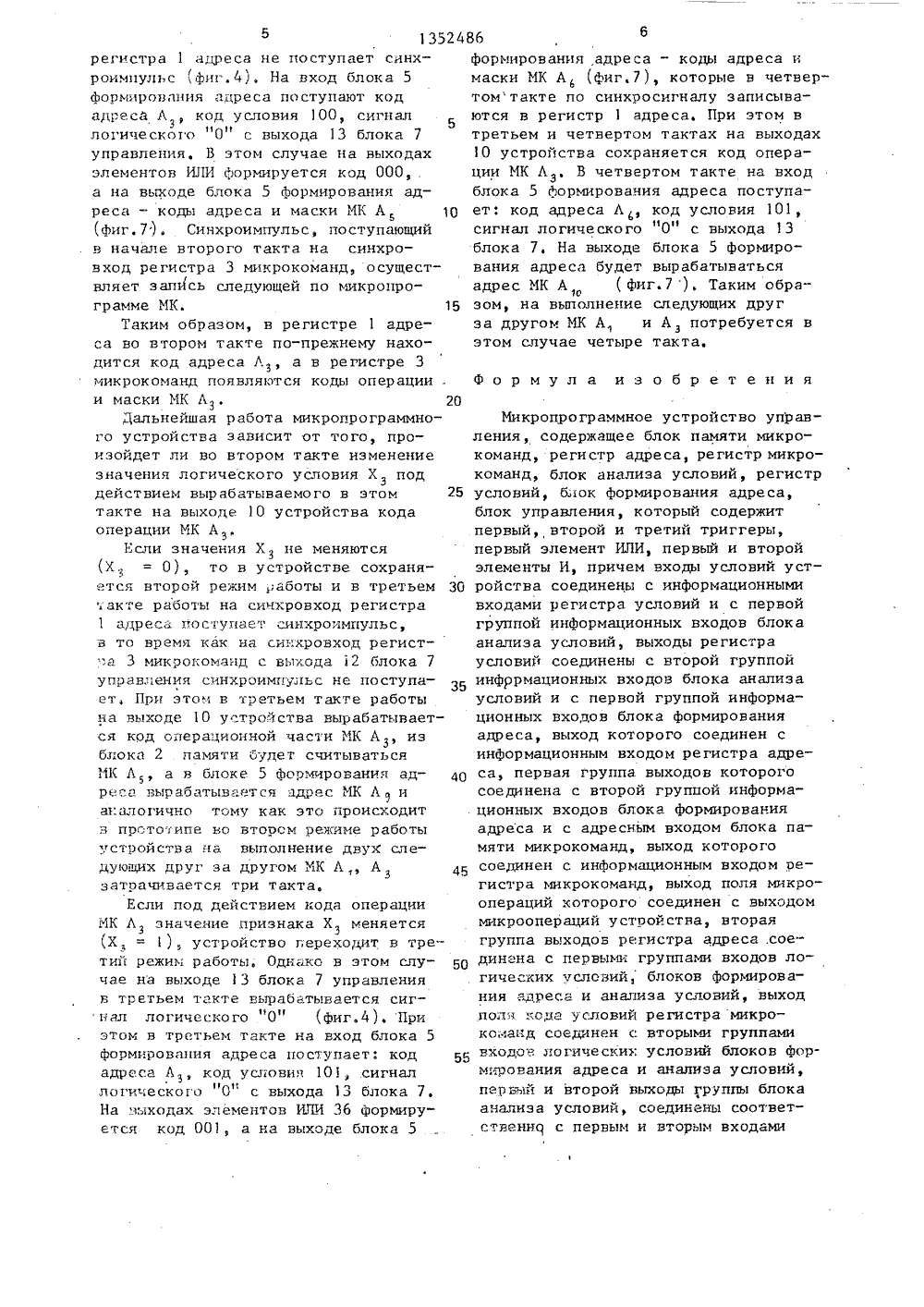

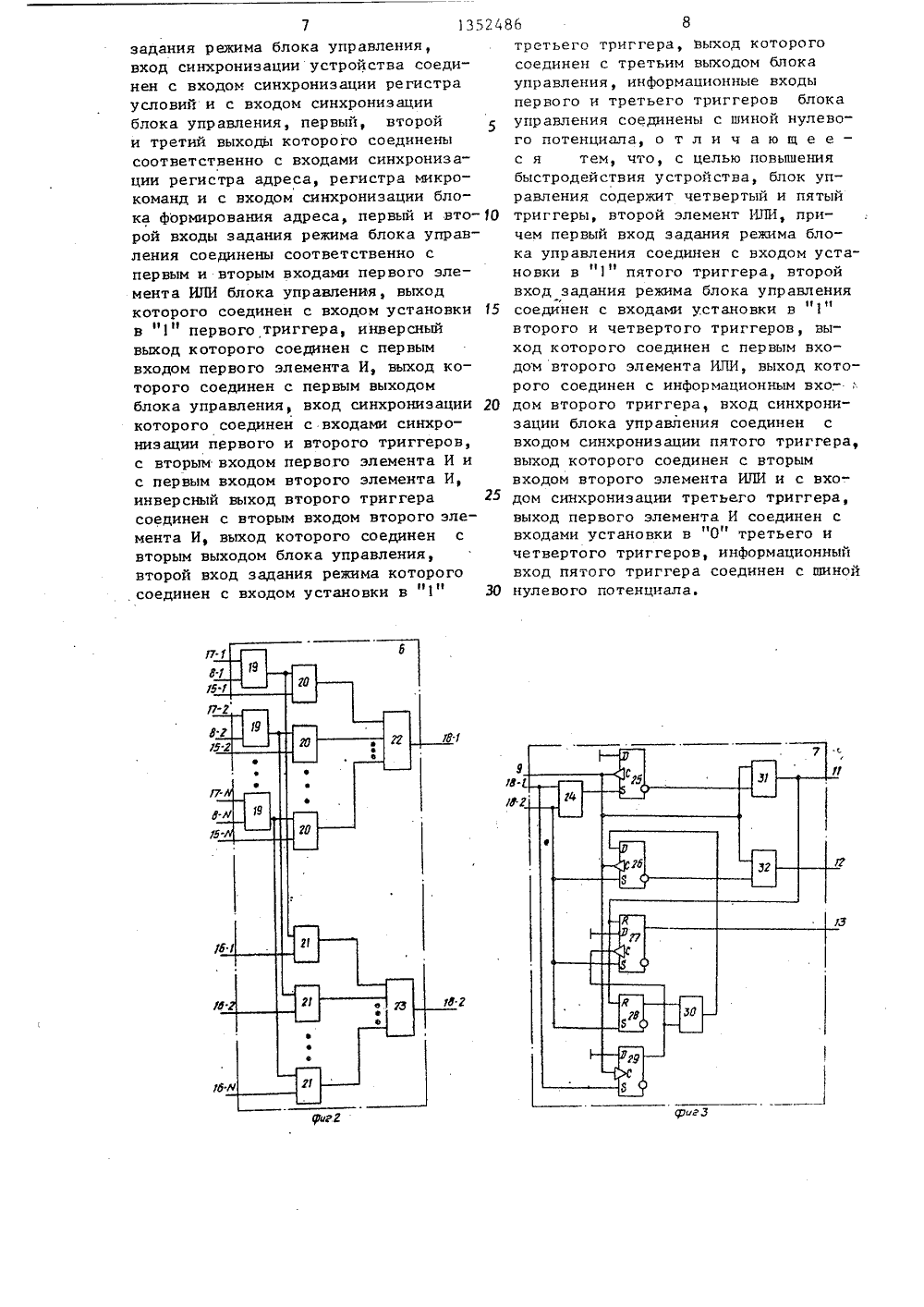

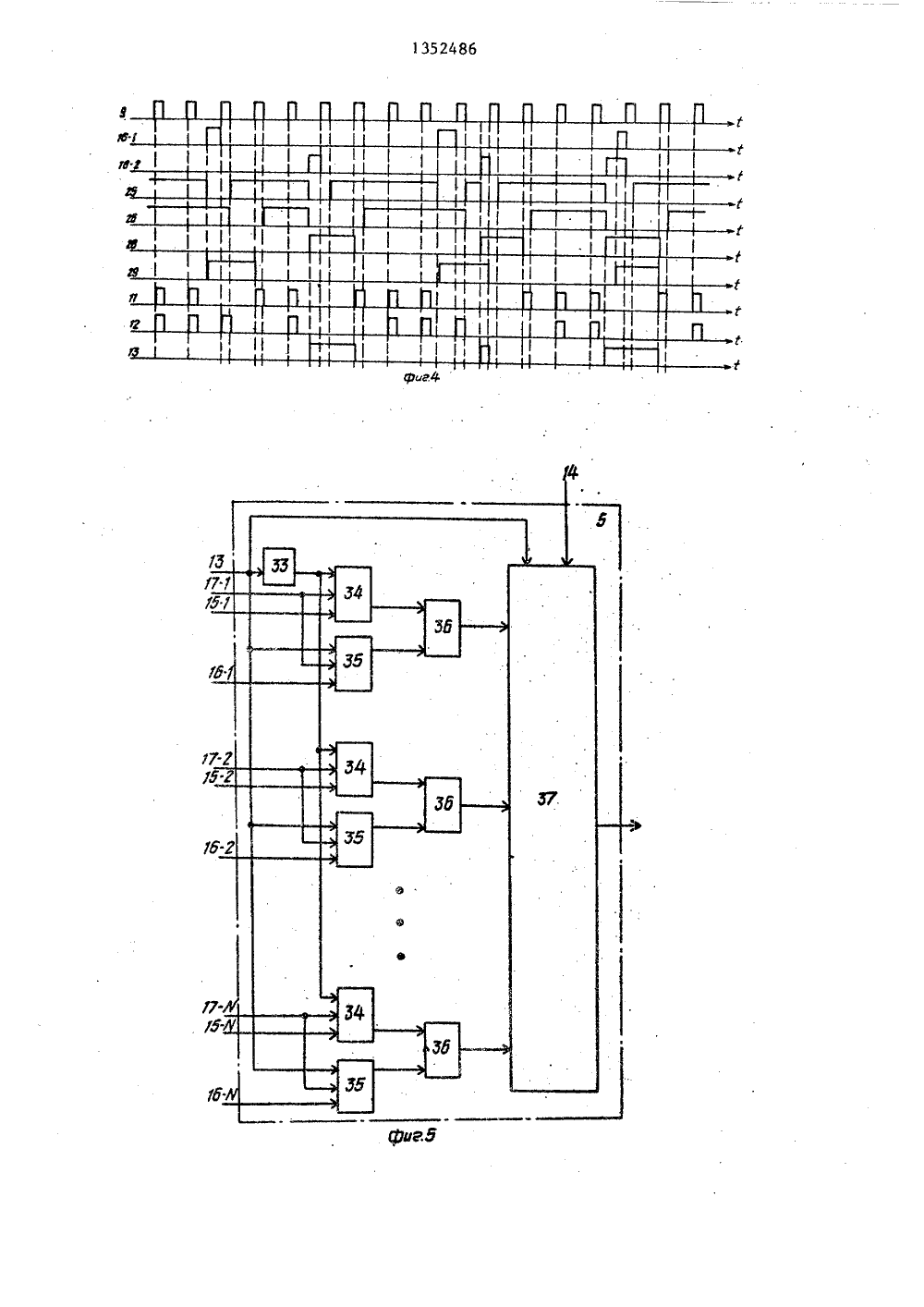

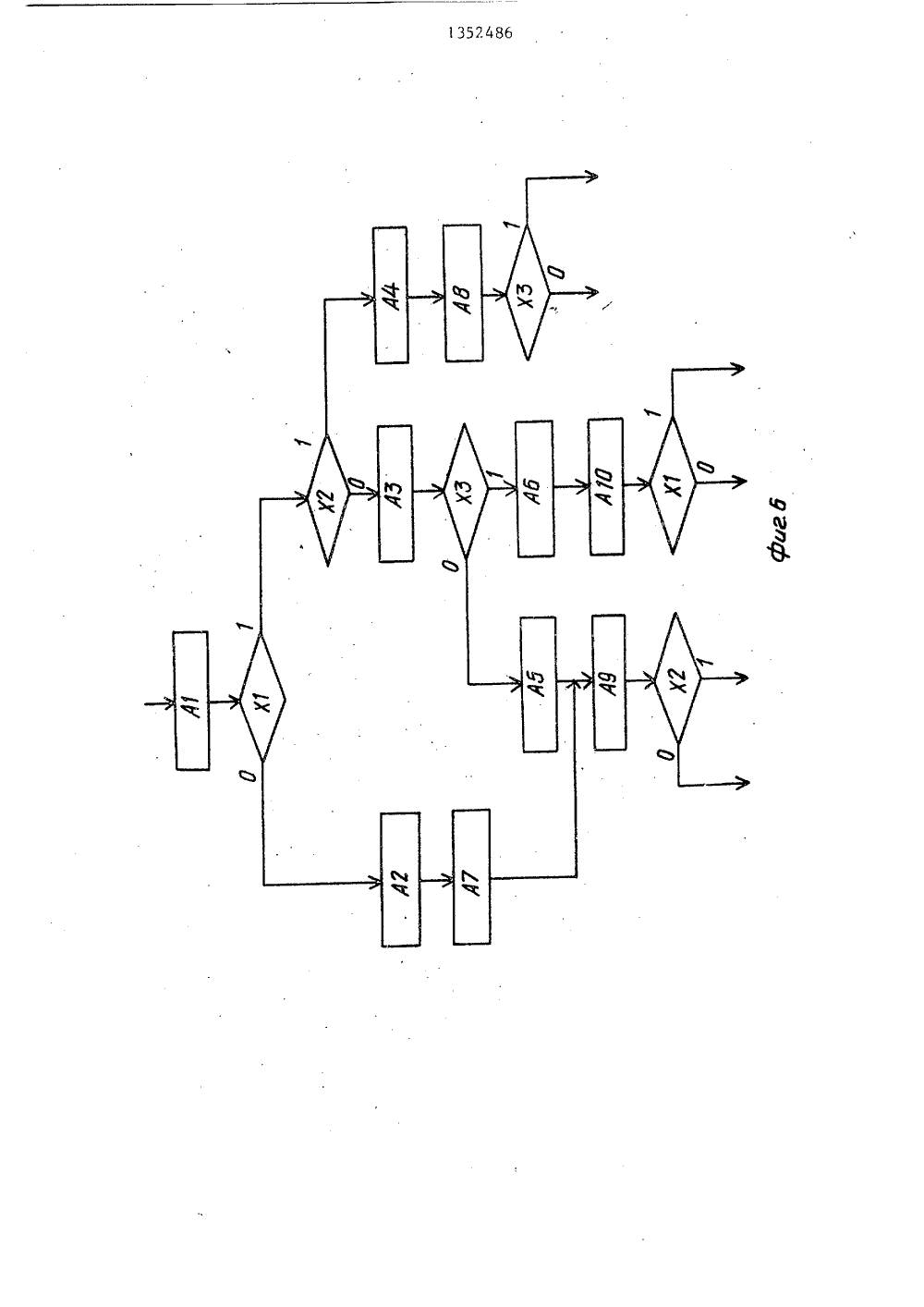

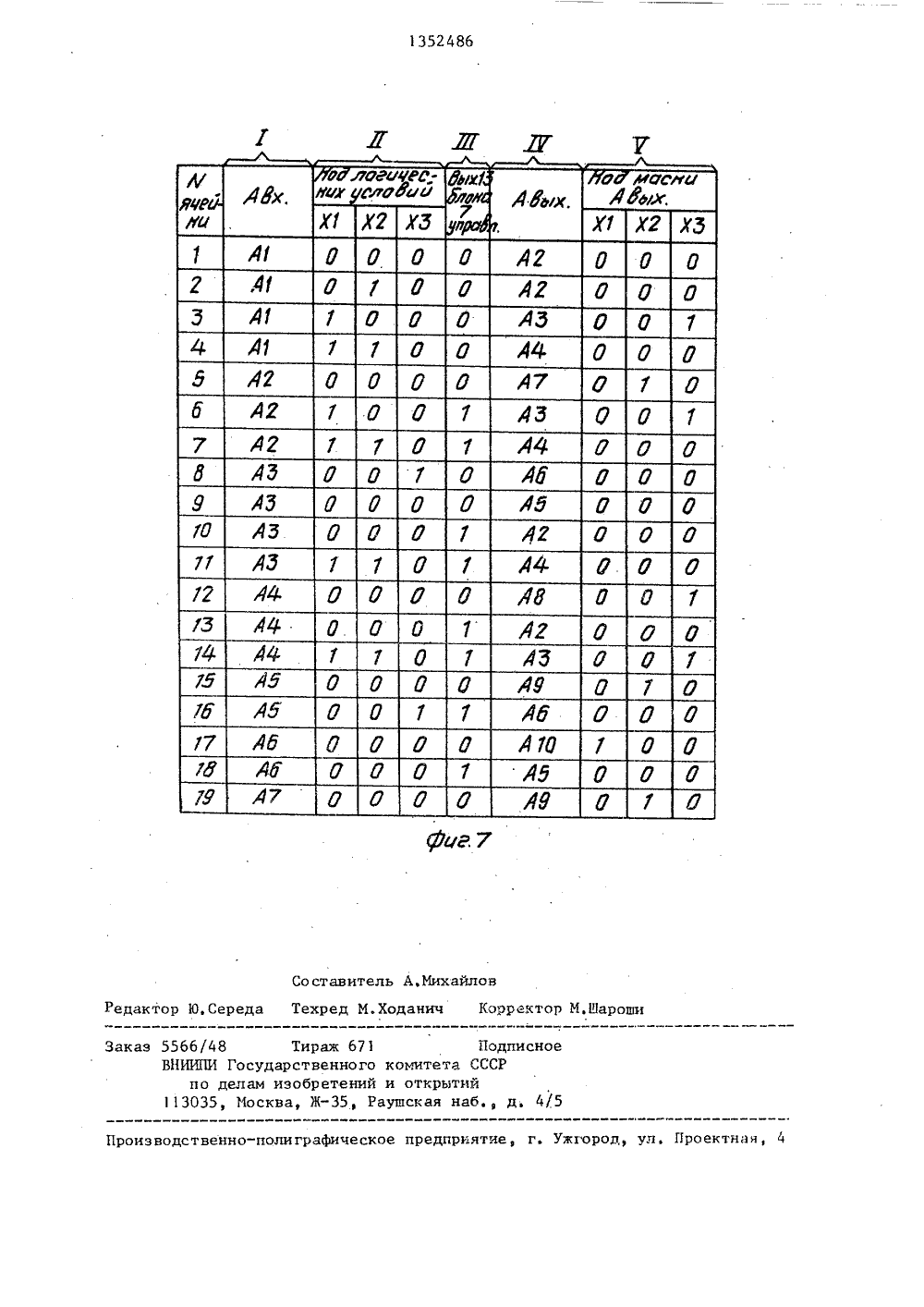

(50 4 О 06 Р 9/22 ОПИСАНИЕ ИЗОБРЕТЕНИЯН А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССРВ 9%061, кл. О 06 Р 9/22, 1981,Авторское свидетельство СССРВ 1185332, кл, С 06 Р 9/22, 1984.(57) Изобретение относится к областивычислительной техники и может бытьиспользовано в цифровых вычислительных системах, а также терминальнойаппаратуре, Цель изобретения - повышение быстродействия устройства. Микропрограммное устройство управления содержит реги стр 1 адре са, блок 2памяти, регистр 3 микрокоманд, регистр 4 условий, блок 5 формированияадреса, блок 6 анализа условий, блок7 управления. Возможны три случаявыполнения микропрограммы, которымсоответствуют три режима работы микропрограммного устройства управления.Если в микропрограмме существуют пары следующих друг за другом микрокоманд, таких,что при выполнениикаждой из этих микрокоманд изменяется значение некоторого признака,. тоиспользование для реализации такойпрограммы предложенного устройствапозволяет сократить время ее выполнения. Укаэанная цель достигаетсяс помощью вышеуказанной совокупностипризнаков. 7 ил.113Изобретение относится к вычислительной технике к может быть использовано в цифровых вычислительных системах, а также в терминальной аппаратуре.Целью изобретения является повышение быстродействияустройства.На фиг.1 изображена функциональная схема микропрограммного устройства управления; на фиг.2 - функциональная схема блока анализа условий;на фиг.З - функциональная схема блока управления; на Фиг,4 - временныедиаграммы работы блока управления;на Фиг.5 - функциональная схема блока Формирования адреса; на фиг,6 -фрагмент граф-схемы микропрограммы,реализуемой предлагаемым устройством;на Фиг.7 - таблица содержимого ассоциативного запоминающего устройства,входящего в блок формирования адреса.Устройство содержит регистр 1адреса, блок 2 памяти микрокоманд,регистр 3 микрокоманд, регистр 4условий, блок 5 формирования адреса,блок 6 анализа условий, блок 7 управления, группу 8 входов условий, синхровход 9, выход 10, первый 11, второй 12 и третий 13 выходы блока 7управленйя, первую 14 и вторую 15группу выходов регистра 1 адреса,группу 16 выходов поля анализируемыхусловий регистра 3 микрокоманд, группу 17 выходов регистра 4 условий ипервый 18-1 и второй 18-2 выходыблока 6 анализаБлок 6 фиг.2) анализа условийсодержит группу элементов ИСКЛ 10 ЧАЮЦЕЕ ИЛИ 19, первую и вторую группыэлементов И 20 и 21 и два элементаИЛИ 22 и 23,Блок 7 управления (фиг.З) содержит первый элемент ИЛИ 24, первый25, второй 26, третий 27, четвертый28 и пятый 29 триггеры, второй элемент ИЛИ 30, первый 31 и второй 32элементы И.Блок 5 формирования адреса(Фиг.5) содержит элемент НЕ 33, первую группу элементов И 34, вторуюгруппу элементов И 35, группу элементов ИЛИ 36 и ассоциативную память(АП) 37. Ассоциативная память состоит из двух частей: ассоциативной иинформационной.Алгоритм работы АП следующий:поиск в ассоциативной части посодержимому поискового входа; 52486 2при обнаружении совпадения со словом, записанным в ассоциативной части, соответствующий индикатор словаустанавливается в состояние "0";чтение слова, записанного в информационной части, индикатор которогоустановлен в состояние "0".Работу микропрограммного устрой 10 ства управления рассмотрим на примере выполнения фрагмента микропрограммы, граф-с: ма которой приведенана фиг.6. Каждую МК микропрогаммыбудем идентифицировать адресом, по15 которому она записана в блоке 2 памяти. Размещение Фрагмента микропрограммы в АП 37 приведено нафиг.7.Путь в первом такте работы уст 20 ройства выполняется в МК А, (в регистре 3 микрокоманды находятся коды операции и маски МК, записанной.в блоке 2 памяти по адресу А ), считывается МК А (в регистре 1 адре 325 са находится код адреса А ), а в) 1регистре 4 условий записан код условия 101, сформированный по значениямлогических условий, поступивших навход 8 устройства в предыдущем такте.30 В этом случае при отсутствии "1" навыходе 13 блока 7 управления на выхбде группы элементов ИЛИ 36 формируется код 001,При этом в АП 37 вырабатываетсясигнал совпадения .с содержанием ассоциативной части 8-й ячейки (фиг.7)и содержимое информационной части8-й ячейки АП 37 поступает на выходблока 5 формирования адреса. Таким40 образом, в первом такте в блоке 5формирования адреса Формируется кодадреса и код маски МК АВозможны три случая выполнениямикропрограммы, которым соответствует три режима работы микропрограммнсго устройства управления.Первый режим соответствует случаю,когда в течение такта работы устройства не происходит изменения значебо ний логических условий, влияющих навыбор пути выполнения микропрограммы из МК выполняемой в данном тактеи МК, считываемой в данном такте изблока 2 памяти.Второй режим соответствует случаю,когда в течение текущего такта изменяются значения логических условий,Фвлияющих на выбор пути выполнениямикропрограммы из МК, считываемой в50 данном такте из блока 2 памяти, азначения ло ги че ских условий, влияющих на выбор пути выполнения микропрограммы из МК, которая выполняетсяв текущем такте (код операционной 5части которой присутствует на выходе10 устройства) остаются неизменными,Третий режим соответствует случаю,когда в текущем такте работы происходит изменение значений логических 10условий, влияющих на выбор пути вы -полнения микропрограммы из МК, которая выполняется в текущем такте.Реализация первого и третьего режимов микропрограммного устройствауправления осуществляется так же,как в устройстве прототипе,Дпя нашего примера условием работы устройства в первом режиме является неизменность значений логических условий Х= 1, Х = О, Х = 1в течение пер во го т ак та. При э томна выходе блока б анализа условийсохраняется код 00 и в следующемтакте на выходах 11 и 12 блока 7управления вырабатывается синхроим-,.пульс. Во втором такте на выход 1 Оустройства поступает операционнаячасть МК Лз, из блока 2 памяти микрокоманд считывается МК Л 6, а на выходе блока 5 Формирования адреса формируется адрес Л,о,Как и в прототипе в первом режимеработы устройства обеспечиваетсяполное совмещение процессов выполнения, считывания и формирования адреса МК, При этом на выполнение двухследующих друг за другом МК (А,А),затрачивается два такта,40При выполнении линейных участковмикропрограммы устройство всегда работает в первом режиме, поскольку вэтом случае логические условия невлияют на траекторию микропрограммы.45В нашем примере устройство переходит в третий режим работы, если втечение первого такта изменилисьзначения Х, или Х, Пусть в первомтакте меняется значение Х, , В этомслучае значения логических условийв конце первого такта будут следующие: Х, =0; Х=О; Х =1. Приэтих значениях логических условийпосле МК А, в микропрограмме следуетМК А, Поэтому в течение второготакта работы устройства в блоке 5Формирования адреса вырабатываетсяадрес А, а в течение третьего такта МК А считывается из блока 2 памяти,Это происходит следующим образом.На выходе блока 6 анализа условийвырабатывается код 10 (фиг,2)Вовтором и третьем тактах работы устройства на синхровход регистра 3 микрокоманд с выхода 12 блока 7 управления не поступают синхроимпульсы, вовтором такте работы синхроимпульсыс выхода 11 блока 7 управления непоступают также на синхровход регистра 1 адреса, кроме того во второмтакте работы устройства на выходе 13блока, 7 управления формируется сигнал логической "1" (фиг4). При этомво втором такте на вход блока 5Формирования адреса поступают: кодадреса А ; код условия 001; сигнал"1" с выхода 13 блока 7 управления.В этом случае на выходе группыэлементов ИЛИ 36 формируется код000, а на выходе блока 5 формирования адреса - коды адреса и маскиМК Л (фиг.7). В третьем такте МКЛ считывается иа блока 2 памяти,в блоке 5 формирования адреса вырабатывается адрес Л, (Фиг.7), а навыходе 1 О устройства будет по-прежнему находиться код операционнойчасти МК А,. В четвертом такте навыход 1 О устройства поступит кодоперационной части МК А, При этомиз блока 2 памяти будет считыватьсяМК А а в блоке 5 Формирования адреса вырабатывается адрес А,Таким образом, в третьем режимеработы на выполнение двух следующихдруг за другом МК 1 А, и А) затрачивается четыре такта (два дополнительных такта ),Рассмотрим работу устройства приреализации второго режима,В нашем примере устройство переходит во второй режим работы, еслив течение первого такта значениялогических условий Х, и Хостаютсянеизмененными (Х= 1, Х= О)а значения Х меняются (Хз = 0).В этом случае после МК А в микропрограмме должна выполняться МКЛ . Поэтому во втором такте работыустройства в блоке 5 формированияадреса должен быть сформирован адресЛ. Это происходит следующим образом.На выходе 18 блока 6 анализа условий вырабатывается код 01 (фиг,2),При этом во втором такте с выхода11 блока 7 управления на синхровход5248 ббформирования, адреса - коды адреса имаски МК А (фиг,7), которые в четвертомтакте по синхросигналу записываются в регистр 1 адреса. При этом втретьем и четвертом тактах иа выходах10 устройства сохраняется код операции МК Лз, В четвертом такте на входблока 5 формирования адреса поступает: код адреса Л , код условия 101,сигнал логического ЯОи с выхода 13блока 7. На выходе блока 5 формирования адреса будет вырабатыватьсяадрес МК А, ( фиг.7 ), Таким обра зом, на выполнение следующих другза другом МК А и Аз потребуется вэтом случае четыре такта. 25 35 50 55 5 13 регистра 1 адреса не поступает синхроимпуш с (фи .4), На вход блока 5 формирования адреса поступают код адреса Л , код условия 100, сигнал логического "0" с выхода 13 блока 7 управления, В этом случае на выходах элементов ИЛИ формируется код 000, . а на выходе блока 5 формирования адреса - коды адреса и маски МК А (фиг7 ) . Синхроимнульс, поступающий в начале второго такта на синхров ход ре ги стр а 3 микро команд, о существляет запись следующей по микропрограмме МК.Таким образом, в регистре 1 адреса во втором такте по-прежнему находится код адреса Л 1, а в регистре 3 микрокоманд появляются коды операции . и маски МК Л 1.Дальнейшая работа микропрограммного устройства зависит от того, произойдет ли во втором такте изменение значения логического условия Хз под действием вырабатываемого в этом такте на выходе 10 устройства кода операции МК АЕсли значения Х не меняются (Х., = 0), то в устройстве сохраняется второй режим работы и в третьемакте работы на синхровход регистра 1 адреса поступает гинхроимпульс, в то время как на синхровход региста 3 микрокоманд с выхода 12 блока 7 управления синхроимпульс не поступает, При этом в третьем такте работы на выходе 10 устройства вырабатывается код операциончой части МК А, из блока 2 памяти будет считываться МК Л, а в блоке 5 формирования адре са выр аб атывает ся адрес МК Ли ж.алогично тому как это происходит в прототипе во втором режиме работы ,стройства на выполнение двух следующих друг за другом МК ЛАз затрачивается три тахта.Если под действием кода операции МК Лз значение признака Х меняется (Х= 1), устройство г;ереходит в третий режим работы, Однакс в этом случае на выходе 1 3 блока 7 управления в третьем такте вырабатывается сигнал логического "0" (фиг.4). При этом в третьем такте на вход блока 5 формирования адреса поступает: код адреса Л , код условия 101 сигнал логического "О с выхода 13 блока 7, На,"выходах элементов ИШ 1 36 формируется код 001, а на выходе блока 5 формула изобретения20 Микропрограммное устройство управления, содержащее блок памяти микро- команд, регистр адреса, регистр микро- команд, блок анализа условий, регистр условий, бчок формирования адреса, блок управления, который содержит первый, второй и третий триггеры, первый элемент ИЛИ, первый и второй элементы И, причем входы условий устройства соединены с информационными входами регистра условий и с первой группой информационных входов блока анализа условий, выходы регистра условий соединены с второй группой инфррмационных входов блока анализа условий и с первой группой информационных входов блока формирования адреса, выход которого соединен с информационным входом регистра адреса, первая группа. выходов которого соединена с второй группой информационных входов блока формирования адреса и с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля микро- операций которого соединен с выходом микроопераций устройства, вторая группа выходов регистра адреса,соединена с первыми группами входов логических условий, блоков формирования адреса и анализа условий, выход полл кода условий регистра микро- команд соединен с вторыми группами входов логических условий блоков формирования адреса и анализа условий, первый и второй выходы группы блока анализа условий, соединены соответственн 1 с первым и вторым входамизадания режима блока управления,вход синхронизации устройства соединен с входом синхронизации регистраусловий и с входом синхронизацииблока управления, первый, второйи третий выходы которого соединенысоответственно с входами синхронизации регистра адреса, регистра мккрокоманд и с входом синхронизации блока формирования адреса, первый и вто Орой входы задания режима блока управления соединены соответственно спервым и вторым входами первого элемента ИЛИ блока управления, выходкоторого соединен с входом установки 15в "1" первого триггера, инверсныйвыход которого соединен с первымвходом первого элемента И, выход которого соединен с первым выходомблока управления, вход синхронизации 20которого соединен с входами синхронизации первого и второго триггеров,с вторым входом первого элемента И ис первым входом второго элемента И,инверсный выход второго триггерасоединен с вторым входом второго элемента И, выход которого соединен свторым выходом блока управления,второй вход задания режима которогосоединен с входом установки в "1" 30 третьего триггера, выход которогосоединен с третьим выходом блокауправления, информационные входыпервого и третьего триггеров блокауправления соединены с шиной нулевого потенциала, о т л и ч а ю щ е е -с я тем, что, с целью повышениябыстродействия устройства, блок управления содержит четвертый и пятыйтриггеры, второй элемент ИЛИ, причем первый вход задания режима блока управления соединен с входом установки в1пятого триггера, второйвход задания режима блока управлениясоединен с входами установки в "1"второго и четвертого триггеров, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с информационным вхо;дом второго триггера, вход синхронизации блока управления соединен свходом синхронизации пятого триггера,выход которого соединен с вторымвходом второго элемента ИЛИ и с входом синхронизации третьего триггера,выход первого элемента И соединен свходами установки в "0 третьего ичетвертого триггеров, информационныйвход пятого триггера соединен с шинойнулевого потенциала.135248 б Со ставитель А,МихайловРедактор Ю,Середа Текред М.Ходанич Корректор М.Ларош Рауш кая н графическое предприятие, г, Ужгород, ул, Проектная роизводственн каз 55 бб/48 Тираж 6ВНИИПИ Государственнои о дел ам из о бр етени113035, Москва, Ж,Подписнокомитета СССРи открытийс аб., д. 4/

СмотретьЗаявка

4083597, 02.07.1986

ПРЕДПРИЯТИЕ ПЯ А-7438

ШАПИРО ИЛЬЯ БОРИСОВИЧ, ШУМИЛОВ ЛЕВ АЛЕКСЕЕВИЧ, КРЯЖЕВ АЛЕКСАНДР ЮРЬЕВИЧ, БЫЧКОВ БОРИС ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.11.1987

Код ссылки

<a href="https://patents.su/8-1352486-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммный автомат

Следующий патент: Многоканальное устройство приоритета

Случайный патент: Способ компенсации волнового фронта для контроля формы поверхности астрономических зеркал