Микропрограммное вычислительное устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

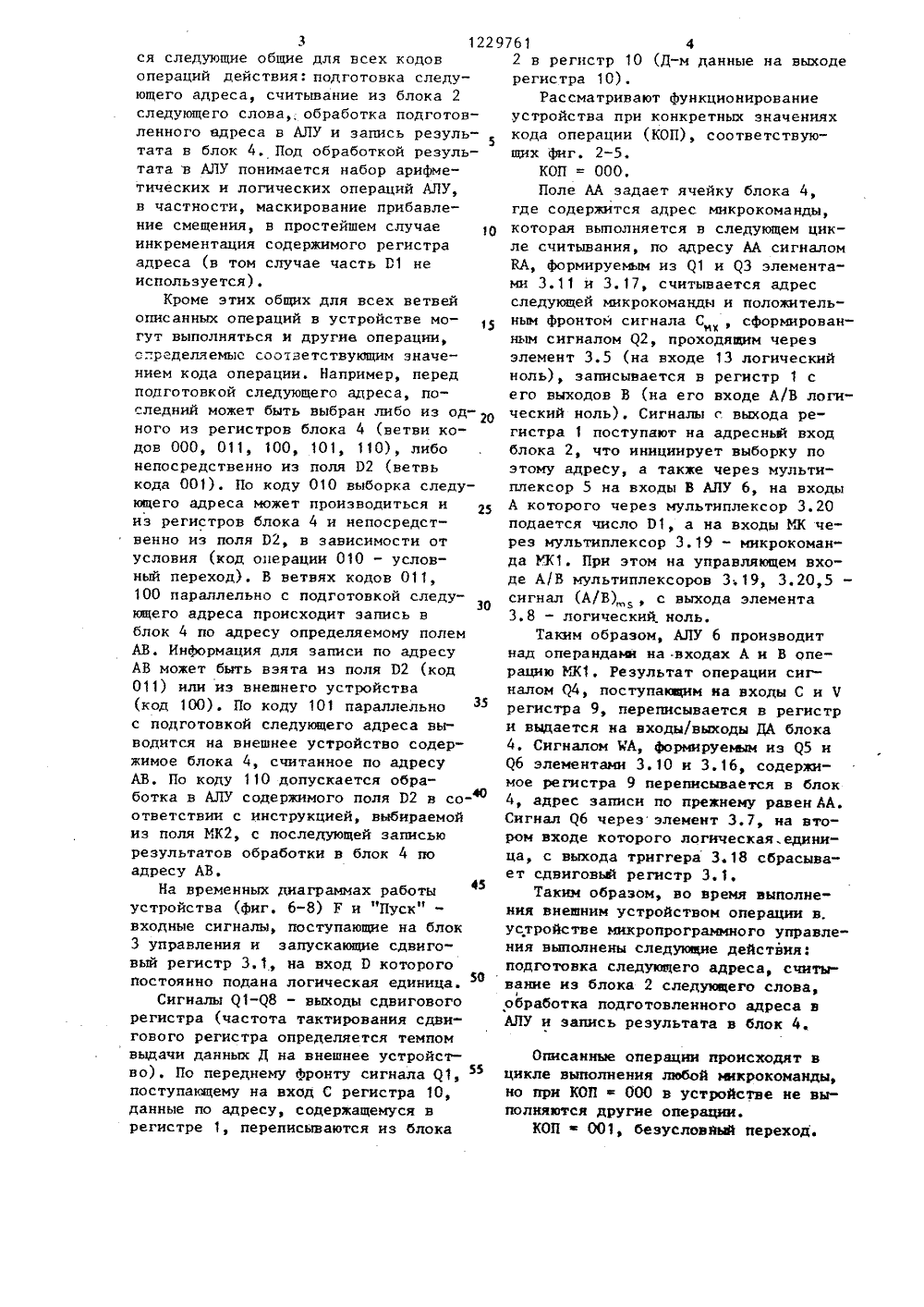

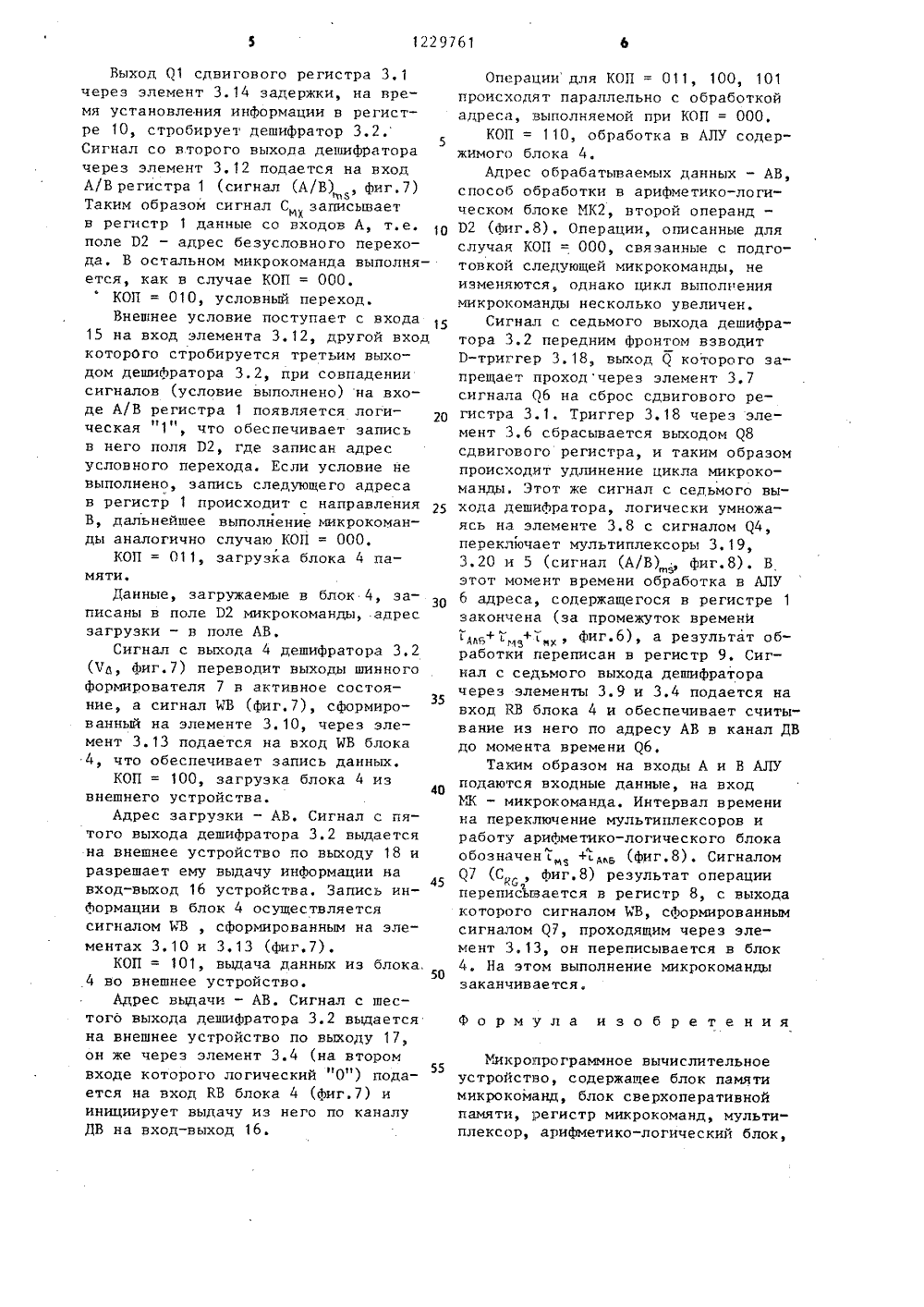

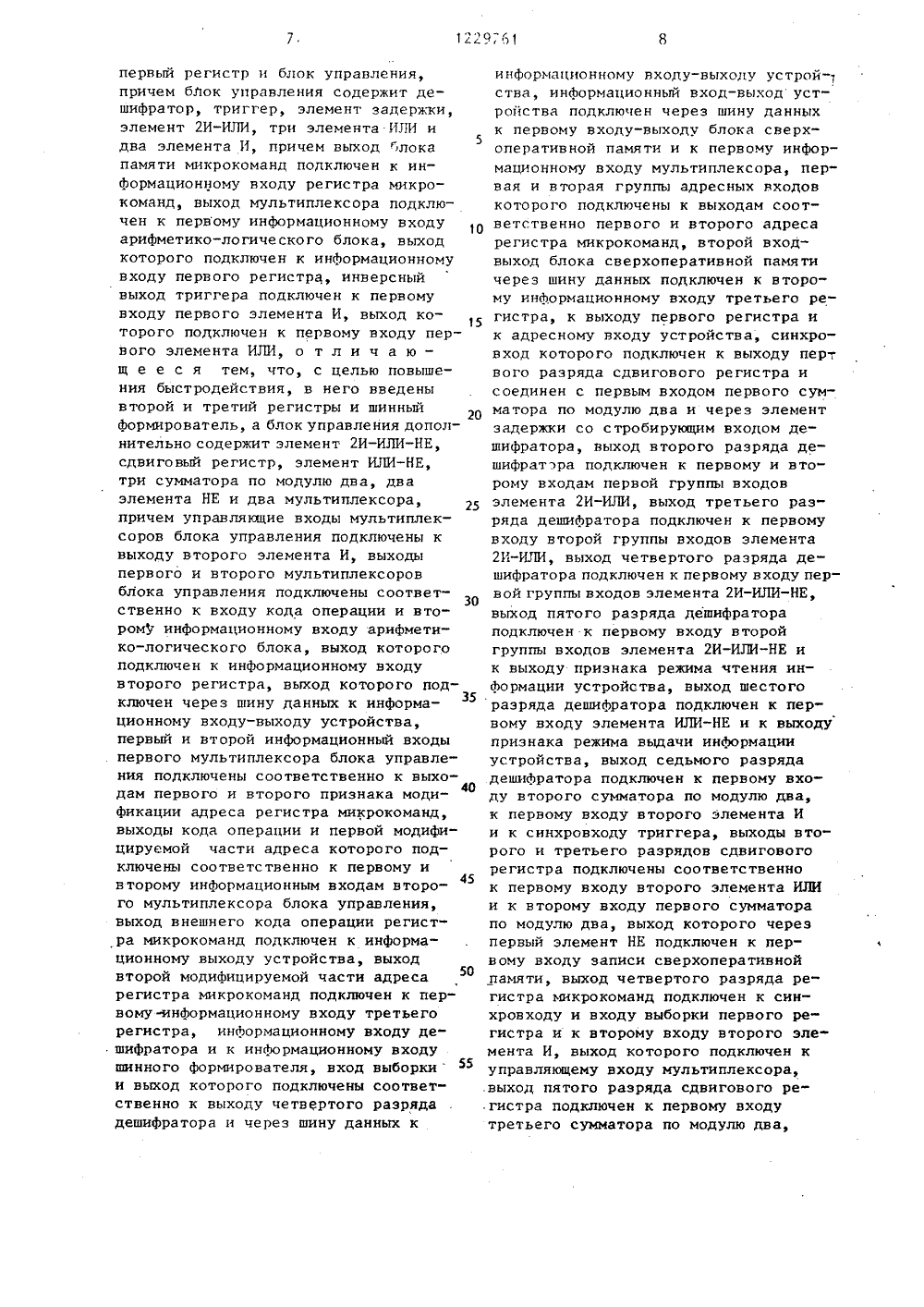

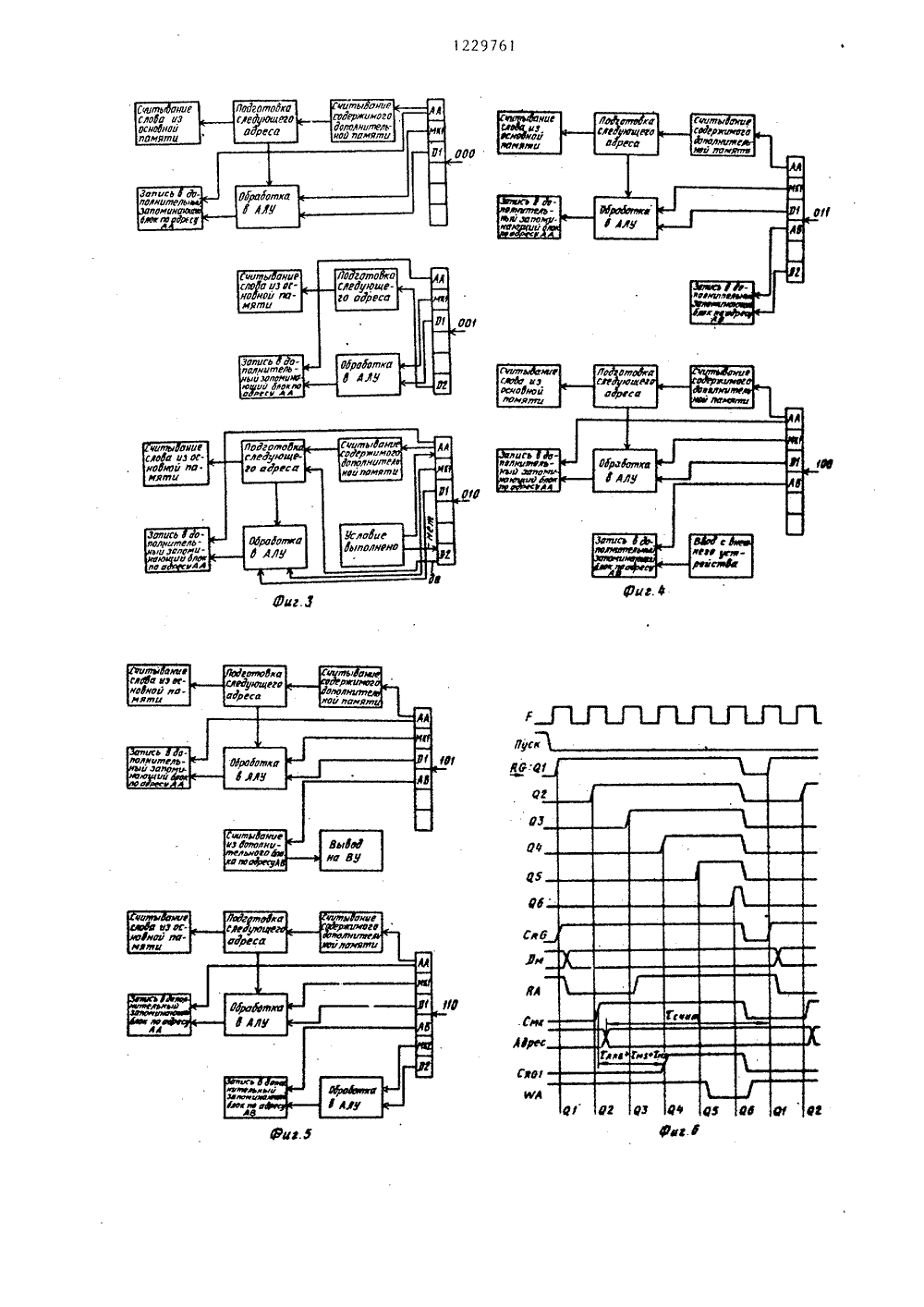

(59 4 С 06 Р 9/22 15/00 сОПИСАНИЕ ИЗОБРЕТЕНИЯ"К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПЪЮ(71) Московский институт электроннойтехники(56) Авторское свидетельство СССРВ 968815, кл. С 06 Р 9/22, 1978.Авторское свидетельство СССРВ 1008741, кл. С 06 Г 9/22, 1981.(57) Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления ЭВМ. Целью изобретения является повышение быстродействия. Устройство содержит три регистра, блок памяти микрокоманд, блок управления, блок сверхоперативной памяти, мультиплексор, арифметика-логическое устройство, регистр микрокоманд. Сущность изобретения заключается в повышении быстродействия за счет параллельного вычисления начальных адресов модулей подпрограмм и загрузки их в сверхоперативную память. 8 ил.1 12Изобретение относится к вычислительной технике и может быть использовано при.разработке электронныхвычислительных машин,Цель изобретения - повышение быстродействия.На Фиг.1 приведена. Функциональнаясхема устройства; на Фиг. 2-5 - блоксхема алгоритма работы устройства;на фиг. 6 - 8 - временные диаграммы работы устройства,Устройство содержит регистр 1,блок 2 памяти микрокоманд, блок 3управления, блок 4 сверхоперативнойпамяти, мультиплексор 5, арифметикологическое устройство (АЛУ) 6, шинный формирователь 7, регистры 8 и 9регистр 10 микрокомйнд, входы тактовых импульсов 11, пуска 12, признаказагрузки 13, адресный 14, логическихусловий 15, информационный вход-выход 16 устройства, выходы 17 признака режима выдачи информации, признакарежима чтения информации 18, информационный выход 19 устройства. Блок 3управления содержит сдвиговый регистр 3.1, дешифратор 3.2 элементИЛИ 3.3, элемент ИЛИ-НЕ 3.4, элементы ИЛИ 3.5 и 3.6, элементы И 3.7 и3,8, сумматоры 3,9-3,11 по модулюдва, элементы 2 И-ИЛИ 3.12, элемент2 И-ИЛИ-НЕ 3,13, элемент 3,14 задержки, выход 3.15 элемента задержки,элементы НЕ 3,16 и 3.17, триггер 3,18мультиплексоры 3.19 и 3,20.Блок 4 устройства может быть реализован, например, на основе микросхемы КР 1802 ИР 1, регистр 1 на основе микросхемы К 533 КП 13, блок 6 наоснове микросхемы К 155 ИПЗ.Изобретение позволяет повыситьэффективность выполнения программ рпредставленных в виде набора модулей, в которой модули могут выполняться последовательно или с прерыванием какого-либо модуля и передачей управления другому модулю. Причем время на переключение с модуляна модуль, когда начальные адресаподготовлены, не тратится. В своюочередь начальные адреса модулей, накоторые будет производиться переключение, загружаются предварительно вблок 4 сверхоперативной памяти параллельно с выполнением команд какого-либо программного модуля без за. трат на это времени машинного цикла.Устройство работае следующим образомм,29761 1В начальном состоянии на входе 12"Пуск" высокий уровень. Подготовкаустройства к работе заключается взаписи начального адреса в регистр 1.5Начальный адрес поступает из внешне-,го устройства по магистрали на входыВ регистра 1 и сопровождается импульсом положительной полярности по входу 13 "Начальная загрузка" через элемент 3.5 на вход С регистра 1. Приэтом на входе А/В регистра 1 логический ноль, выходы блока 4 и регистра 8 находятся в отключенном состоянии. После начальной загрузки регистра 1 на вход 12 можно подавать логический ноль и на вход 11 тактовые имлульсы, что разрешает работу устройстваа. Во время работы устройства выходы внешнего устройства, по которымпередается начальный адрес, должныбыть в отключенном состоянии.Слово, считанное из блока 2 памяти микрокоманд и записанное в регистр 10, разбивается на два поля Ви В : В - поле данных, выдаваемыхна внешнее устройство обработки инФормации, например это могут бытьмикрокоманда, команда или число, вы"даваемое на центральный процессор, 30т,е, на этот выход поступает внешнийкод операции; В - поле данных, выдаваемое для задания адреса, котороев свою очередь состоит иэ 7 частей:КОП - код операции; АА - первый адрес блока 4; МК 1 - первая микрокоманда АЛУ (первый признак модификации адреса в АЛУ); В 1 - данные дляпервой микрокоманды АЛУ (первая модифицируемая часть адреса); АВ - второй адрес блока 4; КК 2 - вторая микрокоманда АЛУ (второй признак модификации адреса); В 2 - данные для второй микрокоманды АПУ (вторая модифицируемая часть адреса).Каждому коду операции соответствует свой Формат, который вместе с кодом операции определяет действия различных блоков устройства, последовательность взаимодействия между ними,входную информацию для работы блоков.После дешифрации части слова В 50считанного из блока 2, устройство работает по алгоритму (фиг. 2-5) в соответствии с кодом операции. Причемэтот алгоритм выполняется параллель-но с обработкой информации, записанной в поле В слова, считанного изблока 2, Как видно из блок-схемы алгоритма в любой из ветвей выполняют2 в регистр 10 (Д-м данные на выходерегистра 10).Рассматривают функционированиеустройства при конкретных значенияхкода операции (КОП), соответствующих Фиг. 2-5.КОП = ООО,Поле АА задает ячейку блока 4,где содержится адрес микрокоманды,которая выполняется в следующем цикле считывания, по адресу АА сигналомВА, формируемым из Я 1 и ЯЗ элементами 3.11 и 3. 17, считывается адресследующеи микрокоманды и положительным фронтом сигнала С, сформированным сигналом Я 2, проходящим черезэлемент 3.5 (на входе 13 логическийноль), записывается в регистр 1 сего выходов В (на его входе А/В логический ноль), Сигналы с выхода регистра 1 поступают на адресный входблока 2, что инициирует выборку поэтому адресу, а также через мультиплексор 5 на входы В АЛУ 6, на входыА которого через мультиплексор 3.20подается число Р 1, а на входы ЬЖ через мультиплексор 3. 19 - микрокоманда И(1. Прн этом на управляющем входе А/В мультиплексоров 3; 19, 3,20,5сигнал (А/В) , с выхода элемента3,8 - логический. ноль.Таким образом, АЛУ 6 производитнад операндаьы на .входах А и В операцию МК 1. Результат операции сигналом (4, поступающим на входы С и 7регистра 9, переписывается в регистри выдается на входы/выходы ДА блока4, Сигналом ЫА, формируеьаям из Я 5 и(6 элементами 3.10 и 3.16, содержимое регистра 9 переписывается в блок4, адрес записи по прежнему равен АА.Сигнал Ц 6 через элемент 3.7, на втором входе которого логическая,единица, с выхода триггера 3.18 сбрасывает сдвиговый регистр 3.1.Таким образом, во время выполнения внешним устройством операции в.устройстве микропрограммного управления выполнены следующие действия:подготовка следующего адреса, считывание из блока 2 следующего слова,обработка подготовленного адреса вАЛУ и запись результата в блок 4,Описанные операции происходят в цикле выполнения любой микрокоманды, но при КОП000 в устройстве не выполняются другие операции.КОП - 001, безусловйый переход. 3 1229761 4ся следующие общие для всех кодовопераций действия: подготовка следующего адреса, считывание из блока 2следующего слова,.обработка подготовленного вдреса в АЛУ и запись резуль 5тата в блок 4Под обработкой результата в АЛУ понимается набор арифметических и логических операций АЛУ,в частности, маскирование прибавление смещения, в простейшем случаеинкрементация содержимого регистраадреса (в том случае часть В 1 неиспользуется).Кроме этих общих для всех ветвейописанных операций в устройстве могут выполняться и другие операции,о-ределяемыс соответствующим значением кода операции. Например, передподготовкой следующего адреса, последний может быть выбран либо из одного из регистров блока 4 (ветви кодов 000, 011, 100, 101, 110), либонепосредственно иэ поля 02 (ветвькода 001). По коду 010 выборка следующего адреса может производиться ииз регистров блока 4 и непосредственно из поля И, в зависимости отусловия (код операции 010 - условный переход). В ветвях кодов 011,100 параллельно с подготовкой следующего адреса происходит запись вблок 4 по адресу определяемому полемАВ, Информация для записи по адресуАВ может быть взята из поля 02 (код011) или из внешнего устройства(код 100). По коду 101 параллельнос подготовкой следующего адреса выводится на внешнее устройство содержимое блока 4, считанное по адресуАВ, По коду 110 допускается обработка в АЛУ содержимого поля Р 2 в со-ответствии с инструкцией, выбираемойиз поля МК 2, с последующей записьюрезультатов обработки в блок 4 поадресу АВ.На временных диаграммах работыустройства (фиг. 6-8) Р и "Пуск"- входные сигналы, поступающие на блок3 управления и запускающие сдвиговый регистр 3. 1, на вход В которогопостоянно подана логическая единица.Сигналы Я 1-Я 8 - выходы сдвиговогорегистра (частота тактирования сдвигового регистра определяется темномвыдачи данных Д на внешнее устройство). По переднему фронту сигнала Ц 1, 55поступающему на вход С регистра 10,данные по адресу, содержащемуся врегистре 1, переписываются из блокаВыход Ц 1 сдвигового регистра 3.1через элемент 3.14 задержки, на время установления информации в регистре 10, стробирует дешифратор 3.2.Сигнал со второго выхода дешифраторачерез элемент 3.12 подается на входА/В регистра 1 (сигнал (А/В), фиг,7)Таким образом сигнал С записываетв регистр 1 данные со входов А, т.е.поле 02 - адрес безусловного перехода. В остальном микрокоманда выполняется, как в случае КОП = 000.КОП = 010, условный переход.Внешнее условие поступает с входа15 на вход элемента 3,12, другой входкоторОго стробируется третьим выходом дешифратора 3.2, при совпадениисигналов (условие выполнено) на входе А/В регистра 1 появляется логическая "1", что обеспечивает записьв него поля Р 2, где записан адресусловного перехода. Если условие невыполнено, запись следующего адресав регистр 1 происходит с направленияВ, дальнейшее выполнение микрокоманды аналогично случаю КОП = 000.КОП = 011, загрузка. блока 4 памяти.Данные, загружаемые в блок 4, записаны в поле Р 2 микрокоманды, адресзагрузки - в поле АВ,Сигнал с выхода 4 дешифратора 3,2(7 д, фиг.7) переводит выходы шинногоформирователя 7 в активное состояние, а сигнал УВ (фиг,7), сформированный на элементе 3. 10, через элемент 3. 13 подается на вход УВ блока4, что обеспечивает запись данных.КОП = 100, загрузка. блока 4 извнешнего устройства.Адрес загрузки - АВ. Сигнал с пятого выхода дешифратора 3,2 выдаетсяна внешнее устройство по выходу 18 иразрешает ему выдачу информации навход-выход 16 устройства. Запись информации в блок 4 осуществляетсясигналом УВ , сформированным на элементах 3.10 и 3.13 (фиг.7).КОП = 101, выдача данных из блока,4 во внешнее устройство.Адрес выдачи - АВ, Сигнал с шестого выхода дешифратора 3.2 выдаетсяна внешнее устройство по выходу 17,он же через элемент 3.4 (на второмвходе которого логический н 0") подается на вход КВ блока 4 (фиг.7) иинициирует выдачу из него по каналуДВ на вход-выход 16. Операции для КОП = 011, 100, 101происходят параллельно с обработкойадреса, выполняемой при КОП = 000,КОП = 110, обработка в АЛУ содержимого блока 4.Адрес обрабатываемых данных - АВ,способ обработки в арифметико-логическом блоке МК 2, второй операнд -10 2 (фиг.8), Операции, описанные дляслучая КОП = 000, связанные с подготовкой следующей микрокоманды, неизменяются, однако цикл выполнениямикрокоманды несколько увеличен.Сигнал с седьмого выхода дешифратора 3.2 передним фронтом взводитВ-триггер 3.18, выход Я которого запрещает проходчерез элемент 3,7сигнала 6 на сброс сдвигового регистра 3,1. Триггер 3,18 через элемент 3.6 сбрасывается выходом Ц 8сдвигового регистра, и таким образомпроисходит удлинение цикла микрокоманды. Этот же сигнал с седьмого вы 25 хода дешифратора, логически умножаясь на элементе 3.8 с сигналом Я 4,переключает мультиплексоры 3.19,3,20 и 5 (сигнал (А/В) , фиг.8). Вэтот момент времени обработка в АЛУб адреса, содержащегося в регистре 1закончена (за промежуток временио+(, +фиг6), а результат обработкй переписан в регистр 9, Сигнал с седьмого выхода дешифраторачерез элементы 3,9 и 3.4 подается навход ВВ блока 4 и обеспечивает считывание из него по адресу АВ в канал ДВдо момента времени Яб,Таким образом на входы А и В АЛУ40 подаются входные данные, на входМК - микрокоманда. Интервал временина переключение мультиплексоров иработу арифметико-логического блокаобозначен , +. (фиг,8). СигналомЦ 7 (С, , фиг.8) результат операциипереписывается в регистр 8, с выходакоторого сигналом З, сформированнымсигналом Я 7, проходящим через элемент 3. 13, он переписывается в блок5 О4, На этом выполнение микрокомандызаканчивается.Формула изобретенияМикропрограммное вычислительноеустройство, содержащее блок памяти микрокоманд, блок сверхоперативной памяти, 1 регистр микрокоманд, мультиплексор, арифметико-логический блок, 1229 61первый регистр и блок управления, причем блок управления содержит дешифратор, триггер, элемент задержки, элемент 2 И-ИЛИ, три элемента ИЛИ и5 два элемента И, причем выход блока памяти микрокоманд подключен к инАормационному входу регистра микро- команд, выход мультиплексора подключен к первому информационному входу арифметико-логического блока, выход которого подключен к инАормационному входу первого регистра, инверсный выход триггера подключен к первому входу первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, о т л и ч а ю - щ е е с я тем, что, с целью повышения быстродействия, в него введены второй и третий регистры и шинный формирователь, а блок управления дополнительно содержит элемент 2 И - ИЛИ-НЕ, сдвиговый регистр, элемент ИЛИ-НЕ, три сумматора по модулю два, два элемента НЕ и два мультиплексора, причем управляющие входы мультиплексоров блока управления подключены к выходу второго элемента И, выходы первого и второго мультиплексоров блока управления подключены соответственно к входу кода операции и второму информационному входу арифметико-логического блока, выход которого подключен к информационному входу второго регистра, выход которого подключен через шину данных к информа 35 ционному входу-выходу устройства, первый и второй информационный входы . первого мультиплексора блока управления подключены соответственно к выхо 40 дам первого и второго признака модификации адреса регистра микрокоманд, выходы кода операции и первой модифицируемой части адреса которого подключены соответственно к первому и45 второму информационным входам второго мультиплексора блока управления, выход внешнего кода операции регистра микрокоманд подключен к информационному выходу устройства, выход второй модиАицируемой части адреса регистра микрокоманд подключен к первому-инАормационному входу третьего регистра, инАормационному входу дешифратора и к информационному входу шинного формирователя, вход выборкии выход которого подключены соответственно к выходу четвертого разряда дешифратора и через шину данных к информационному входу-выходу устрой ства, инйормационный вход-выход устройства подключен через шину данныхк первому входу-выходу блока сверхоперативной памяти и к первому информационному входу мультиплексора, первая и вторая группы адресных входовкоторого подключены к выходам соответственно первого и второго адресарегистра микрокоманд, второй входвыход блока сверхоперативной памятичерез шину данных подключен к второму инАормационному входу третьего регистра, к выходу первого регистра ик адресному входу устройства, синхровход которого подключен к выходу пертвого разряда сдвигового регистра исоединен с первым входом первого сумматора по модулю два и через элементзадержки со стробирующим входом дешифратора, выход второго разряда дешифратэра подключен к первому и второму входам первой группы входовэлемента 2 И-ИЛИ, выход третьего разряда дешиАратора подключен к первомувходу второй группы входов элемента2 И-ИЛИ, выход четвертого разряда дешифратора подключен к первому входу первой группы входов элемента 2 И-ИПИ-НЕ,выход пятого разряда дешифратораподключен к первому входу второйгруппы входов элемента 2 И-ИЛИ-НЕ ик выходу признака режима чтения инАормации устройства, выход шестогоразряда дешиАратора подключен к первому входу элемента ИЛИ-НЕ и к выходупризнака режима выдачи информацииустройства, выход седьмого разрядадешиАратора подключен к первому входу второго сумматора по модулю два,к первому входу второго элемента Ии к синхровходу триггера, выходы второго и третьего разрядов сдвиговогорегистра подключены соответственнок первому входу второго элемента ИЛИи к второму входу первого сумматорапо модулю два, выход которого черезпервый элемент НЕ подключен к первому входу записи сверхоперативнойпамяти, выход четвертого разряда регистра микрокоманд подключен к синхровходу и входу выборки первого регистра и к второму входу второго элемента И, выход которого подключен куправляющему входу мультиплексора,выход пятого разряда сдвигового регистра подключен к первому входутретьего сумматора по модулю два, 1 2297 б 1второй вход которого подключен к выходу шестого разряда сдвигового регистра и соединен с вторым входом первого элемента И и вторым входом второго сумматора по модулю два, выход которого подключен к второму входу элемента ИЛИ-НЕ, выход которого подключен к второму входу чтения блока сверхоперативной памяти первый и второй входы записи которого подключены соответственно к выходу второго элемента НЕ и к выходу элемента 2 И-ИЛИ-НЕ, выход седьмого разряда сдвигового регистра подключен к первому и второму входам третьей группы входов элемента 2 И-ИЛИ-НЕ и к синхровходу и входу выборки второго регистра, восьмой выход сдвигового регистра подключен к первому входу третьего элемента ИЛИ, выход которого подключен к входу установки в 0 триггера, информационный вход триггера подключен к входу логической единицы устройства и соединен с информационным входом сдвигового регистра, синхровход и вход установкив О которого подключе ны соо тв етств е н но к входу тактовых импульсов устрой ств а и к выходу первого элементаИПИ, вход пуска устройства подключенк вторым входам первого и третьегоэлементов ИЛИ , второй вход второгоэлемента ИЛИ подключен к входу призн ак а загрузки устройства , выход в торо го элеме та ИЛИ подключен к синхровходу третьего регистра, вхоД управле ния выборкой информационных входовкоторого подключен к выходу элемента2 И-ИЛИ , второй вход второй группы которо го подключен к входу логиче с ки:.условий устройства , выход третье госумматора по модулю два подключен к 20 входу второго элемента НЕ и к вторымвходам первой и второй группы входовэлемента 2 И-ИЛИ-НЕ , выход тре ть е горегистра подключен к второму информационному входумультиплексора ик ад Б ресному входу блока памяти микрокоманд.зр. л вУ Слвг Составитель М.Сидиедактор М.Бланар Техред Г.Гербер Корректор Е.Ропп Заказ 2451/В роизводственно-полиграфическое предприятие, г Ужгород, уп, Проектная,49 ТиражНИИПИ Государстпо делам изоб5, Москва, Ж71 Подписиного комитета СССРений и открытийРаушская наб д. 4/5

СмотретьЗаявка

3775989, 03.08.1984

МОСКОВСКИЙ ИНСТИТУТ ЭЛЕКТРОННОЙ ТЕХНИКИ

ВЕРСТАКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, ИГНАТОВА ИРИНА ГУРГЕНОВНА, ПРЕСНУХИН ДМИТРИЙ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 9/22

Метки: вычислительное, микропрограммное

Опубликовано: 07.05.1986

Код ссылки

<a href="https://patents.su/8-1229761-mikroprogrammnoe-vychislitelnoe-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное вычислительное устройство</a>

Предыдущий патент: Датчик случайных чисел

Следующий патент: Устройство для контроля последовательности сигналов

Случайный патент: Станок для вертикальной статической балансировки в динамическом режиме