Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1007106

Авторы: Кондратьев, Тимонькин, Ткаченко, Харченко

Текст

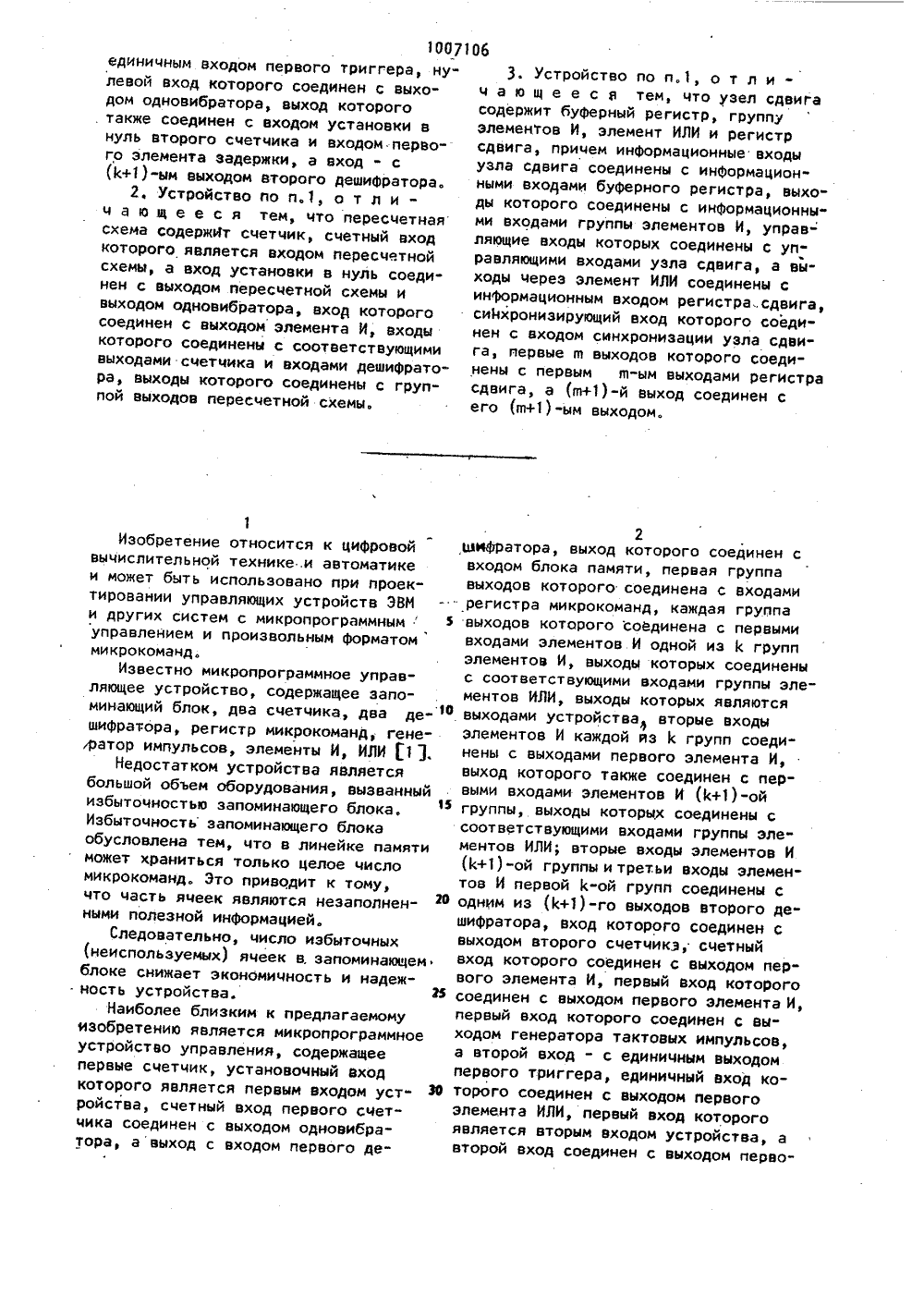

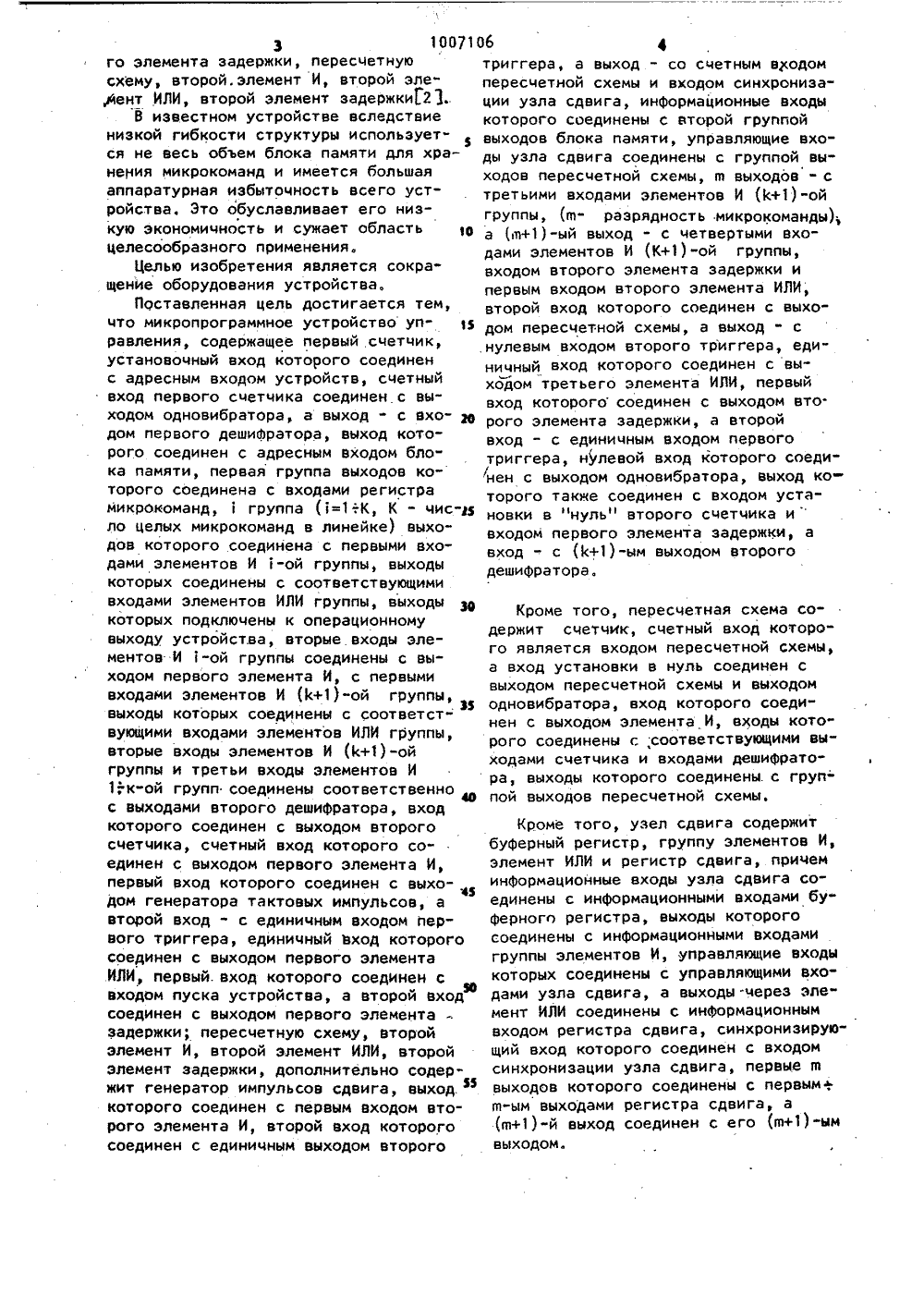

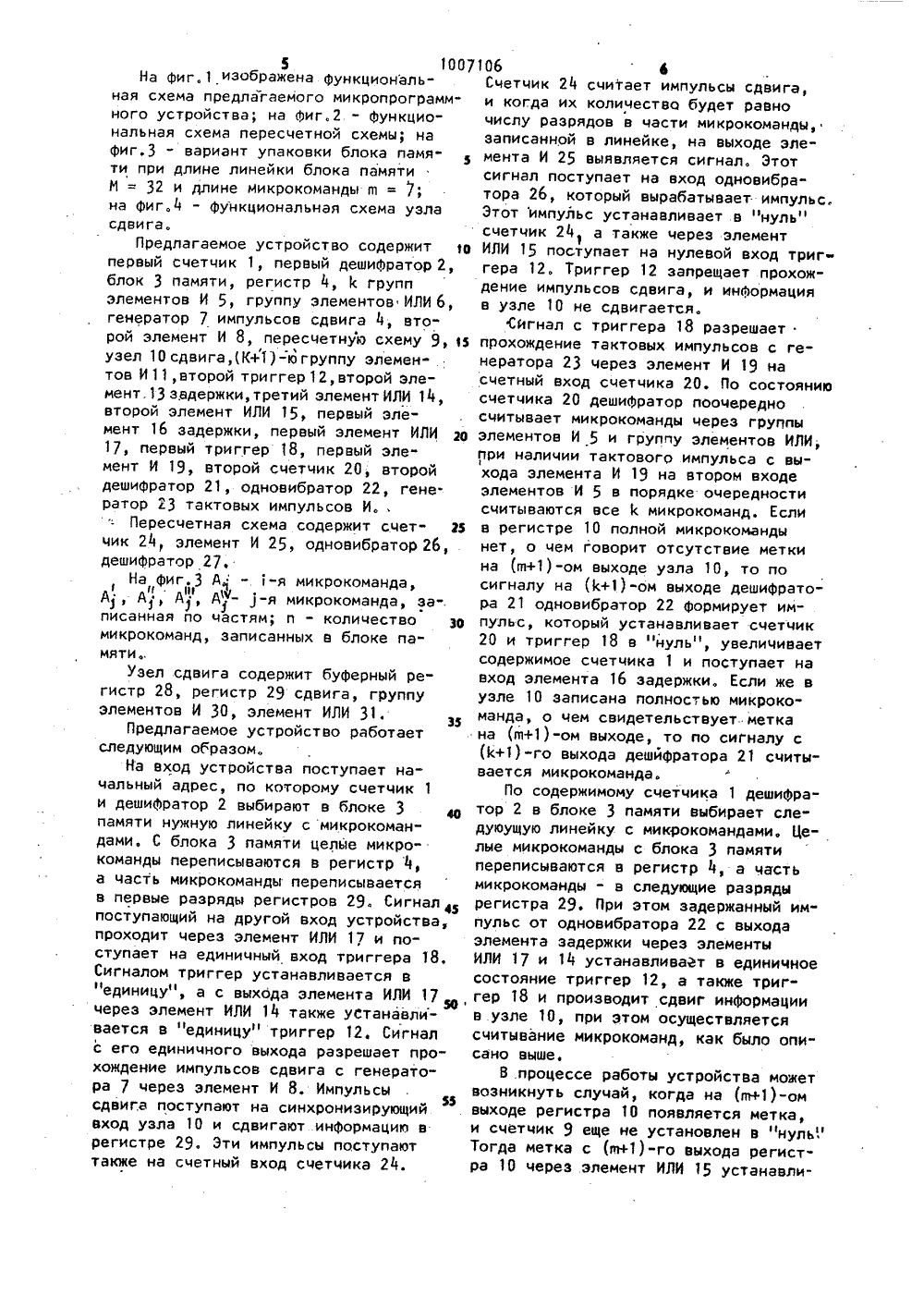

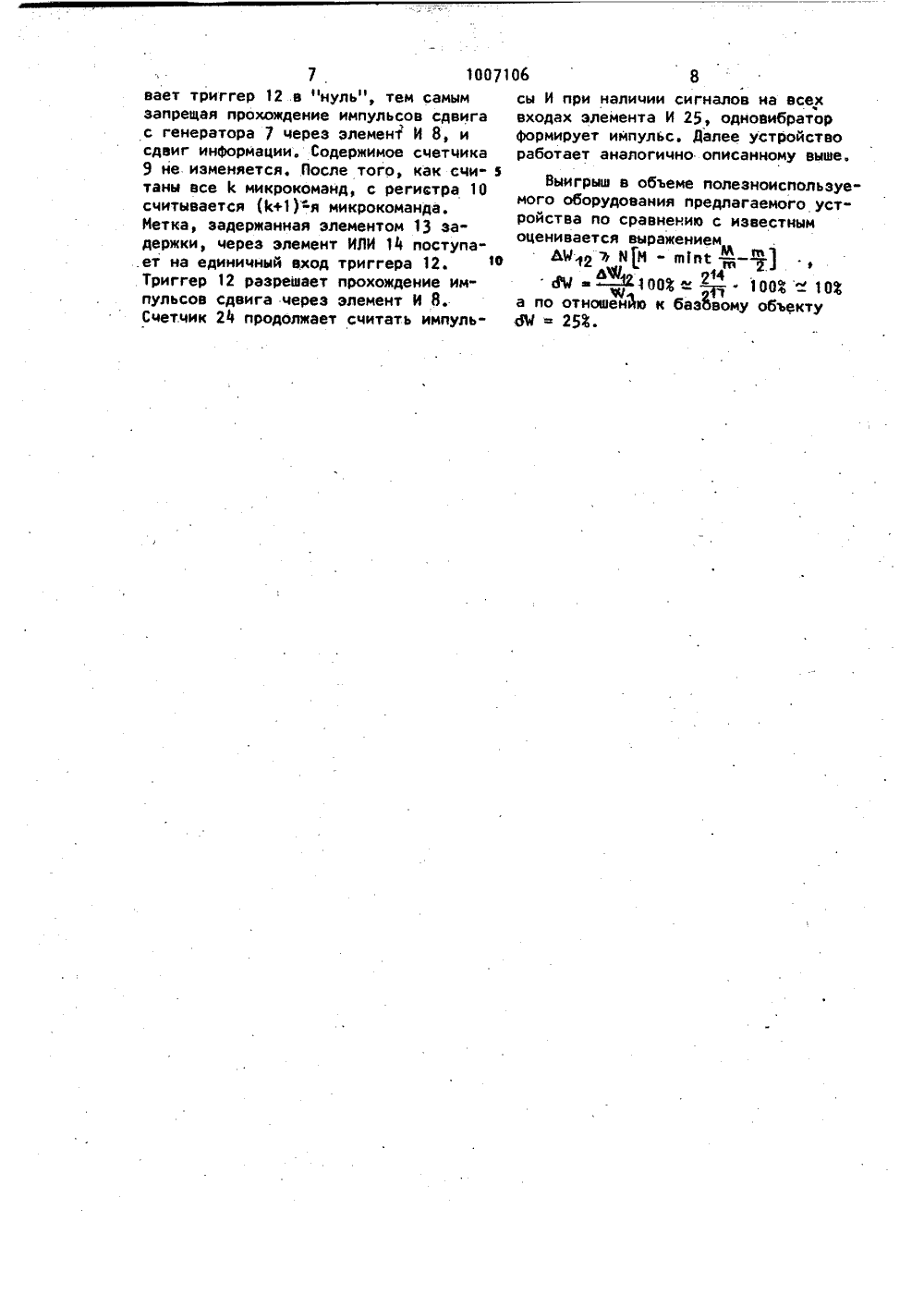

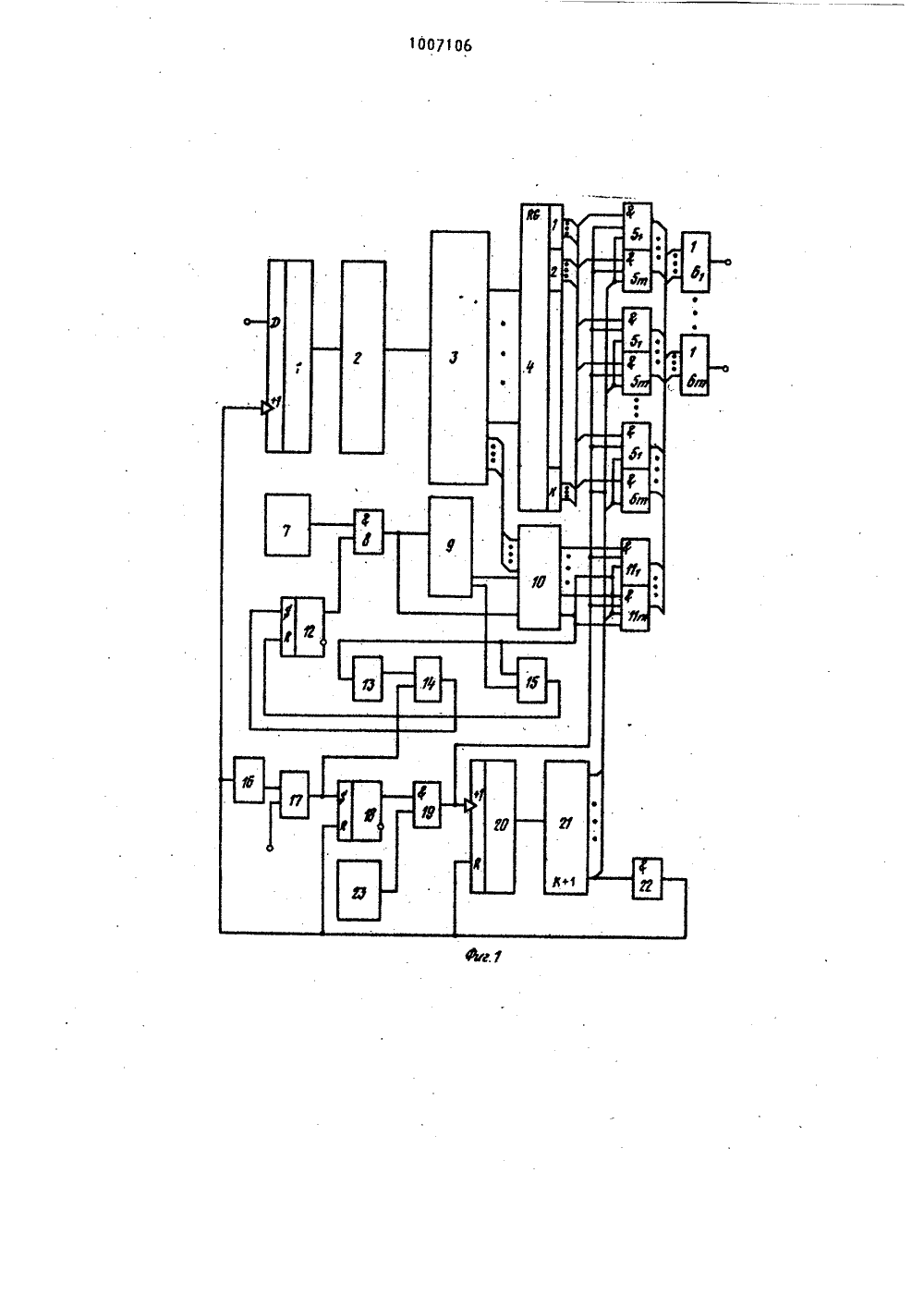

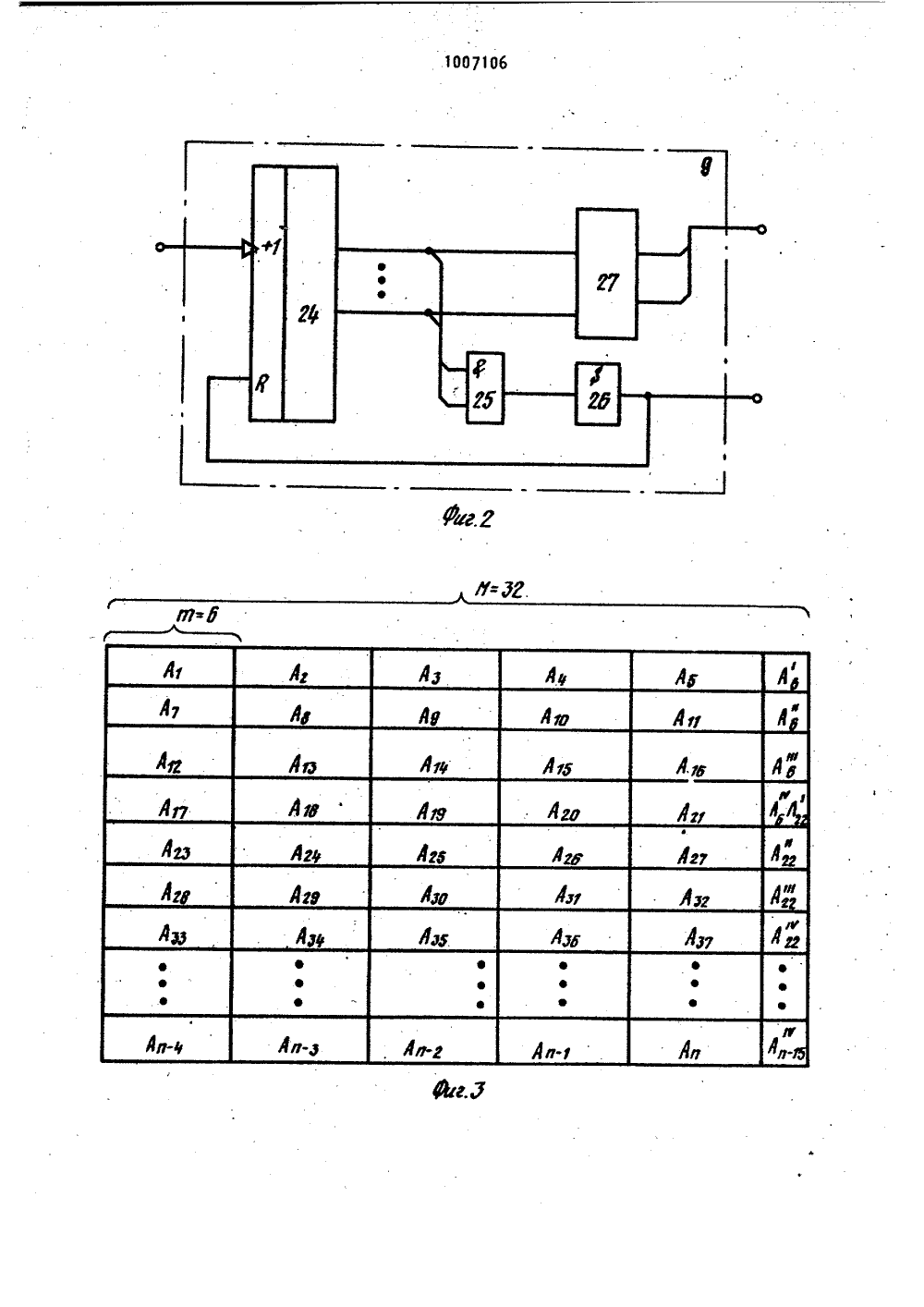

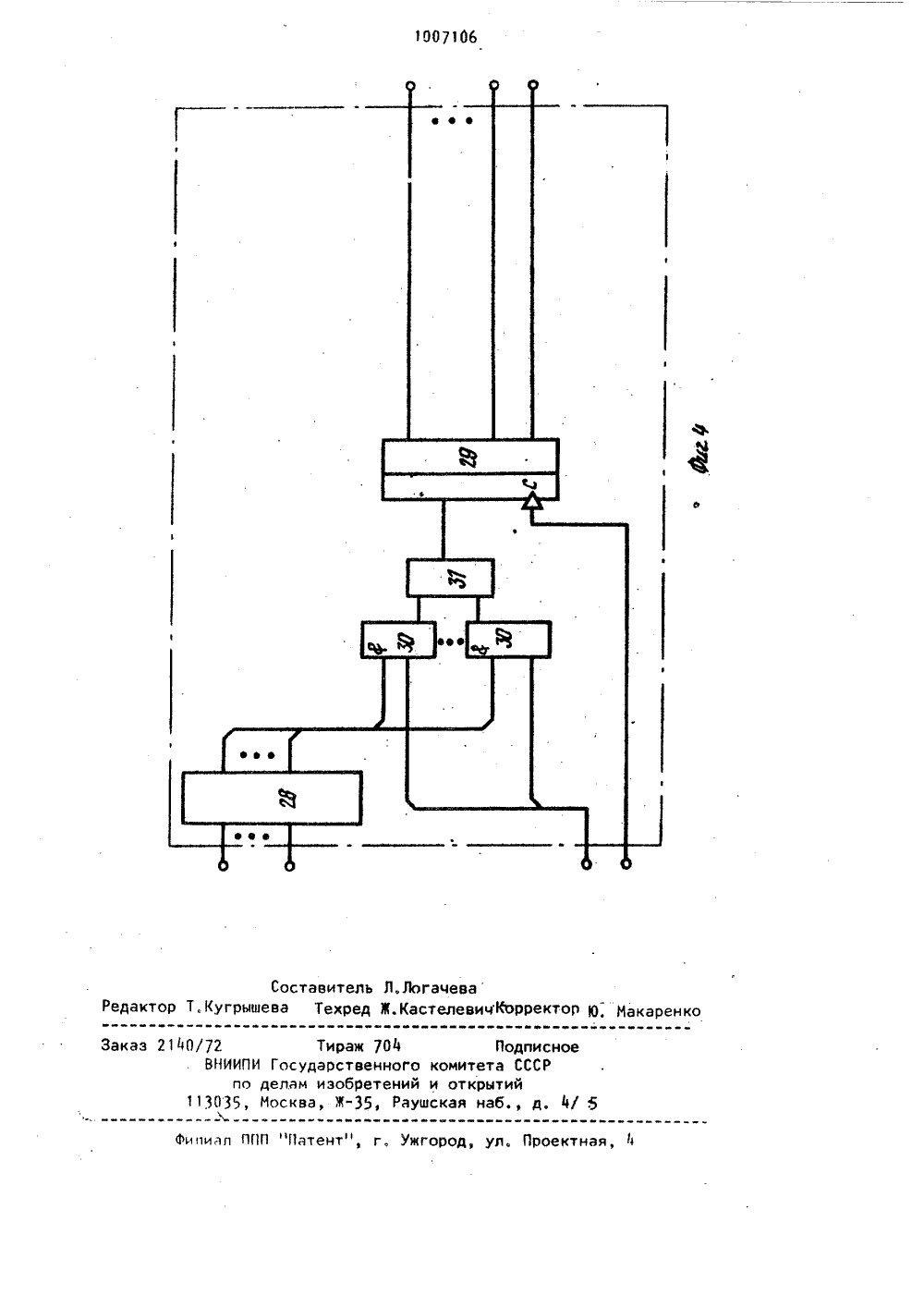

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 071 19) р С 06 Р 9/2 Г= Е ИЗОБРЕТЕНИЯСВИДЕТЕЛЬСТВУ Н АВТОРСК Я.МйайЮ ОСУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ"Статистика", 1979, рис. 15.2, Авторское свидетельство СССРпо заявке У 2961311/18-24,кл. 6 06 Г 9/22, 1981 (прототип).(54) (57) 1.МИКРОПРОГРАММНОЕ УСТ"РОЙСТВО УПРАВЛЕНИЯ, содержащее пер"вый счетчик, установочный вход которого подключен к адресному входу устройства, счетный вход первого счетчи"ка соединен с выходом одновибратора,а выход- с входом первого деширатора, выход которого соединен с адресным входом блока памяти, перваягруппа выходов которого соединена свходами регистра микрокоманд, 1 груп"па (1=1;К, К - число. целых микрокоманд в линейке): выходов которого.соединена с первыми входами элементов И 1-ой группы, выходы которыхсоединены с соответствующими входамиэлементов ИЛИ группы, выходы которыхподключены к операционному выходуустройства, вторые входы элементовИ 1-ой группы соединены с выходомпервого элемента И, с первыми входами элементов И Ь+1) -ой группы, выходы которых соединены с,соответствующими входами элементов ИЛИ группывторые входы элементов И (1+1)-ойгруппы и третьи входы элементов И1"М-ой групп соединены соответственно с выходами второго дещибратора,вход которого соединен с выходомвторого счетчика, счетный вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом генератора тактовыхимпульсов, а второй вход " с единичным выходом первого. триггера, единичный вход которого соединен с выходомпервого элемента ИЛИ, первый входкоторого соединен с входом пуска устройства, а второй вход соединен с выходом первого элемента задержки; пересчетную схему, второй элемент И,второй элемент задержки, о т л и "ч а ю щ и й с я тем, что, с цельюсокращения оборудования, оно дополнительно содержит генератор импульсовсдвига, выход которого соединен спервым входом второго элемента И,второй вход которого соединен с еди"ничным выходом второго триггера, авыход - со счетным входом пересчетнойсхемы и входом синхронизации узласдвига, информационные входы которогосоединены с второй группой выходовблока памяти, управляющие входи узласдвига соединены с группой выходовпересчетной схемы, в выходов - с тре"тьими входами элементов И (1+1)"ойгруппы (е."разрядность микрокоманды),а (в+1)-ый выход - с четвертыми входами элементов И (1+1)-ойгруппы, входом второго элемента задержки и первым входом второго элемента ИЛИ, второй вход которого соединен с выходомпересчетной схемы, а выход - с нуле"вым входом второго триггера, единичный вход которого соединен с выходомтретьего элемента ИЛИ, первый входкоторого соединен с выходом второгоэлемента задержки, а второй вход - с1007 единичным входом первого триггера, нулевой вход которого соединен с выходом одновибратора, выход которого . также соединен с входом установки в нуль второго счетчика и входом первого элемента задержки, а вход - с Ь+1)-ым выходом второго дешифратора.2, Устройство по п,1, о т л ич а ю щ е е с я тем, что пересчетная схема содержйт счетчик, счетный вход которого является входом пересчетной схемы, а вход установки в нуль соединен с выходом пересчетной схемы и выходом одновибратора, вход которого соединен с выходом элемента И, входы которого соединены с соответствующими выходами счетчика и входами дешифратора, выходы которого соединены с группой выходов пересчетной схемы. 1063. Устройство по и.1, о т л ич а ю щ е е с я тем, что узел сдвига содержит буферный регистр, группу элементов И, элемент ИЛИ и регистр сдвига, причем информационные входы узла сдвига соединены с информационными входами буферного регистра, выходы которого соединены с информационными входами группы элементов И, управляющие входы которых соединены с управляющими входами узла сдвига, а вйходы через элемент ИЛИ соединены синформационным входом регистра.,сдвига,сийхронизирующий вход которого соединен с входом синхронизации узла сдвига, первые е выходов которого соединены с первым щ-ым выходами регистра сдвига, а (в+1)-й выход соединен с его в+1) -ым выходом.21 анфратора, выход которого соединен свходом блока памяти, первая группавыходов которого соединена с входами - - регистра микрокоманд, каждая группа 3 выходов которого соединена с первымивходами элементов И одной из 1 группэлементов И, выходы которых соединеныс соответствующими входами группы элементов ИЛИ, выходы которых являются 1 ф выходами устройства вторые входыэлементов И каждой яз к групп соединены с выходами первого элемента И,выход которого также соединен с первыми входами элементов И (1+1) -ой Изобретение относится к цифровой вычислительной техникеи автоматике и может быть использовано при проектировании управляющих устройств ЗВИ и других систем с микропрограммнымуправлением и произвольным форматом микрокоманд.Известно микропрограммное управляющее устройство, содержащее запоминающий блок, два счетчика, два дешифратора, регистр микрокоманд, генегратор импульсов, элементы И, ИЛИ Г 1 .1.Недостатком устройства является большой объем оборудования, вызванный избыточностью запоминающего блока, Избыточность запоминающего блока обусловлена тем, что в линейке памяти может храниться только целое число микрокоманд. Это приводит к тому, что часть ячеек являются незаполненными полезной информацией.Следовательно, число избыточных (неиспользуемых) ячеек в, запоминающем блоке снижает экономичность и надежность устройства.Наиболее близким к предлагаемому изобретению является микропрограммное устройство управления, содержащее первые счетчик, установочный вход которого является первым входом устройства, счетный вход первого счетчика соединен с выходом одновибратора, авыход с входом первого дегруппы, выходы которых соединены ссоответствующими входами группы эле"ментов ИЛИ; вторые входы элементов И(1+1) -ой группы и третьи входы элементов И первой М-ой групп соединены с одним из Ь+1)-го выходов второго дешифратора, вход которого соединен свыходом второго счетчика, счетныйвход которого соединен с выходом первого элемента И, первый вход которогосоединен с выходом первого элемента И,первый вход которого соединен с выходом генератора тактовых импульсов,а второй вход - с единичным выходомпервого триггера, единичный вход которого соединен с выходом первогоэлемента ИЛИ, первый вход которогоявляется вторым входом устройства, авторой вход соединен с выходом перво3 1 ООУ 1 го элемента задержки, пересчетную схему, второй. элемент И, второй элемент ИЛИ, второй элемент задержкиГ 23В известном устройстве вследствие низкой гибкости структуры использует 3 ся не весь объем блока памяти для хранения микрокоманд и имеется больщая аппаратурная избыточность всего устройства. Это обуславливает его низкую экономичность и сужает область 1 в целесообразного применения.Целью изобретения является сокращение оборудования устройства.Поставленная цель достигается тем, что микропрограммное устройство уп- д равления, содержащее первый счетчик, установочный вход которого соединен с адресным входом устройств, счетный вход первого счетчика соединен с выходом одновибратора, а выход - с вхо- щ дом первого дещифратора, выход которого соединен с адресным входом блока памяти, первая группа выходов которого соединена с входами регистра микрокоманд, 1 группа (1=1-:К, К - чис-и ло целых микрокоманд в линейке) выходов которого соединена с первыми входами элементов И 1-ой группы, выходы которых соединены с соответствующими входами элементов ИЛИ группы, выходы которых подключены к операционному выходу устройства, вторые. входы элементов"И 1-ой группы соединены с выходом первого элемента И, с первыми входами элементов И (к+1)-ой группы,. 35 выходы которых соединены с соответст" вующими входами элементов ИЛИ группы, вторые входы элементов И Ь+1) -ой группы и третьи входы элементов И 1,"к-ой групп соединены соответственно с выходами второго дешифратора, вход которого соединен с выходом второго счетчика, счетный вход которого соединен с выходом первого элемента И,ервый рход которого соединен с выходом генератора тактовых импульсов, а второй вход - с единичным входом первого триггера, единичный вход которого соединен с выходом первого элемента ИЛИ, первый. вход которого соединен с входам пуска устройства, а второй вход соединен с выходом первого элемента -. задержки; пересчетную схему, второй элемент И, второй элемент ИЛИ, второй элемент задержки, дополнительно содержит генератор импульсов сдвига, выход. которого соединен с первым входом второго элемента И, второй вход которого соединен с единичным выходом второго 06 4триггера, а выход - со счетным входомпересчетной схемы и входом синхронизации узла сдвига, информационные входыкоторого соединены с второй группойвыходов блока памяти, управляющие входы узла сдвига соединены с группой выходов пересчетной схемы, в выходов - стретьими входами элементов И (1+1)"ойгруппы, (в" разрядность микрокоманды);а (в+1)-ый выход - с четвертыми входами элементов И (К+1) "ой группы,входом второго элемента задержки ипервым входом второго элемента ИЛИ,второй вход которого соединен с выходом пересчетной схемы, а выход - снулевым входом второго триггера, единичный вход которого соединен с выходом третьего элемента ИЛИ, первыйвход которого соединен с выходом вто.рого элемента задержки, а второйвход - с единичным входом первоготриггера, нулевой вход которого соединен с выходом одновибратора, выход которого также соединен с входом установки в "нуль" второго счетчика ивходом первого элемента задержки, авход - с (к+1)-ым выходом второгодещифратора. Кроме того, пересчетная схема содержит счетчик, счетный вход которого является входом пересчетной схемы, а вход установки в нуль соединен с выходом пересчетной схемы и выходом одновибратора, вход которого соединен с выходом элемента И, входы которого соединены с соответствующими выходами счетчика и входами дещифратора, выходы которого соединены. с группой выходов пересчетной схемы,Кроме того, узел сдвига содержит буферный регистр, группу элементов И, элемент ИЛИ и регистр сдвига, причем информационные входы узла сдвига соединены с информационными входами буферногп регистра, выходы которого соединены с информационными входами группы элементов И, управляющие входы которых соединены с управляющими входами узла сдвига, а выходы .через эле" мент ИЛИ соединены с информационным входом регистра сдвига, синхронизирую" щий вход которого соединен с входом синхронизации узла сдвига, первые в выходов которого соединены с первым+ в-ым выходами регистра сдвига, а (в+1)-й выход соединен с его (в+1)-ым ыодом.5 1007На фиг.1 изображена функциональная схема предлагаемого микропрограммного устройства; на Фиг.2 - Функциональная схема пересчетной схемы; нафиг.3 - вариант упаковки блока памяти при длине линейки блока памятиИ = 32 и длине микрокоманды щ = 7;на фиг,4 - функциональная схема узласдвига,Предлагаемое устройство содержит 1 Впервый счетчик 1, первый дешифратор 2,блок 3 памяти, регистр 4, 1 группэлементов И 5, группу элементов ИЛИ 6,генератор 7 импульсов сдвига 4, второй элемент И 8, пересчетную схему 9, 1 зузел 10 сдвига,К+1) -ю группу элемен- .тов И 11,второй триггер 12,второй элемент.13 задержки, третий элемент ИЛИ 14,второй элемент ИЛИ 15, первый элемент 16 задержки, первый элемент ИЛИ 2017, первый триггер 18, первый эле"мент И 19, второй счетчик 20, второйдешифратор 21, одновибратор 22, гене.ратор 23 тактовых импульсов И.,Пересчетная схема содержит счетчик 24, элемент И 25, одновибратор 26,дешифратор 27,На фиг,3 А- 1-я микрокоманда,А 1, А, А, Я-я микрокоманда, за-,писанйая йо частям; и - количество Звмикрокоманд, записанных в блоке памятиУзел сдвига содержит буферный ре"гистр 28, регистр 29 сдвига, группуэлементов И 30, элемент ИЛИ 31,Предлагаемое устройство работаетследующим образом.На вход устройства поступает начальный адрес, по которому счетчик 1и дешифратор 2 выбирают в блоке 3памяти нужную линейку с микрокомандами. С блока 3 памяти целые микрокоманды переписываются в регистр 4,а часть микрокоманды переписываетсяв первые разряды регистров 29. Сигналпоступающий на другой вход устройствапроходит через элемент ИЛИ 17 и поступает на единичный вход триггера 18.Сигналом триггер устанавливается в"единицу", а с выхода элемента ИЛИ 17через элемент ИЛИ 14 также устанавливается в "единицу" триггер 12, Сигналс его единичного выхода разрешает прохождение импульсов сдвига с генерато"ра 7 через элемент И 8, ИмпульсыЯсдвига поступает на синхронизирующийвход узла 10 и сдвигают информацию врегистре 29, Эти импульсы поступаеттакже на счетный вход счетчика 24. 106 6Счетчик 24 считает импульсы сдвига, и когда их количества будет равно числу разрядов в части микрокоманды, записанной в линейке, на выходе элемента И 25 выявляется сигнал. Этот сигнал поступает на вход одновибратора 26, который вырабатывает импульс, Этот импульс устанавливает в "нуль" счетчик 241 а также через элемент ИЛИ 15 поступает на нулевой вход триггера 12, Триггер 12 запрещает прохождение импульсов сдвига, и информация в узле 1 О не сдвигается.Сйгнал с триггера 18 разрешает прохождение тактовых импульсов с генератора 23 через элемент И 19 на счетный вход счетчика 20. По состоянию счетчика 20 дешифратор поочередно считывает микрокоманды через груПпы элементов И 5 и группу элементов ИЛИ,при наличии тактового импульса с выхода элемента И 19 на втором входе элементов И 5 в порядке очередности считываются все 1 микрокоманд. Бсли в регистре 1 О полной микрокоманды нет, о чем говорит отсутствие метки на (в+1)-ом выходе узла 10, то по сигналу на (1+1)-ом выходе дешифратора 21 одновибратор 22 формирует импульс, который устанавливает счетчик 20 и триггер 18 в "нуль", увеличивает содержимое счетчика 1 и поступает на вход элемента 16 задержки, Бсли же в узле 1 О записана полностью микрокоманда, о чем свидетельствует метка на (щ+1)-ом выходе, то по сигналу с (1+1) -го выхода дешйфратора 21 считывается микрокоманда.По содержимому счетчика 1 дешифратор 2 в блоке 3 памяти выбирает следуюущую линейку с микрокомандами. Целые микрокоманды с блока 3 памяти переписываются в регистр 4, а часть микрокоманды - в следующие разряды регистра 29. При этом задержанный импульс от одновибратора 22 с выхода элемента задержки через элементы ИЛИ 17 и 14 устанавливает в единичное состояние триггер 12, а также триггер 18 и производит сдвиг информации в узле 10, при этом осуществляется считывание микрокоманд, как было описано выше.В,процессе работы устройства может возникнуть случай, когда на (о+1)-ом выходе регистра 10 появляется метка, и счетчик 9 еще не установлен в "нульР Тогда метка с (в+1)-го выхода регистра 10 через элемент ИЛИ 15 устанавли7, 10071 вает триггер 12 .в "нуль", тем самым запрещая прохождение импульсов сдвига с генератора 7 через элемент И 8, и сдвиг информации. Содержимое счетчика 9 не изменяется. После того, как счи-таны все М микрокоманд, с регистра 10 считывается (1+1)-я микрокоманда. Метка, задержанная элементом 13 задержки, через элемент ИЛИ 14 поступа" .ет на единичный вход триггера 12. е Триггер 12 разрешает прохождение импульсов сдвига через элемент И 8. Счетчик 24 продолжает считать импуль 06 8сы И при наличии сигналов на всех входах элемента И 25, одновибратор формирует импульс. Далее устройство работает аналогично описанному выше.Выигрыш в объеме полезноиспользуемого оборудования предлагаемого уст" ройства по сравнению с известным оценивается выражениемщ 4. ъ ИИ - е 1 М8 Ч - 100 а - " 1003103дФ 2 Иа по отнощенйю к базовому объекту оЧ = 253.1907106 Составитель Р.РогачеваРедактор Т,Кугрышева Техред Ж.КастелевичКорректор 10, Макарен ее ею вел 69 еве 4 иал ППП "Патент", г, Ужгород, ул. Проектная, 1 1 ЙО/72 Тираж ВНИИПИ Государств по делам изобр 113035, Москва, Жнного ком тений и оРаушска Подписиета СССРрытийнаб д.

СмотретьЗаявка

3317913, 20.07.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

КОНДРАТЬЕВ ИГОРЬ ЕВГЕНЬЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.03.1983

Код ссылки

<a href="https://patents.su/8-1007106-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Интегродифференциальный вычислитель

Следующий патент: Устройство микропрограммного управления

Случайный патент: Активный делитель для жаток