Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

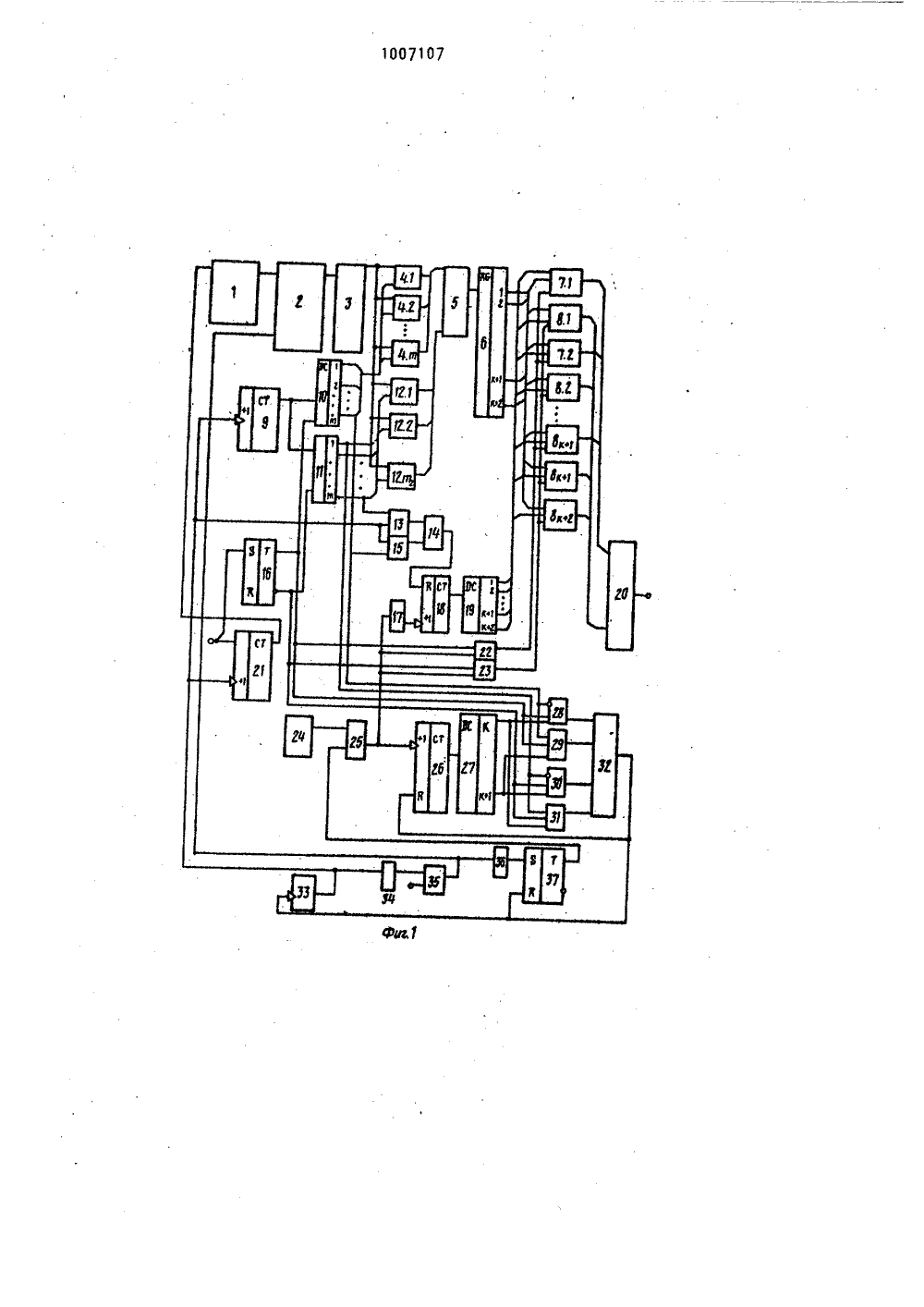

а 91 ОВ У ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙОПИСАНИЕ ИЗОБР РСКОМУ СВИДЕТЕЛЬСТ(56) 1Авторское свидетельство СССР,й 467351, кл. С Об Р 9/22 19752. Авторское свидетельство СССРпо заявке Р 2961311/18-24,кл, С 06 Г 9/22, 1981 (прототип) .(54) (57) УстРойство микРОпРОГРАииНОГО УПРАВЛЕНИЯ, содержащее блок памяти, буферный регистр, четыре счетчика, четыре дешифратора, два блокаэлементов .ИЛИ, регистр микрокоманд,три элемента задержки, четыре эле"мента И, два элемента ИЛИ, генератортактовых импульсов, одновибратор,триггер управления, (щ+К+1) блокэлементов И (К - число микрокомандв линии, щ - число линеек в секции),причем установочный: вход, первогосчетчика соединен с адресным входомустройства, выход счетчика соединенс входом первого дешифратора, выходкоторого соединен с адресным входомблока памяти, выход которого соединенс входом буферного регистра, выходыкоторого соединены с первыми входамипервого (щ)-го блоков элементов И,вторые входы которых соединены соответственно с выходами второго дешифратора, а выходы соединены с первыми (щ ) -м входами первого блокаэлементов ИЛИ, выходы которого соединены с входами регистра микрокоманд,первый (К+1) -й выходы которого соединены с первыми входами (щ +1) Ф1(щ 1+К+1)-го блоков элементов И, вторые входы которых соединены соответ"ственно с выходами третьего дешифратора, а выходы соединены с первым(К+1)-м входами второго блока элементов ИЛИ, выходы которых подключенык выходу устройства, первый вход первого элемента ИЛИ соединен с входомпуска устройства, второй вход соединен через первый элемент задержки свыходом одновибратора, а выход соединен с единичным входом триггерауправления через второй элемент задержки и с управляющим входом блокапамяти, единичный выход триггера управления соединен с первым входомпервого элемента И, второй вход которого соединен с выходом тенераторатактовых импульсов, а выход соедйнен со счетным входом третьего счетчикаи через третий элемент задержки сосчетным входом четвертого счетчика,выход которого соединен с входомтретьего дешифратора, выход третьегосчетчика соединен с входом четвертого дешифратора, К-й выход которогосоединен с первым входом второго элемента И, а (К+1)-й выход соединен спервым входом третьего элемента И, "второй вход которого и инверсный входвторого элемента И соединены с (щ.1)-мвыходом второго дешифратора, а выходы обоих элементов И соединены спервым и вторым входами второго элемента ИЛИ, выход которого соединен свходом установки в нуль третьегосчетчика, с нулевым входом триггераи с входом одноаибратора, выход которого соединен со счетными входамипервого и второго счетчиков и с первым входом четвертого элемента И,второй вход которого соединен с (щ 1)-миал ППР "Патен ВНИИПИ Заказ амар Р 1007107 фиа У 72 Тираж 704 Подпи100 выходом второго дешифратора, о т л и- ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения работы с произвольным, форматом микрокоманд, дополнительно содержит пятый дешифратор, второй триггер, пятый элемент И, третий элемент ИЛИ, (щ +К+2) блоков эле агентов И, причем едйничный вход второго триггера соединен с управляющим входом устройства, единичный выход соединен с управляющим входом второго дешифратора, первым входом пятого элемента И, вторым входом второго элемента И и третьим входом третьего элемента И, нулевой выход второго триггера соединен с управляющим входом пятого дешифратора, выходы которого соединены соответственно с первыми входами (в+К+2) 4. (в +ела+К+1) го блоков элементов И, вторые входы которых соединены с выходами буферного регистра, а выходы соединены с (в+1)(щ+л 2)-ми входами первого блока элемейтов ИЛИ, выходы регистра микрокомандсоединены соответственно с первыми входами (в+в +К+2)(в+а 2+2 К+3) го блоков элементов И, вторые входы которых соединены соответственно с выходами третьего дешифратора, а выходы соединены с (К+2) - (2 К+3)-ми входами второго 7107блока элементов ИЛИ, вторые входы пятого и шестого элементов И соединены с выходом первого элемента И, первь 1 й вход шестого элемента И соединен с нулевым выходом второго триггера, а выходы пятого, шестого элементов И соединены соответственно с третьими . входами (в+1) Ф (в+К+1)-го и (гп.1+о, +К+2)(щ.+в +2 К+3)-го блоков1 2элементов И, первый вход седьмого элемента И соединен с К"м выходом четвертого дешифратора, первый вход восьмого элемента И соединен с (К+1)-м выходом четвертого дешифра" тора, инверсный вход восьмого элемента И и второй вход седьмого элемента И соединены с первым выходом пятого дешифратора, а второй и третий входы восьмого и седьмого элементов И соответственно соединены с нулевым выходом второго триггера, выходы обоих элементов И соединены с третьим и четвертым входами второго элемента ИЛИ, (а )-й выход пятого дешифратора соединей с первым входом девятого элемента И, второй вход которого соединен с выходом одновибратора, а выход соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход соединен с входом установки в нуль четвертого .счетчика.1Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано при синтезе устройствуправления микропрограммных ЭВИ и вычислительных систем, допускающих мо"дификацию Формата микрокоманд.Известно устройство микропрограммного управления, содержащее регистр,дешифратор, блок памяти, логическиеэлементы, счетчик (1 1,Недостатком этого устройства является низкая экономичыость, обусловленная нерациональным использованиемячеек запоминающего блока,Наиболее близким к предлагаемомуизобретению по технической сущностии достигаемому положительному эффекту.является устройство микропрограммногоуправления, содержащее блок памяти,буферный регистр, четыре счетчика,четыре дешифратора, два блока элементов ИЛИ, регистр микрокоманд, три эле.мента задержки, четыре элемента И,два элемента ИЛИ, генератор тактовых 3 импульсов, одновибратор, триггер управления, в+К+1 блок элементов И,причем первйй вход первого счетчикаявляется входом устройства, выход соединен с входами первого дешифратора,выходы которого соединены с первымивходами блока памяти, выходы которогосоединены с входами буферного регистра, выходы которого соединены с первыми входами первого ш-го блоков 1 ф элементов И, вторые входй которых соединены с первым + ш -и выходами второго дешифратора, а выходы соединеныс первым" о-м входами первого блокаэлементов ИЛИ, выходы которого соеди-,нены с входами регистра микрокоманд,3 1 ОО 71 О 7 4 первый+ (К+1)-й выходы которого со- определенной величиной формата микроединены с первыми входами (щ+1)+ команд, модификация которого,в процес(щ.+К+1)-го блоков элементса И, вто- се эксплуатации невозможна. Этот вырыв входы которых соединены с первыми вод является следствием низких функ(К+1)-м выходами третьего дешифраторациональных возможностей устройства. а выходы соединены с первыми -(К+1) Целью изобретения является расшивходами второгоблока элементов ИЛИ, рение функциональных возможностей за , выходы которого являются выходами счет обеспечения работы с произвольустройства, первый вход пеРвого эле- ным форматом микрокоманд, мента ИЛИ является входом пу Уст" О Поставленная цель достигается темЭ ройства, второй вход соединен чеРез, что в устройство микропрограммного первый элемент задержки с выходом управления, содержащее блок памяти, одновибратора, а выход соединен с буферный регистр, четыре счетчика, единичным входом триггера управления четыре дешифратора, два блока элемен- . через второй элемент задержки и с м тов ЙЛИ, регистр микрокоманд, три вторым входом блока памяти, единичный элемента задержки, четыре элемента. И, выход триггера управления соединен с два элемента ИЛИ, генератор тактовых первым входом первого элемента И, импульсов, одновибратор, триггер упвторой вход которого соединен с вы- равления, (щ +К+1) блок элементов И, ходом генератора тактовых импульсоб, м (К - число мйкрокоманд в линии, ща выход соединен со счетным входом число лийеек в секции), причем уста- третьего счетчика и через третий эле- новочный вход первого счетчика сомент задержки со счетным входом чет- единен с адресным входом устройства, вертого счетчика, выходы которого со- выход счетчика соединен с входом перединены с входами третьегодешифратора, 23 вого дешифратора, выход которого совыходы третьего счетчика соединены единен с адресным входом", .блока памятиВ с входами чертвертого дешифра- выход которого соединен с входом бу-, тора, К-й выход которого соединен с ферного регистра, выходы которого сопервым входом второго элемента И а Мдинены с первыми входами первом(К+ .)-и выход соединен с первым вхо-(щ )-го блоков элементов И торыс первыми входами первого л. дом третьего элемента И, второй вход входы которых соединены соответственкоторого и инверсный вход второго но с выходами второго.дешифратора, а Эяемента И соединены с (щ.1-м) вЫходом выходы Соединены с первым. +(щ )- ым. + щ -м второго дешифратора, а выходы обоих входами первого блока элементов ИЛИ) элементов И соединены с пеРвым и вто выходы которого соединены с входами3рым входами второго элемента ИЛИ вы регистра микрокоманд, первый (К+1)-й ход которого соединен с входом уста- выходы которого соединены с первыми новки в нуль третьего счетчика, с ну- входами (щ+1) , (щ +К+1)-го блоков левым входом триггера и с входом одно- элементов И вторые входы ко оры вибратора, выход которого соединен со 46 соединены соответственно с выходами счетными входами пеРвого и второго третьего дешифратора а выходы соеди 1 счетчиков и с первым входом четверто- нены с первым ф(К+1) -м входами второго элемента И, .второй вход которого го блока элементов ИЛИ выходы котоФ ,соединен с (щ -м) выходом второго де- рых подключены к выходу устройства,4 первый вход первого элемента ИЛИ со"Недостатками данного устройства единен с входом пуска устройства,являются низкая экономичность и узкая второй вход соединен чер рй вход соединен через первыи область применения, обусловленные элемент задержки с выходом одновибраследующим. Так как в процессе обработ- тора, а выход соединен с единичным ки информации может возникнуть необ- входом триггера управления через вто"ЗЮходимость, не изменяя длины линейки рой элемент задержки и с управляющим памяти запоминаецего устройства, из- входом блока памяти, единичный выход менить формат микрокоманд, то возни- триггера управления соединен с первым кает ситуация, когда остаток микро- входом первого элемента И, второй команды в линейке больше половины дли- вход которого соединен с выходом гены микрокоманды.Янератора тактовых импульсов, а выходТаким образом, область применения соединен со счетным входом третьего известного устройства ограничивается счетчика и через третий элемент замикропрограммными системами со строго держки со счетным входом четвертого5 10071счетчика, выход которого соединен свходом третьего дешифратора, выходтретьего счетчика соединен с входомчетвертогс .дешифратора, К-й выход которого соединен с первым входом вто- Зрого элемента И, а К+1 -й выходсоединен с первым входом третьегоэлемента И, второй вход которого иинверсный 1 вход второго элемента И соединены с (щ )-м выходом второго де- О1шифратора, а выходы обоих элементов Исоединены с первым и вторым входа(ивторого элемента ИЛИ, выход которогосоединен с входом установки в нуль.третьего сцетцика, с нулевым входомтриггера и с входом одновибратора, выход которого соединен со счетнымивходами первого и второго счетчикови с первым входом четвертого элемента И, второй вход которого соединен 20:с (щ)-м выходом второго дешифратора,дополнительно введены пятый дешифратор, второй триггер, пятый элемент И,третий элемент ИЛИ, (щи+К+2) блоков5 лементов И, причем единичный входвторого триггера соединен с управляющим входом устройства, единичный выход соединен с управляющим входомвторого дешифратора, первым входомпятого элемента И, вторым входом вто- ЗОрого элемента И, и третьм входом третьего элемента И, нулевой выход второго триггера соединен с управляющимвходом пятого дешифратора, выходы которого соединены соответственно с з 5первыми входами (щ+К+2) ф (щ+щ 2+К+1)го блоков элементов И,. вторые входыкоторых соединены с выходами буферного регистра, а выхода соединены с(щ+1) т (щ+щ 2)-ми входами первого 40блока элемейтов ИЛИ, выходы регистрамикрокоманд соединейы соответственнос первыми входами (щ.1+щ,+К+2)щ,)+щ 2+2 К+3)-го блоков элементов И,вторые входы которых соединены соответственно с выходами третьего дерифратора, а выходы соединены сК+2)Ф 12 К+3 )-ми входами второго блокаэлементов ИЛИ, вторые входы пятого ишестого элементов И соединены с выхо"дом первого элемента И, первый входшестого элемента И соединен с нулевымвыходом второго триггера, а выходыпятого и шестого элементов И соединенысоответственно с третьими входами ,(щ.4 ) т (щ+К+1) "го и (щ+п 1 +К+2) -: ф-1 щ.1+щ +2 К+3)-го блоков элементов И,Лпервый вход седьмого элемента И соеди"нен с К-м выходом четвертого дешифра 07тора, первый вход восьмого элемента Исоединен с К+1)-м выходом этогодешифратора, инверсный вход восьмого.элемента И и второй вход седьмогоэлемента И соединены с первым выходомпятого дешифратора, а второй и третийвходы восьмого и седьмого элементов Исоответственно соединены с нулевымвыходом второго триггера, выходы обоихэлементов И соединены с третьим и чет"вертым входами второго элемента ИЛИ,(щ 2)-й выход пятого дешифратора соединен с первым входом девятого элемента И, второй вход которого соединен свыходом одновибратора, а выход соединен с первым входом третьего элемента ИЛИ, второй вход которого соединенс выходом четвертого элемента И, авыход соединен с входом установки внуль четвертого счетчика.На фиг.1 представлена Функциональная схема устройства; на фиг.2 - варианты.упаковок блока памяти при раз-.личной длине его линеек и различномформате микрокоманд; на Фиг.3 - порядок считывания микрокоманд при различных остатках (д); в табл, приЬ 1 0,5, табл.2 при Ь ( 0,5,Устройство Фиг.1 содержит дешифратор 1, блок 2 памяти, буферный регистр 3, первый Ф (щ)-й блоки элементов И 4-,4 щ, первый блок элементов ИЛИ 5, регйстр 6 микрокоманд,+К+1)"й блоки элементов И 12(-,12 щ 2девятый элемент И 13, третий элемент ИЛИ 14, четвертый элемент И 15,второй регистр 16, третий элемент 17задержки, четвертый счетчик 18,третий дешифратор 19, второй блокэлементов ИЛИ 20, первый счетчик 21,пятый элемент И 22, шестой элементИ 23, генератор 24 тактовых импульсов, первый элемент И 23, третийсчетчик 26, четвертый дешифратор 27,второй, третий, восьмой и седьмойэлементы И 28-31 соответственно,второй элемент ИЛИ 32, одновибратор33, первый элемент 34 задержки, первый элемент ИЛИ 35 второй элемент36 задержки, первый триггер 37.На фиг.2 и 3 А- микрокоманды,где 1 - номера микрокоманд, А 1, А",части микрокоманды А, записываемые вразличных линейках, щ -число линеек,7 10071 в которых микрокоманда укладывается целое число раэ, Ч - формат 1 раэрядность ) микрокомагды, о - длина свобод ного поля в линейке после заполнения ее целым числом микрокоманд, К - минимальное целое число микрокоманд, укладывающихся в линеике блока памяти, . 0 - длина линейки блока памяти, М " целое число микрокоманд, при котором выполняется равенство а 1 й Ч вУстройство работает следующим образом.По сигналу "Пуск", поступающему на вход первого элемента ИЛИ 35, разрешается считывание информации из блока 2 памяти. Считанная из ячейки инФормация и состоящая иэ К целых микро- команд и части К+1 -й .микрокоманды, записывается в буферный регистр 3 и через соответствующие, открытые с 26 первого выхода дешифратора 11, блоки элементов И подгруппы блоков элементов И 12 и элементы первого блока элементов ИЛИ 5 поступает на регистр 6 микрокоманд. В его К группах разрядов ф оказываются записанными целые микро- команды, а в (К+1)-ю группу разрядов записывается часть микрокоманды А.Через время, равное времени считы-. вания информации, в регистр 6 микро- команд и определяемое элементов 36 задержки, первый триггер 37 устанавливается в. единичное состояние и импульсы от генератора 24 через открытый элемент. И 25 начинают поступать на третий счетчик 26, на элемент 17 задержки и на пятый и шестой элементы И 22 и 23. Через открытый элемент И 23 разрешающие сигналы поступают на третьи входы. блоков элементов И подгруп- в пы блоков элементовИ 8. Считывается информация из первой группы разрядов регистра 6 микрокоманд. Затем состояние счетчика 18 изменяется и из регист ра 6 микрокоманд считается следующая . группа разрядов, Затеи поочередно воз- буждаются 3 - К-й выходы дешифратора 19, и микрокоманды Ау.АК с соответствующих полей регистра 6 микрокоманд через блоки элементов И 8 также поступают на второй блок элементов ИЛИ 20 и далее на выход устройства. Послеприхода К-го импульса четвертый де" шифратор 27 устанавливается в К-е состояние и, так :как седьмой элемент И 31 Открыт сигналами с первого выхоИ да дешифратора 10 и с нулевого выхода триггера 16, этот импульс, пройдя через второй элемент ИЛИ 32, обнуляет 07 ,8счетчик 26 и триггер 37, блокируя пер-, вый элемент И 25. С задержкой К-й импульс переводит счетчик 18 в состояние, которому соответствует единичный сигнал на (К+1)-м выходе третьего дешифратора 19.Одновременно импульс, сформированный одновибратором 33, увеличивает содержимое счетчиков 21 и 9 на единицу. Меняется код адреса ячейки блока памяти на втором выходе дешифратора 11 появляется единичный сигнал. Тем са" мым закрывается седьмой элемент И 31и открывается восьмой элемент 30 И.Через время, определяемое задерж" кой 34, на выходе первого элемента.ИЛИ 35 появляется сигнал, по которому считывается информация иэ выбранной ячейки .блока памяти. Блоки элементов подгруппы блоков элементов И 12 скоммутированы так что информация иэ ячейки памяти записывается следующим образом: дозаполняется К+1)-я группаразрядов регистра 6, заполняется И +2)-я группа разрядов, заполняется первая, вторая и т.д. группы разрядов, а К-я группа оказывается заполненной не до конца.Через время, определяемое элементом 36 задержки, триггер 37 вновь ус"танавливается в единичное состояние,Разрешая тем самым прохождение тактовых импульсов через первый элемент И 25Первым импульсом генератора считывается из регистра 6 микрокоманд микрокоманда АА , Аи ), записанная в К+1 -й группе разрядов, Вторым импульсом считывается информация из К+ 2)-й грумы разрядов регистра 6 микрокоманд, а затем на первом выходе дешифратора 19 появляется единица, считывается микрокоманда, записанная в первом поле регистра 6 и т.д.К-ым импульсом считывается информация иэ К-й группы разрядов Регистра 6 микрокоманд, так как седьмой эле" мент И 31 закрыт, генератор выдает 1,К+1) -й импульс. По этому импульсусчитывается информация из К+1) -йгруппы разрядов регистра 6 микрокоманд. (К+1) -й импульс проходит черезоткрытый элемент 30 и второй элемент ИЛИ 32 блокирует триггер 37,иобнуляет счетчик 26. Через время, оп" ределяемое элементом .17 задержки, на К+2) -м выходе деширатора 19 ло"является единичный сигнал. СостояниеПосле прихода К-го импульса на счетчик 26, на К-м выходе дешифратора 27 появляется единичный сигнал, ко торый проходит через второй элемент И 28 на первый вход второго элемента, ИЛИ. По этому сигналу обнуляется счетчик 26, триггер 27 устанавливается в нулевое состояние и запрещает про" хождение тактовых импульсов генератора 24 на выход первого элемента И 25; Этот же К-й импульс, пройдя с задержкой на вход счетчика 18, устанавлигЬает дешифратор 19 в 1,К+1) -е состояние. Одновременно импульс, сформиро" ванный одновибратором 33, увеличивает содержимое счетчиков 21 и 9 на единицу. Затем осуществляется считывание информации из следующей ячейки блока.2 памяти в буФерный регистр 3. Микро- команда из этого регистра через блоки элементов И подгруппы блоков элементов И 4 и блок элементов ИЛИ 5 посту" пает в регистр 6 микрокоманд. Причем остаток К+1 -й микрокоманды А 1+,1 поступает в К+1) -ю группу разрядов регистра 6 микрокрманд, где хранится ее первая часть Ак 1. После установки 9 1 оо 710счетчиков 9 и 21 увеличивается наединицу,. Затем разрешается считывание информации из очередной ячейки блокапамяти запоминающего устройства 2,Дополняется К-я группа разрядов ре-гистра б,микрокоманд, Незаполненнойоказывается 1,К 2-Ц-я группа разрядов.Зат .м триггер 37 переключается в единичное состояние, тактовые импульсы 1 впроходят через открытый первый элемент И 25 и происходит считывание1,К+2)-й и 1 - К-й групп разрядов регистра 6 микрокоманд.После считывания информации иза-й ячейки блока памяти запоминающего устройства в регистре 6 микрокоманд оказываются заполненными всегруппы ячеек. Считывание информациипроисходит аналогично вышеописанному. 20Отличие состоит лишь в том, что после прихода К+1) -го импульса считывается последняя микрокоманда и проходит на выход второго элемента ИЛИ 3 ЪТриггер 37 устанавливается в нулевое 25состояние, импульс, выработанный одновибратором 33, проходит на выходтретьего элемента ИЛИ 14 через открытый единичным сигналом с а 2-го выхода.дешифратора 11 девятый элемент И 13 и 39устанавливает в исходное состояниесчетчик 18. На первом выходе дешифра"тора 19 устанавливается единичный сигнал. Сигналом с выхода второго элемента И 32 счетчики 9 и.21 также устазнавливаются в исходное состояниеТаким образом, исходя из особенности упаковки ячеек блока 2 памяти вслучае, когда остаточное поле первойячейки больше половины длины форматамикрокоманды д)0,5, в первом и последующих тактах работы устройства изрегистра 6 микрокоманд считываются Ки 1,К+1) целых микрокоманд соответст"венно. 4В процессе работы формат микроко-манды может поменяться и тогда устрой,ство будет работать во втором режиме.Дпя перевода устройство во второй режим, соответствующий ЬСО,5, на второй триггер 16 подается сигнал, устанавливающий его в единичное состояние,В соответствии с этим разрешающийсигнал подается уже на второй дешифратор 10 на первый вход пятого элеменФЫта И .22 и на вторые входы второго эле-мента И 28 и третьего элемента И 29,В данном режиме устройство функционирует следующим образом. 7 10Счетчики 9 и 18 находятся в состоянии, которым на первых выходах дешифраторов 10 и 19 соответствует единичный сигнал. По команде "Пуск", поступающей на первый вход первого элемен" та ИЛИ 35, разрешается считывание информации из блока 2 памяти в буферный регистр 3; которая поступает далее через соответствующие блоки элементов И подгруппы блоков элементов И 4 и элементы ИЛИ первого блока элементов ИЛИ 5 в регистр 6 микрокоманд.Через время, равное времени считывания информации и определяемое элементов 36 задержки, первый триггер 37 устанавливается в единичное состояние и импульсы от генератора 24 поступают через открытый первый элемент И 25 в счетчик 26, а затем с задержкой, определяемой элементом 17 задержки - в счетчик 18. В результате поочередно . возбуждаются первый К-й выходы дешифратора 19 и микрокоманды АА 1,с соответствующих групп разрядов регистра б микрокоманд через блоки элементов 4 подгруппы .блоков элементов И 7, от крытых разрешающим сигналом с выхода открытого пятого элемента И 22, поступают на соответствующие элементы ИЛИ второго блока элементов ИЛИ 20 и далее на выход устройства,107 12ИЛИ 32, По этому сигналу с выходаэлемента ИЛИ 32 обнуляется счетчик26, регистр 37. Импульсом, в выработанным одновибратором 33, счетчики 9и 2 устанавливаются в исходное состояние, а через открытый единичнымпотенциалом щ-го выхода дешифратора10 четвертый элемент И 15 на выходтретьего элемента ИЛИ 11 проходитсигнал, обнуляюший счетчик 18. Напервых выходах 10, 11 и 19 дешифраторов имеется в наличии единичный сигнал. Устройство готово к новому циклуработы,Таким образом, предлагаемое устройство отличается от прототипа расширенными функциональными возможностями,поскольку позволяет исключить критичность схемы к соотношению длины ос"татка линейки памяти, заполняемогочастью следующей микрокоманды и длинымикрокоманды,Благодаря этому предлагаемое уст"ройство имеет более широкую областьприменения, поскольку позволяет реализовать микропрограммы с различнымипараметрами, используя стандартныеблоки памяти, Кроме того, предлагаемое устройство превосходит прототиппо коэффициенту использования, блоковпамяти, так как полностью реализуетих полезный объем, Для рассмотренныхпримеров выигрыш в объеме оборудования.и коэффициенте его использованиясоставляет После считывания из т,1 ячейки блока 2 памяти запоминающего устрой- в ства информации, которая проходит. из буферного регистра 3 через блоки эле-. ментов И подгруппы блоков эле-. иентов И 4 и элементы первого блока элементов ИЛИ 5, в регистре 6 микро- фф команд записана К+1 полная микрокоманда, Организация считывания этих микрокоманд из регистра 6 микрокоманд в данномцикле осуществляется такие аналогично описанному выье. Отличие 36 состоит лишь в том,.что после установки счетчика 26 в состояние, которому соответствует единица на К-м выходе дешифратора 27, второй элемент И 28 остается закрытым из-за наличия 3 з единичного, сигнала .на Фвыходе де" шифратора 1 О. Поэтому очередным им" , пульсом счетчик 26 переводится в 1,К+1)-е состояние, и с регистра 6 микрокоманд считывается К-я микро- команда через блок элементов И подгруппы блоков элементов И 7, Затем :единичный сигнал с (К+1-го выхода дешифратора 27 проходит через открытый единичным сигналом с а -го выхода1 фз . дешифратора 10 третий элемент И 29, на второй вход второго элемента дЮ= 0=16 Ч =7 Ь 32 9=10 61 У= 12 и при ои 11 1007 в единицу триггера 37 импульс от генератора 21 разрешает выдачу микрокоманды через блоки элементовИ под-группы блоков элементов И 7, открытые единичные потенциалом с (К+1)-го вы- з хода дешифратора 19. Затем этим импульсом счетчик 18 устанавливается в состояние, которому соответствует единичный сигнал на первом выходе дешифратора 19, и с первой группы .О разрядов регистра 6 микрокоманд через блок. элементов И подгруппы блоков элементов И 7 и второй блок элементов ИЛИ 20 на выход устройства поступает мйкрокоманда А)42.МДалее устройство работает аналогично описанному выше. дс=-И" ооца=юйъ32 йПо сравнению .с базовым объектом выигрыш в объеме оборудования блока памяти определяется по формуле.

СмотретьЗаявка

3318108, 20.07.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, МАТВИЕНКО ЮРИЙ АНДРЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 23.03.1983

Код ссылки

<a href="https://patents.su/10-1007107-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Реконфигурируемое устройство с программным управлением

Случайный патент: Торцовое закрытие плавучего дока