Формирователь сигналов выборки адресов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1003141

Автор: Кугаро

Текст

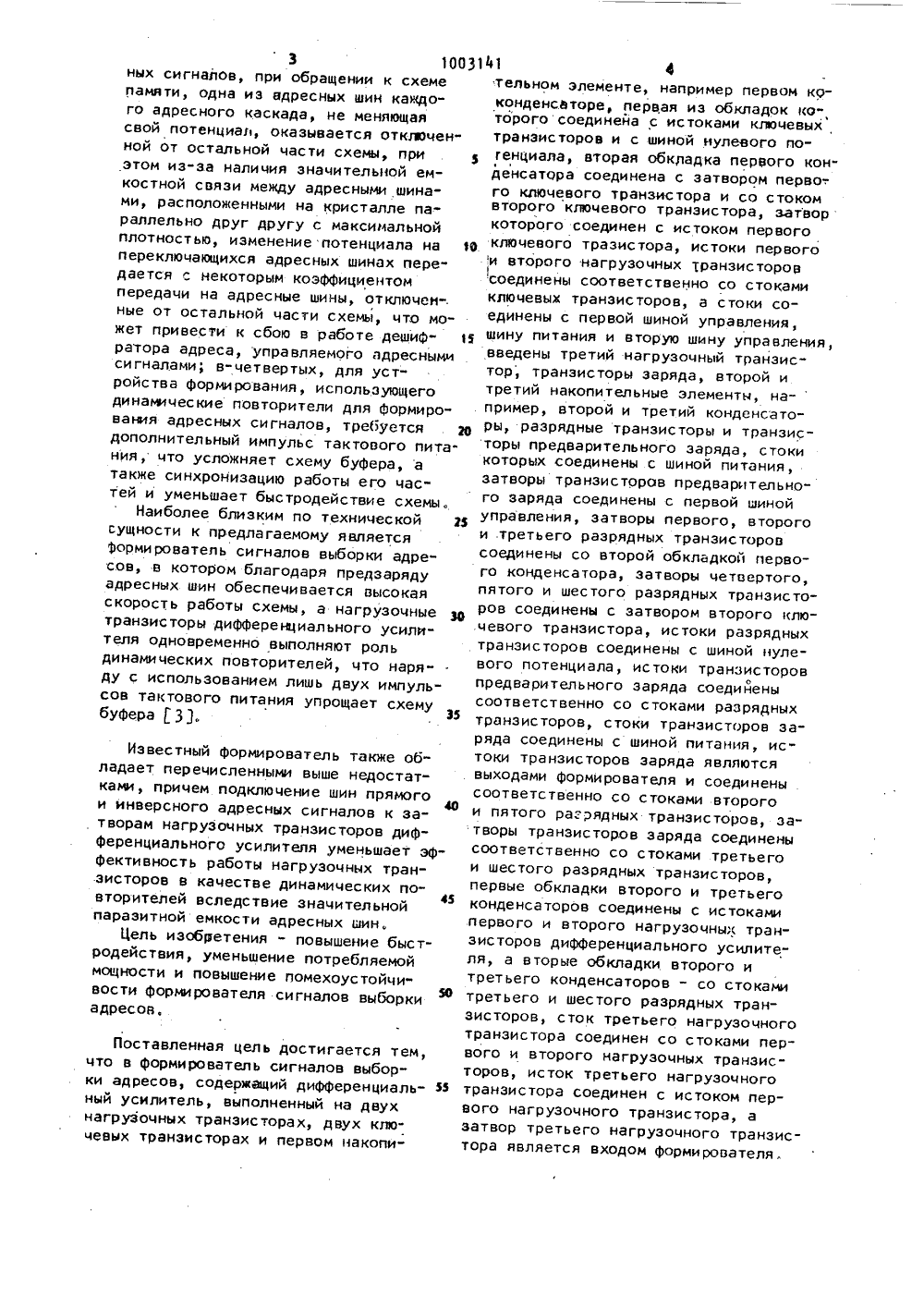

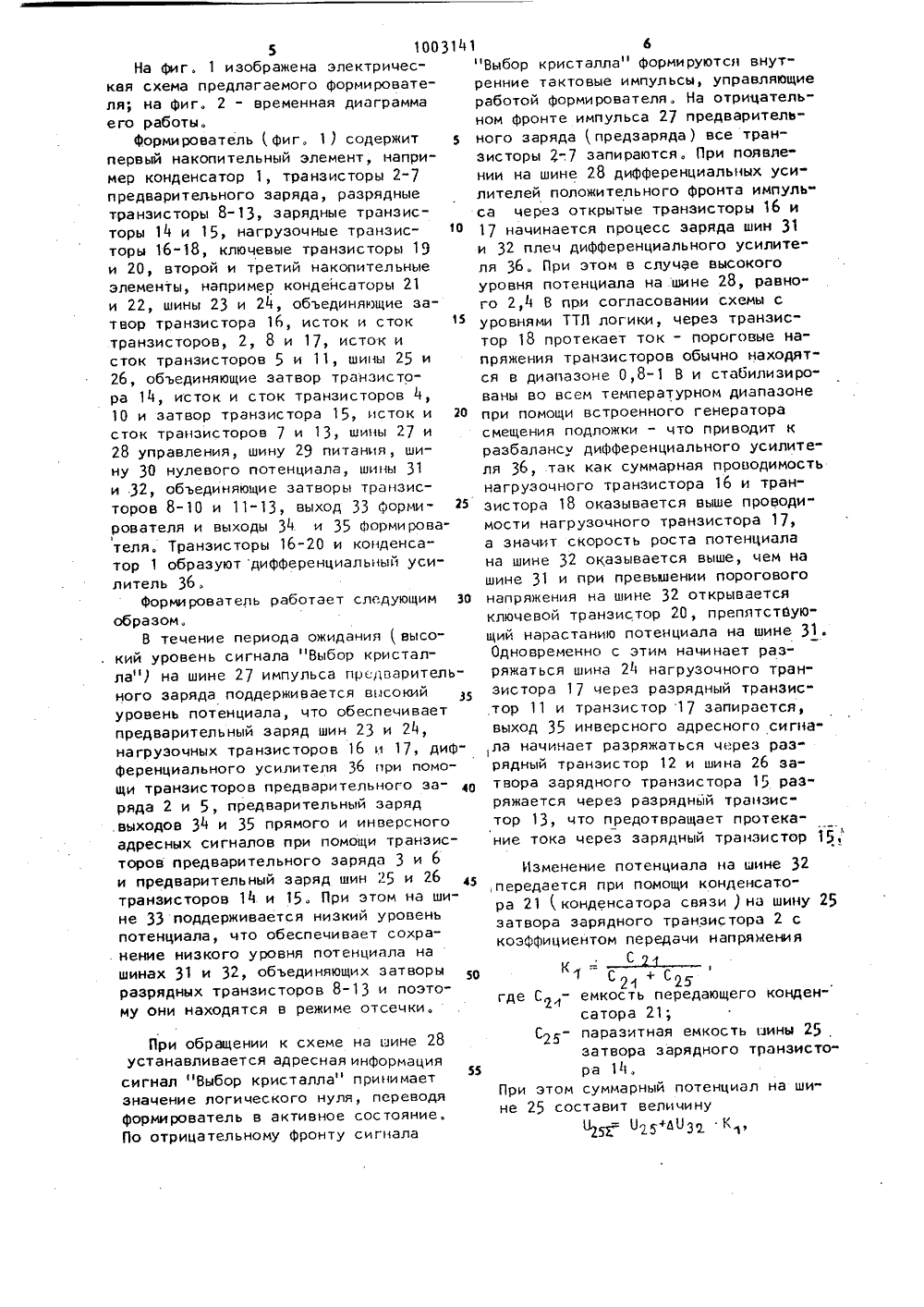

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалистическихРеспублик(51)М, Кл. С, 11 С 8/00 Гесударстеевва кфмитет ае Млам кзебретенкй и вткрмтий(72) Автор изобретения В.С. Кугаро Государственное союзное конструкторско-технологическое боюро по проектированию счетных машин( 5 Й) ФОРМИРОВАТЕЛЪ СИГНАЛОВ ВЫБОРКИ АДРЕСОВ Изобретение относится к вычислительной технике и может быть использовано для построения запоминающих устройств в интегральном исполнении,Известно устройство для формирова-ния адресных сигналов, в котором адресные сигналы формируют с помощьюинверторов Г 1 ),Данное простейшее техническое решение определило, вследствие большой 10емкости адресных шин, невысокое быстродействие устройства при сравнительно высокой потребляемой мощности,свойственной статическим схемам,Известно также устройство для формированчя адресных сигналов, в котором с целью увеличения быстродействияи уменьшения потребляемой мощности,для считывания адресной информациииспользуются дифференциальные усилители, а для Формирования адресных сигналов - динамические повторители,подключенные к каждому из плеч диф 2фере нциального усилителя, Использова" ние д,1 фференциальных усилителей позволяет с высокой скоростью йормировать на затворах динамических повторителей прямой и инверсный адресные сигналы, а использование динамических повторителей позволяет без потерь мощности в устройстве, установить ин" формацию на адресных шинах2 ,Однако известные устройства обладают рядом недостатков, во-первых значительным сквозным потреблением мощности в одном из плеч дифйеренци", ального усилителя; во-вторых исполь" зование предзаряженных адресных шин приводит к пониженному потенциалу логической единицы на адресных шинах вследствие значительных трудностей получения потенциала импульса пред- заряда, превышающего напряжение источника питания; в-третьих, в устройствах, использующих принцип пред" заряда адресных шин или динанические, повторители для формирования адрес 3 10031ных сигналов, при обращении к схеме памяти, одна иэ адресных шин каждого адресного каскада, не меняющая свой потенциал, оказывается отключенной от остальной части схемы, при этом из-за наличия значительной емкостной связи между адресными шинами, расположенными на кристалле параллельно друг другу с максимальной плотностью, изменение потенциала на И переключающихся адресных шинах передается с некоторым коэффициентом передачи на адресные шины, отключен-.ные от остальной части схемы, что может привести к сбою в работе дещиф ратора адреса, управляемого адресными сигналами; в-четвертых, для устройства формирования, использующего динамические повторители для формирования адресных сигналов, требуется 26 дополнительный импульс тактового питания, что усложняет схему буфера, а также синхронизацию работы его частей и уменьшает быстродействие схемы.Наиболее близким по технической 2 З сущности к предлагаемому является формирователь сигналов выборки адресов, в котором благодаря предзаряду адресных шин обеспечивается высокая скорость работы схемы, а нагрузочные щ транзисторы дифференциального усилителя одновременно выполняют роль динамических повторителей, что наряду с использованием лишь двух импульсов тактового питания упрощает схему буфера3 .Известный формирователь также обладает перечисленными выше недостатками, причем подключение шин прямого40 и инверсного адресных сигналов к затворам нагрузочных транзисторов дифференциального усилителя уменьшает эффективность работы нагрузочных транзисторов в качестве динамических по 45 вторителей вследствие значительной параэитной емкости адресных ыин.Цель изобретения - повышение быстродействия, уменьшение потребляемой мощности и повышение помехоустойчивости формирователя сигналов выборки адресов,Поставленная цель достигается тем, что в формирователь сигналов выборки адресов, содержащий дифференциаль- И ный усилитель, выполненный на двух нагрузочных транзисторах, двух ключевых транзисторах и первом накопиИ 4тельном элементе, например первом коконденсаторе, первая иэ обкладок которого соедийейа с истоками ключевых транзисторов и с шиной нулевого погенциала, вторая обкладка первого конденсатора соединена с затвором перво-. го ключевого транзистора и со стоком второго ключевого транзистора, затвор которого соединен с истоком первого ключевого траэистора, истоки первого и второго нагрузочных транзисторов соединены соответственно со стоками ключевых транзисторов, а стоки соединены с первой шиной управления, шину питания и вторую шину управления, введены третий нагрузочный транзистор, транзисторы заряда, второй и третий накопительные элементы, например, второй и третий конденсаторы, разрядные транзисторы и транзисторы предварительного заряда, стоки которых соединены с шиной питания, затворы транзисторов предварительного заряда соединены с первой шиной управления, затворы первого, второго и третьего разрядных транзисторов соединены со второй обкладкой первого конденсатора, затворы четвертого, пятого и шестого разрядных транзисторов соединены с затвором второго клю.чевого транзистора, истоки разрядных транзисторов соединены с шиной нулевого потенциала, истоки транзисторов предварительного заряда соедийены соответственно со стоками разрядных транзисторов, стоки транзисторов заряда соединены с шиной питания, истоки транзисторов заряда являются выходами формирователя и соединены соответственно со стоками второго и пятого разрядных транзисторов, затворы транзисторов заряда соединены соответственно со стоками третьего и шестого разрядных транзисторов, первые обкладки второго и третьего конденсаторов соединены с истоками первого и второго нагрузочных транзисторов дифференциального усилителя, а вторые обкладки второго и третьего конденсаторов - со стоками третьего и шестого разрядных транзисторов, сток третьего нагрузочного транзистора соединен со стоками первого и второго нагрузочных транзисторов, исток третьего нагрузочного транзистора соединен с истоком первого нагрузочного транзистора, а затвор третьего нагрузочного транзистора является входом формирователя,5 1003141 6На фиг. 1 изображена электрическвя схема предлагаемого формирователя; на фиг. 2 - временная диаграммаего работы.формировательфиг. 1) содержитпервый накопительный элемент, например конденсатор 1, транзисторы 2-7предварительного заряда, разрядныетранзисторы 8- 13, зарядные транзис- са через открытые транзисторы 16 иторы 14 и 15, нагрузочные транзисторы 16-18, ключевые транзисторы 19и 20, второй и третий накопительныеэлементы, например конденсаторы 21и 22, шины 23 и 24, объединяющие затвор транзистора 16, исток и сток 15транзисторов, 2, 8 и 17, исток исток транзисторов 5 и 11, шины 25 и26, объединяющие затвор транзистора 14, исток и сток транзисторов 4,10 и затвор транзистора 15, исток и 20сток транзисторов 7 и 13, шины 27 и28 управления, шину 29 питания, шину 30 нулевого потенциала, шины 31и 32, объединяющие затворы транзисторов 8- 10 и 11-13, выход 33 Формирователя и выходы 34 и 35 Формирователя, Транзисторы 16-20 и конденса" а значит скорость роста потенциалатор 1 образуют дифференциальный усилитель 36.Формирователь работает следующим Зообразом.В течение периода ожиданиявысокий уровень сигнала "Выбор кристалла") на шине 27 импульса предварительного заряда поддерживается высокийуровень потенциала, что обеспечиваетпредварительный заряд шин 23 и 24,нагрузочных транзисторов 16 и 17, диф- ла начинает разряжаться через разференциального усилителя 36 при помощи транзисторов предварительного заряда 2 и 5, предварительный заряд.выходов 34 и 35 прямого и инверсногоадресных сигналов при помощи транзисторов предварительного заряда 3 и 6и предварительный заряд шин 25 и 26транзисторов 14 и 15. При этом на шине 33 поддерживается низкий уровеньпотенциала, что обеспечивает сохра. нение низкого уровня потенциала нашинах 31 и 32, объединяющих затворыразрядных транзисторов 8-13 и поэтому они находятся в режиме отсечки,"Выбор кристалла" Формируются внут"ренние тактовые импульсы, управляющие работой Формирователя. На отрицатель"ном фронте импульса 27 предварительного зарядапредзаряда ) все транзисторы 2-.7 запираются, При появле"нии на шине 28 дифференциальных усилителей положительного фронта импуль" 17 начинается процесс заряда шин 31и 32 плеч дифференциального усилите"ля 36, При этом в случае высокогоуровня потенциала на шине 28, равно" го 2,4 В при согласовании схемы суровнями ТТЛ логики, через транзистор 18 протекает ток - пороговые напряжения транзисторов обычно находятся в диапазоне 0,8- 1 В и стабилизиро"ваны во всем температурном диапазонепри помощи встроенного генератора смещения подложки - что приводит кразбалансу дифференциального усилителя 36, так как суммарная проводимость нагрузочного транзистора 16 и транзистора 18 оказывается выше проводи"мости нагрузочного транзистора 17,на шине 32 оказывается выше, чем на шине 31 и при превышении порогового напряжения на шине 32 открывается ключевой транзистор 20, препятствующий нарастанию потенциала на шине 31. Одновременно с этим начинает разряжаться шина 24 нагрузочного транзистора 17 через разрядный транзистор 11 и транзистор 17 запирается, выход 35 инверсного адресного сигна" Изменение потенциала на шине 32 ,передается при помощи конденсато" ра 21конденсатора связи ) на шину 25 затвора зарядного транзистора 2 с коэффициентом передачи напряжения КС 2 + С 2где С - емкость передающего конденсатора 21;С 2- паразитная емкость шины 25затвора зарядного транзистора 14,При этом суммарный потенциал на ши" не 25 составит величинуО 2. О 2+ЬО 3 К При обращении к схеме на нине 28устанавливается адресная информациясигнал "Выбор кристалла" принимает55значение логического нуля, переводяформирователь в активное состояние,По отрицательному Фронту сигнала рядный транзистор 12 и шина 26 за"твора зарядного транзистора 15 разряжается через разрядный транзис"тор 13, что предотвращает протекание тока через зарядный транзистор 15,7 1003141где О - исходный потенциал шины 25затвора зарядного транзис"тора 14;дО - величина изменения потенциа 32ла в плече дифференциального 5усилителя 36.Величина коэффициента передачи напряжения может варьироваться в широких пределах при помощи изменения геометрических размеров 1,а также и емкости) МДП"конденсатора 21.увеличение потенциала на шине 25затвора зарядного транзистора 14 приведет. к его отпиранию и зарядит выход 34 прямого адресного сигнала от 15исходного потенциаланапример,02=Е - ЧТ; где Е - напряжение источника питания, Чт - величина пороговогонапряжения транзистора) до потенциала источника питания, при условии, щчто коэффициент передачи напряжения К. выбран достаточно высоким исуммарный потенциал на шине, 25 составит величину не менееЕ ур.)Е+Чт. . 25Заряд выхода 34 при помощи зарядноготранзистора 14 предотвращает падениепотенциала на адресной шине как засчет возможного паразитного всплеска потенциала на шине 31, так и засчет емкостной связи между выходом 34и другими адресными шинами Формирователей,Изменение потенциала на шине 32на положительном Фронте импульса тактового питания передается на шину 23затвора транзистора 16, причем егозатвор играет здесь роль передающегоконденсатора. благодаря низкойвеличине паразитной емкости шины 23,состоящей иэ емкости перекрытия за,твор-исток транзистора 2, емкостиперекрытия затвор-сток разрядноготранзистора 8 и емкости межсоединений, суммарный потенциал на шине 23может превысить напряжение источника 45питанияесли при этом достаточновелика емкость затвора нагрузочноготранзистора ). 55 В случае низкого потенциала на шине 33, равного 0,8 В при согласовании схемы с уровнями ТТЛ логики, транзистор 18 заперт и ток через него равен нулю. Благодаря небольшой разнице в ширине каналов нагрузочных транзисторов 16 и 17, дифференциальный усилитель 36 на фронте импульса тактового питания устанавливается в состояние, при котором шина 31 заряжена до высокого логичес- ) кого уровня. При этом разряжается шина 23 затвора нагрузочного транзистора 16 через разрядный транзис,тор 8, разряжается также и выход 34 через разрядный транзистор 9, а шина 25 затвора зарядного транзистора 14 разряжается через разрядный транзистор 10, Изменение потенциала на шине 31 передается при помощи конденсатора 22 на шину 26 с коэффициентом передачи напряжения;С22 26где С - емкость передающего конден 22,сатора 22;паразитная емкость шины 2626затвора зарядного транзистора 15.Потенциал на шине 26 в результате превышает напряжение источника питания и происходит заряд выхода 35 инверсного адресного сигнаа через зарядный транзистор 15. Для правильной работы дифференци-. ального усилителя 36 необходимо выполнить следующие условия: оба плеча дифференциального усилителя 36шины 31 и 32) должны иметь одинаковую емкостную нагрузку, так что подключение истока транзистора 18 к одному из плеч дифференциального усилителя 36о должно быть компенсировано подключением конденсатора 1 эквивалентной емкости к другому плечу. Небольшая разница в ширине каналов нагрузочных транзисторов 16 и 17, обеспечивающая несколько большую проводимость нагрузочного транзистора 17, должна быть такова. что при низком уровне - потенциала на шине 33 транзистор 18 не проводит ) дифференциальный усилитель 36 устанавливается в такое состояние, что на шине 31 появляется высокий потенциал, а шина 32 остается при низком уровне потенциала и,при высоком уровне потенциала на шине 33 (транзистор 18 открыт), дифференциальный усилитель 36 устанавливается в противоположное состояние благодаря тому, что суммарная проводимость транзистора 6 и транзистора 18выше, чем проводимость транзистора 17.После окончания сигнала "Выбор крис"талла" происходит восстановление начального состояния формирования, Навходе 28 тактового питания дифференциального усилителя 36 появляется низкий уровень потенциала, что приводитПовышенный потенциал одного из затворов транзисторов 16 или 17 дифференциального усилителя 36 позволяет заряжать одно из его плеч с боль" шей скоростью и до потенциала, равного потенциалу источника питания, Это, в свою очередь, приводит к увеличению быстродействия формирователя, так как приводит к ускорению разряда шины прямого или инверсного адресных сигналов через соответствующий разрядный транзистор, затвор которого подключен к одному иэ плеч дифференциального усилителя 36. 9 100314 к разряду плеча дифференциального усилителя 36, заряженного при обращении к схеме, при этом потенциал на затворе нагрузочного транзистора этого плеча на отрицательном фронте так тового импульса уменьшится до исходного значения благодаря емкостной передаче, где роль передающего конденсатора будет выполнять затвор нагрузочного транзистора дифференциально го усилителя. Изменение потенциала одного из плеч дифференциального усилителя передается через конденсатор 21 или 22 на затвор одного иэ зарядных транзисторов, уменьшая ее потенциал до исходного значения, Появление высокого потенциала на шине 27 импульса предзаряда, открывающего все транзисторы 2-7, происходит с небольшой задержкой относительно отрицательного Фронта тактового импульса для предотвращения сквозного потребления мощности в формирователе. Открытые импульсом 27 предэаряда транзисторы 2-7 предзаряда восстанавливают исходные потенциалы на шинах прямого и инверсного адресных сигналов, на затворах зарядного транзистора и нагрузочного транзистора дифференциального усили-. теля 36, разряженных при обращении к формирователю,При этом следует отметить, что шина прямого или инверсного адресного сигнала, заряженная при обращении до потенциала источника питания, сохра- З 5 нит свой потенциал. Уменьшение этого потенциала до исходного может происходить лишь за счет токов утечки. Однако для дешифратора адреса (не показан ), управляемого предзаряженными 40 адресными шинами, такая неопределенность потенциала адресных шин этот потенциал будет лежать в пределах от Е до (Е-Чт) при потенциале шины 27 импульса предзаряда, равном напряже- Ф 5 нию источника питания ) не существенна, так как этот потенциал поддержи-, вается не ниже определенного уровня ( равного Е- Чт), запирающего адресные транзисторы дешифратора.В предлагаемом формирователе обеспечивае,ся высокая скорость разряда. затворов транзисторов 16 или 17 при обращении в том из плеч дифференциального усилителя 36, где устанавливает 55 ся низкое значение потенциала, благодаря тому, что паразитная емкость шин 23 и 2 ч затворов нагрузочных транзисторов 16 и 17 мала и может 1 10составить величину порядка 0,1-0,2 пф,тогда как в схеме-прототипе к затворам нагрузочных транзисторов подключены шины прямого и инверсного адресных сигналов, емкость которых может достигать величины 3-1 пф и более. Высокая скорость разряда затвора нагрузочного транзистора 16 или 17дифференциального усилителя 36 обеспечивает минимальное время сквозногопотребления мощности, так как сквозной ток в плече дифференциального усилителя 36 будет протекать лишь от начала положительного фронта импульса 33тактового питания 1,точнее после превышения порогового напряженияпротивоположным плечом дифференциальногоусилителя) до разряда затвора нагру"эочного транзистора 16 или 17 до потенциала, меньшего порогового напряжения транзистора. Низкая паразитная емкость шин 23 и 21 затворов нагрузочных транзисторов 16 и 17 обеспечивает высокий коэффициент передачи напряжения на шины 23 и 21 на положительном фронте импульса 33 тактового питания, так что суммарное напряжение на одном из затворов транзисторов 16 или 17 превысит напряжение источника питания при достаточно больших геометрических размерах канала, и, следовательно, большой емкости затворов транзисторов 16 и 17. Значительное увеличение проводимости одного из транзисторов 16 и 17 при эффективном подавлении потенциала затвора и, следовательно, уменьшении проводимости другого транзистора 17 на положителвном фронте импульса шины 28 тактового питания приводит к увеличению раэ" баланса плеч дифференциального усилителя 36, а значит увеличению помехозащищенности формирователя,11 1003Включение транзистора 18 между ши" ной 28 и одним из плеч дифференциального усилителя 36, т.е. параллельно одному из нагрузочных транзисторов 16, а не между плечом дифференциального усилителя 36. и общей шиной источника питания, позволяет избежать уменьшения потенциала логической единицы плеча диФФеренциального усилителя 36 для случая низкого потенциала адресного 1 ф сигналауровня логического нуля ), превышающего пороговое напряжение адресного транзистора и, таким образом, переводящего его из режима отсечки в проводящее состояние, 3%Наличие даже небольшой проводимости транзистора 18 в случае логического нуля на адресном входе про" водит для схем-аналогов к уменьшению разбаланса дифференциального усилителя, а значит к снижению его помехозащищенности и надежности. В формирователе в этом случае опасность умень шения разбаланса схемы значительно снижена благодаря тому, что повышающийся потенциал плеча дифференциального усилителя 36 запирает транзистор 18, ток через него уменьшается и в случае небольшого начального открывающего потенциала быстро становится равным, нулю. Уменьшение проводимости транзистора 18 на фронте импульса, включающего дифференциальный усилитель, имеет место и в случае логической единицыфп -- 2,4 В 1 на шине 28, Однако в современных п -канальных ИС памяти величины пороговых напряжений транзисторов достигают весьма низких значенийоколо 0,8 В и менее ), вследствие чего транзистор 18 будет сильно открыт даже минимальным потенциалом логической единицы на шине 28. даже при достижении потенциала плеча дифференциального усилителя 36 порогового напряжения транзистора. Таким образом, предлагаемый фор,мирователь обладает повышенным быстродействием благодаря высокой скорости переключения усилителя, связанной с органиэацией эффективной обратной связи между плечами дифференциального усилителя и затворами нагрузочных транзисторов и связанный с высоким потенциалом логической единицы одного из плеч дифференциального усилителя, обеспечивающего боль 141 12 ший открывающий потенциал разрядныхтранзисторов, а значит и более высокую скорость разряда подключенных кним шин. Формирователь также обладаетменьшим сквозным потреблением мощности, связанным с высокой скоростьюразряда шины затвора нагрузочноготранзистора плеча дифференциальногоусилителя обладающего сквозным потреблением мощностиФормирователь обладает повышенной помехоустойчивостьюи надежностью, связанным с большейвеличиной разбаланса плеч дифференциального усилителя и с отсутствиемвлияния проводимости адресного транзистора на величину раэбаланса дифференциального усилителя. Устройство формирует на шинах прямого и инверсного адресных сигналов логическиесигналы, принимающие значения или потенциала общей шины источника питания или потенциала источника питания, обеспечивая подавление помех,возникающих как в самом дифференциальном усилителе, так и на кристалле схемы памяти вследствие наличияемкостной связи между шинами прямыхи инверсных адресов сигналов.формула изобретения Формирователь сигналов выборки адресов, содержащий дифференциальный усилитель, выполненный на. двух нагрузочных транзисторах, двух ключевых транзисторах и первом накопительном элементе, .например первом конденсаторе, первая из обкладок которого соединена с истоками ключевых транзисторов и с шиной нулевого потенциала, вторая обкладка первого конденсатора соединена с затвором первого ключевого транзистора и со стоком второго ключевого транзистора, затвор которого соединен с истоком первого ключевого транзистора, истоки первого и второго нагрузочных транзисторов соединены соответственно со стоками ключевых транзисторов, а стоки соединены с первой шиной управления, шину питания и вторую шину управления, отличающийся тем, что, с целью повышения быстродействия, уменьшения потребляемой мощности и повышения помехоустойчи 1 вости формирователя, в него введены третий нагрузочный транзистор, транзисторы заряда, второй и третий накодительные элементы, например второй и третий конденсаторы, разрядные13 100314 транзисторы и транзисторы предвари-тельного заряда, стоки которых соединены с шиноЙ питания, затворы транзисторов предварительного заряда соединены с первой шиной управления, затворы первого, второго и третьего разрядных транзисторов соединены со второй обкладкой первого конденсатора, затворы четвертого, пятого и шестого разрядных транзисторов соединены 1 в с затвором второго ключевого транзистора, истоки разрядных транзисторов соединены с шиной нулевого потенциала, истоки транзисторов вредварительного заряда соединены соответственно со стоками разрядных транзисторов, стоки .транзисторов заряда соединены с шиной питания, истоки транзисторов заряда являются выходами формирователя и соединены соответственно со стоками второго и пятого разрядных транзисторов, затворы транзисторов заряда соединены соответственно со стоками третьего и шестого разрядных транзис 1 14торов, первые обкладки второго и третьего конденсаторов соединены с истоками первого и второго нагрузочныхтранзисторов дифференциального усилителя, а вторые обкладки второго и третьего конденсаторов - со стоками третьего и шестого разрядных транзисто-.ров, сток третьего нагрузочного транзистора соединен со стоками первогои второго нагрузочных транзисторов,исток третьего нагрузочного транзистора соединен с истоком первого нагру"эочного транзистора, а затвор третьего нагрузочного транзистора являетсявходом формирователя,Источники информации,принятые .во внимание при экспертизе 1. "5 о 11 о - 5 айе С гсц 1 э". 1976, У 5, р. 570-573. 2. Патент США М 4074148) кл. О 11 С 8/00, 1979. 3. Патент.США М 4146802,кл. С 11 С 8/00, 3980 (прототип).10031" 1 232 25;2 б г рони тель А.М. Кошту ор екто М. роши 575/35РВНИИПИ Государствепо делам изобреЦ 3035 Москва Ж Филиал ППП "Патент",8 "йроектная, ч ул Соста Ре 8 актор В. Пилипенко Техре Заказ 1 Ти аж 92ного кений иРаушсУжго омитета открыт кая наб

СмотретьЗаявка

3338279, 22.09.1981

ГОСУДАРСТВЕННОЕ СОЮЗНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО ПО ПРОЕКТИРОВАНИЮ СЧЕТНЫХ МАШИН

КУГАРО ВИКТОР СТАНИСЛАВОВИЧ

МПК / Метки

МПК: G11C 8/00

Метки: адресов, выборки, сигналов, формирователь

Опубликовано: 07.03.1983

Код ссылки

<a href="https://patents.su/8-1003141-formirovatel-signalov-vyborki-adresov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сигналов выборки адресов</a>

Предыдущий патент: Интегральный преобразователь индикатора магнитофона

Следующий патент: Динамическое оперативное запоминающее устройство

Случайный патент: Газоразрядная тлеющая лампа