Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

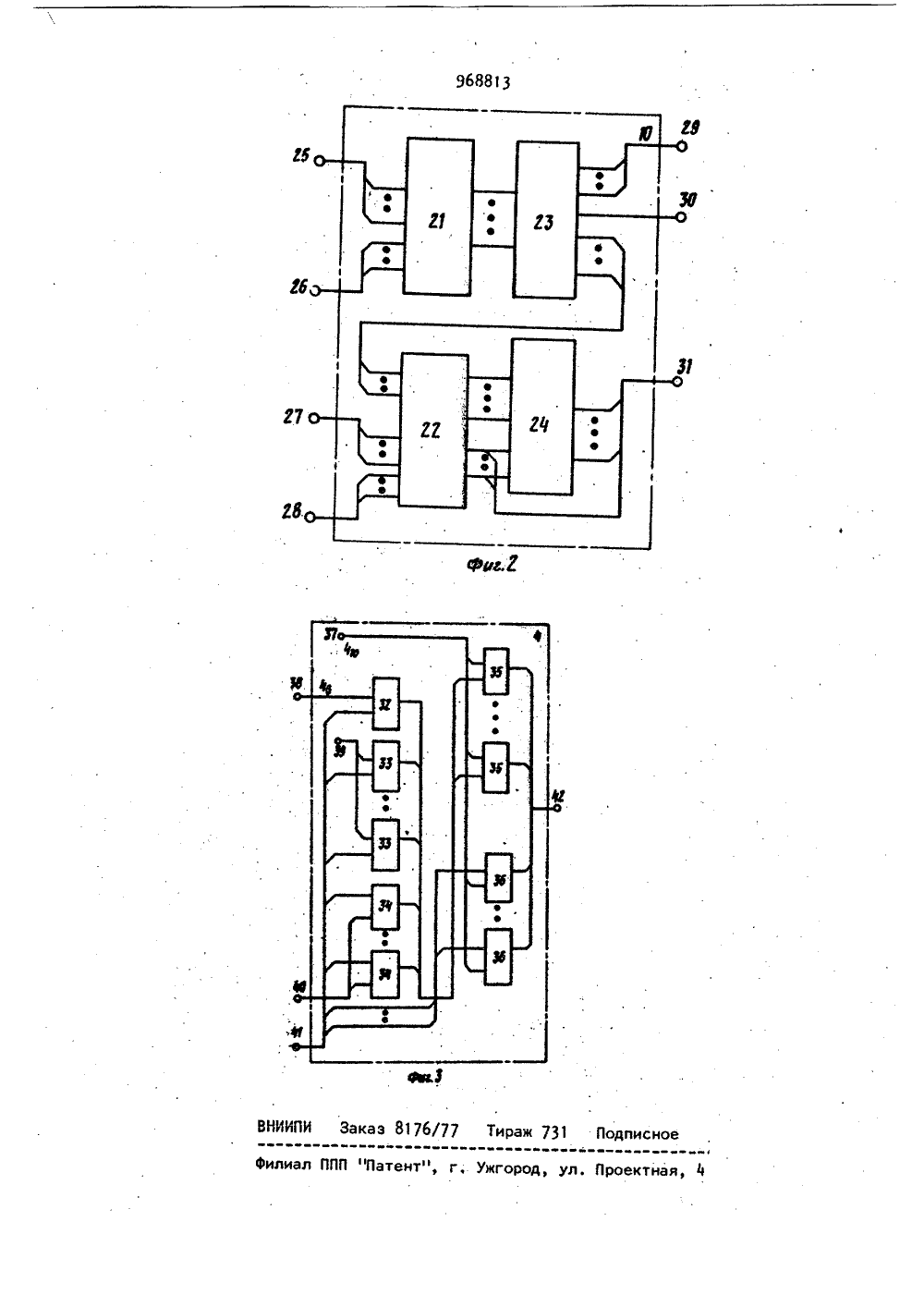

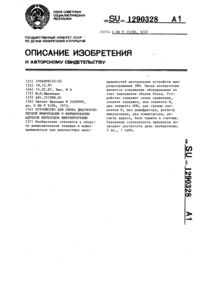

Сееэ СоветсиикСфциалистнческикРеспублик ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ пц 968813(5 )М, Кл. 6 06 Г 9/22 3 ЬоуАврожювй комнтвт СССР в доаиа взобрвтвоий и открытийДата опубликования описания 23 . 1 О .82 В.В.Алексеев, В.Н.Ерженинов, В.И,Ключко, .Г,Н. имоцр 111,и В.С.Харченко.", ,(72) Авторы изобретения БЫзЙ 1) Заявител) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ ния Изобретение относится к цифровой вычислительной технике и можетбыть использОвано при разработкераспределенных вычислительных и управляющих систем в качестве микропрограммного устройства управленияобработкой данных в процессорных модулях и передачей информации междумодулями с защитой от ошибок,Известно микропрограммное устройство управления, содержащее ком"мутатор, регистры адреса и микрокоманд, блок памяти микрокоманд, регистр данных 1.1,Недостатком устройства являетсянизкая производительность, обусловленная сложностью реализации алгоритмов защиты от ошиЬок и отсутствием средств, обеспечивающих непосредственный прием и передачу данных. 2 оНаиболее Ьлизким по техническойсущности и достигаемому положительному эффекту к предлагаемому изобретению является устройствосодержащее коммутатор адреса, первыи информационный регистр, последовательно соединенные Формирователь адреса микрокоманд, регистр адреса, регистр микрокоманд, Ьлок памяти микрокоманд, регистр микрокоманд, первый выход которого соединен с первым входом формирователя адреса микрокоманд, блок приоритета, вход которого является первым входом устройства, второй ин" формационный регистр, вход которого является вторым входом устройства, а выход - соединен с первым входом блока сравнения 1.21.Недостатком устройства является низкая производительность, обусловленная отсутствием специальных средств реализации алгоритмов защиты информа" ции от ошибок и использованием для этого внешних операционных устройств, не ориентированных на данный класс задач, невдзможностью использова режимов ожидания, возникающих при управлении выполнением вычислитель3 96881ных задач, для управления решениемзадач приема, передачи информации изащиты ее от ошибок и перераспределения вычислительных мощностей процессорного модуля.Целью изобретения является повышение производительности микропро"граммного устройства управления передачей и обраЬотки данных.Поставленная цель достигается 1 Отем, что в устройство, содержащеепоследовательно соединенные Формиро-.ватель адреса микрокоманд, регистрадреса, память минрокоманд и регистрмикрокоманд, первый и второй инфор" . мационные регистры, блок приоритета, блок сравнения и коммутатор ад".реса, адресный выход регистра микрокоманд подключен к первому входу формирователя адреса микрокоманд, вход блока приоритета подключен к входу,номера датчика информации устройства, вход второго информационного регистра подключен к первому .Информационному входуустройства, а вы-23 ход соединен с первым входом блокасравнения, дополнительно введены вход;ной и выходной коммутаторы, блок мас"кирования информации и коммутатор данных, причем первый вход входногокоммутатора подключен к второму информационному входу устройства, управляющий вход входногр коммутатораподключен к выходу номера датчика блока приоритета, выход номера каналакоторого подключен к первому входуЗфвыходного коммутатора, а выход признака режима ожидания - к второмувходу формирователя адреса микрокоманд, третий вход которого соединенс входом начального адреса устройст вва, четвертый вход - с входом логических условий устройства, а пятыйвход - с выходом логических условийЬлока маскирования информации, инфор" мационный выход которого соединен с фЗпервыми входами коммутаторов адресаи данных, управляющий выход блока мас"кирования информации подключен к первому выходу устройства, операционный выход регистра микрокоманд под" 0ключен к первому входу блока маскирования информации, второй вход которого соединен с выходом блока сравнения, выходы первого и второго информационных регистров подключены исоответственно к третьему и четвертому входам блока маскирования инфор" мации, к вторым и третьим входам ком 3 4мутатора адреса и данных, выход первого информационного регистра подключен к второму входу блока срав- нения, вход первого информационного регистра соединен с первым информационным входом устройства, информационные выходы выходного коммутатора и коммутатора данных подключены к . второму и третьему выходам устройства соответственно, информационный выход входного коммутатора подключен к четвертому входу коммутатора данных, адресный выход коммутатора адреса подключен к четвертому выходу устройства.При этом блок маскирования информа" ции содержит два дешифратора и два шифратора, причем первый и .второй входы первого дешифратора соединены с первым и вторым входами блока соответственно, третий вход первого дешифратора соединен с первым выходом второго шифратора, а выход - с входом первого шифратора., первый и второй входы первого дешифратора соединены с третьим и четвертым входами блока соответственно, выход второго дешифратора соединен с входом второго шифратора, второй и третий выходы которого соединены с выходом логических условий и с управляющим выходом блока соответственно, выход первого шифратора и выход первого дешифратора соответственно подключены .к информационному выходу блока. Кроме того, формирователь адреса микрокоманд содержит три сумматора по модулю два и две группы элементов, ИЛИ, причем первый вход формирователя подключен к первым входам первого, второго и третьего сумматоров, по модулю два и элементов ИЛИ первой группы, второй вход формирователя подключен к второму входу первого сумматора по модулю два, третий вход формирователя соединен с вторыми входами элементов ИЛИ первой группы и с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены соответственно с выходами пер. вого. сумматора по модулю два, второго и третьего сумматоров пд модулю два, выходы элементов ИЛИ первой и второй групп подключены к выходу формирователя, четвертый и пятый входы формирователя подключены к вторым входам второго и третьего сумматоров по модулю два соответственно,5 9688На фиг. 1 представлена Функциональная схема микропрограммного устройства управления, на фиг. 2 - функциональная схема блока маскирования информации, на Фиг. 3 - формироватепь з здреса микрокоманд.Устройство содержит блок 1 приоритетов, входной коммутатор,2, выходной коммутатор 3, Формирователь 4 адреса микрокоманд, регистр 5.адреса, . 1 О блок 6 памяти микрокоманд, регистр 7 микрокоманд, информационный регистр 8, блок 9 сравнения, блок 10 маскирования информации, коммутатор 11 адреса, информационный регистр 1% 12, коммутатор 13 данных, информационный вход 14 устройства, вход 15 номера датчика информации устройства, второй выход 16 устройства, информационный вход 17 устройства, 20 первый выход .18 устройства, четвертый выход 19 устройства, третий выход 20 устройства.Блок 10 маскирования информации (фиг, 2) содержит два дешифратора 2 з 21, 22, два шифратора 23, 24, входы 25-28 блока, выходы 29-31 блока,Формирователь 4 адреса микрокоманд (фиг. 3) содержит три сумматора 32-34, две группы элементов ИЛИ 35 зв 36, входы 37-41, выход 42.Сущность изобретения состоит в повышении производительности микропрограммного устройства управления передачей и обработкой данных, путем реализации алгоритмов защиты информации от ошибок сиспользованием специализированных микропрограммных средств, ориентированных на .данный класс задач и свободного ресурса оперативной памяти процессорного мо в дуля,"утилизации режимов ожидания, возникающих при управлении вычислительными задачами, для выполнения микропрограмм приема, Передачи и за" щиты информации от. ошибок.В предлагаемом устройстве выполняются микропрограммы управления вычислительными задачами Мв, микропрограммы управления приемом информации от датчиков и передачей ее к по- эв требителям.И. и микропрограммы вы" полнения кодирования информации с целью ее защиты от ошибок при передаче в канал ИвМикропрограммы второй и третьей групп выполняются в режимах ожидания, которые имеют место при управлении вычислительными задачами, а также при изменении (увеличении) их приоритета, задаваемым программными средствами. Специфика этих микропрограммтакова, что они могут Ьыть реализованы с использованием внешней оператив"ной памяти достаточно простыми и бы"стродействующими комбинационными схемами.Предлагаемое устройство работаетв двух основных режимах - режиме управления вычислительными задачами(реализации микропрограмм И )и в режиме приема, кодирования и переда -чи информации (реализации микропрограмм М и М ),Переход из первого режима во второй может быть осуЩествлен принудительно и при возникновении режимовожидания в ходе выполнения микропро"грамм Ив. При этом наступление режима ожидания означает наличие в ходевыполнения микропрограмм Мэ свободного времени и возможности для доступа к оперативной памяти.Работа устройства в первом режимесостоит в следующем.По коду операций, поступающему навход Формирователя 4 и далее в регистр5, из блока б памяти в регистр 7 считывается первая микрокоманда. Сигналы микроопераций подаются в операци"онное устройство процессорного модуля,задавая порядок его работы. Адреснаячасть микрокоманды поступает на формирователь 4, где модифицируется значениями логических условийСформированный код задает адрес следующей микрокоманды, считываемой из блока 6. Да- "лее устройство работает аналогично,последовательно реализуя микропрограммы управления вычислительными задачами, до перехода во второй режим.Во. второй режим устройство переходит при появлении единичного сигналана выходе блока 1 приоритета. По это"му сигналу формирователь 4 адреса Фор.мирует адрес первой микрокоманды,которая считывается затем в регистр7. По этой микрокоманде блок 10 выдает начальный код., а коммутатор 11 и13 формируют информационное слово,подаваемое в оперативную память (навыходы 19, 20).В следующем такте преоЬразование(кодирование) информации осуществляется с учетом кодов, считанных из оперативной памяти в регистры 8, 12.В.регистре 8 записывается закодиро"ванное в первом такте слово, а в,ре9688гистре 12 - номер такта преобразова"ния (и номер датчика информации),Блок 9 сравнения анализирует коды ре-,гистров 8 и 12 и вырабатывает сигналы логических условий равенства их 3соответствующих частей.Блок 10 по сигналам микроопераций иэ регистраосуществляет маскирование информации, поступающей изрегистров 8, 12, и вычисляет новое 16значение адреса (номера такта) и данных, Кроме того, блок 10 на своемвыходе 20 формирует код модификации,адреса и из блока 6 памяти считыва"ется очередная микрокоманда, учитывающая результаты преобразования кодана предыдущем шаге 20Новые значения переменных, вычисленные блоком 10, передаются в ком"мутаторы 11, 13, Коммутатор 11 пере"дает на:выход 13 адресную часть информации, а коммутатор 13 - вычисленные данные и следуоций разряд кодаот датчика, поступающего иэ входного коммутатора 2.Затем из оперативной памяти в ре"гистры 8, 12 считывается следующее эепреобразованное слово и вновь осуществляется вычисление существующихпеременных кода, .к которому присоединяется следующий разряд от датчика информации.ЭЗЕсли устройство одновременно принимает информацию от нескольких дат"чиков, то входной коммутатор 2 пооче"редно коммутирует их выходы и".кодирование осуществляется последователь" 4 Оно для одноименных разрядов этих датчиков, В этом случае в счетчик Ьлока1 приоритета подаются тактовые импульсы и дешифратор последовательнооткрывает элементы И коммутатора 2,разрешая прохождение информации отразличных датчиков.После вычисления последних значений переменных, т.е. окончания кодирования информации ( например, умножения на образующий полином при циклическом кодировании), коммутатор 13передает полученный код на выходной. коммутатор 3. Коммутатор 3 в соответствии с номером канала передаетзакодированное сооЬщение,ЫПри приеме и декодировании инфор"мации устройство работает аналогично описанному выше, В этом случае 13 8блок 10 также осуществляет последовательную оЬработку разрядов (напри-. мер, путем деления на оЬразующий полином при циклическом кодировании).Таким образом, за счет использования режимов ожидания и решения задач приема, кодирования и передачи информации специальными средствами, сравнимыми по быстродействию с комбинационными схемами, предлагаемое устройство существенно превосходит и известное по производительности.Использование предлагаемого устройства позволит разрабатывать высокопроизводительные системы обработки . и передачи данных.Формула изобретения1, Микропрограммное устройство управления, содержащее последовательно соединенные Формирователь адреса микрокоманд, регистр адреса, память микрокоманд и регистр микрокоманд, первый и второй информационные регистры, блок приоритета, блок сравнения и коммутатор адреса., адресный выход регистра микрокоманд подключен к йервому входу формирователя адреса микрокоманд, вход блока приоритета подключен к входу номера датчика информации устройства, вход второго информационного регистра подключен к первому информационному входу устройства, а выход соединен с первым входом блока сравнения, о тл и ч а ю щ е е с я тем, что, с целью повышения производительности устройства, оно дополнительно содержит входной и выходной коммутаторы, блок маскирования информации и коммутатор данных, причем первый вход входного коммутатора подключен к второму информационному входу устройства, управляющий вход входного коммутатора подключен к выходу номера датчика Ьлока приоритета, выход номера канала которого подключен к первому входу выходного коммутатора, а выход признака режима ожиданияк- второму входу формирователя адреса микрокоманд, третий вход которого соединен с входом начального адреса устройства, четвертый вход- входом логических условий устройст" ва, а пятый вход - с выходом логических условий блока маскирования информации, информационный выход ко9688 9торого соединен с первыми входами коммутаторов адреса и данных, управляющий выход блока маскирования информации, подключен к первому выходу устройства, операционный выход регистра микрокоманд подключен к первому входу блока маскирования информации, второй вход которого соединен с выходом блока сравнения, выходы первого и второго информаци онных регистров порключены соответственно к третьему и четвертому входам блока маскирования информации, к вторым и третьим входам коммутаторов адреса и данных, выход первого И информационного регистра подключен к второму входу Ьлока сравнения, вход первого информационного регистра соединен с первым информационным входом устройства, информационные 20 выходы выходного коммутатора и комму. татора данных подключены к второму и третьему выходам устройства соответственно, информационный выход входного коммутатора подключен к четз вертому входу коммутатора данных, адресный выход коммутатора адреса .подключен к четвертому выходу устройства.2. Устройство по и, 1, о т л и - з ч а ю щ е е с.я тем, что блок маскирования информации содержит два дешифратора и два шифратора, причем первый и второй входы первого дешиФратора соединены с первым и .вторым входами блока соответственно, третий вход первого дешифратора соединен с первым выходом второго шифратора, а выход - с входом первого шифратора, первый и второй входы первого дешифратора соединены с третьим и четвер. тым входами блока соответственно,13 10выход второго дешифратора соединенс входом второго шифратора, второйи третий выходы которого соединеныс выходом логических условий и суправляющим выходом блока соответственно, выход первого шифратора ивыход первого дешифратора соответст"венно подключены к информационномувыходу Ьлока.3. Устройство по и. 1, о т л и "ч а ю щ е е с я тем, что формирователь адреса микрокоманд содержит трисумматора по модулю два и две группы элементов ИЛИ, причем первый входФормирователя. подключен к первымвходам первого, второго и третьегосумматоров по модулю два и элементовИЛИ первой группы, второй вход формирователя подключен к второму входу первого сумматора по модулю два,третий вход Формирователя соединенс вторыми входами элементов ИЛИ пер"вой группы и с первыми входами эле"ментов ИЛИ второй группы, вторые входы которых соединены соответственнос выходами первого сумматора по модулю два, второго и третьего сумма"торов по модулю два, выходы элементов ИЛИ первой и второй групп подключены к выходу Формирователя, четвертый и пятый входы Формирователя подключены к вторым входам второго итретьего сумматоров по модулю два со"ответственно.Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРпо заявке 6 2648456, кл. С 06 Г 9/22,"1979.2. Авторское свидетельство СССРпо заявке М 2834705, кл. С 06 Г 9/22,1980 (прототип),968813 НИИПИ Закаэ 8176/77 Тираж 731 Подписное илиад ППП "Патент", г; Ужгород, ул. Проектная, 4

СмотретьЗаявка

3287415, 19.05.1981

ПРЕДПРИЯТИЕ ПЯ Г-4190

АЛЕКСЕЕВ ВАЛЕНТИН ВАСИЛЬЕВИЧ, ЕРЖЕНИНОВ ВАЛЕНТИН НИКОЛАЕВИЧ, КЛЮЧКО ВЛАДИМИР ИГНАТЬЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.10.1982

Код ссылки

<a href="https://patents.su/7-968813-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Умножитель частотно-импульсных сигналов

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для очистки фильтров водозаборных скважин