Устройство для вычисления степенной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

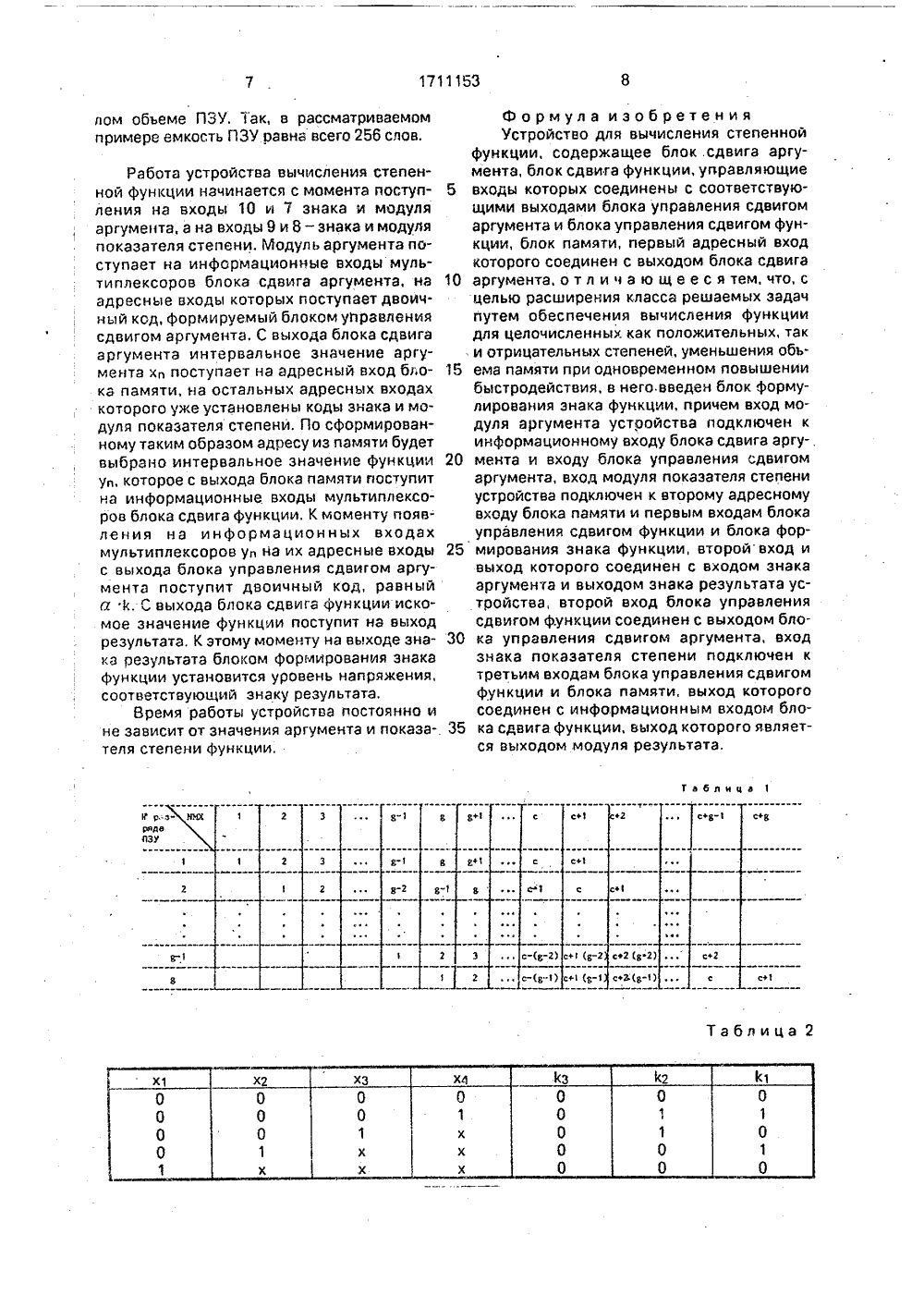

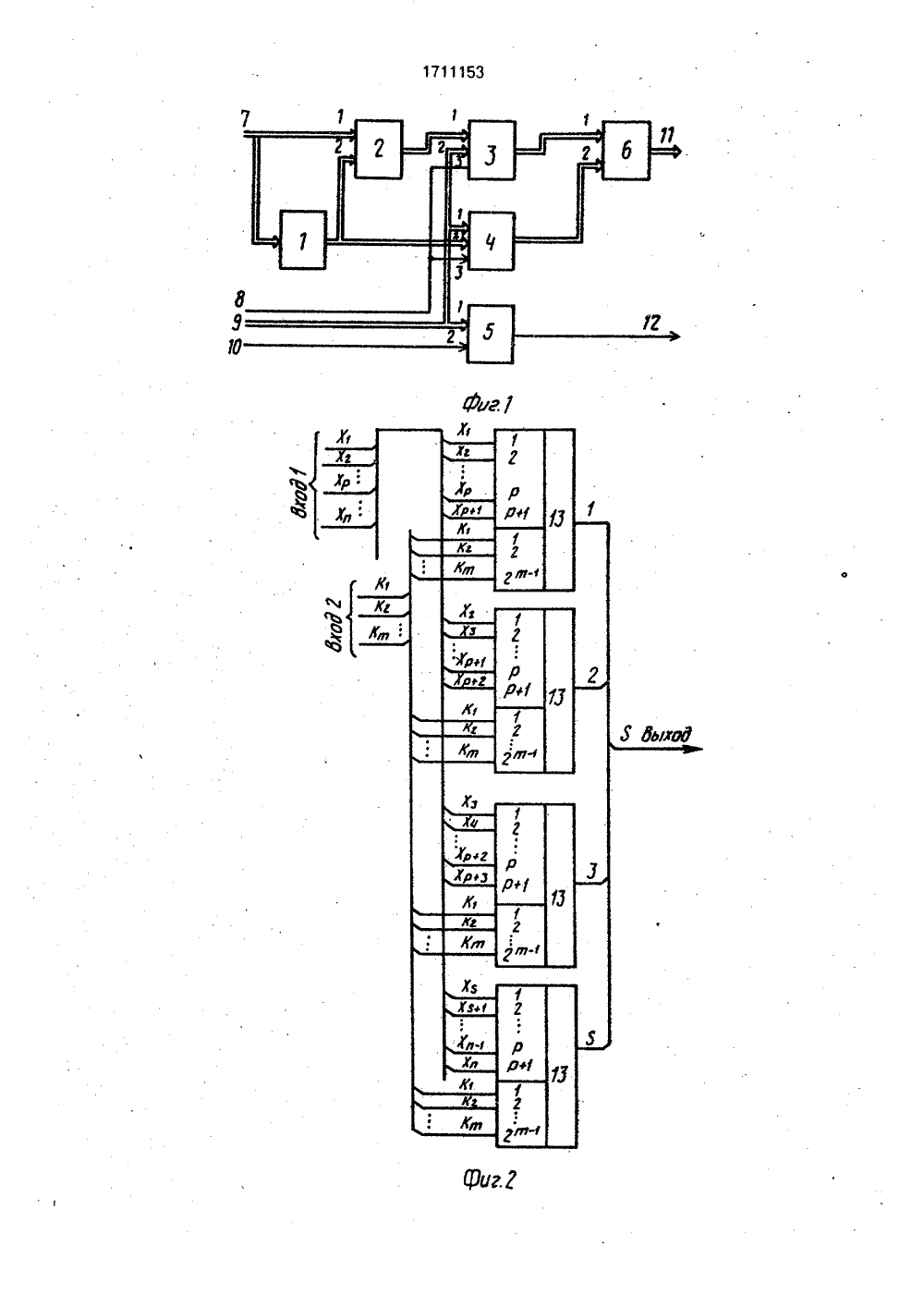

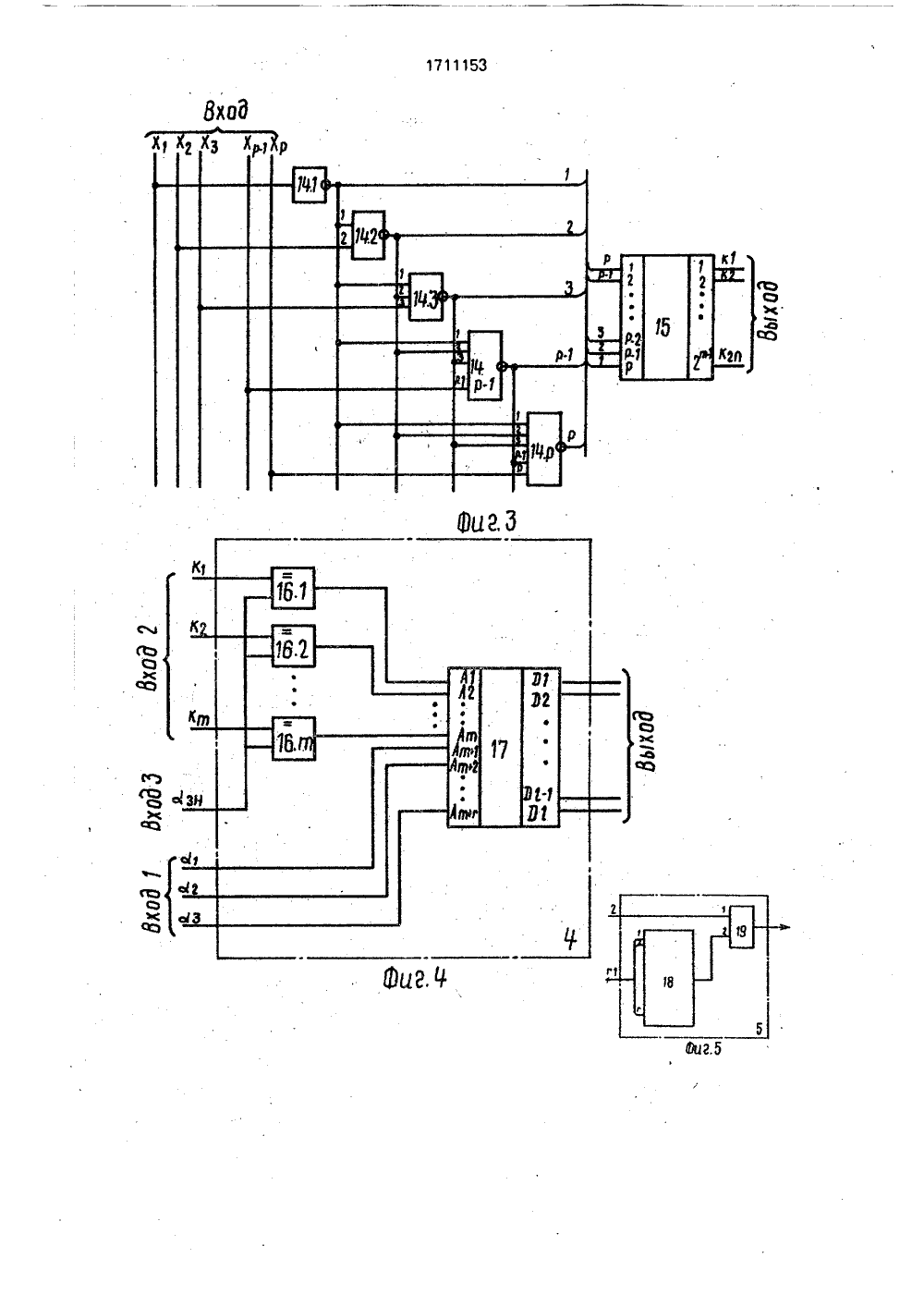

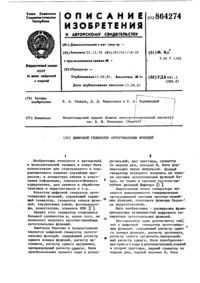

)5 6 Об Р 755 ПИСАНИЕ ИЗОБРЕТЕНИЯ ЕНИЯ ительано в и раз- готав- льных ОСУДАРСТВЕННЫИ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(71) Харьковский институт радиоэлектроники им, акад. М.К,Янгеля(56) Авторское свидетельство СССРМ 1298740, кл. 8 06 Р 7/544, 1985,Авторское свидетельство СССРЯ 746544, кл. 6 06. Р 7/552, 1978,(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛСТЕПЕННОЙ ФУНКЦИИ(57) Изобретение относится к вычислной технике и может быть использовспециализированных ЭВМ, а также прработке вычислительных устройств, изливаемых в составе больших интегра Изобретение относится к вычислительной технике и может бы гь использовано в специализированных Э ВМ, а также при разработке вычислительных устройств, изготавливаемых в составе больших интегральных схем.Цель изобретения - расширение класса решаемых задач за счет вычисления функции для целочисленных как положительных, так и отрицательных степеней уменьшения объема памяти при одновременном повышении быстродействия,На фиг.1 представлена функциональная схема устройства вычисления степенной функции; на фиг.2 - схема блока сдвига аргумента; на фиг.3 - схема блока управления сдвигом аргумента; на фиг,4 - схема блока схем. Цель изобретения - расширение класса решаемых задач за счет вычисления функции для целочисленных как поло. жительных, так и Отрицательных степеней, уменьшения объема памяти при одновременном повышении быстродействия, Поставленная цель достигается тем, что в устройство, содержащее блок памяти, блок управления сдвигом аргумента, блок сдвига аргумента, блок управления сдвигом функции и блок сдвига функции, введен блок формирования знака функции с соответствующими связями. Устройство позволяет вычислять степенную функцию в неограниченной области изменения аргумента при одновременном повышении быстродействия, а также без изменения структуры увеличивать число целочисленных (отрицательных и положительных) значений показателя степени. 6 ил 2 табл. управления сдвигом функции; на фиг,5 - схема блока формирования знака функции; на фиг.б - схема блока сдвига функции.Устройство содержит блок 1 управления сдвигом аргумента, блок 2 сдвига аргумента, блок 3 памяти (постоянное запоминающее устройство), блок 4 управления сдвигом функции, блок 5 формирования знака функции, блок 6 сдвига функции, вход 7 модуля аргумента, вход 8 знака показателя степени, вход 9 модуля показателя степени, вход 10 знака аргумента, выход 11 модуля результата и выход 12 знака результата, мультиплексоры 13, элементы 14,1 - 14.Р И-НЕ, шифратор 15, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 16.1 - 16 в, блок 17 памяти. элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 и элемент И 19.Устройство работает следующим образам;и-разрядный код аргумента х поступает на вход 7 модуля аргумента и далее на первый вход блока 2 сдвига аргумента (фиг,2). Этот блок состоит из Я мультиплексоров 13.1-13.3, информационные входы которых образуют первый вход блока сдвига аргумента, их адресные входы - второй вход сдвига аргумента, а выходы всех мультиплексоров - Я-разрядный выход блока сдвига аргумента, Каждый из мультиплексоров содержит(Р+1) информационных входов, на которые поступают разряды аргумента Х, Выбор номеров разрядов аргумента, подключаемых к каждому мультиплексору, осуществляется по следующему правилу: на каждый мультиплексор поступает па одному на каждый его вход (Р+1) разрядов аргумента так, что на первый охад поступает разряд аргумента, номер катааого равен номеру рассматриваемого мультиплексора. а с увеличением на единицу номера входа мультиплексора увеличивается на единицу и номер разряда аргумента, подключаемого к рассматриваемому мультиплексору.Р старших разрядов аргумента с охода аргумента поступает на вход блока 1 управления сдвигом аргумента (фиг,З), щ-разрядный выход катарага соединен с вторыми входами блока 4 управления сдвигом функции (фиг,4) и блока 2 сдвига аргумента, И блоке 2 сдвига аргумента в-разрядный выход схемы управления сдвигом аргумента подключен поразрядно к гл-разрядному адресному входу одновременно всех Я мультиплексоров,Адрес блока 3 памяти арго иэуется следующим образом, Первый вход(Я младших разрядов адреса) соединен с выходом блока сдвига аргумента; на второй вход(г следующих разрядов адреса) с входа 9 поступает г-разрядный код модуля показателя степени; третий вход (старший разряд адреса) соединен с входом 8 знака показателя степени, На первый и второй входы блока 8 формирования знака функции (фиг.5) поступают соответственно модуль показателя степени с входа 9 и знак аргумента с охода 10, выход блока соединен с выходом 12 знака результата, Первый вход блока 4 управления сдвигом функции связан с входом 9 модуля показателя степени, а ее третий вход - с входом 8 знака показателя степени, 1-разрядный вы од этого блока - с вторым входом блока 6 сдвига функции, 9-разрядный выход блока памяти соединен с первым входам блока 6 сдвига функции (фиг,б). Этот блок состоит из (д+с) мультиплексоров, где с= р Плакс,информационные входы которых образуютпервый вход блока сдвига функции, их адресные входы - второй вход блока сдвига5 функции, а выходы всех мультиплексоров -(9+с)-разрядный выход блока сдвига функции. Каждый из мультиплексоров содержит (с+1) информационных входов, накоторые поступают разряды выхода блока1 О памяти, Выбор номера мультиплексора иномера его выхода для каждого разрядаблока памяти осуществляется в соответствии со следующим правилом; каждый разряд выхода блока памяти поступает15 одновременно на один из входов (с+1)мультиплексоров, начиная с мультиплексора, номер которого совпадает с номеромрассматриваемого разряда, и кончая мультиплексорам, номер которого больше на 20 чальнаго на с, в начальном мультиплексорерассматриваемый раэояд выхода блокапамяти поступает на первый вход, а с увеличением на единицу номера мультиплексора увеличивается на единицу и номер его25 входа, подключаемого к рассматриваемому разряду выхода блока памяти. Правилаиллюстрируется фиг.б и табл,1, В табл,1на пересечении 1-й строки и )-га столбцарасположен номер входа )-го мультиплек 30 сора, к которому подключается 1-й разрядвыхода ПЗУ,Один иэ вариантов схемотехническойреализации блока управления сдвигом аргумента приведен на фиг,З, Функциональное35 назначение этой схемы состоит в том, чтобыопределить число К подряд стоящих нулей,начиная со старшего, в Р разрядах аргумента х. Принцип работы схемы следующий: если 1-й (1р) разряд аргумента40 равен единице. а все старшие (1+0-1-разряды аргумента равны нулю, на выходеблока устанавливается двоичный кад, десятичный эквивалент которого равен числунулей в (1-1) разрядах; если же все Р стар 45 ших разрядов аргумента равны нулю, навыходе блока устанавливается двоичныйкод, десятичный эквивалент которого равен р. Так, для случая р = 4, этот принципиллюстрируется табл,2,50 Р схем И-НЕ формируют унитарный рразрядный код(фиг,З) в 1-м разряде которогопоявляется нуль, если 1-й (11р) разрядаргумента равен единице, а все старшие(1+(И-е разряды аргумента равны нулю.55 йифратор преобразует унитарный код в гпразрядный двоичный код.Один из вариантов реализации блокауправления сдвигом функции приведен нафиг,4, Функциональное назначение этойсхемы состоит в том, чтобы получить двоичное число, равное а К, если аО, и а К,если аО. Блок работает следующим образом. в элементов ИСКЛЮЧАЮЩЕЕ ИЛИреализуют поразрядную инверсию двоичного кода К, если аО, выходы этих элементов образуют е младших адресов блокапамяти ПЗУ, а г-разрядный код - а-г старших адресов ПЗУ, по сформулированномутаким образом адресу читается двоичныйкод искомого произведения.На выходе блока формирования знакафункции (фиг,5) устанавливается уровеньлогической единицы, если аргумент функции отрицательный и нечетный показательстепени,Элементы устройства могут быть реализованы на основе стандартных микросхем,например мультиплексоры второго и шестого блоков - на микросхемах К 155 КП 1,ПЗУ третьего и четвертого блоков - нэ микросхемах типа РТ 556, шифратор и элементы И-НЕ первого блока - соответственно намикросхемах К 155 ИВ 1 и К 155 ЛА 2, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ четвертого и пятого блоков - на микросхеме К 155 ЛП 5,элемент И пятого блока - на микросхемеК 155 ЛИ 1.Устройство позволяет вычислять степенную функцию у=х, где х - положительные иотрицательные действительные числа; а - положительные и отрицательные целые числа,Устройство осуществляет вычисление, используя следующее свойство степеннойфункции: изменение аргумента в б раз приводит к изменению функции в О" раз, Следовательно, если представить функцию втабличном. виде на некотором минимальном интервале, то за счет только операциисдвига аргумента и табличного значенияфункции возможно вычисление искомогозначения функции в неограниченной области изменения аргумента, При этом относительная погрешность вычисления степеннойфункции на всей области ее определенияне будет превышать относительной погрешности ее табличного представления,Табличное представление степеннойфункции на интервале рассмотрим на примере функции у=х .Задаем умакс = 256, а относительнаяпогрешность вычисления пусть будет равна ду = 2, В этом случае значение абсолют ной погрешности для всех уу не будетпревышать единицы.Определяем начальное значение исходного интервала:256 Конечное значение интервала равнохм,= 2 х 4 = 2Определяем шаг разбиения интервала5 1 1 -18Умакс Ь у умзксОпределяем число значащих разрядов двоичного кода аргумента в интервале таб 10 личного представления функции;х -хн5 = 1 о 92 - = 8.Ьх15 В рассчитанном интервале измененияаргумента с шагом Ьх вычисляем все значения функции и заносим е таблицу, Для рассматриваемого случая число табличныхзначений функции равно 256.20 Рассмотрим процедуру вычисленияфункции в двоичной системе счисления.Возможны следующие два случая.Значение аргумента находится в интервале табличного представления функции,25 т.е. хс( хн, х), В этом случае вычислениефункции сводится к выборке из таблицы соответствующего значения функции у,Второй случай, ххк, или хх т.е.х(хн, хк),30 Вводим следующее обозначение: х =хн,если хе (хн, х)., а соответствующие значения у = у. Для всех х (хн. х).справедливо х = 2 х. а для срответствующих значений функции - у = 2 - у, где 1 и35 1 М - целые числа, такие. что 0р (р= п-з).а 0М ас (с = р а макс). Число двоичныхразрядов для представления К равно п 1 ==092 р, для.представления а- г = ю 92 амакс,а для представления л к - г= 1 о 92 С, Очевид 40 но,что МО, если хх и МО, если ххн.Вычисление функции в этом случае осуществляем следующим образом, В ыполняется сдвиг аргумента влево(к0) или вправо( МО) на М разрядов. После такого сдвига45 значащие разряды аргумента попадают винтервал табличного представления функции, что позволяет получить ее табличноезначение ул, Для получения искомого значения функции, полученное табличное значение уп следует сдвинуть на а М разрядовв том же направлении, что и аргумент, еслиаО и в противоположном, если аО.По такому способу вычисление функции осуществляется с абсолютной погрешностью, не превышающей Ьудля всех х, длякоторых уумакс, и с относительной поЬугрешностью, не превышающей яу = у дляУвсей области изменения аргумента при ма1711153 таблицаса 2 3 с лом объеме ПЗУ, Так, в рассматриваемомпримере емкость ПЗУ равна всего 256 слов,Работа устройства вычисления степенной функции начинается с момента поступления на входы 10 и 7 знака и модуля аргумента, а на входы 9 и 8 - знака и модуля показателя степени, Модуль аргумента поступает на информационные входы мультиплексоров блока сдвига аргумента, на адресные входы которых поступает двоичный код, формируемый блоком управления сдвигом аргумента, С выхода блока сдвига аргумента интервальное значение аргумента хп поступает на адресный вход блока памяти, на остальных адресных входах которого уже установлены коды знака и модуля показателя степени. По сформированному таким образом адресу из памяти будет выбрано интервальное значение функции у), которое с выхода блока памяти поступит на информационные входы мультиплексоров блока сдвига функции, К моменту появления на информационных входах мультиплексоров уп на их адресные входы с выхода блока управления сдвигом аргумента поступит двоичный код, равный а К. С выхода блока сдвига функции искомое значение функции поступит на выход результата. К этому моменту на выходе знака результата блоком формирования знака функции установится уровень напряжения, соответствующий знаку результата.Время работы устройства постоянно и не зависит от значения аргумента и показателя степени функции. Формула изобретения Устройство для вычисления степеннойфункции, содержащее блок. сдвига аргумента, блок сдвига функции, управляющие 5 входы которых соединены с соответствующими выходами блока управления сдвигом аргумента и блока управления сдвигом функции, блок памяти, первый адресный вход которого соединен с выходом блока сдвига 10 аргумента, о т л и ч а ю щ е е с я тем, что. сцелью расширения класса решаемых задач путем обеспечения вычисления функции для целочисленных как положительных, так и отрицательных степеней, уменьшения объ ема памяти при одновременном повышениибыстродействия, в него. введен блок формулирования знака функции, причем вход модуля аргумента устоойства подключен к информационному входу блока сдвига аргу мента и входу блока управления сдвигомаргумента, вход модуля показателя степени устройства подключен к второму адресному входу блока памяти и первым входам блока управления сдвигом функции и блока фор мирования знака функции, второй вход ивыход которого соединен с входом знака аргумента и выходом знака результата устройства, второй вход блока управления сдвигом функции соединен с выходом бло ка управления сдвигом аргумента, входзнака показателя степени подключен к третьим входам блока управления сдвигом функции и блока памяти, выход которого соединен с информационным входом бло ка сдвига функции, выход которого является выходом модуля результата.1711153 Составитель В, Гусят Техред М,Моргентал ректор С, Шев Козориз к Патент", г. Ужгород, ул.Гагарина, 10 здательский комб Производств Заказ 340 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Рауаская наб., 4/5

СмотретьЗаявка

4663108, 15.03.1989

ХАРЬКОВСКИЙ ИНСТИТУТ РАДИОЭЛЕКТРОНИКИ ИМ. М. К. ЯНГЕЛЯ

ГУСЯТИН ВЛАДИМИР МИХАЙЛОВИЧ, ГОРБАЧЕВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ, РУДЕНКО ОЛЕГ ГРИГОРЬЕВИЧ, ЛИБЕРОЛЬ БОРИС ДАВЫДОВИЧ, ТИМЧЕНКО ГЕОРГИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, степенной, функции

Опубликовано: 07.02.1992

Код ссылки

<a href="https://patents.su/7-1711153-ustrojjstvo-dlya-vychisleniya-stepennojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления степенной функции</a>

Предыдущий патент: Устройство для умножения двоичных чисел

Следующий патент: Устройство для возведения чисел в n-ю степень

Случайный патент: Способ обесцвечивания сахарных растворов