Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

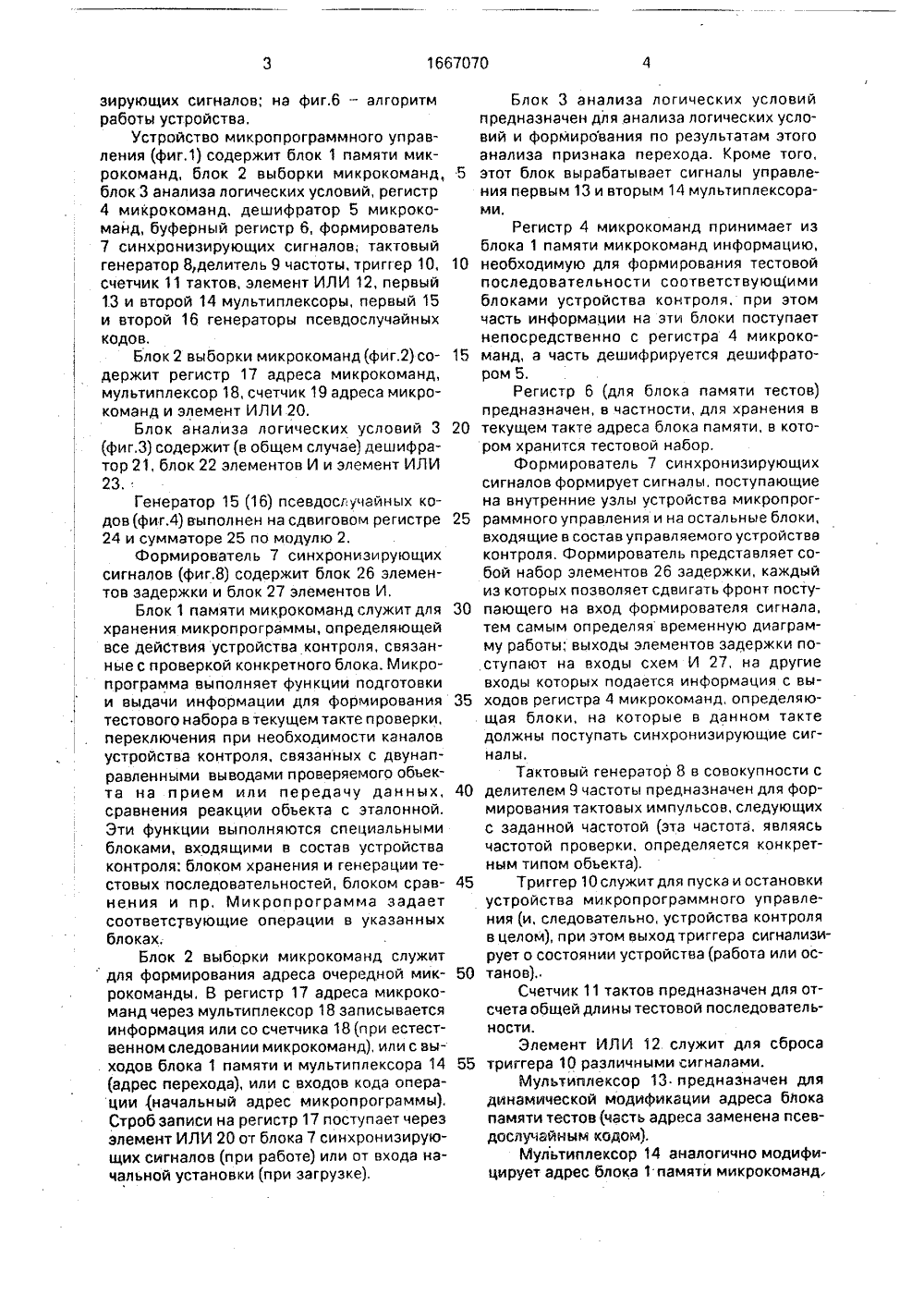

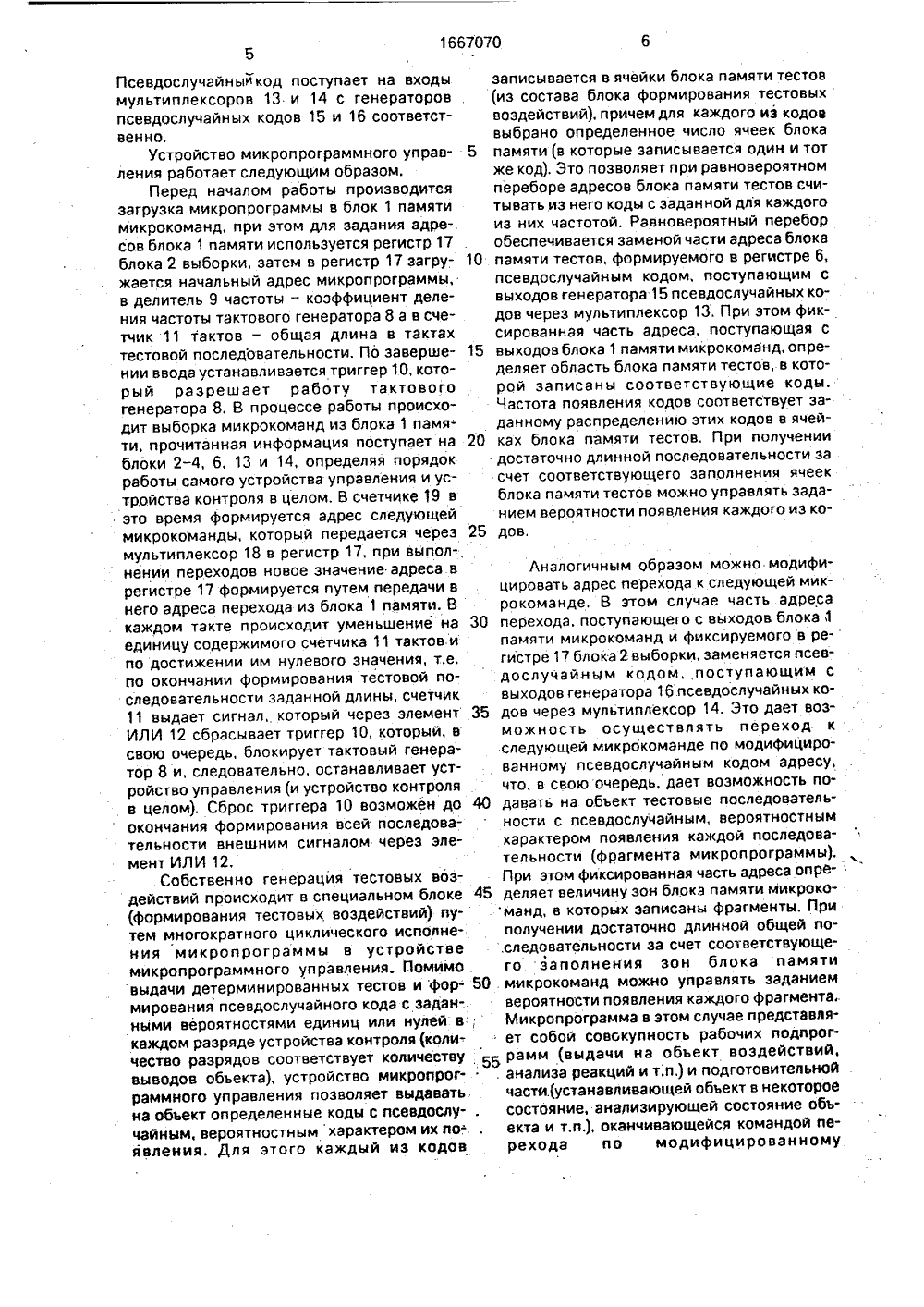

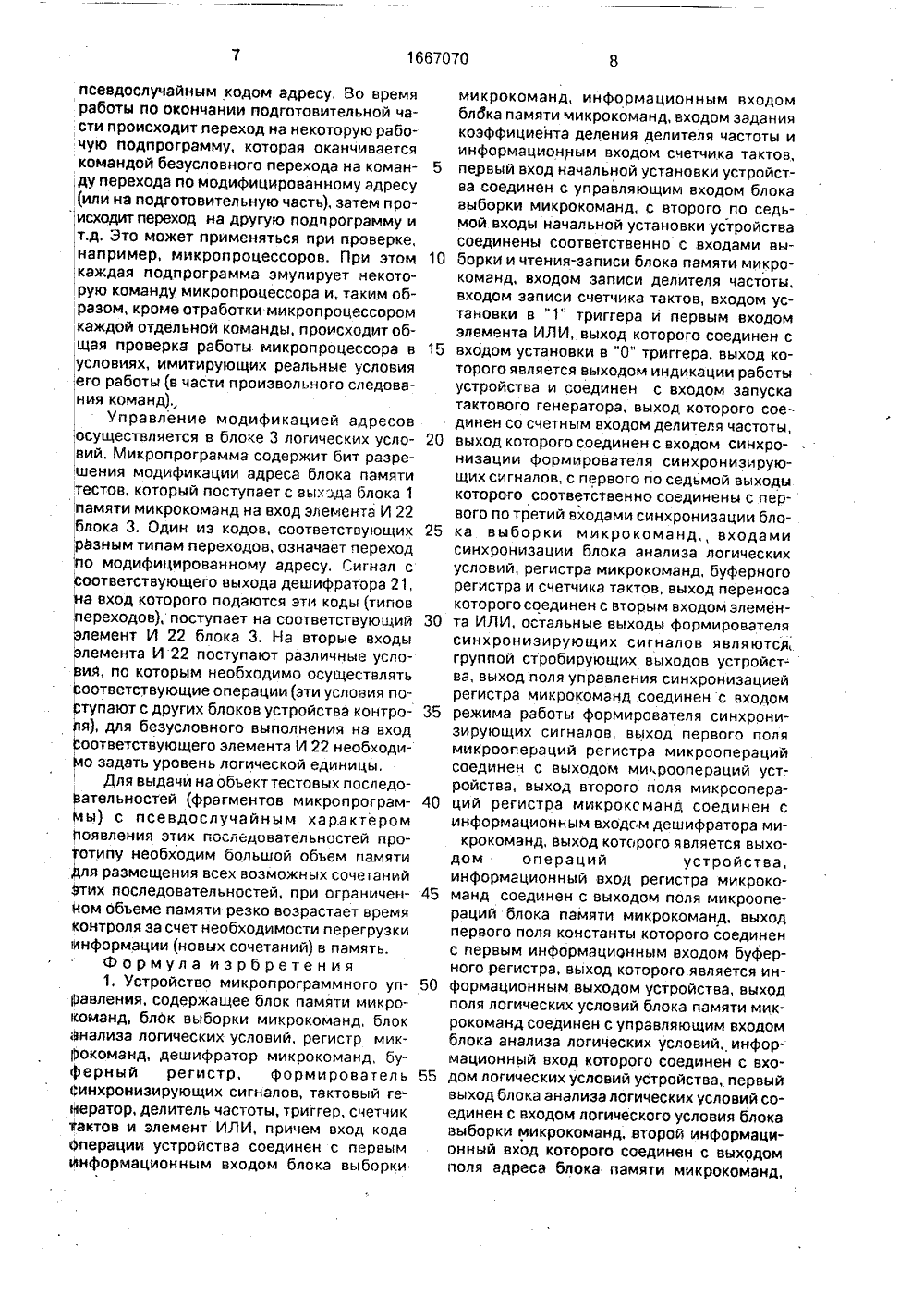

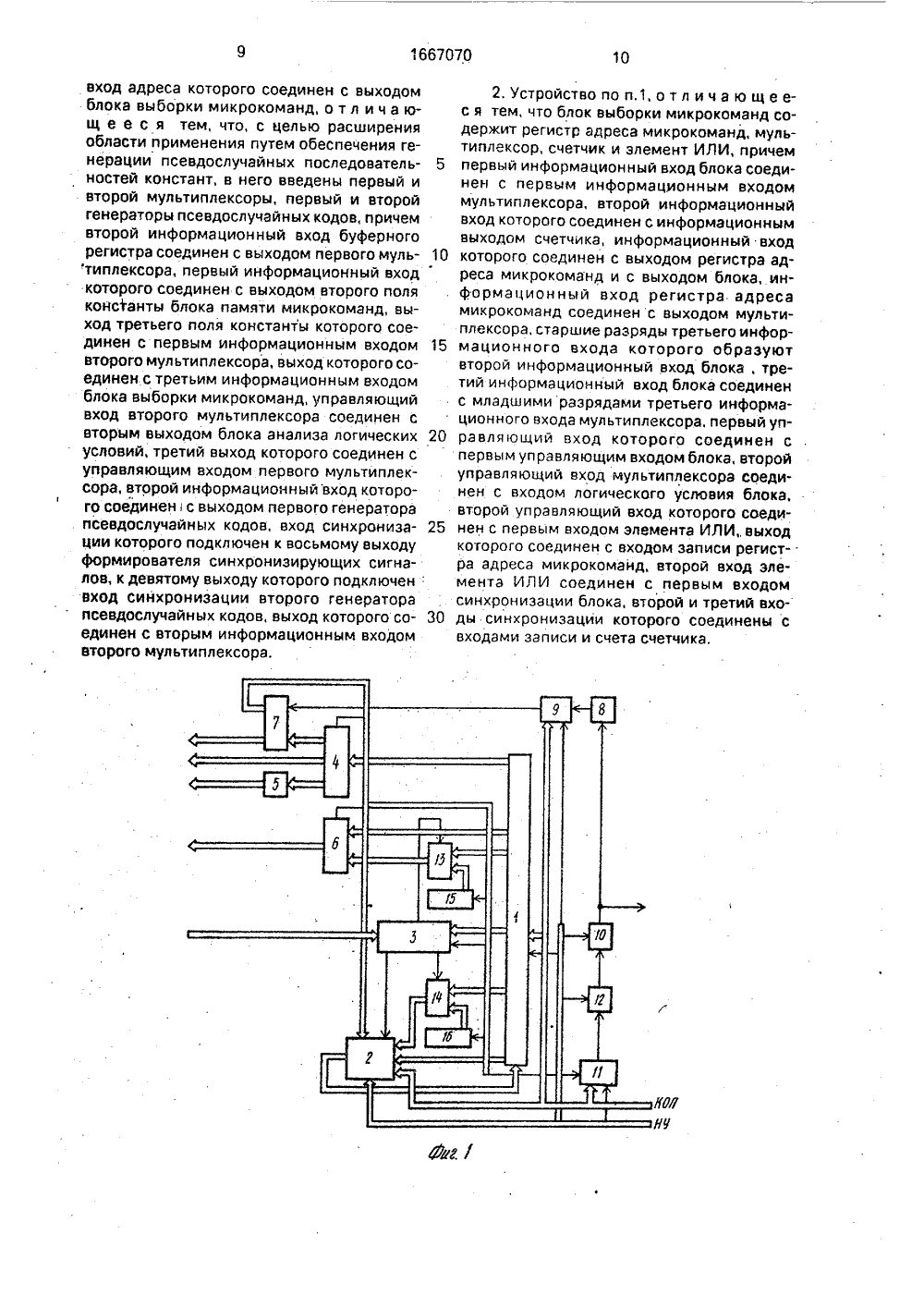

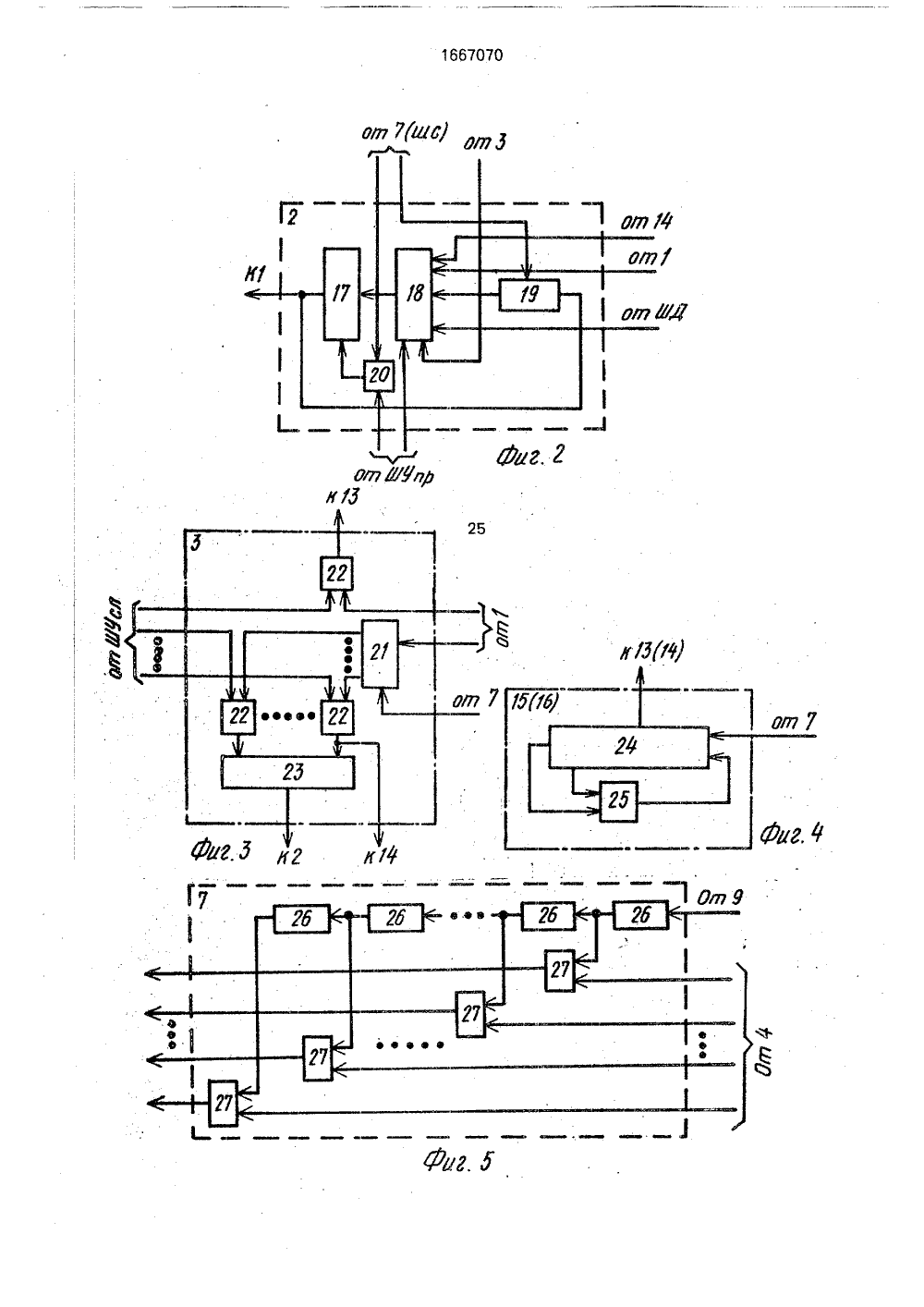

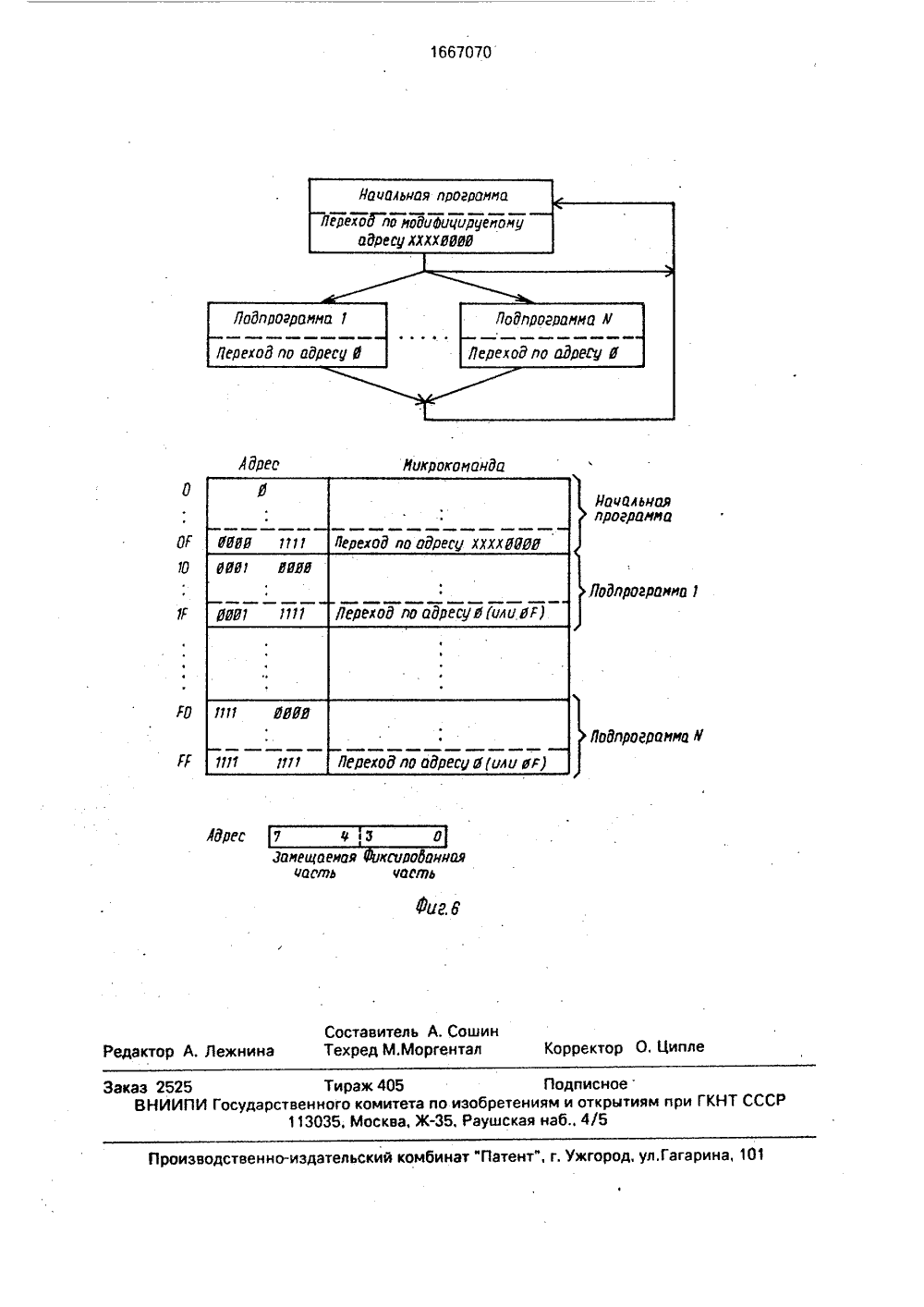

.Рук МН слительам автоъектов и аммируеействий.ширение чения ге-. довательх последоваНа фиг.1 при предлагаемого ус фиг.2 - функцион ки микрокоманд; схема блока анал фиг.4 - функцион псевдослучайных ональная схема ктурная схема правления; на а блока выбор. нкциональная их условий; на ма генератора иг.5 - функциеля синхрониведена струтройства у альная схем на фиг,3- фу иза логическ альная схе кодов; на ф формироват я расширем обеспечеОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ПИСАНИЕ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРВ 642708, кл, 6 06 Е 11/00, 1976.Авторское свидетельство СССРМ 1003086, кл. 6 06 Р 9/22, 1983.Авторское свидетельство СССРМ 1042023, кл, 6 06 Е 11/00, 1983.(54) УСТРОЙСТВО МИКРОПРОГР ГО УПРАВЛЕНИЯ(57) Изобретение относится к вычи ной технике, в частности к средст матической проверки цифровых об может быть использовано в прогр мых генераторах тестовых возд Целью изобретения. является рас области применения путем обеспе нерации псевдослучайных после Изобретение относится к вычислительной технике, в частности к средствам автоматической проверки цифровых обьектов и может быть использовано в программируемых генераторах тестовых воздействий, в устройствах функционального контроля логических блоков ЭВМ и других средств цифровой техники при их производстве и техническом обслуживании.Целью изобретения являетсние области применения путе ностей констант. Устройство микропрограммного управления содержит блок памяти микрокоманд, блок выборки микрокоманд, блок анализа логических условий, регистр микрокоманд, дешифратор микрокоманд, буферный регистр, формирователь синхронизирующих сигналов, тактовый генератор, делитель частоты, триггер, счетчик тактов, элемент ИЛИ, первый и второй мультиплексоры, первый и второй генераторы псевдослучайных кодов. Генерация тестовых воздействий происходит в специальном блоке (формирования тестовых воздействий) путем. многократного циклического исполнения микропрограммы в устройстве микропрограммного управления. Помимо выдачи детерминированных тестов и формирования псевдослучайного кода с заданными вероятностями единиц или нулей в каждом разряде устройства контроля (количество разрядов соответствует количеству выводов объекта), устройство микропрограммного управления позволяет выдавать на объект определенные коды с псевдослучайным, вероятностным характером их появления. 1 з.п, ф-лы, 6 ил. я генерации псевдослучальностей констант.10 20 25 30 35 40 45 зирующих сигналов; на фиг.б - алгоритмработы устройства,Устройство микропрограммного управления (фиг.1) содержит блок 1 памяти микрокоманд, блок 2 выборки микрокомандблок 3 анализа логических условий, регистр4 микрокоманд, дешифратор 5 микрокоманд, буферный регистр 6, формирователь7 синхронизирующих сигналов, тактовыйгенератор 8,делитель 9 частоты, триггер 10,счетчик 11 тактов, элемент ИЛИ 12, первый1.3 и второй 14 мультиплексоры, первый 15и второй 16 генераторы псевдослучайныхкодов,Блок 2 выборки микрокоманд (фиг.2) содержит регистр 17 адреса микрокоманд,мультиплексор 18, счетчик 19 адреса микрокоманд и элемент ИЛИ 20.Блок анализа логических условий 3(фиг,3) содержит (в общем случае) дешифратор 21, блок 22 элементов И и элемент ИЛИ23.Генератор 15 (16) псевдослучайных кодав(фиг.4) выполнен на сдвиговом регистре24 и сумматоре 25 по модулю 2.Формирователь 7 синхронизирующихсигналов (фиг.8) содержит блок 26 элементов задержки и блок 27 элементов И,Блок 1 памяти микрокоманд служит дляхранения микропрограммы, определяющейвсе дейСтвия устройства контроля, связанные с проверкой конкретного блока. Микропрограмма выполняет функции подготовкии выдачи информации для формированиятестового набора в текущем такте проверки,переключения при необходимости каналовустройства контроля, связанных с двунаправленными выводами проверяемого обьекта на прием или передачу данных,сравнения реакции обьекта с эталонной.Эти функции выполняются специальнымиблоками, входящими в состав устройстваконтроля: блоком хранения и генерации тестовых последовательностей, блоком сравнения и пр, Микропрограмма задаетсоответствующие операции в указанныхблоках.Блок 2 выборки микрокоманд служитдля формирования адреса очередной микрокоманды, В регистр 17 адреса микрокоманд через мультиплексор 18 записываетсяинформация или со счетчика 18 (при естественном следовании микрокоманд), или с выходов блока 1 памяти и мультиплексора 14(адрес перехода), или с входов кода операции (начальный адрес микропрограммы),Строб записи на регистр 17 поступает черезэлемент ИЛИ 20 от блока 7 синхронизирующих сигналов (при работе) или от входа начальной установки (при загрузке),Блок 3 анализа логических условий предназначен для анализа логических условий и формирования по результатам этого анализа признака перехода. Кроме того, этот блок вырабатывает сигналы управления первым 13 и вторым 14 мультиплексорами. Регистр 4 микрокоманд принимает из блока 1 памяти микрокоманд информацию, необходимую для формирования тестовой последовательности соответствуюЩими блоками устройства контроля, при этом часть информации на эти блоки поступает непосредственно с регистра 4 микрокоманд, а часть дешифрируется дешифратором 5.Регистр б (для блока памяти тестов) предназначен, в частности, для хранения в текущем такте адреса блока памяти, в котором хранится тестовой набор Формирователь 7 синхронизирующихсигналов формирует сигналы, поступающие на внутренние узлы устройства микропрограммного управления и на остальные блоки,входящие в состав управляемого устройства контроля. Формирователь представляет собой набор элементов 26 задержки, каждый из которых позволяет сдвигать фронт поступающего на вход формирователя сигнала, тем самым определяя временную диаграмму работы; выходы элементов задержки поступают на входы схем И 27, на другие входы которых подается информация с выходов регистра 4 микрокоманд, определяющая блоки, на которые в данном такте должны поступать синхронизирующие сигналы.Тактовый генератор 8 в совокупности с делителем 9 частоты предназначен для формирования тактовых импульсов, следующих с заданной частотой (эта частота, являясь частотой проверки, определяется конкретным типом объекта).Триггер 10 служит для пуска и остановки устройства микропрограммного управления (и, следовательно, устройства контроля в целом), при этом выход триггера сигнализирует о состоянии устройства (работа или останов)Счетчик 11 тактов предназначен для отсчета общей длины тестовой последовательности.Элемент ИЛИ 12 служит для сброса триггера 10 различными сигналами.Мультиплексор 13 предназначен для динамической модификации адреса блока памяти тестов (часть адреса заменена псевдослучайным кодом).Мультиплексор 14 аналогично модифицирует адрес блока 1 памяти микрокоманд,Псевдослучайныйкод поступает на входы мультиплексоров 13 и 14 с генераторов псевдослучайных кодов 15 и 16 соответственно,Устройство микропрограммного управления работает следующим образом.Перед началом работы производится загрузка микропрограммы в блок 1 памяти микрокоманд, при этом для задания адресов блока 1 памяти используется регистр 17 блока 2 выборки, затем в регистр 17 загружается начальный адрес микропрограммы, в делитель 9 частоты - коэффициент деления частоты тактового генератора 8 а в счетчик 11 тактов - общая длина в тактах тестовой последовательности. По завершении ввода устанавливается триггер 10, который разрешает работу тактового генератора 8. В процессе работы происходит выборка микрокоманд из блока 1 памяти, прочитанная информация поступает нэ блоки 2-4, 6, 13 и 14, определяя порядок работы самого устройства управления и устройства контроля в целом. В счетчике 19 в это время формируется адрес следующей микрокоманды, который передается через мультиплексор 18 в регистр 17, при выполнении переходов новое значение адреса в регистре 17 формируется путем передачи в него адреса перехода из блока 1 памяти. В каждом такте происходит уменьшение на единицу содержимого счетчика 11 тактови по достижении им нулевого значения, т.е, по окончании формирования тестовой последовательности заданной длины, счетчик 11 выдает сигнал, который через элемент ИЛИ 12 сбрасывает триггер 10, который, в свою очередь, блокирует тактовый генератор 8 и, следовательно, останавливает устройство управления (и устройство контроля в целом). Сброс триггера 10 возможен до окончания формирования всей последовательности внешним сигналом через элемент ИЛИ 12,Собственно генерация тестовых воздействий происходит в специальном блоке (формирования тестовых воздействий) путем многократного циклического исполнения микропрограммы в устройстве микропрограммного управления. Помимо выдачи детерминированных тестов и формирования псевдослучайного кода с заданными вероятностями единиц или нулей в каждом разряде устройства контроля (количество разрядов соответствует количеству выводов объекта), устройство микропрограммного управления позволяет выдавать на объект определенные коды с псевдослучайным, вероятностным характером их по-. явления. Для этого каждый из кодов25 дов,30 35 45 деляет величину зон блока памяти микрокоманд, в которых записаны фрагменты. При 50 микрокомэнд можно управлять заданием вероятности появления каждого фрагмента,.Микропрограмма в этом случае представляет собой совокупность рабочих подпрог рамм (выдачи на объект воздействий,. анализа реакций и т.п.) и подготовительнойчаста(устанавливающей объект в некоторое состояние, анализирующей состояние объекта и т.п,), оканчивающейся командой перехода по модифицированному 5 10 15 20 записывается в ячейки блока памяти тестов (из состава блока формирования тестовыхвоздействий), причем для каждого иэ кодов выбрано определенное число ячеек блока памяти (в которые записывается один и тот же код), Это позволяет при равновероятном переборе адресов блока памяти тестов считывать из него коды с заданной для каждого из них частотой. Равновероятный перебор обеспечивается заменой части адреса блока памяти тестов, формируемого в регистре 6,псевдослучайным кодом, поступающим с выходов генератора 15 псевдослучайных кодов через мультиплексор 13. При этом фиксированная часть адреса, поступающая с выходов блока 1 памяти микрокоманд, определяет область блока памяти тестов, в которой записаны соответствующие коды. Частота появления кодов соответствует заданному распределению этих кодов в ячейках блока памяти тестов, При получении достаточно длинной последовательности за счет соответствующего заполнения ячеек блока памяти тестов можно управлять заданием вероятности появления каждого из коАналогичным образом можно модифицировать адрес перехода к следующей микрокоманде. В этом случае часть адреса перехода, поступающего с выходов блока 1 памяти микрокомэнд и фиксируемого в регистре 17 блока 2 выборки, заменяется псевдослучайным кодом, поступающим с выходов генератора 16 лсевдослучайных кодов через мультиплексор 14. Это дает возможность осуществлять переход к следующей микрокоманде по модифицированному псевдослучайным кодом адресу, что, в свою очередь, дает возможность подавать на объект тестовые последовательности с псевдослучайным, вероятностным характером появления каждой последовательности (фрагмента микропрограммы).При этом фиксированная часть адреса опре-; получении достаточно длинной общей последовательности за счет соответствующего заполнения зон блока памяти1, Устройство микропрограммного управления, содержащее блок памяти микро- команд, блОк выборки микрокоманд, блок анализа логических условий, регистр микфокоманд, дешифратор микрокоманд, буфернцй регистр, формирователь (,инхронизирующих сигналов, тактовый геИератор, делитель частоты, триггер, счетчик тактов и элемент ИЛИ, причем вход кода операции устройства соединен с первым йнформационным входом блока выборки 50 псевдослучайным кодом адресу. Во времяработы по окончании подготовительной части происходит переход на некоторую рабочуЮ подпрограмму, которая оканчиваетсякомандой безусловного перехода на команду перехода по модифицированному адресу(или на подготовительную часть), затем и роисходитпереход на другую подпрограмму и,т.д. Зто может применяться при проверке,например, микропроцессоров. При этом 10(каждая подпрограмма эмулирует некоторую команду микропроцессора и, аким об, разом, кроме отработки микропроцессоромкаждой отдельной команды, происходит общая проверка работы микропроцессора в 15,условиях, имитирующих реальные условияего работы (в части произвольного следования команд)Управление модификацией адресовосуществляется в блоке 3 логических условии. Микропрограмма содержит бит разрещения модификации адреса блока памятитестов, который поступает с вью.ода блока 1памяти микрокоманд на вход элемента И 22блока 3. Один из кодов, соответствующих 25разным типам переходов, означает переход,по модифицированному адресу. Сигнал сссоответствующего выхода дешифратора 21,йа вход которого подаются эти коды (типов,переходов), поступает на соответствующий 30лемент И 22 блока 3, На вторые входыЬлемента И 22 поступают различные услоия, по которым необходимо осуществлятьоответствующие операции (эти условия потупают с других блоков устройства контроя), для безусловного выполнения на входоответствующего элемента И 22 необходио задать уровень логической единицы.Для выдачи на объект тестовых последоательностей (фрагментов микропрограмМы) с псевдослучайным характеромоявления этих последовательностей про"отипу необходим большой объем памятиля размещения всех возможных сочетанийФтих последовательностей, при ограниченйом Объеме памяти резко возрастает время контроля за счет необходимости перегрузки информации (новых сочетаний) в память.Формула изрбретения микрокоманд, информационным входом блока памяти микрокоманд, входом задания коэффициента деления делителя частоты и информационным входом счетчика тактов, первый вход начальной установки устройства соединен с управляющим входом блока выборки микрокоманд, с второго по седьмой входы начальной установки устройства соединены соответственно с входами выборки и чтения-записи блока памяти микро- команд, входом записи .делителя частоты, входом записи счетчика тактов, входом установки в "1" триггера и первым входом элемента ИЛИ, выход которого соединен с входом установки в "0" триггера, выход которого является выходом индикации работы устройства и соединен с входом запуска тактового генератора, выход которого соединен со счетным входом делителя частоты, выход которого соединен с входом синхронизации формирователя синхрониэи рующих сигналов, с первого по седьмой выходы которого соответственно соединены с первого по третий входами синхронизации блока выборки микрокоманд входами синхронизации блока анализа логических условий, регистра микрокоманд, буферного регистра и счетчика тактов, выход переноса которого соединен с вторым входом элемента ИЛИ, остальные выходы формирователя синхронизирующих сигналов являются, группой стробирующих выходов устройства, выход поля управления синхронизацией регистра микрокоманд соединен с входом режима работы формирователя синхронизирующих сигналов, выход первого поля микроопераций регистра микроопераций соединен с выходом ми,роопераций уст; ройства, выход второго поля микроопераций регистра микроксманд соединен с информационным входсм дешифратора микрокоманд, выход котсрого является выходом операций устройства информационный вход регистра микрокоманд соединен с выходом поля микроопераций блока памяти микрокоманд, выход первого поля константы которого соединен с первым информационным входом буферного регистра, выход которого является информационным выходом устройства, выход поля логических условий блока памяти микрокоманд соединен с управляющим входом блока анализа логических условий. информационный вход которого соединен с входом логических условий устройства, первый выход блока анализа логических условий соединен с входом логического условия блока выборки микрокоманд, второй информационный вход которого соединен с выходом поля адреса блока памяти микрокоманд,"1667070 10 НОПИ вход адреса которого соединен с выходом блока выборки микрокоманд, о т л и ч а ющ е е с я тем, что, с целью расширения области применения путем обеспечения генерации псевдослучайных последовательностей констант, в него введены первый и второй мультиплексоры, первый и второй генераторы псевдослучайных кодов, причем второй информационный вход буферного регистра соединен с выходом первого мультиплексора, первый информационный вход которого соединен с выходом второго поля константы блока памяти микрокоманд, выход третьего поля константы которого соединен с первым информационным входом второго мультиплексора, выход которого соединен с третьим информационным входом блока выборки микрокоманд, управляющий вход второго мультиплексора соединен с вторым выходом блока анализа логических условий, третий выход которого соединен с управляющим входом первого мультиплексора, второй информацион н ый вход которого соединенс выходом первого генератора псевдослучайных кодов, вход синхронизации которого подключен к восьмому выходу формирователя синхронизирующих сигналов, к девятому выходу которого подключен вход синхронизации второго генератора псевдослучайных кодов, выход которого соединен с вторым информационным входом второго мультиплексора. 2, Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок выборки микрокоманд содержит регистр адреса микрокоманд, мультиплексор, счетчик и элемент ИЛИ, причем 5 первый информационный вход блока соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с информационным выходом счетчика, информационный вход 10 которого соединен с выходом регистра адреса микрокоманд и с выходом блока, информационный вход регистра адреса микрокоманд соединен с выходом мультиплексора. старшие разряды третьего инфор мационного входа которого образуютвторой информационный вход блока . третий информационный вход блока соединен с младшими разрядами третьего информационного входа мультиплексора, первый уп равляющий вход которого соединен спервым управляющим входом блока, второй управляющий вход мультиплексора соединен с входом логического условия блока, второй управляющий вход которого соеди нен с первым входом элемента ИЛИ,. выходкоторого соединен с входом записи регистра адреса микрокоманд, второй вход элемента ИЛИ соединен с первым входом синхронизации блока, второй и третий вхо ды синхронизации которого соединены свходами записи и счета счетчика.1667070 рсс крокою Падпрограииа 1 дпрораина Н част часть Редактор А, Лежнин пле екто аказ 2525 Тираж 405 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 оставитель А. Сошинехред М.Моргентал начаяьная пространна

СмотретьЗаявка

4643240, 26.12.1988

КИЕВСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ И КОНСТРУКТОРСКИЙ ИНСТИТУТ ПЕРИФЕРИЙНОГО ОБОРУДОВАНИЯ

КАДАНСКИЙ АЛЕКСАНДР АБРАМОВИЧ, КОРОЛЕВ ВЛАДИМИР НИКОЛАЕВИЧ, РУККАС ОЛЕГ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/7-1667070-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство управления обращениями

Случайный патент: Устройство для измерения углов отклонения поверхностей от вертикали