Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1649540

Автор: Текутова

Текст

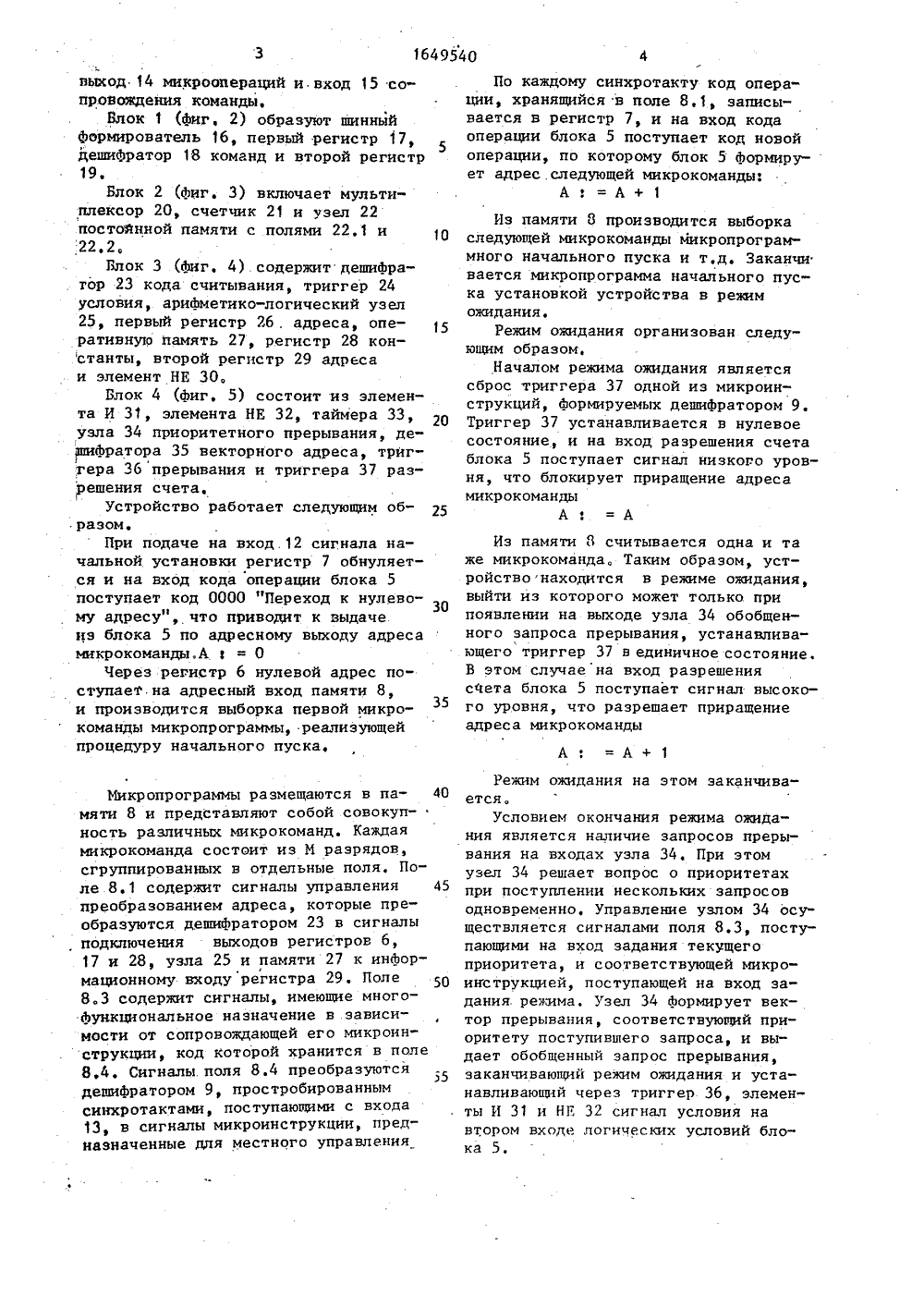

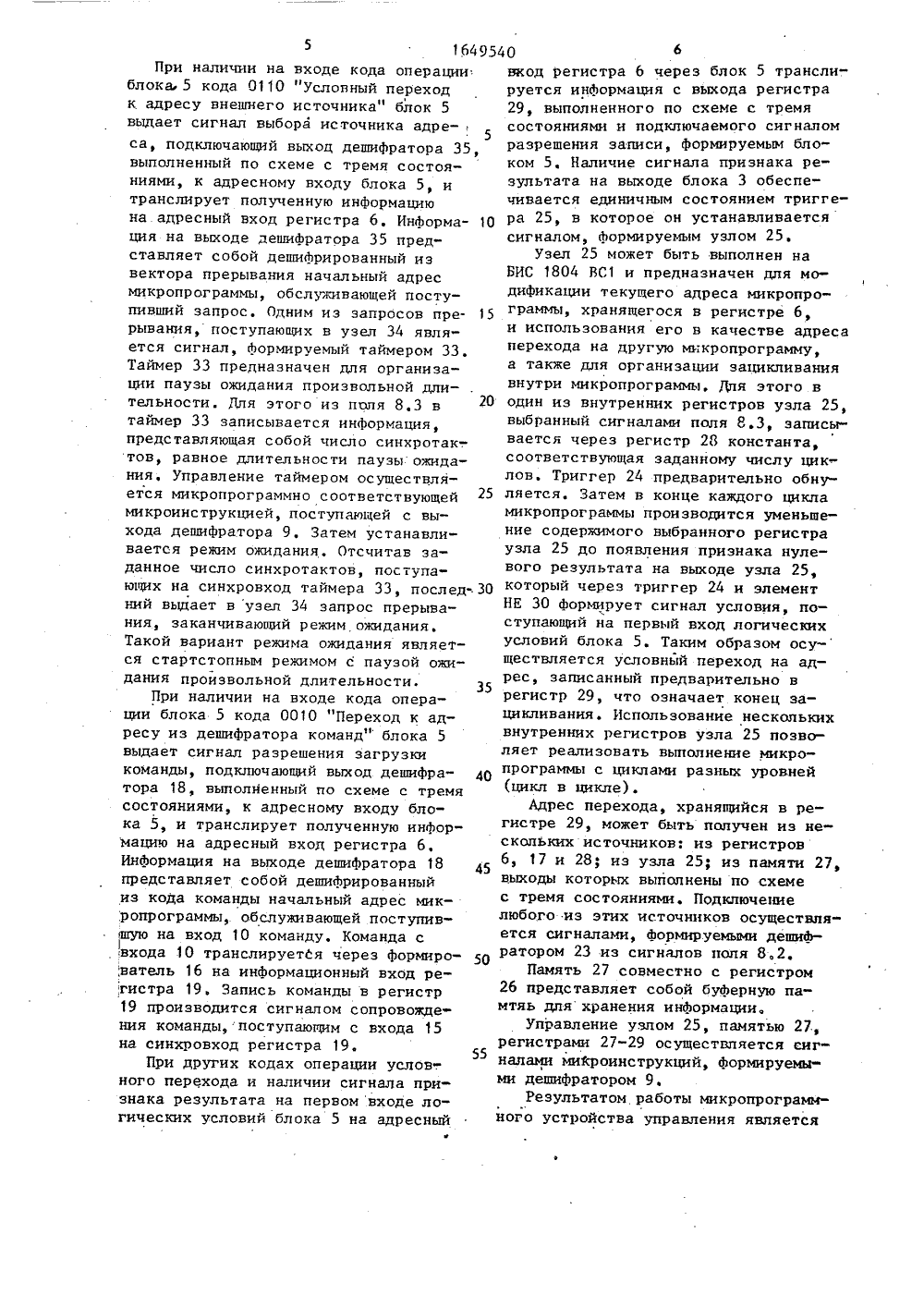

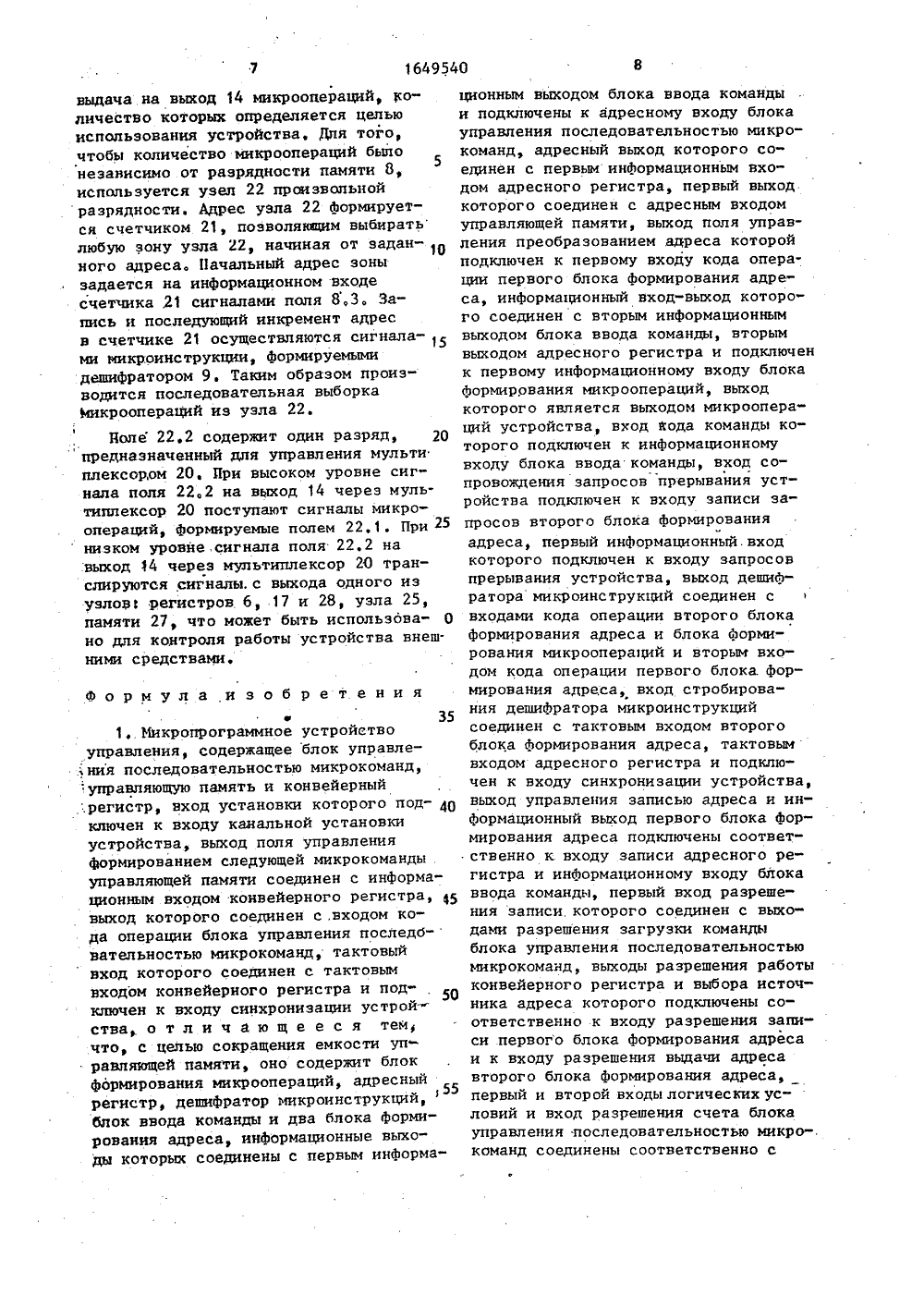

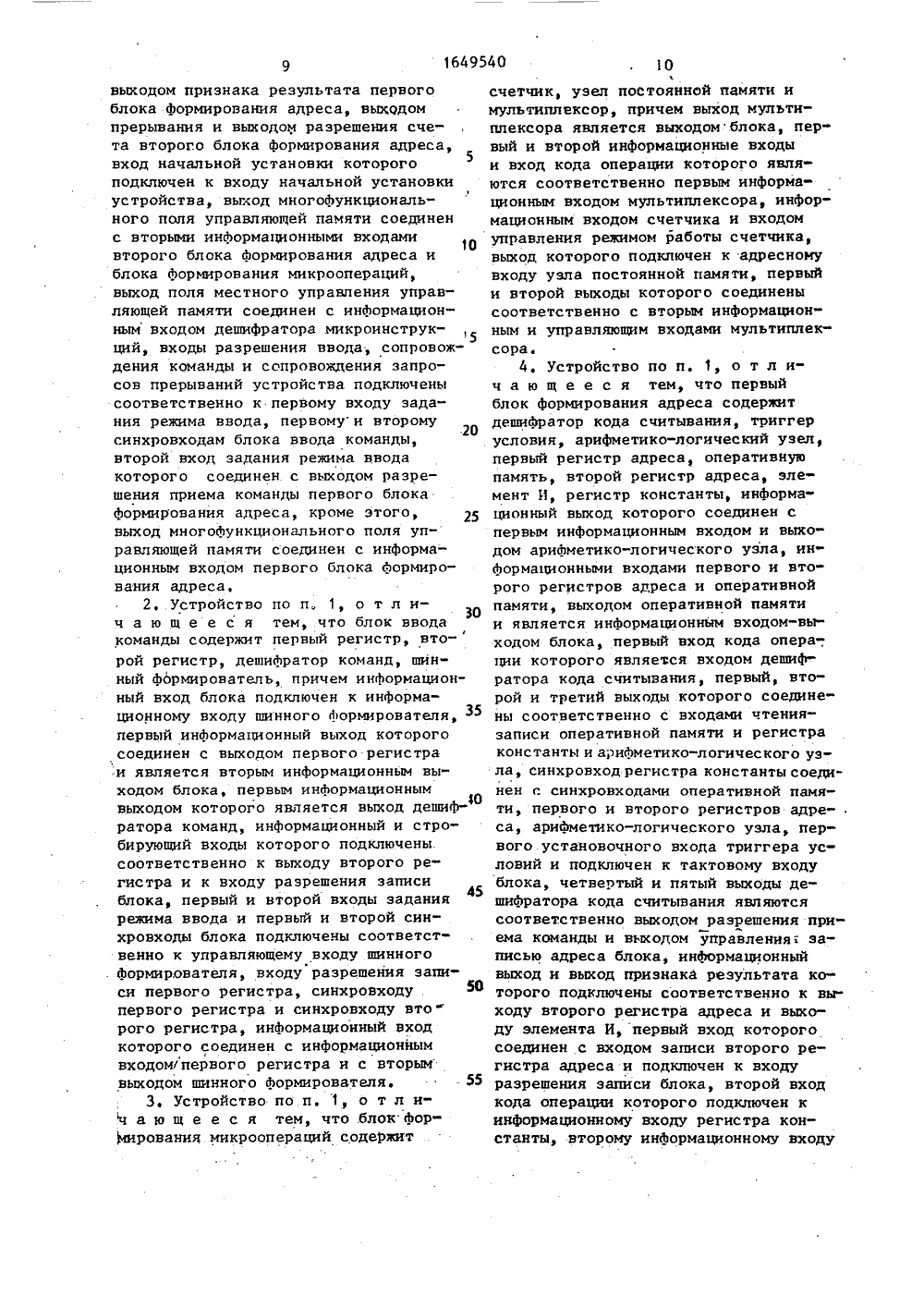

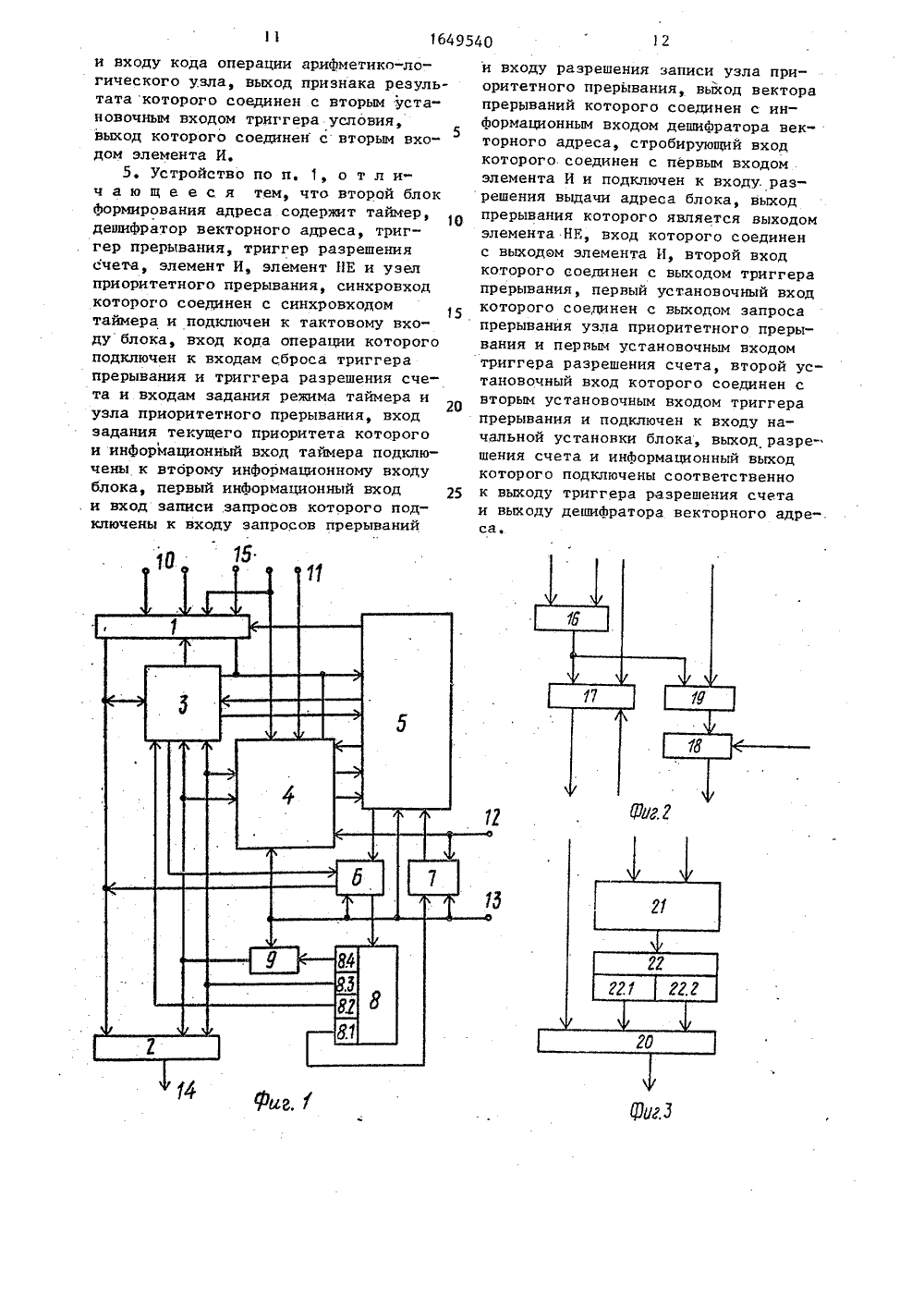

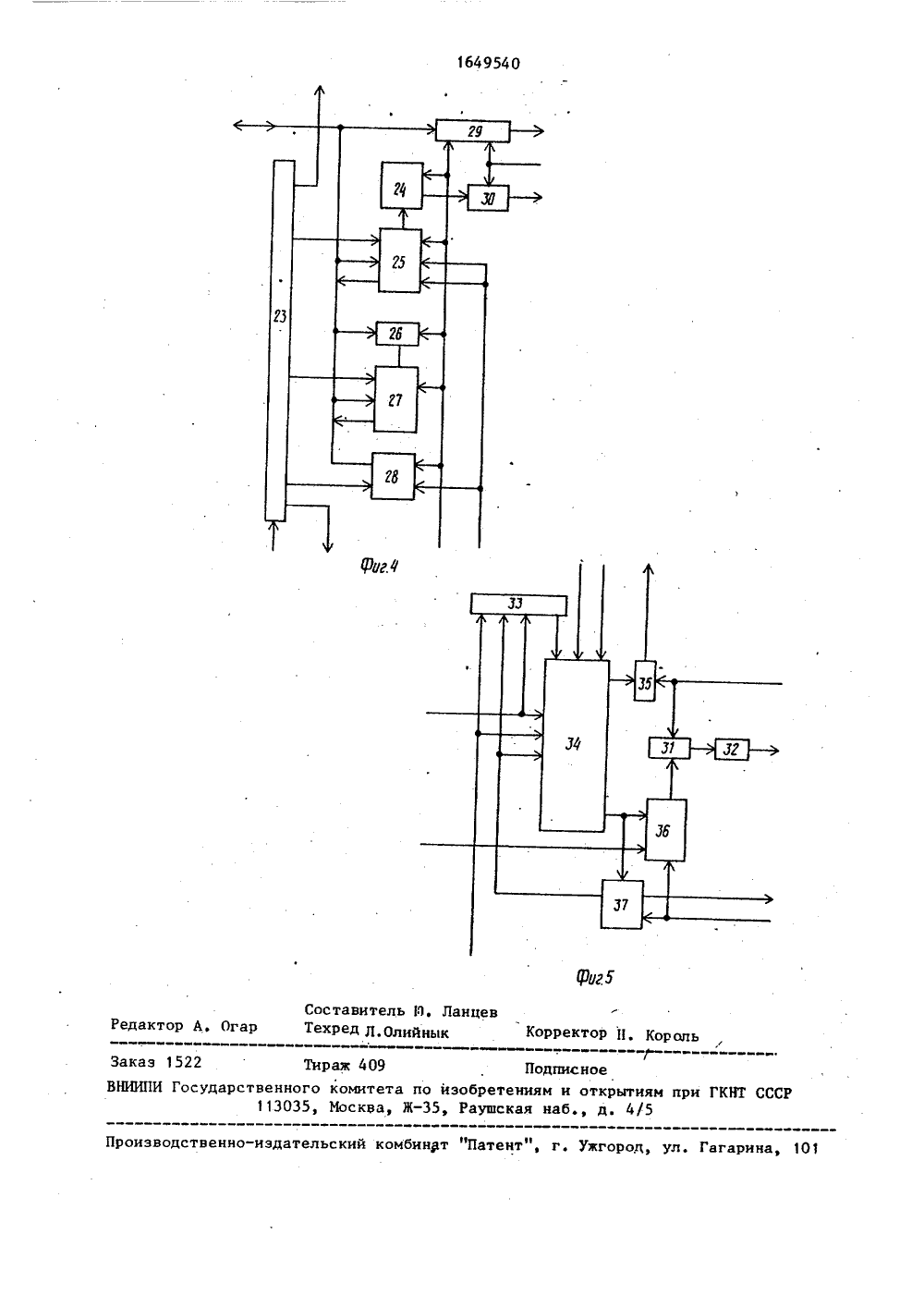

СОЮЗ СОВЕТСКИХсандаюнвжРЕСПУБЛИК 51)5 С 06 Р 9/22 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМОПИСАНИЕ ИЗОБРЕТЕН Р 18 етельство СССР Г 9/22, 1985.ектирование микроств с разрядно-мой. И.: Мир, 1984,ОЙСТ х окращение АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54) ИИКРОПРОГРШМНОН УСТР ВО УПЛЕНИЯ(57) Изобретение относится к цифровычислительной технике, в частностк микропрограммным устройствам упрления, и может быть использовано ивычислительных системах, устройствсвязи, контрольно-измерительных приборах, системах управления внешними Изобретение относится к цифровой вычислительной технике, в частности к микропрограммным устройствам управления, и может быть использовано в вычислительных системах, устройствах связи, контрольно-измерительных приборах, системах управления. внешними устройствами и в процессорах специального назначения,Цель изобретения - с емкости управляющей памяти.На фиг. 1-5 представлены соответственно структурные схемы микропрограм много устройства управления, блока ввода команды, блока формнрования ф,ЯО И ОЦ 9 0 А 1 устройствами и в процессорах специального назначения. Целью изобретенияявляется сокращение емкости управля-ющей памяти. Устройство содержит блок1 ввода команды, блок 2 формированиямикроопераций, первый и второй блоки3, 4 формирования адреса, блок 5 управления последовательностью. микрокоманд, адресный регистр 6, конвейерный регистр 7, управляющую память 8и дешифратор 9 микроинструкций. Цельдостигается особой организацией полей управляющей памяти, что позволяет уменьшить ее разрядность, а такжеиспользованием возможности работатьбез приращения адреса микрокоманды,т.е. обеспечивать выполнение одной Еи той же микрокоманды любое количество раз, что упрощает микропрограммноеобеспечение по обслуживанию запросовпрерывания, 4 з.п.ф-лы. 5 ил. микроопераций, первого и второго блоков формирования адреса.Микропрограммное устройство управления (фиг. 1) содержит блок 1 ввода команды, блок 2 формирования микро- операций, первый и второй блоки 3 и 4 формирования адреса, блок 5 управления последовательностью микрокоманд, ф выполненный на БИС 1804 ВУ 4, адресный регистр 6, конвейерный регистр 7, фф фф управляющую память 8 с выходами полей 81-8.4дешифратор 9 микроинструкций, вход 10 кода команды, вход 11апросов прерываний, вход 12 начальой установки, вход 13 синхронизации,1649540 4По каждому синхротакту код операции, хранящийся в поле 8,1, записывается в регистр 7, и на вход кода5операции блока 5 поступает код новойоперации, по которому блок 5 Формиру-ет адрес следующей микрокоманды:А= А + 1 3 А ; = А + 1 выход 14 микроопераций и вход 15 сопроВождения команды.Блок 1 (фиг, 2) образуют шинныйФормирователь 16, первый регистр 17,дешифратор 18 команд и второй регист19.Блок 2 (Фиг. 3) включает мультиплексор 20, счетчик 21 и узел 22постоянной памяти с полями 22.1 и22,2,Блок 3 (Фиг. 4) содержит дешифра. тор 23 кода считывания, триггер 24условия, арифметико-логический узел25, первый регистр 26 . адреса, оперативную память 27, регистр 28 константы, второй регистр 29 адресаи элемент НЕ 30,Блок 4 (Фиг, 5) состоит из элемента И 31, элемента НЕ 32, таймера 33,узла 34 приоритетного прерывания, де 1 шифратора 35 векторного адреса, триггера 36 прерывания и триггера 37 разрешения счета.Устройство работает следуюшнм образом.При подаче на вход.32 сигнала начальной установки регистр 7 обнуляется и на вход кода операции блока 5поступает код 0000 "Переход к нулево 30му адресу", что приводит к выдачеиэ блока 5 по адресному выходу адресамикрокомаиды.А= 0Через регистр 6 нулевой адрес поступает на адресный вход памяти 8,и производится выборка первой микро 35команды микропрограммы, реализующейпроцедуру начального пуска,Из памяти 8 производится выборка следующей микрокоманды микропрограммного начального пуска и т,д. Заканчи вается микропрограмма начального пуска установкой устройства в режим ожидания.Режим ожидания организован следующим образом.Началом режима ожидания является сброс триггера 37 одной из микроинструкций, Формируемых дешифратором 9. Триггер 37 устанавливается в нулевое состояние, и на вход разрешения счета блока 5 поступает сигнал низкого уровня, что блокирует приращение адреса микрокомандыА 3 = А Из памяти 8 считывается одна и та же микрокоманда. Таким образом, устройство находится в режиме ожидания, выйти из которого может только при появлении на выходе узла 34 обобщенного запроса прерывания, устанавливающего триггер 37 в единичное состояние. В этом случае на вход разрешения счета блока 5 поступает сигнал высокого уровня, что разрешает приращение адреса микрокомандыМикропрограммы размещаются в па мяти 8 и представляют собой совокупность различных микрокоманд. Каждая микрокоманда состоит из М разрядов, сгруппированных в отдельные поля. Поле 8.1 содержит сигналы управления 45 преобразованием адреса, которые преобразуются дешифратором 23 в сигналы подключения выходов регистров 6, 17 и 28, узла 25 и памяти 27 к информационному входу регистра 29. Поле 8.3 содержит сигналы, имеющие многоФункциональное назначение в зависимости от сопровождающей его микроинструкцни, код которой хранится в поле 8.4, Сигналы. поля 8.4 преобразуются дешифратором 9, простробированным синхротактами, поступающими с входа 13 в сигналы микроинструкции, предВназначенные для местного управления Режим ожидания на этом заканчивается.Условием окончания режима ожидания является наличие запросов прерывания на входах узла 34. При этом узел 34 решает вопрос о приоритетах при поступлении нескольких запросов одновременно. Управление узлом 34 осу" ществляется сигналами поля 8.3, поступающими на вход задания текущего приоритета, и соответствующей микро- инструкцией, поступающей на вход задания режима, Узел 34 Формирует вектор прерывания, соответствующий приоритету поступившего запроса, и выдает обобщенный запрос прерывания, заканчивающий режим ожидания и устанавливающий через триггер 36, элементы И 31 и НГ 32 сигнал условия на втором входе логических условий блока 5.5 164При наличии на входе кода операции: блока 5 кода 0110 "Условный переход к адресу внешнего источника" блок 5 выдает сигнал выбора источника адре-: са, подключающий выход дешнфратора 35 выполненный по схеме с тремя состояниями, к адресному входу блока 5, и транслирует полученную информацию на адресный вход регистра 6. Информация на выходе дешифратора 35 представляет собой дешифрированный из вектора прерывания начальный адрес микропрограммы, обслтивающей поступивший запрос. Одним из запросов прерывания,поступающих в узел 34 является сигнал, Формируемый таймером 33, Таймер 33 предназначен для организации паузы ожидания произвольной длительности. Для этого из поля 8,3 в таймер 33 записывается информация, представляющая собой число синхротак-. тов, равное длительности паузы: ожидания, Управление таймером осуществляется микропрограммно соответствующей микроинструкцией, поступающей с выхода дешифратора 9, Затем устанавливается режим ожидания. Отсчитав заданное число синхротактов, поступающих на синхровход таймера 33, послед ний выдает в узел 34 запрос прерывания, заканчивающий режим ожидания. Такой вариант режима ожидания является стартстопным режимом с паузой ожидания произвольной длительности.При наличии на входе кода операции блока 5 кода 0010 "Переход к адресу из дешифратора команд" блока 5 выдает сигнал разрешения загрузки команды, подключающий выход дешифратора 18, выполненный по схеме с тремя состояниями, к адресному входу блока 5, и транслирует полученную информацию на адресный вход регистра 6, Информация на выходе дешифратора 18 представляет собой дешифрированный из коДа команды начальный адрес микропрограммы, обслуживающей поступивна вход 10 команду. Команда с входа 10 транслируетСя через Формиро,ватель 16 на информационный вход ре;гистра 19. Запись команды в регистр 19 производится сигналом сопровождения команды,поступающим с входа 15 на синхровход регистра 19.При других кодах операции услов-. ного перехода и наличии сигнала признака результата на первом входе логических условий блока 5 на адресный 95406 вкод Регистра Ь через блок 5 транслируется информация с выхода регистра29, выполненного по схеме с тремясостояниями и подключаемого сигналом5разрешения записи, формируемым блоком 5. Наличие сигнала признака результата на выходе блока 3 обеспечивается единичным состоянием тригге 10 ра 25 в которое он устанавливаетсяВсигналом, Формируемым узлом 25,Узел 25 может быть выполнен наБИС 1804 ВС 1 и предназначен для модификации текущего адреса микропрограммы, хранящегося в регистре 6,и использования его в качестве адресаперехода на другую микропрограмму,а также для организации зацикливаниявнутри микропрограммы, Для этого в20 один из внутренних регистров узла 25,выбранный сигналами поля 8.3, записывается через регистр 28 константа,соответствующая заданному числу циклов. Триггер 24 предварительно обну 25 ляется. Затем в конце каждого цикламикропрограммы производится уменьшение содержимого выбранного регистраузла 25 до появления признака нулевого результата на выходе узла 25,который через триггер 24 и элементНЕ 30 формирует сигнал условия, поступающий на первый вход логическихусловий блока 5. Таким образом осу-ществляется условный переход на адрес, записанный предварительно врегистр 29, что означает конец зацикливания. Использование несколькихвнутренних регистров узла 25 позволяет реализовать выполнение микро 40 программы с циклами Разных уровней(цикл в цикле).Адрес перехода, хранящийся в регистре 29, может быть папучен из нескольких источников: из регистров456, 17 и 28; из узла 25; из памяти 27,выходы которых выполнены по схемес тремя состояниями. Подключениелюбого из этих источников осуществляется сигналами, Формируемыми дешифратором 23 из сигналов поля 8.2.Память 27 совместно с регистром26 представляет собой буферную памтяь для хранения информации,Управление узлом 25, памятью 27,регистрами 27-29 осуществляется сиг 55 налами мийроинструкций, формируемыми дешифратором 9.Результатом работы микропрограммного устройства управления является1649540 7выдача на выход 14 микроопераций, количество которых определяется цельюиспользования устройства, Для того,чтобы количество микроопераций бионезависимо от разрядности памяти 8,используется узел 22 произвольнойразрядности. Адрес узла 22 формируется счетчиком 21, позволякщим выбиратьлюбую зону узла 22, начиная от заданного адреса. Начальный адрес зонызадается на информационном входесчетчика 21 сигналами поля 8,3. Запись и последующий инкремент адресв счетчике 21 осуществляются сигналами иикроинструкции, формируемымидешифратором 9. Таким образом производится последовательная выборкаИикроопераций из узла 22.Ноле 22,2 содержит один разряд, 20предназначенный для управления мультиплексором 20, Нри высоком уровне сигнала поля 22,2 иа выход 14 через мультиплексор 20 поступают сигналы микроопераций, Формируемые полем 22,1. При 25низком уровне, сигнала поля 22.2 на:выход 34 через мультиплексор 20 транслируются сигналы, с выхода одного изузлов регистров. 6, 17 и 28, узла 25,памяти 27, что может быть использовано для контроля работы устройства внеш.ними средствами,Формула изобретения 351, Микропрограммное устройство управления, содержащее блок управле.ния последовательностью микрокоманд, управляющую память и конвейерный .регистр, вход установки которого под ключен к входу канальной установки устройства, выход поля управления формированием следующей микрокоманды управляющей памяти соединен с информационным входом конвейерного регистра, выход которого соединен с,входом кода операции блока управления последб-Вательностью микрокоманд, тактовый вход которого соединен с тактовым входом конвейерного регистра и подключен к входу синхронизации устрой ства, о т л и ч а ю щ е е с я тем, что, с целью сокращения емкости управляющей памяти, оно содержит блок формирования микроопераций, адресный регистр, дешифратор микроинструкций,,55 блок ввода команды и два блока Формирования адреса, информационные выходы которых соединены с первым информационным выходом блока ввода команды и подключены к адресному входу блока управления последовательностью микро- команд, адресный выход которого соединен с первым информационным входом адресного регистра, первый выход которого соединен с адресным входом управляющей памяти, выход поля управления преобразованием адреса которой подключен к первому входу кода операции первого блока формирования адреса, информационный вход-выход которого соединен с вторым информационным выходом блока ввода команды, вторым выходом адресного регистра и подключен к первому информационному входу блока формирования микроопераций, выход которого является выходом микрооперацнй устройства, вход йода команды которого подключен к информационному входу блока ввода команды, вход сопровождения запросов прерывания устройства подключен к входу записи запросов второго блока формирования адреса, первый информационный. вход которого подключен к входу запросов прерывания устройства, выход дешифратора микроинструкцнй соединен с входами кода операции второго блока формирования адреса и блока Формирования микроопераций и вторым входом кода операции первого блока формирования адреса, вход стробирования дешифратора микроинструкций соединен с тактовым входом второго блока формирования адреса, тактовымвходом адресного регистра и подключен к входу синхронизации устройства, выход управления записью адреса и информационный выход первого блока Формирования адреса подключены соответственно к. входу записи адресного регистра и информационному входу блока ввода команды, первый вход разрешения записи. которого соединен с выходами разрешения загрузки команды блока управления последовательностью микрокоманд, выходы разрешения работы конвейерного регистра и выбора источника адреса которого подключены соответственно к входу разрешения записи первого блока Формирования адреса и к входу разрешения выдачи адреса второго блока формирования адреса, первый и второй входы логических условий и вход разрешения счета блока управления последовательностью микро-. команд соединены соответственно свыходом признака результата первого блока формирования адреса, выхадом прерывания и выходом разрешения счета второго блока формирования адреса, вход начальной установки которого подключен к входу начальной установки1 устройства, выход многофункционального поля управляющей памяти соединен с вторыми информационными входами второго блока формирования адреса и блока формирования микроопераций, выход поля местного управления управляющей памяти соединен с информационным входом дешифратора микроинструк 5 ций, входы разрешения ввода, сопровождения команды и сопровождения запросов прерываний устройства подключены соответственно к первому входу задания режима ввода, первому и второму синхровходам блока ввода команды, второй вход задания режима ввода которого соединен с выходом разрешения приема команды первого блока формирования адреса, кроме этого, выход многофункционального поля управляющей памяти соединен с информационным входом первого блока формирования адреса.2. Устройство по и., 1, о т л ич а ю щ е е с я тем, что блок ввода команды содержит первый регистр, вто-рой регистр, дешифратор команд, шинный фЬрмирователь, причем информационный вход блока подключен к информационному входу шинного формирователя, З 5 первый информационный выход которого соединен с выходом первого регистра и является вторым информационным выходом блока, первым информационным0 выходом которого является выход дешифратора команд, информационный и стробирующий входы которого подключены соответственно к выходу второго регистра и к входу разрешения записи блока, первый и второй входы задания45 режима ввода и первый и второй синхровходы блока подключены соответственно к управляющему входу шинного формирователя, входу разрешения записи первого регистра, синхровходу 5 О первого регистра и синхровходу второго регистра, информационный вход которого соединен с информационным входом/первого регистра и с вторым выходом шинного формирователя. 553. Устройство по п. 1, о т л ич а ю щ е е с я тем, что .блок форкиравания микроопераций содеРжит 1649540 1 Осчетчик, узел постоянной памяти имультиплексор, причем выход мультиплексора является выходом блока, первый и второй информационные входыи вход кода операции которого являются соответственно первым информационным входом мультиплексора, информационным входом счетчика и входомуправления режимом работы счетчика,выход которого подключен к адресномувходу узла постоянной памяти, первыйи второй выходы которого соединенысоответственно с вторым информационным и управляющим входами мультиплексора.4. Устройство по п. 1, о т л ич а ю щ е е с я тем, что первыйблок формирования адреса содержитдешифратор кода считывания, триггерусловия, арифметико-логический узел,первый регистр адреса, оперативнуюпамять, второй регистр адреса, элемент И, регистр константы, информационный выход которого соединен спервым информационным входом и выходом арифметико-логического узла, информационными входами первого и второго регистров адреса и оперативнойпамяти, выходом оперативной памятии является информационным входом-выходом блока, первый вход кода операции которого является входом дешифратора кода считывания, первый, второй и третий выходы которого соединены соответственно с входами чтениязаписи оперативной памяти и регистраконстанты и арифметико-логического узла, синхровход регистра константы соединен с синхровходами оперативной памяти, первого и второго регистров адреса, арифметико-логического узла, первого установочного входа триггера условий и подкпючен к тактовому входублока, четвертый и пятый выходы дешифратора кода считывания являютсясоответственно выходом разрешения приема команды и выходом управления. -записью адреса блока, информационныйвыход и выход признака результата которого подключены соответственно к вы"ходу второго регистра адреса и выходу элемента И, первый вход которогосоединен с входом записи второго регистра адреса и подключен к входуразрешения запйси блока, второй входкода операции которого подключен кинформационному входу регистра константы, второму информационному входуи входу кода операции арифметико-логического узла, выход признака результата которого соединен с вторым установочным входом триггера условия, выход которого соединен с вторым вхо 5 дом элемента И.5Устройство по и. 1, о т л ич а ю щ е е с. я тем, что второй блок Формирования адреса содержит таймерО дешифратор векторного адреса, триггер прерывания, триггер разрешения счега, элемент И, элемент ИЕ и узел приоритетного прерывания, синхровход которого соединен с синхровходом таймера и подключен к тактовому входу блока, вход кода операции которого подключен к входам сброса триггера прерывания и триггера разрешения счета и входам задания режима таймера и20 узла приоритетного прерывания, вход задания текущего приоритета которого и информационный вход таймера подключены к втброму информационному входу блока, первый информационный вход и вход записи запросов которого подключены к входу запросов прерываний и входу разрешения записи узла приоритетного прерывания, выход векторапрерываний которого соединен с информационным входом дешифратора векторного адреса, стробирующий входкоторого. соединен с первым входомэлемента И и подключен к входу. разрешения выдачи адреса блока, выходпрерывания которого является выходомэлемента НЕ, вход которого соединенс выходом элемента И, второй входкоторого соединен с выходом триггерапрерывания, первый установочный входкоторого соединен с выходом запросапрерывания узла приоритетного прерывания и первым установочным входомтриггера разрешения счета, второй установочный вход которого соединен свторым установочным входом триггерапрерывания и подключен к входу начальной установки блока, выход разрешения счета и информационный выходкоторого подключены соответственнок выходу триггера разрешения счетаи выходу дешифратора векторного адре-.са.-,1 едактор А. Ог Тираж 40 одписное твенного комитет 113035, Москва,и ГКНТ СССР п омбинат "Патент", г. Ужгород, ул. Гага Производственно-иэдательск Заказ 1522ВНИИПИ Госуд изобретениям и открыт Раушская наб., д.

СмотретьЗаявка

4499691, 28.10.1988

ПРЕДПРИЯТИЕ ПЯ В-2962

ТЕКУТОВА АНТОНИНА МИХАЙЛОВНА

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 15.05.1991

Код ссылки

<a href="https://patents.su/7-1649540-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство микропрограммного управления

Следующий патент: Многоканальное устройство для обслуживания групповых запросов

Случайный патент: Устройство для затяжки резьбовых шпилек фланцевых соединений