Формирователь линейно-частотно-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1584070

Авторы: Банковский, Иванов, Работаев

Текст

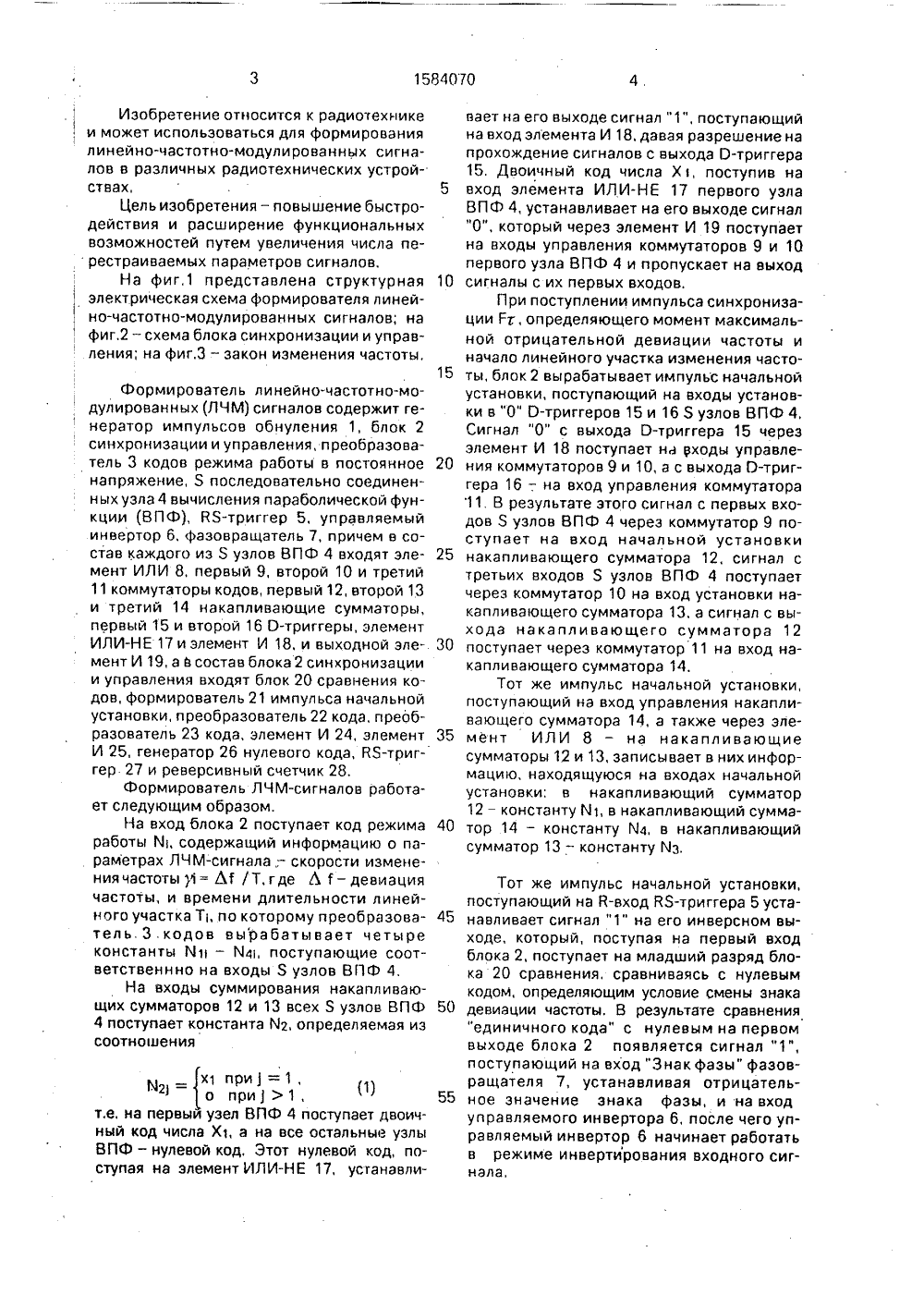

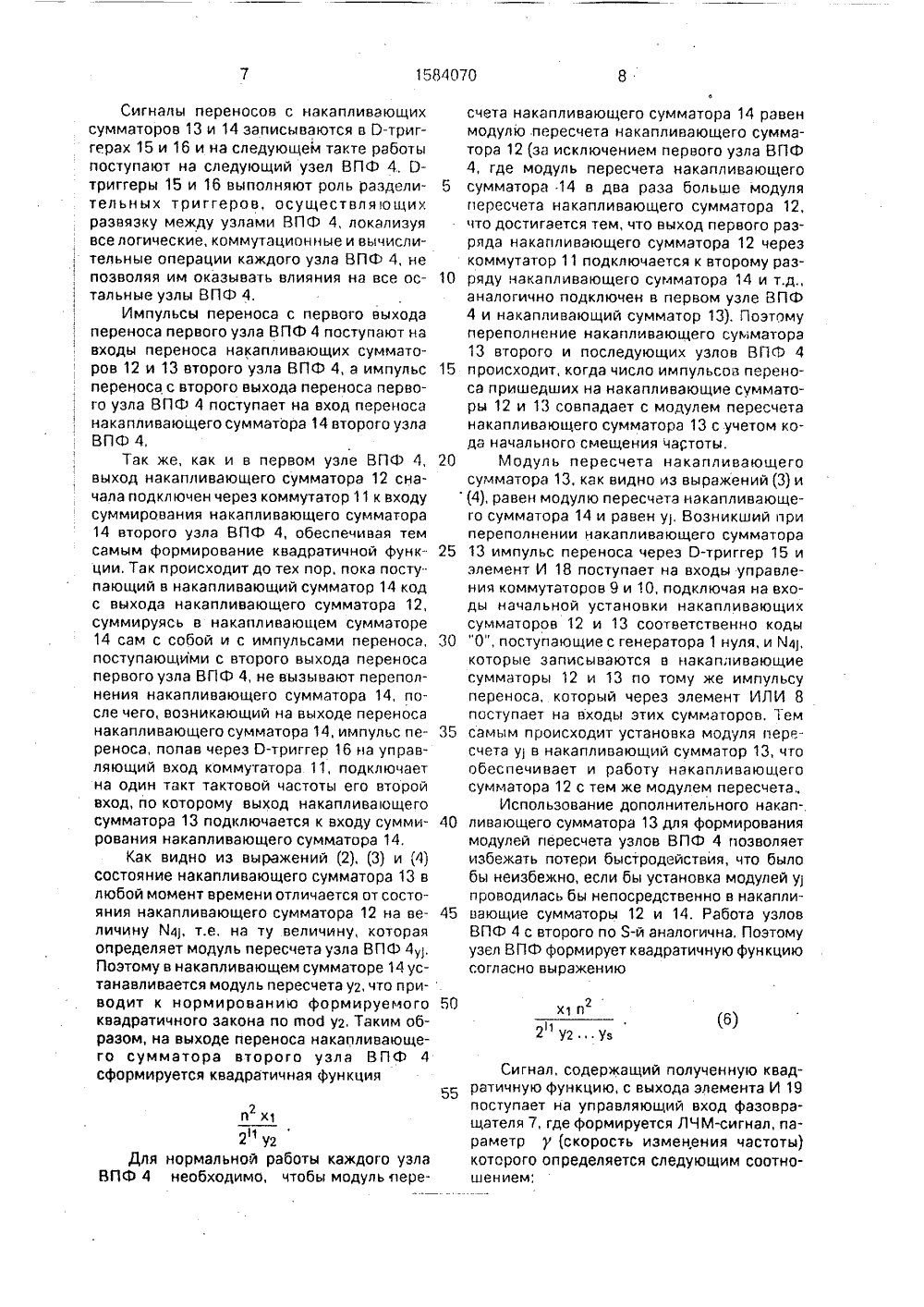

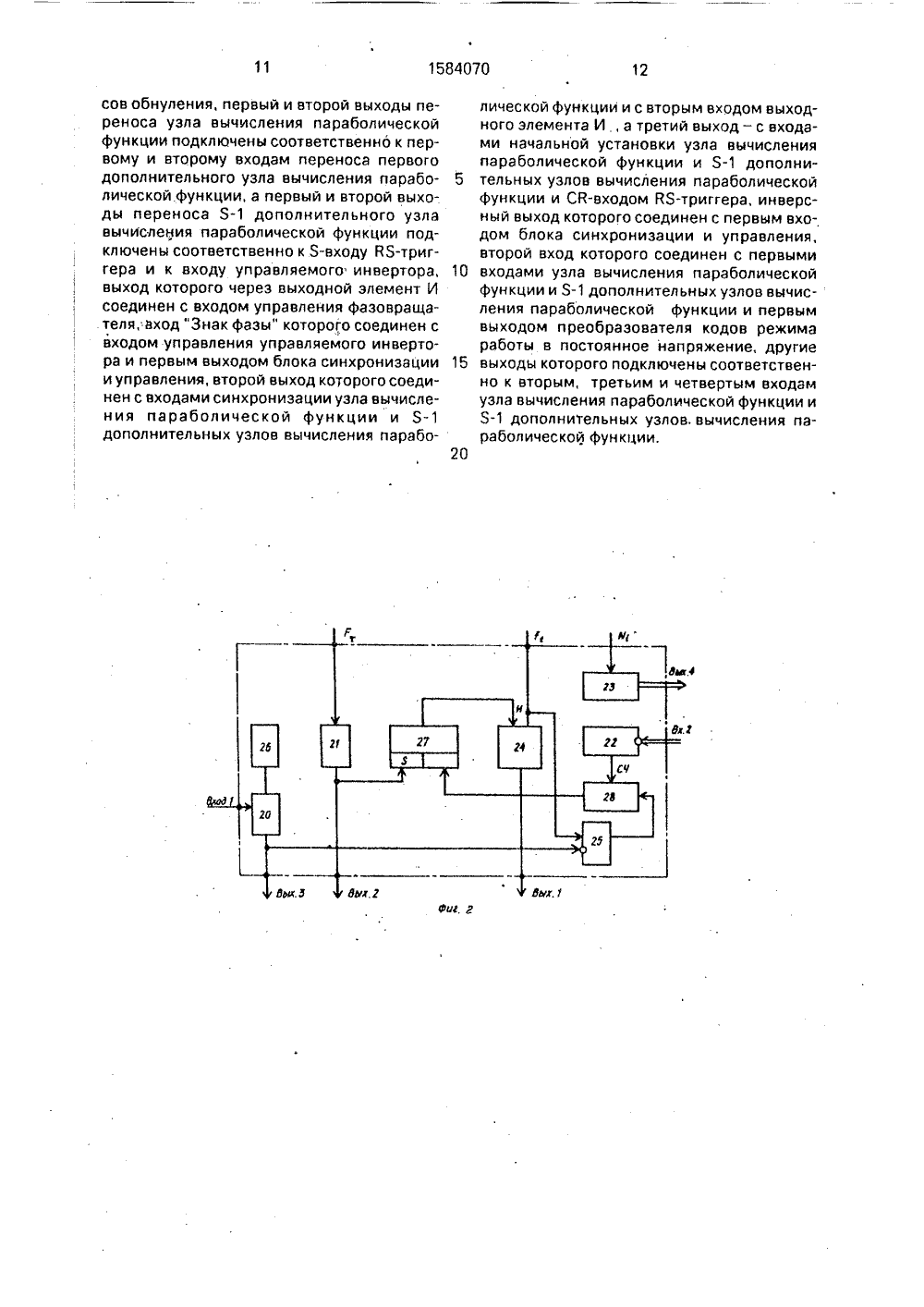

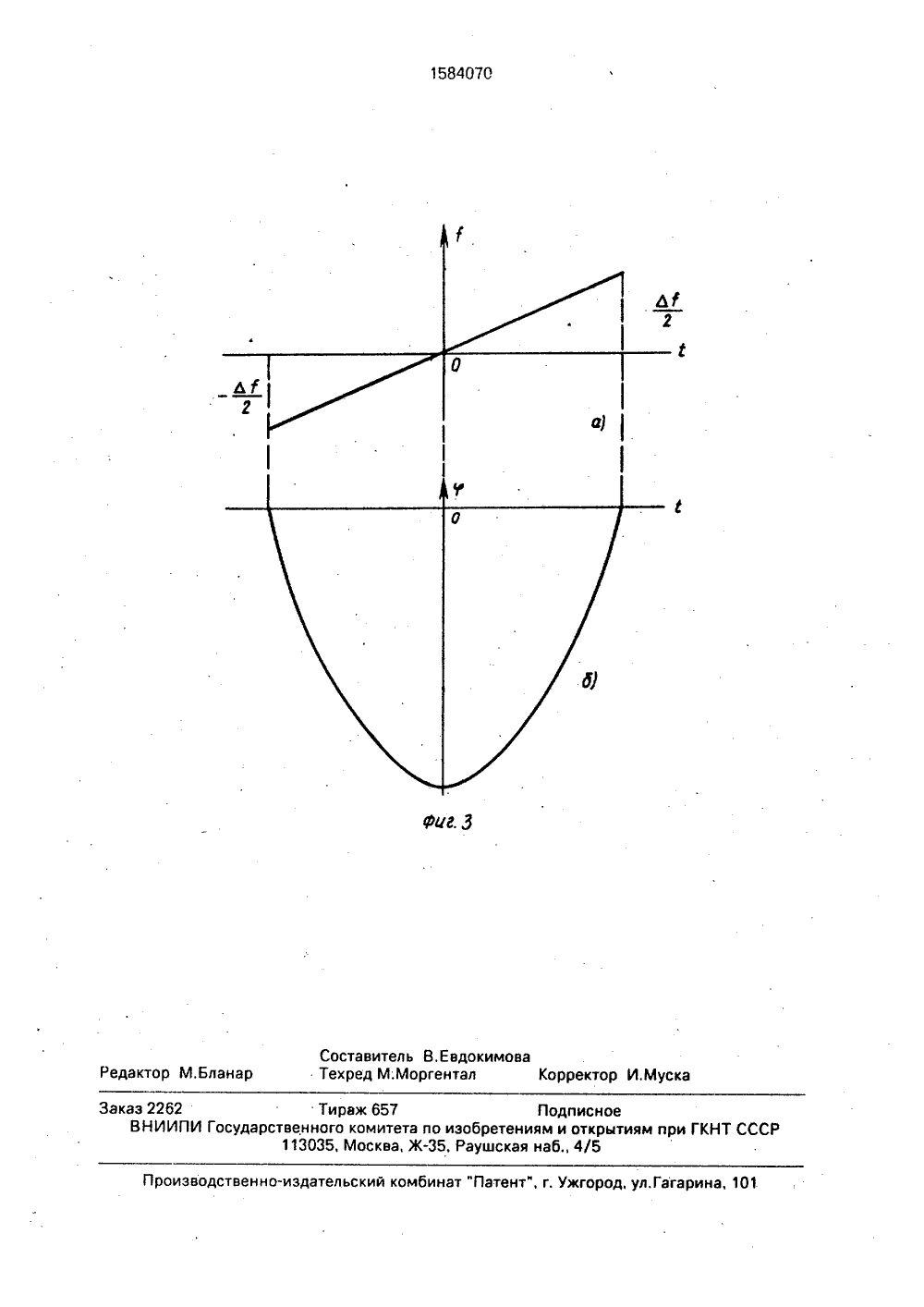

( 9) 5)5 Н 03 С 3/08 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗС)БРЕТЕНИЯ ВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРМ 915213,.кл. Н 03 С 3/08, 1980,(57) Изобретение относится к радиотехнике.Цель изоретения - повышение быстродействия и расширение функциональныхвозможностей путем увеличения числа перестраиваемых параметров сигналов, Дляэтого формирователь линейно-частотно-модулированных (ЛЧМ) сигналов содержит г-р1 импульсов обнуления, блок 2 синхронизации и управления, преобразователь 3 кодов режима работы в постоянное напряжение, узлы 4 вычисления параболической фции, состоящие каждый из эл-та ИЛИ 8, коммутаторов 9, 10 и 11 кодов, накапливающих сумматоров 12, 13 и 14, О-триггеров 15 и 16, эл-та ИЛИ-НЕ 17 и эл-та И 18, а также содержит ВЯ-триггер 5, управляемый инвертор 6, фазовращатель 7 и выходной эл-т И 19, Код режима работы формирователя содержит информацию о параметрах ЛЧМ- сигнала: скорости изменения частоты и времени длительности линейного участка, по которому преобразователь 3 вырабатывает четыре константы, поступающие на узлы 4 вычисленияИспользование сумматора 13 для формирования модулей пересчета узлов 4 вычисления позволяет избежать потери быстродействия, при этом узлы 4 вычисления формируют заданную квадратичную ф-цию.3 ил.Изобретение относится к радиотехникеи может использоваться для формированиялинейно-частотно-модулированных сигналов в различных радиотехнических устройствах, 5Цель изобретения - повышение быстродействия и расширение функциональныхвозможностей путем увеличения числа перестраиваемых параметров сигналов.На фиг,1 представлена структурная 10электрическая схема формирователя линейно-частотно-модулированных сигналов; нафиг,2 - схема блока синхронизации и управления; на фиг,3 - закон изменения частоты,15Формирователь линейно-частотно-модулированных (ЛЧМ) сигналов содержит генератор импульсов обнуления 1, блок 2синхронизации и управления, преобразователь 3 кодов режима работы в постоянное 20напряжение, 5 последовательно соединенных узла 4 вычисления параболической функции (ВПФ), ВЯ-триггер 5, управляемыйинвертор 6, фазовращатель 7, причем в состав каждого из 5 узлов ВПФ 4 входят элемент ИЛИ 8, первый 9, второй 10 и третий11 коммутаторы кодов, первый 12, второй 13и третий 14 накапливающие сумматоры,первый 15 и второй 16 О-триггеры, элементИЛИ-НЕ 17 и элемент И 18, и выходной элемент И 19, а в состав блока 2 синхронизациии управления входят блок 20 сравнения кодов, формирователь 21 импульса начальнойустановки, преобразователь 22 кода, преобразователь 23 кода, элемент И 24, элемент 35И 25, генератор 26 нулевого кода, БЯ-триггер 27 и реверсивный счетчик 28,Формирователь ЛЧМ-сигналов работает следующим образом.На вход блока 2 поступает код режима 40работы йь содержащий информацию о параметрах ЛЧМ-сигнала - скорости изменениячастоты 4= Лт /Т,где Л 1 - девиациячастоты, и времени длительности линейного участка Т 1, по которому преобразователь.З.кодов вырабатывает четыреконстанты й 1 - М 4 ь поступающие соответственнно на входы 3 узлов ВПФ 4,На входы суммирования накапливающих сумматоров 12 и 13 всех Я узлов ВПФ 504 поступает константа М 2, определяемая изсоотношения х 1 при) =1,о при 1, ) 55 т.е. на первыи узел ВПФ 4 поступает двоичный код числа Х 1, а на все остальные узлы ВПФ - нулевой код, Этот нулевой код, поступая на элементИЛИ-НЕ 17, устанавливает на его выходе сигнал "1", поступающий на вход элемента И 18, давая разрешение на прохождение сигналов с выхода О-триггера 15, Двоичный код числа Х 1, поступив на вход элемента ИЛИ-НЕ 17 первого узла ВПФ 4, устанавливает на его выходе сигнал "0", который через элемент И 19 поступает на входы управления коммутаторов 9 и 10 первого узла ВПФ 4 и пропускает на выход сигналы с их первых входов.При поступлении импульса синхронизации Гг, определяющего момент максимальной отрицательной девиации частоты и начало линейного участка изменения частоты, блок 2 вырабатывает импульс начальной установки, поступающий на входы установки в "0" О-триггеров 15 и 16 Я узлов ВПФ 4, Сигнал "0" с выхода О-триггера 15 через элемент И 18 поступает на входы управления коммутаторов 9 и 10, а с выхода О-триггера 16 - , на вход управления коммутатора 11, В результате этого сигнал с первых входов Б узлов ВПФ 4 через коммутатор 9 поступает на вход начальной установки накапливающего сумматора 12, сигнал с третьих входов Я узлов ВПФ 4 поступает через коммутатор 10 на вход установки накапливающего сумматора 13, а сигнал с выхода накапливающего сумматора 12 поступает через коммутатор 11 на вход накапливающего сумматора 14.Тот же импульс начальной установки, поступающий на вход управления накапливающего сумматора 14, а также через элемент ИЛИ 8 - на накапливающие сумматоры 12 и 13. записывает в них информацию, находящуюся на входах начальной установки; в накапливающий сумматор 12 - константу М 1, в накапливающий сумматор 14 - константу М 4, в накапливающий сумматор 13 - константу йз. Тот же импульс начальной установки, поступающий на В-вход ВЯ-триггера 5 устанавливает сигнал "1" на его инверсном выходе, который, поступая на первый вход блока 2, поступает на младший разряд блока 20 сравнения, сравниваясь с нулевым кодом, определяющим условие смены знака девиации частоты, В результате сравнения "единичного кода" с нулевым на первом выходе блока 2 появляется сигнал "1", поступающий на вход "Знак фазы" фазовращателя 7, устанавливая отрицательное значение знака фазы, и на вход управляемого инвертора 6, после чего управляемый инвертор 6 начинает работать в режиме инвертирования входного сигнала, 1584070) - номер узла ВПФ;- число разрядов накапливающего сумматора 14 ).-го узла ВПФ 4.Константа И 4, поступающая на накапливающий сумматор 14 Б узлов ВПФ 4, представляет собой число, дополняющее модуль Управляемый инзертор 6 определяет знак измен.ния абсслютного значения охклонения о несущей фоомируемой частоты. Поэтому при установке отрицател 1;ного знака фазь: в фазовращателе 7(что означает уменьшение фазового сдвига), такая установка формирует максимальное отрицательное смещение текущей частоты, и по мере заполнения накапливающего сумматора 12 это смеЩение уменьшается, т.е, формируется закан изменения частоты (фиг.2 а). Для того, чтобы сигналы, поступающие с выхода управляемого инвеотора 6 на вход управления фазовращателя 7, имели импульсный характер, что необходимо для работы фазовращателя 7, они стробируются импульсами тактовой частоты 1 т, поступающими на выходной элемент И 19,Режим отрицательной девиации частоты необходимо начинать с требуемого отрицательного смещения частоты. Так как При формироваии квадратичной функции с помощью двух накапливающих сумматоров 12 и 14 содержимое накапливающего сумматора 12 определяет значение текущей частоты, а содержимое накапливающего сумматора 14 - значение текущей фазы формируемого сигнала, то константа Й 1, определяющая величину требуемого отрицательного смещения частоты, записывается в накапливающий сумматор 12,Код йь разложенный по модулям узлов ВПФ 4, имеет видпересчета накапливающего сумматора 14до его полного объема и определяется следующим соотношением; й 4,=. 2"-у при) 1 (3) 0 при) =1,где г- полный объем накапливающего1сумматора 14)-го узла ВПФ 4.Константа И 4 предназначена для формирования модуля пересчета узла ВПФ 4 в момент начальной установки.Для формирования модуля пересчета 15 узла ВПФ 4 в процессе работы служит накапливающий сумматор 13, в который по импульсу начальной установки записывается константа Йз, определяемая соотноше- нием 20ИЗ = М 1 + Й 41,(4) П=х 1, (2 +1)/тоб 211, (5) г При переполнении накапливающего сумматора 14 возникающий при этом импульс переноса устанавливает в "1" 0-триггер 16 на время действия сигнала переноса, т.е. на один такт тактовой частоты 1 т. Это приводит к тому, что коммутатор 11 подключает на один такт на вход суммирования накапливающего сумматора 14 выход накапливающего сумматора 13, который работает в первом узле ВПФ 4 аналогично накапливающему сумматору 12, т.е. такое переключение не сказывается на режиме формирования квадратичного закона,т,е. в накапливающем сумматоре 13 устанавливается модуль пересчета такой же, кэк и в накапливающем сумматоре 14 плюс код начального смещения частоты. После того как прошла установка начальных условий, с второго выхода блока 2 начинают поступать импульсы тактовой частоты на входы синхронизации накапливающих сумматоров 12 - 3014, а также О-триггеров 15 и 16.Поступающий на входы суммированиянакапливающих сумматоров 12 и 13 первого узла ВПФ 4 код числа Х начинает складываться в этих сумматорах, формируя в нихх 1число . С выхода накапливающего сум 21матора 12 через коммутатор 11 этот код поступает на вход суммирования накапли вающего сумматора 14, в котором он суммирует с частотой синхронизации согласно рекуррентному выражению:1584070 осчета накапливающего сумматора 14 равен модулю пересчета накапливающего сумматора 12 (за исключением первого узла ВПФ 4, где модуль пересчета накапливающего Сигналы переносов с накапливающих сумматоров 13 и 14 записываются в О-триггерах 15 и 16 и на следующем такте работы поступают на следующий узел ВПФ 4. О- триггеры 15 и 16 выполняют роль разделительных триггеров, осуществляющих развязку между узлами ВПФ 4, локалиэуя все логические, коммутационные и вычислительные операции каждого узла ВПФ 4, не позволяя им оказывать влияния на все остальные узлы ВПФ 4,Импульсы переноса с первого выхода переноса первого узла ВПФ 4 поступают на входы переноса накапливающих сумматоров 12 и 13 второго узла ВПФ 4, а импульс переноса с второго выхода переноса первого узла ВПФ 4 поступает на вход переноса накапливающего сумматора 14 второго узла ВПФ 4,Так же, как и в первом узле ВПФ 4, выход накапливающего сумматора 12 сначала подключен через коммутатор 11 к входу суммирования накапливающего сумматора 14 второго узла ВПФ 4, обеспечивая тем самым формирование квадратичной функции. Так происходит до тех пор, пока посту. пающий в накапливающий сумматор 14 код с выхода накапливающего сумматора 12, суммируясь в накапливающем сумматоре 14 сам с собой и с импульсами переноса, поступающими с второго выхода переноса первого узла ВПФ 4, не вызывают переполнения накапливающего сумматора 14, после чего, возникающий на выходе переноса накапливающего сумматора 14, импульс переноса, попав через О-триггер 16 на управляющий вход коммутатора. 11, подключает на один такт тактовой частоты его второй вход, по которому выход накапливающего сумматора 13 подключается к входу суммирования накапливающего сумматора 14.Как видно из выражений (2), (3) и (4) состояние накапливающего сумматора 13 в любой момент времени отличается от состояния накапливающего сумматора 12 на величину М 4, т.е, на ту величину, которая определяет модуль пересчета узла ВПФ 4 у, Поэтому в накапливающем сумматоре 14 устанавливается модуль пересчета у 2, что приводит к нормированию формируемого квадратичного закона по вод у 2, Таким образом, на выходе переноса накапливающего сумматора второго узла ВПФ 4 сформируется квадратичная функция сумматора 14 в два раза больше модуля пересчета накапливающего сумматора 12, что достигается тем, что выход первого разряда накапливающего сумматора 12 через коммутатор 11 подключается к второму разряду накапливающего сумматора 14 и т.д., аналогично подключен в первом узле ВПФ 4 и накапливающий сумматор 13). Поэтому 10 переполнение накапливающего сумматора 13 второго и последующих узлов ВПФ 4 происходит, когда число импульсов переноса пришедших на накапливающие сумматоры 12 и 13 совпадает с модулем пересчета накапливающего сумматора 13 с.учетом кода начального смещения частоты,Модуль пересчета накапливающего сумматора 13, как видно из выражений 3) и 20(4), равен модулю пересчета накапливающего сумматора 14 и равен у, Возникший при переполнении накапливающего сумматора 13 импульс переноса через О-триггер 15 и элемент И 18 поступает на входы управления коммутаторов 9 и 10, подключая на входы начальной установки накапливающих сумматоров 12 и 13 соответственно коды "0", поступающие с генератора 1 нуля, и Мл, которые записываются в накапливающие сумматоры 12 и 13 по тому же импульсу переноса, который через элемент ИЛИ 8 поступает на входы этих сумматоров.ем самым происходит установка модуля пересчета у в накапливающий сумматор 13, что обеспечивает и работу накапливающего сумматора 12 с тем же модулем пересчетаИспользование дополнительного накап-. ливающего сумматора 13 для формирования модулей пересчета узлов ВПФ 4 позволяет избежать потери быстродействия, что было бы неизбежно, если бы установка модулей у проводилась бы непосредственно в накапливающие сумматоры 12 и 14. Работа узлов ВПФ 4 с второго по Я-й аналогична. Поэтому узел ВПФ формирует квадратичную функцию согласно выражению 25 30 35 40 45 50 х 1 п(6) 2 у 2у и Сигнал, содержащий полученную квадратичную функцию, с выхода элемента И 19 поступает на управляющий вход фаэовращателя 7, где формируется ЛЧМ-сигнал, параметр у (скорость изменения частоты) и х 1 г" у 2 Для нормальной работы каждого узла которого определяется следующим соотноВПФ 4 необходимо, чтобы модуль г 1 ере- шением;где Я21 . Р2 дх 1 Поскольку содержимое накапливающих сумматоров 12 3 узлов ВПФ 4 определяет код текущей частоты, то момент обнуления этих сумматоров, т.е. возникновение импульса переноса на выходе первого переноса последнего узла ВПФ 4 соответствует моменту изменения знака девиации частоты. Поэтому этот импульс переноса, поступающий на Я-вход ЯЯ-триггера 5 устанавливает на его инверсном выходе сигнал "0", по которому блок 2 устанавливает на первом выходе сигнал "0", который, поступая на вход "Знак фазы" фазовращателя 7 устанавливает в нем положительный знак фазы, и на управляющий вход управляемого инвертора 6, устанавливает в нем режим неинвертирования входного сигнала.В виду того, что формируемый формирователем квадратичный закон изменения фазы имеет вид симметричной параболы (фиг,2 б), момент окончания модуляции определяется также значением константы М 1. Поэтому код М 1 поступает на второй вход блока 2, где преобразуется в обратный код, Таким образом, при положительном знаке девиации накапливающие сумматоры 12 всех Я узлов ВПФ 4 накапливают свое значение от нуля до величины обратного кода М 1, после. чего блок 2 прекращает поступление тактовой частоты 1 т на узел ВПФ до прихода следующего импульса Гт.Формула изобретения Формирователь линейно-частотно-модулированных сигналов, содержащий последовательно соединенные блок синхронизации и управления и преобразователь кодов режима работы в постоянное напряжение, управляемый инвертор, фазовращатель и узел вычисления параболической функции, в состав которого входят три сумматора.отл ича ющи йс я тем, что, с целью повышения быстродействия и расширения функциональных возможностей путем увеличения числа перестраиваемых параметров сигналов, введены генератор импульсов обнуления, ВЗ-триггер, выходной элемент И и Япоследовательно соединенных дополнительных узлов вычисления параболической функции, каждый из которых выполнен идентично узлу вычисления параболической функции, в состав которого введены три коммутатора ко 15 20 25 30 переноса - вход переноса третьего накапливающего сумматора, первым входом - первый вход первого коммутатора кодов, вторым входом - соединенные между собой входы суммирования первого и второго ка 45 напливающих сумматоров и входэлемента ИЛИ-НЕ, третьим входом - первый вход второго коммутатора кодов, четвертым входом - соединенные между собой второй вход второго коммутатора кодов и вход начальной установки третьего накапливающего сумматора и пятым входом - второй вход первого коммутатора кодов, а первым и вто 50 рым выходами переноса - выходы первого и второго О-триггеров соответственно, кро 55 ме того, первый и второй входы переноса узла вычисления. параболической функции и пятый вход каждого из 5-1 дополнительных узлов вычисления параболической функции соединены с выходом генератора импуль 5 10 35 40 дов, элементы ИЛИ-ЧЕ, ИЛИ, И и два О- триггера, сумматоры выполнены в виде накапливающих сумматоров, при этом выход первого коммутатора кодов соединен с входом начальной установки первого накапливающего сумматора, к входу управления которого подключен выход элемента ИЛИ и вход управления второго накапливающего сумматора, к входу начальной установки которого подключен выход второго коммутатора кодов, выход переноса второго накапливающего сумматора подключен к входу первого О-триггера, а выход второго накапливающего сумматора подключен к второму входу третьего коммутатора кодов,к первому входу которого подключен выход первого накапливающего сумматора, а выход третьего коммутатора кодов соединен с входом суммирования третьего накапливающего сумматора, выход переноса которого соединен с входом второго О-триггера, выход которого соединен с входом управления третьего коммутатора кодов, выход первого О-триггера и выход элемента ИЛИ-НЕ через элемент И подключен к входам управления первого и второго коммутаторов кодов и к первому входу элемента ИЛИ, причем входы синхронизации первого, второго и третьего накапливающих сумматоров и первого и второго О-триггеров соединены между собой и являются входом синхронизации узла вычисления параболической функции, входом начальной установки которого является второй вход элемента ИЛИ, соединенный с входом управления третьего накапливающего сумматора и с входами установки в "0" первого и второго О-триггеров, первым входом переноса - соединенные между собой входы .переноса первого и второго на-. капливающих сумматоров, вторым входомсов обнуления, первый и второй выходы переноса узла вычисления параболической функции подключены соответственно к первому и второму входам переноса первого дополнительного узла вычисления парабо лической функции, а первый и второй выходы переноса 5-1 дополнительного узла вычисления параболической функции подключены соответственно к 5-входу КБ-триггера и к входу управляемого инвертора, 10 выход которого через выходной элемент И соединен с входом управления фазовращателя, вход "Знак фазы" которого соединен с входом управления управляемого инвертора и первым выходом блока синхронизации 15 и управления, второй выход которого соединен с входами синхронизации узла вычисления параболической функции и 5-1 дополнительных узлов вычисления парабо 20 лической функции и с вторым входом выходного элемента И ., а третий выход - с входами начальной установки узла вычисления параболической функции и 5-1 дополнительных узлов вычисления параболической функции и Сй-входом ЯЯ-триггера, инверсный выход которого соединен с первым входом блока синхронизации и управления, второй вход которого соединен с первыми входами узла вычисления параболической функции и Ядополнительных узлов вычисления параболической функции и первым выходом преобразователя кодов режима работы в постоянное напряжение, другие выходы которого подключены соответственно к вторым, третьим и четвертым входам узла вычисления параболической функции и 5-1 дополнительных узлов. вычисления параболической функции.,Бланар Техред М;Моргентал Корректор И Муска ак тельский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 роизво но Заказ 2262 Тираж 657 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4330354, 17.11.1987

ПРЕДПРИЯТИЕ ПЯ Г-4273

ИВАНОВ ЮРИЙ ПЕТРОВИЧ, БАНКОВСКИЙ ЮРИЙ АЛЕКСАНДРОВИЧ, РАБОТАЕВ ЮРИЙ ВАЛЕНТИНОВИЧ

МПК / Метки

МПК: H03C 3/08

Метки: линейно-частотно-модулированных, сигналов, формирователь

Опубликовано: 07.08.1990

Код ссылки

<a href="https://patents.su/7-1584070-formirovatel-linejjno-chastotno-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь линейно-частотно-модулированных сигналов</a>

Предыдущий патент: Цифровой формирователь частотно-модулированных сигналов

Следующий патент: Модулятор плоскости поляризации

Случайный патент: Водонапорная башня