Запоминающее устройство с исправлением дефектов и ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

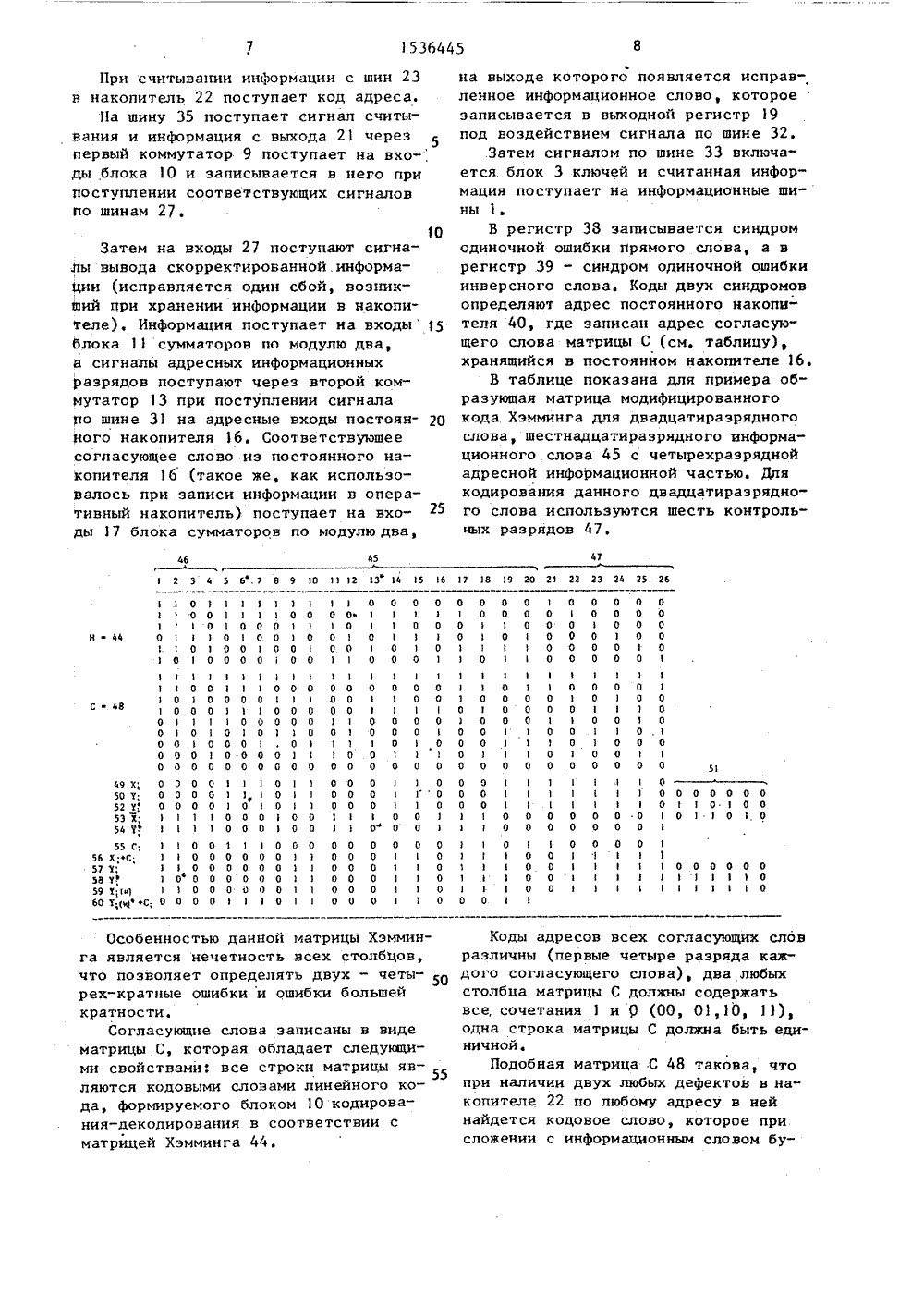

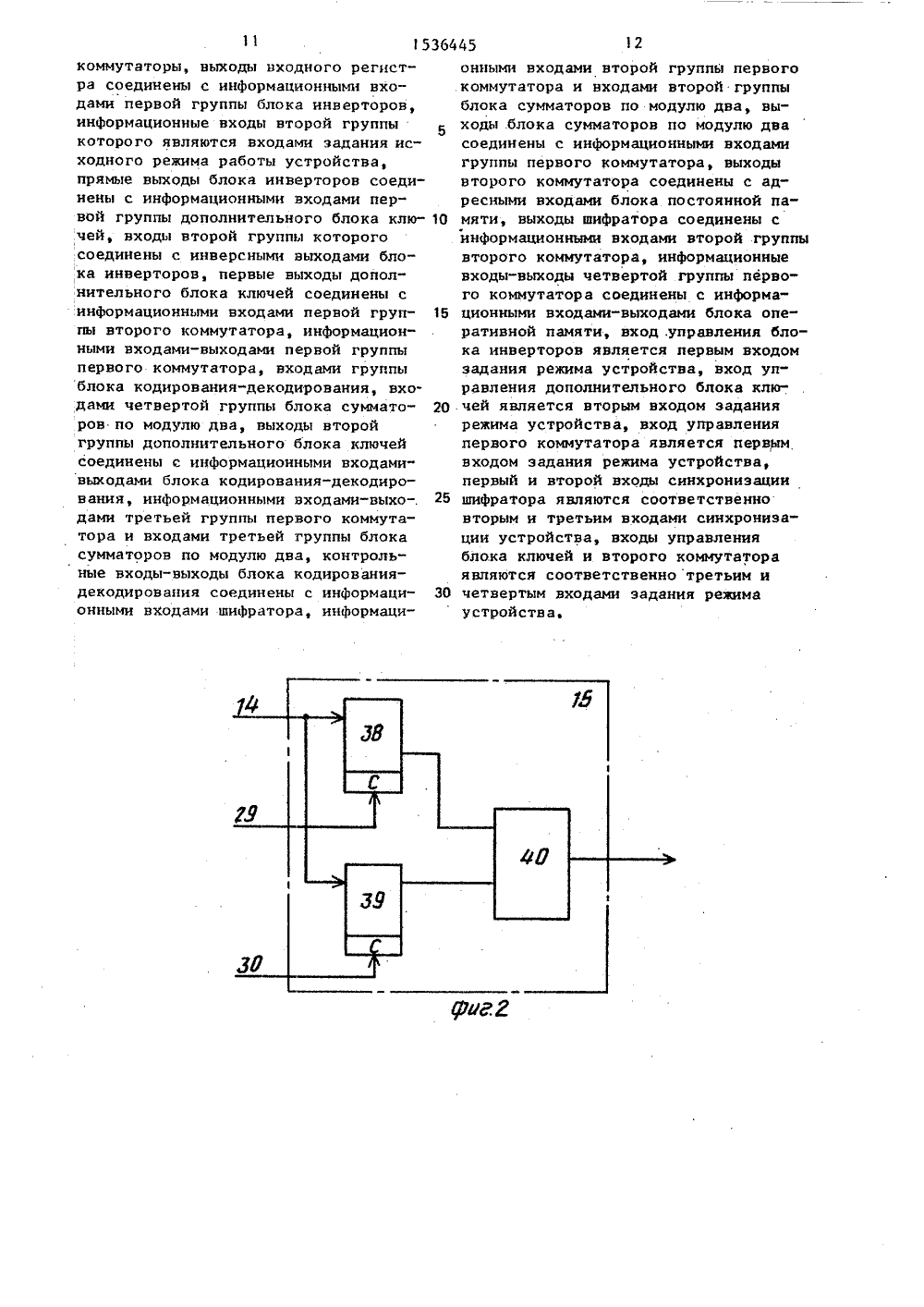

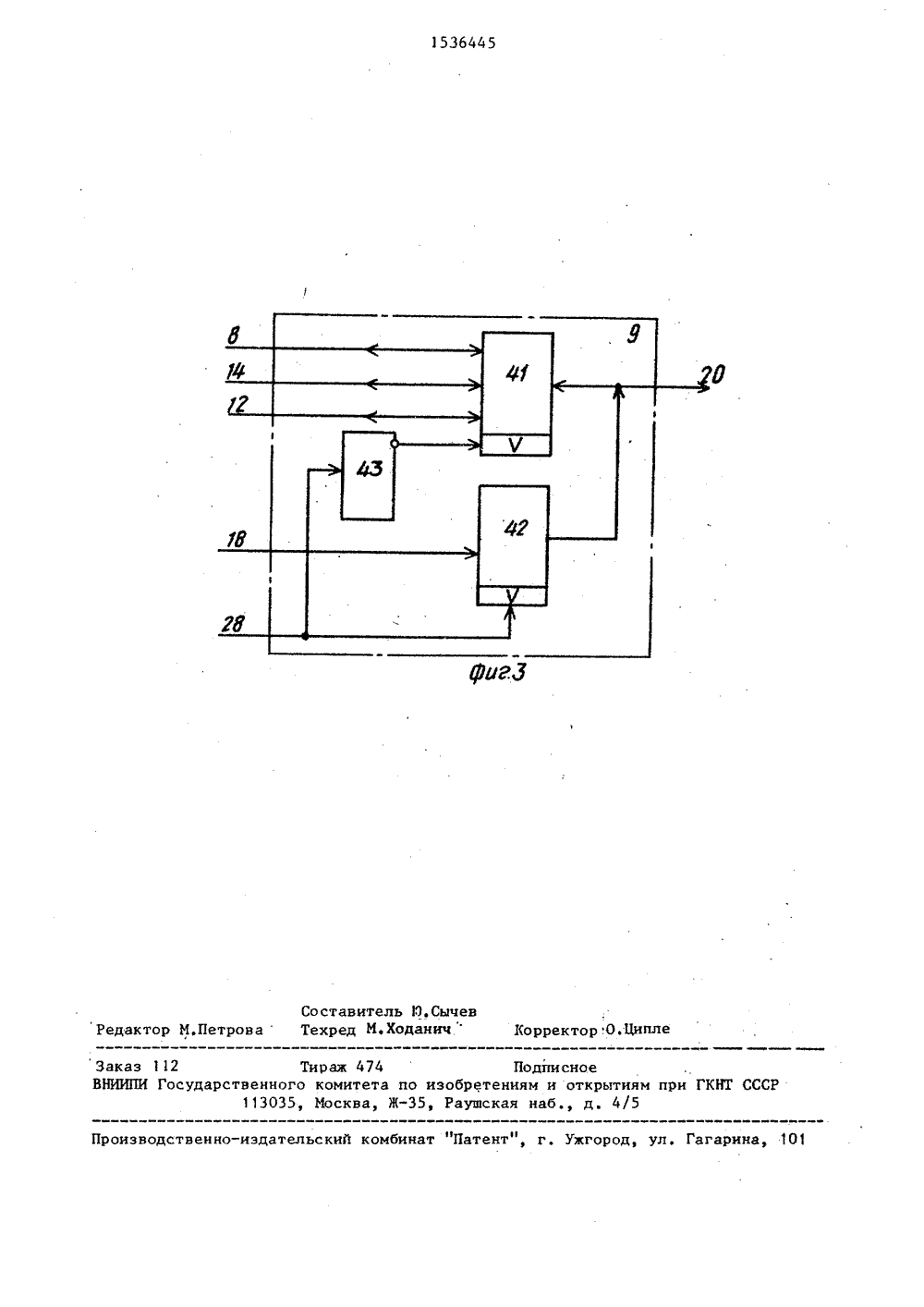

(5 Е ИЗОБРЕТЕНИЯ Н АВТО С ИСПвычнс-г ь ис- минаю надежения - тройст- оды-вьюк 5 ок 7 блок 1 О ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОЧНРЬВИЯМПРИ П 1 НТ СССРОПИСАНИ МУ СВИДЕТЕЛЬСТ 1 (21) 4256899/24-24 (22) 04,06,87 (46) 15.090. Бюл. 11 г 2 (72) В.Д.Комаров, А.В.Кузнецов А.Д.Кухарев и Ю.А.Трофимов (53) 681.327.66(088.8) (56) Комаров В,Д., Кузнецов А.В. Увеличение средней наработки на отказ запоминающего устройства с исправлением дефектов и оигибок, И.: Техника средств связи, 1982, с.68-76Авторское свидетельство СССР11 г 1048520, кл. С 11 С 29/00, 1983,(54) ЗАПОИИНАММ 11 ЕЕ УСТРОЙСТВО РАВЛЕНИЕИ ДЕФЕКТОВ И ОШИБОК (57) Изобретение относится к лительной технике и может быт пользовано в оперативных зап щих устройствах для повышени ности их работы. Цель изобре увеличение быстродействия, У во содержит информационные вх ходы 1, входной регистр 2, бл инверторов, дополнительный бл ключей, первый коммутатор 9,Я 87Изобретение относится к вычислительной технике и может. быть использовано в оперативных запоминающихусТройствах для повышения надежностиик работы.Цель изобретения - увеличение бы 1.,стродействия15На фиг. 1 приведена структурнаясхема запоминающего устройства с ис"правлением дефектов и ошибок; нафи". 2 - структурная схема шифратора;на Фиг. 3 - структурная схема первого коммутатора.Устройство (фиг. 1) содержит инФормационные входы-выходы 1, входнойреистр 2, выходы блока 3 ключей,входы 4 второй группы блока 5 инверторов, входы 6 первой группы блокаинЬерторов, дополнительный блок 7клЮчей, выходы 8 второй группы дополниТельного блока ключей, первый коммутатор 9, блок 10 кодирования-декодирования, блок 11 сумматоров по модулю два, выходы 12 первой группыдополнительного блока ключей, второйкоммутатор 13, входы-выходы 14 второ группы блока кодирования-декоди" 35розания, шифратор 15, блок 16 постоянной памяти, входы 17 первой группысуМматора по модулю два, входы 18первой группы первого коммутатора,выходной регистр 19, четвертые входы выходы 20 первого коммутатора, входывьходы 21 блока 22 оперативной памяти, адресные входы 23 устройства,первый вход 24 синхронизации, первыйвход 25 задания режима, второй вход26 задания режима, входы 27 заданиярежима группы, третий вход 28 заданиярежима, второй вход 29 синхронизации,третий вход 30 синхронизации, четвертый вход 31 задания режима, четвертый вход 32 синхронизации, пятыйвход 33 задания режима, вход 34 обращения вход 35 записи-чтения, выходы одиночной 36 и многобитовой 37ошибок. 55Шифратор (фиг, 2) содержит регистры38 и 39 и второй блок 40 постояннойпамяти. Первый коммутатор (фиг, 3) содержит блок 41 ключей, блок 42 ключей и блок 43 инверторов,Устройство работает следующим образом.При первом цикле записи информа"ции на шине 23 устанавливается кодадреса, а на информационной шине 1 "информационное слово (например, шестнадцатиразрядное), подлежащее записи,Сигналом по шине 24 это слово записывается во входной регистр 2. Приотсутствии. сигнала по нине 25 блок 5инверторов не инвертирует информацию,поступающую на входы 4 и 6. Затемпоступает сигнал по шине 26, открывает блок 7 ключей и на выходах 8 появляется входное информационное слово(неинвертированное), а на выходах2 - нули (в рассматриваемом примеречетыре разряда),На управляющих входах 27 появляется комбинация сигналов, соответствующая режиму кодирования входной информации, и на выходах 14 контрольныхразрядов блока 10 появляются контрольные разряды соответствующего кода Хзмминга (в рассматриваемом примере шесть разрядов).При отсутствии сигнала на шине 28первый коммутатор 9 соединяет входывыходы с входами-выходами 20.Таким образом, входное информационное неинвертированное слово (16разрядов), адресные информационныеразряды - нули, (четыре разряда) иконтрольные разряды Хэмминга (шестьразрядов) поступают через коммутатор.9 на входы-выходы 21 блока 22 оперативной памяти и под действием сигналов записи по шине 34 записываютсяв него по адресу 23.Затем происходит первый цикл считывания информации.. Снимается сигнал с шины 26 и выключается блок 7 ключей. На шине 35появляется сигнал считывания и информация с выходов 21 накопителя 22 через коммутатор 9 поступает на входыблока 10 декодирования. На входах 275 15 появляется комбинация сигналов, осуществляющая запись считанной информации в блок 10 декодирования.Затем выключается сигнал 35 и появляется сигнал по шине 28, при котором отключаются входы-выходы коммутатора 9 и соединяются входы 18 и входы-выходы 20. На входах 27 появляют" ся сигналы, осуществляющие вывод скорректированной информации, на выходах 14 - синдром ошибки, который под воздействием сигнала по шине 29 записывается в шифратор.На выходах 36 и 37 ошибок появляются соответствующие сигналы. Если ошибки отсутствуют, то запись информации в запоминающее устройство за" каичивается. Если на выходах 36 или 37 появляются сигналы ошибок, то уст. ройство переходит к второму циклу записи-считывания информации. При этом на шине 25 появляется сигнал ин.вертирования, на шине 26 - сигнал включения блока ключей, на шинах 27- сигналы кодирования, с шины 28 снимается сигнал переключения. Инвертированная информация с выходов 8 пос" тупает в блок 10 и через коммутатор 9 - на входы накопителя 22, с выходов 12 единичное слово также поступает в блок 10 и на входы накопителя 22, а с выходов 14 соответствующие контрольные разряды также поступают на входы накопителя. На шину 34 поступает сигнал записи и инвертированное информационное слово вместе с единичной информационной частью и со. ответствующими контрольными разрядами записывается в оперативный накопитель 22. Заканчиваются сигналы по шинам 34, 25, 26 и 27.Устройство переходит к второму циклу считывания. На шине 35 появляется сигнал считывания и информация из накопителя 22 поступает иа входы блока 10 и под воздействием сигналов по шинам 27 записывается в блок 10, затем на шине 28 появляется сигнал, переключающий коммутатор 9, на входы 27 поступает комбинация сигналов, осуществляющая вывод скорректированной информации иэ блока 10, На выходах 14 появляется синдром ошибок, ко" торый поступает на входы шифратора 15 и записывается в него под воздействием сигнала записи по шине 30. На выходах ошибок появляются соответствующие сигналы, поступающие на шины 36445 630 и 37, Если сигналы ошибок отсутствуют, то запись информации в запоминающее устройство заканчивается.Если на шине 37 отсутствует сигнал многобитовой ошибки, ели на шине36 присутствует сигнал одиночнойошибки и если в первом цикле считывания обнаружена лишь одиночная ошиб"ка, то устройство переходит к третьему циклу записи-считывания (если .впервом цикле записи-считывания былиобнаружены многобитовые ошибки, а вовтором цикле - однобитовыеили многобитовые, то это значит, что количест"во по данному адресу превьппает корректирунппую способность устройствадва дефекта).Прекращаются сигналы по шинам 27 20 и 30.В третьем цикле записи информацииоткрывается блок 7 ключей сигналом пошине 25, на шинах.27 устанавливаетсякомбинация сигналов кодирования и ин формация в прямом коде поступает навходы блока 10 кодирования и входыблока 11 сумматоров по модулю двавместе с нулевыми адресными информационными сигналами и соответствующи ми контрольными разрядами с выходов14. ШиФратор 15 по двум записаннымв него синдромам одиночных ошибокпрямого и инверсного информационныхслов вырабатывает код адреса согласующего слова, который поступает через второй коммутатор 13 на адресныевходы постоянного накопителя. 16, Согласующее слово (в данном примередвадцатишестиразрядное) поступает на 40 другие входы 17 блока 11 сумматоровпо модулю два, где суммируется с информационным словом, С выхода блока11 сумматоров информация поступаетна входы 18 первого коммутатора 9 ипосле прихода сигнала переключенияпо шине 28 поступает на входы-выходы21 накопителя 22, По шине 34 поступает сигнал записи и суммированная информация записывается в накопитель 22,Вместе с окончанием сигналов по шинам 34, 28 и 26 заканчивается циклзаписи информации в запоминающее устройство.Если по данному адресу в оперативном накопителе 22 имелось не более,двух дефектов, то гарантируется запись информации в согласованном с дефектами виде не более чем за три цик,ла записи считывания,При считывании информации с шин 23в накопитель 22 поступает код адреса.а шину 35 поступает сигнал считывания и информация с выхода 21 черезпервый коммутатор 9 поступает на вхо-,ды блока 10 и записывается в него припоступлении соответствующих сигналовпо шинам 27,ОЗатем на входы 27 поступают сигнаЛы вывода скорректированной.информации (исправляется один сбой, возникший при хранении информации в накопителе). Информация поступает на входы 15 блока 11 сумматоров по модулю два, в сигналы адресных информационных разрядов поступают через второй коммутатор 13 при поступлении сигнала по шине 31 на адресные входы постоян Ного накопителя 16. Соответствующее согласующее слово из постоянного накопителя 16 (такое же, как использоВалось при записи информации в оперативный накопитель) поступает на входы 17 блока сумматоров по модулю два,Особенностью данной матрицы Хэмминга является нечетность всех столбцов,что позволяет определять двух - четырех-кратные ошибки и ошибки большейкратности,Согласующие слова записаны в видематрицы С, которая обладает следующими свойствами; все строки матрицы являются кодовыми словами линейного кода, формируемого блоком 10 кодирования-декодирования в соответствии сматрицей Хэмминга 44. ъна выходе которого появляется исправленное информационное слово, котороезаписывается в выходной регистр 19 под воздействием сигнала по шине 32.Затем сигналом по шине 33 включается блок 3 ключей и считанная информация поступает на информационные шиныВ регистр 38 записывается синдром одиночной ошибки Прямого слова, а в регистр 39 " синдром одиночной ошибки инверсного слова. Коды двух синдромов определяют адрес постоянного накопителя 40, где записан адрес согласующего слова матрицы С (см. таблицу), хранящийся в постоянном накопителе 16.В таблице показана для примера образующая матрица модифицированного кода Хэмминга для двадцатиразрядного слова, шестнадцатиразрядного информационного слова 45 с четырехразрядной адресной информационной частью. Для кодирования данного двадцатиразрядного слова используются шесть контрольных разрядов 47. Коды адресов всех согласующих слов различны (первые четыре разряда каждого согласукнцего слова), два любых столбца матрицы С должны содержать все, сочетания 1 и 9 (00, 01,10, 11), одна строка матрицы С должна быть единичной.Подобная матрица С 48 такова, что при наличии двух любых дефектов в накопителе 22 по любому адресу в ней найдется кодовое слово, которое при сложении с информационным словом бу 1536445 0сбоев у 57 декодер ошибок не обнаруживает и синдром равен нулю.При считывании слова, в котором возник один сбой, например во втором разряде, у. 58 при декодировании синдФром равен 111110, что указывает ошибку во втором разряде. После исправления информация во втором разряде будет восстановлена (59), Первые четыре разряда слова 1100 являются адресом строки матрицы С 55, которая считывается из постоянного накопителя 16, складывается са словом 59 и информационная часть записывается в выходной регистр 19.Это слово соответствует записываемому слову 49. Таким образом, предлагаемое устройство обеспечивает исправление двойных дефектов оперативного накопителя 22 и одного сбоя, возникающего прихранении информации. Формула изобретения Запоминающее устройство с исправлением дефектов и ошибок, содержащее блок оперативной памяти, адресные входы которого являются соответствующими входами устройства, входной регистр, информационные входы которого соединены с выходами блока ключей и являются информационными входами-выходами устройства, информационные входы блока ключей соединены с выходами выходного регистра, блок постоянной памяти, выходы которого соединены с входами первой группы блока сумматоров по модулю два, выходы которого соединены с информационными входами выходного регистра, блок кодирования-декодирования, входы управления которого являются группой входов задания режима, вход синхронизации входного регистра является первым входом синхронизации устройства, вход синхронизации выходного регистра является четвертым входом синхронизации устройства, вход управления блока ключей является пятым входом Задания режима устройства, вход обращения блока оперативной памяти является соответствующим входом устройства, вход записи-чтения блока оперативной памяти является соответствующим входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок инверторов, дополнительный блок ключей, шиФратор, первый и второй 45 дет храниться по этому адресу безошибок,П р и м е р. Предположим, что навходы 1 поступает для записи шестнадцатиразрядное слово 110110001100011,На выходах 12 будет добавлен адрес0000 и после кодирования в блоке 10кодирования на выходах 14 появятсяконтрольные разряды 111110. 10В накопитель 22 запишется двадцатишестиразрядное слово х 49. Еслипри считывании этого же слова у; изнакопителя 22 в нем нет ошибок (50),то при декодировании в блоке 10 синдром 51 равен нулю (все разряды синдрома равны нулю). Если в данной ячейке накопителя 22 есть дефекты, например в шестом разряде (помечен звездочкой), вместо "1" считывается постоянно "0", то при считывании и декодировании слова у, (синдром ошибки%152) на выходах 14 блока 10 при декодировании появляется синдром 110100,который записывается в шифратор 15.Процесс записи продолжается. Входноеслово инвертируется блоком 5 инвер"торов и в виде слова х; 5311110001001110011100000001 записывается в накопитель 22, 30Если после считывания и декодиров+вания инвертированного слова у 54,будет обнаружена одиночная ошибка,например в тринадцатом разряде (вместо единицы постоянно считывается ЗБноль), то синдром будет равен011010.1(оды разрядов синдромов считанногопрямого 52 и инверсного 54 слов определяют строку матрицы С 48 (строка 40должна иметь ноль в шестом столбце иноль в тринадцатом столбце матрицыС 48).Данный подбор сочетаний синдромови строк матрицы С делается заранеепри программировании постоянногонакопителя 40 шифратора 15. В данномслучае нужной строкой матрицы С является слово 55 11003110000000001103300003,в котором в шестом разряде будетединица, а в тринадцатом - ноль.После сложения строки матрицы С;и исходного слова х в блоке сумматоров 11 по модулю дваполучим слово56 1100000011000110111001111, которое запишется в накопитель 22 безошибок.При считывании согласованного слова без возникновения при хранениикоммутаторы, выходы входного регистра соединены с информационными входами первой группы блока инверторов,информационные входы второй группыкоторого являются входами задания исходного режима работы устройства,прямые выходы блока инверторов соединены с информационными входами первой группы дополнительного блока ключей, входы второй группы которогосоединены с инверсными выходами блока инверторов, первые выходы дополнительного блока ключей соединены синформационными входами первой группы второго коммутатора, информационными входами-выходами первой группыпервого коммутатора, входами группыблока кодирования"декодирования, входами четвертой группы блока сумматоров по модулю два, выходы второйгруппы дополнительного блока ключейсоединены с информационными входамивыходами блока кодирования-декодирования, информационными входами-выхо-.дами третьей группы первого коммутатора и входами третьей группы блокасумматоров по модулю два, контрольные входы-выходы блока кодированиядекодирования соединены с информационными входами шифратора, информационными входами второй группы первогокоммутатора и входами второй группыблока сумматоров по модулю два, выходы блока сумматоров по модулю двасоединены с информационными входамигруппы первого коммутатора, выходывторого коммутатора соединены с адресными входами блока постоянной па О мяти, выходы шифратора соединены синформационными входами второй группывторого коммутатора, информационныевходы-выходи четвертой группы первого коммутатора соединены с информа циониыми входами-выходами блока оперативной памяти, вход .управления блока инверторов является первым входомзадания режима устройства, вход уп"равления дополнительного блока клю .чей является вторым входом заданиярежима устройства, вход управленияпервого коммутатора является первымвходом задания режима устройства,первый и второй входы синхронизации 25 шифратора являются соответственновторым и третьим входами синхронизации устройства, входы управленияблока ключей и второго коммутатораявляются соответственно третьим и 30 четвертым входами задания режимаустройства.Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 1 Заказ 112 Тираж 474 ВНИИПИ Государственного комитета по 113035, Москва, Ж-ЗПодпи своеобретениям и открытиям при ГКНТ СССРРаушская наб., д, 4/5

СмотретьЗаявка

4256899, 04.06.1987

ПРЕДПРИЯТИЕ ПЯ В-8835

КОМАРОВ ВАЛЕНТИН ДАНИЛОВИЧ, КУЗНЕЦОВ АЛЕКСАНДР ВАСИЛЬЕВИЧ, КУХАРЕВ АЛЕКСАНДР ДМИТРИЕВИЧ, ТРОФИМОВ ЮРИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G11C 29/00

Метки: дефектов, запоминающее, исправлением, ошибок

Опубликовано: 15.01.1990

Код ссылки

<a href="https://patents.su/7-1536445-zapominayushhee-ustrojjstvo-s-ispravleniem-defektov-i-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с исправлением дефектов и ошибок</a>

Предыдущий патент: Устройство для контроля многоразрядных блоков памяти

Следующий патент: Запоминающее устройство с контролем

Случайный патент: Гидросистема