Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1383468

Автор: Чистяков

Текст

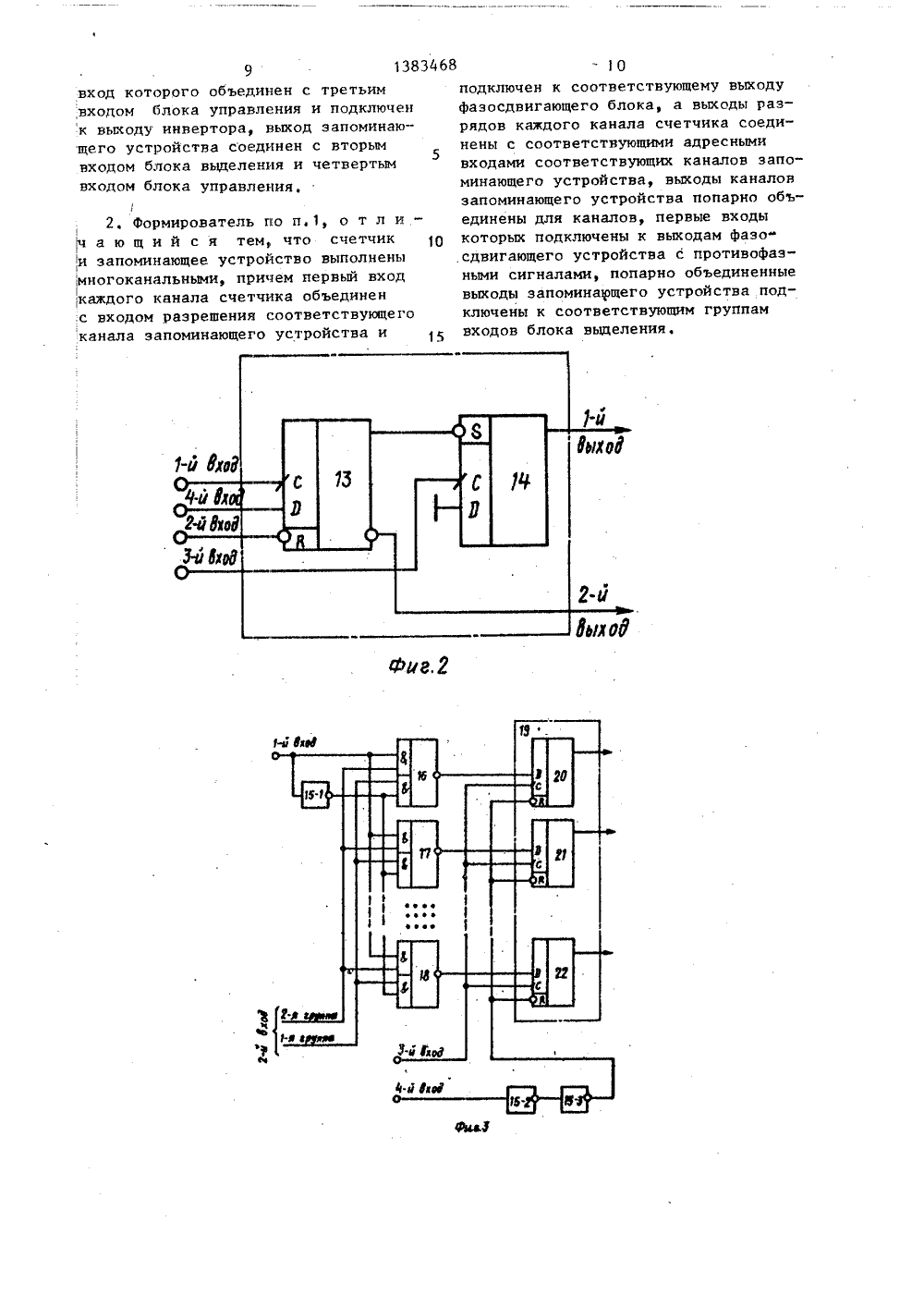

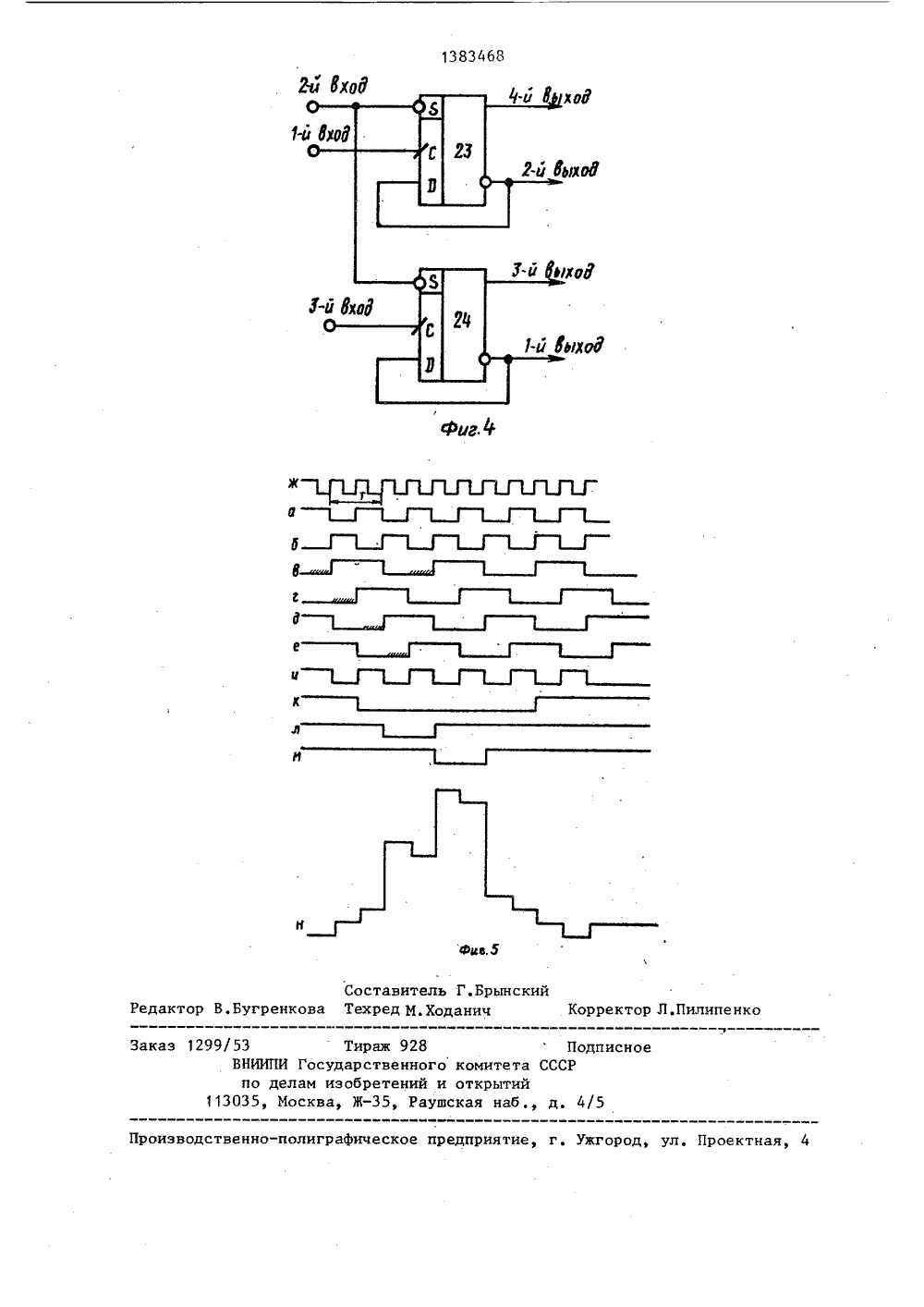

венно на первом, втором, третьем ичетвертом выходах фазосдвигающегоблока 4; с - сигнал на выходе генератора тактовых импульсов 2 О - сигнал5на выходе первого разряда блока 9 выделения; к - сигнал на выходе второгоразряда блока 9 вьделения; Л - сигнална выходе третьего разряда блока 9вьделения; М - сигнал на выходе четвертого разряда блока 9 вьделения;Н - сигнал на выходе 12 ЦАП 11; Т -период сигнала на выходе делителя 10,Генератор 2 тактовых импульсовреализуется на микросхемах 530 ГГ 1 и530 ЛН 1, при этом на микросхеме 530 ГГ 1реализуется управляемый генераторимпульсов - в соответствии с типовойсхемой, рекомендованной техническимиусловиями на микросхему. Сигнал свхода генератора 2 на управляющийвход микросхемы 530 ГГ 1 подается черезинвертор на микросхеме 530 ЛН 1.Триггер 3 выполнен на микросхеме530 ТМ 2, при этом первый вход является 25Я-входом установки единичного состояния, второй - информационным П-входом, третий - синхрониэирующим С-входом.Фазосдвигающий блок 4 выполнен всоответствии с фиг.4 на микросхеме530 ТМ 2. При этом для удобства рас-.смотрения принципа действия на фиг.4дан вариант реализации фаэосдвигающего блока 4 для формирования сигналов35с четырьмя фазами.Инвертор 5 реализуется на микросхеме 530 ЛН 1,Счетчик 6 выполнен многоканальным - по числу фаз фазосдвигающего 40блока 4, на микросхемах типа 530 ИЕ 17,включенных по типовой схеме в соответствии с техническими условиями наних. При этом входы синхронизациимикросхем 530 ИЕ 17 каждого канала45(первый вход счетчика 6) объединеныи подключены к соответствующему вы-:ходу фаэосдвигающего блока 4. Второйвход счетчика 6 образован объединенными входами разрешения записи информации в параллельном коде всех каналов (всех микросхем 530 ИЕ 17), приэтом информационные входы параллельного кода всех микросхем 530 ИЕ 17 соединены с общей точкой схемы (уровеньлогического нуля), Запоминающее устройство 7 реализуется на микросхемахтипа 556 РТ 7 в многоканальном варианте - по числу каналов счетчика 6При этом адресные входы запоминающего устройства в каждом канале подключены к выходам разрядов соответствующего канала счетчика 6, а входы разрешения выборки информации микросхем 556 РТ 7 каждого из каналов (первый вход запоминающего устройства 7) подсоединены к входу синхронизации соответствующего канала счетчика 6 и соответствующему выходу фазосдвигающего устройства 4. Выходы микросхем 556 РТ 7 каналов, входы разрешения выборки которых подключены к противофазным сигналам, объединены между собой и образуют (для четырехканального варианта) соответственно первую и вторую группы выходов запоминающего устройства 7, подсоединенных к соответствующим входам блока 9 вьделения (фиг.З) . В качестве выхода, соединенного с четвертым входом блока 8 управления, служит один из выходных разрядов запоминающего устройства 7.Блок 8 управления выполнен на микросхеме 530 ТМ 2 по схеме, приведенной на фиг,2,при этом единичный выход триггера 13 соединен с входом Я установки единичного состояния триггера 14, выход которого подключен к первому выходу блока 8 управления, а вход С синхронизации триггера 14 соединен с третьим входом блока 8 управления, первый вход которого подключен к входу С синхронизации триггера 13, второй вход - к входу К установки нулевого состояния триггера 13, четвертый - к информационному входу триггера 13, нулевой выход которого соединен с вторым выходом блока 8 управления.Блок 9 вьделения реализуется на логических элементах микросхем типа 530 ЛР 11, 530 ЛН 1 и 530 ТМ 2 в соответствии с фиг,З, При этом буферный регистр 19 образован из Р триггеров микросхем 530 ТМ 2Делитель 10 выполнен на триггере микросхемы 530 ТМ 2, информационный П-вход которого соединен с нулевым выходом, первый вход делителя 10 подключен к входу С синхронизации, а второй вход делителя 10 соединен с входом 8 установки единичного состояния укаэанного триггера,Цифроаналоговый преобразователь 11 реализован в виде резпстивной матрицы, выполненной на резисторах С 2-3613834689вход которого объединен с третьим входом блока управления и подключен к выходу инвертора, выход запоминающего устройства соединен с вторым входом блока выделения и четвертым входом блока управления,2, формирователь по и, 1, о т л и - ч а ю щ и й с я тем что счетчик ,и запоминающее устройство выполнены многоканальными, причем первый вход ,каждого канала счетчика объединен с входом разрешения соответствующего канала запоминающего устройства и подключен к соответствующему выходуфазосдвигающего блока, а выходы разрядов каждого канала счетчика соединены с соответствующими адреснымивходами соответствующих каналов запоминающего устройства, выходы каналовзапоминающего устройства попарно объединены для каналов, первые входыкоторых подключены к выходам фазосдвигающего устройства с противофазными сигналами, попарно объединенныевыходы запоминащего устройства подключены к соответствующим группамвходов блока вьщеления.1383468 хоР Составитель Г.БрынсРедактор В.Бугренкова Техред М.Ходанич орректор Л.Пилипенко 8 каз 1299/53 Тираж ВНИИПИ Государст по делам изобре 113035, Москва, ЖПодписноСР енного ком ений и откРаушская тета т 5 а Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектна

СмотретьЗаявка

4099314, 31.07.1986

ПРЕДПРИЯТИЕ ПЯ Г-4421

ЧИСТЯКОВ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

Метки: импульсов, формирователь

Опубликовано: 23.03.1988

Код ссылки

<a href="https://patents.su/7-1383468-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Формирователь импульсов

Следующий патент: Индикаторная головка измерителя мощности сверхвысоких частот

Случайный патент: Машина для уборки бахчевых культур