Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1282326

Автор: Петренко

Текст

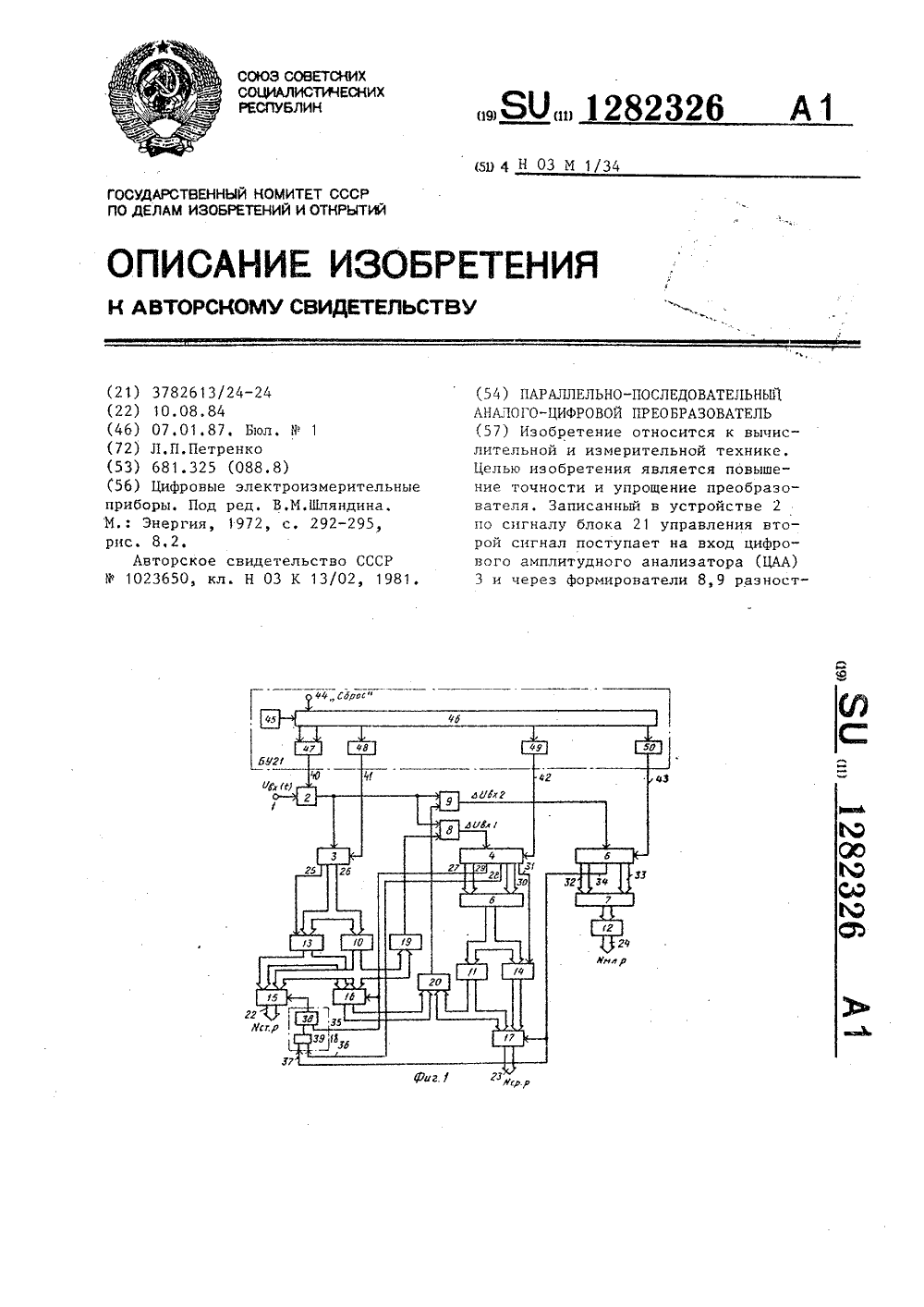

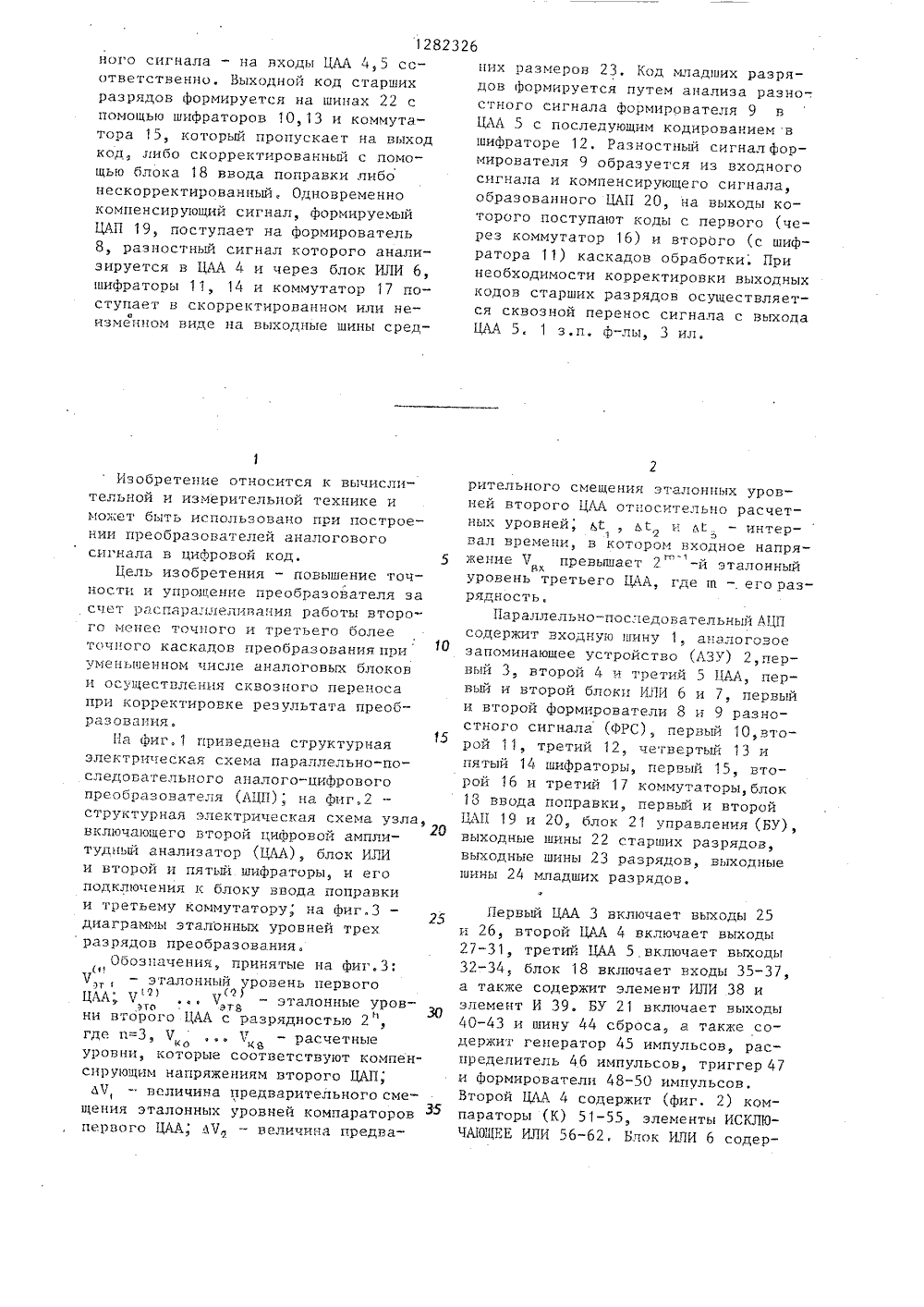

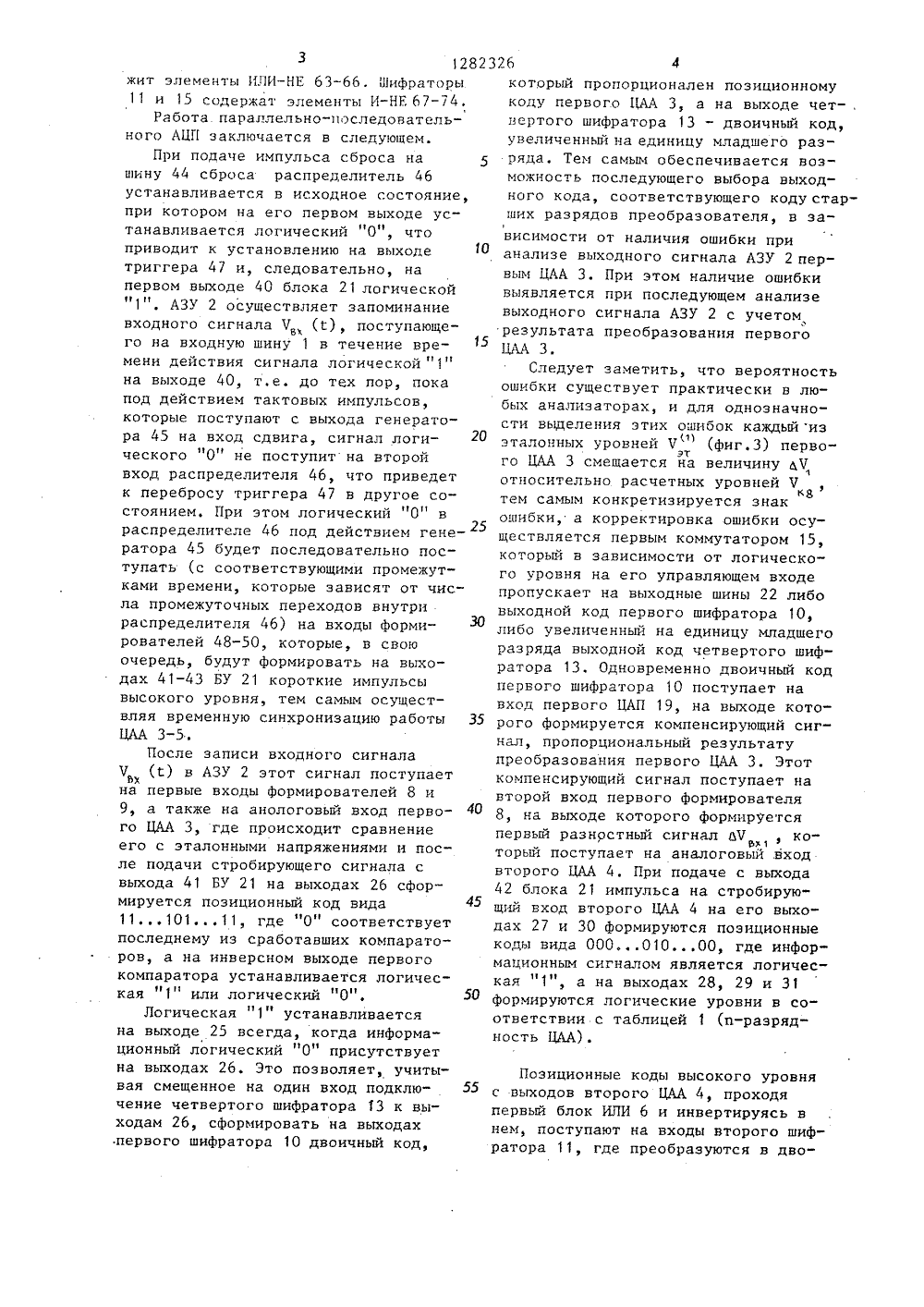

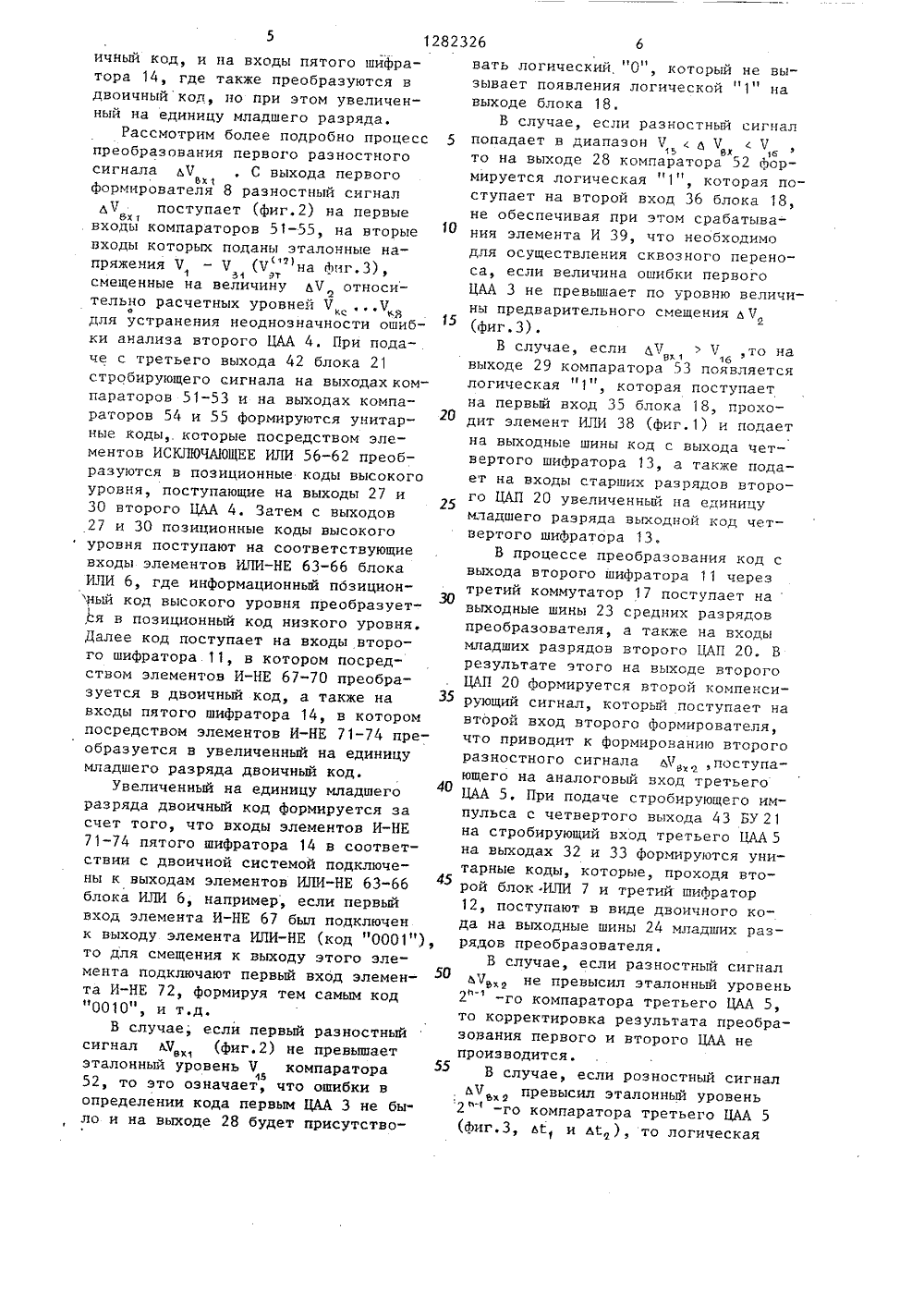

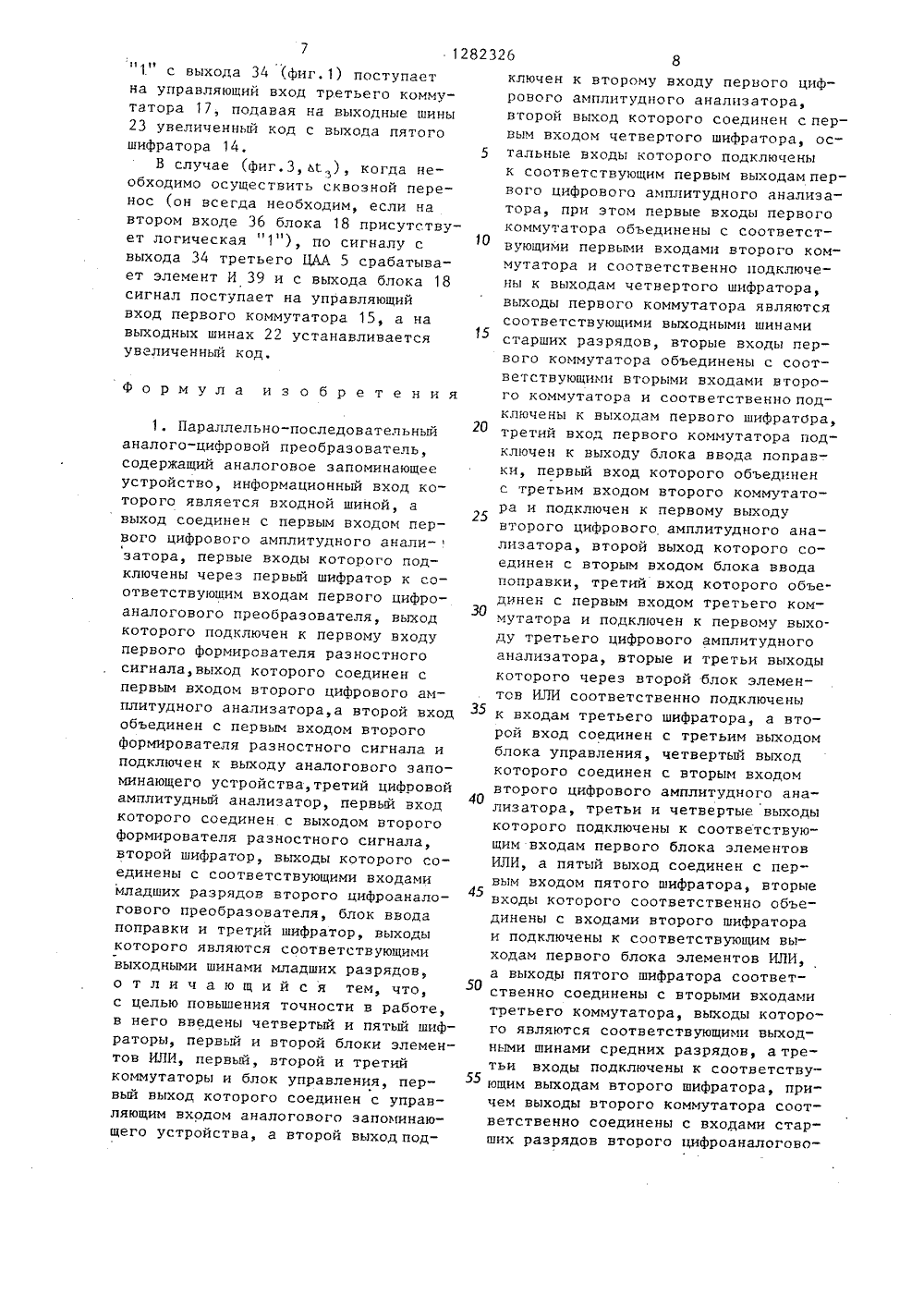

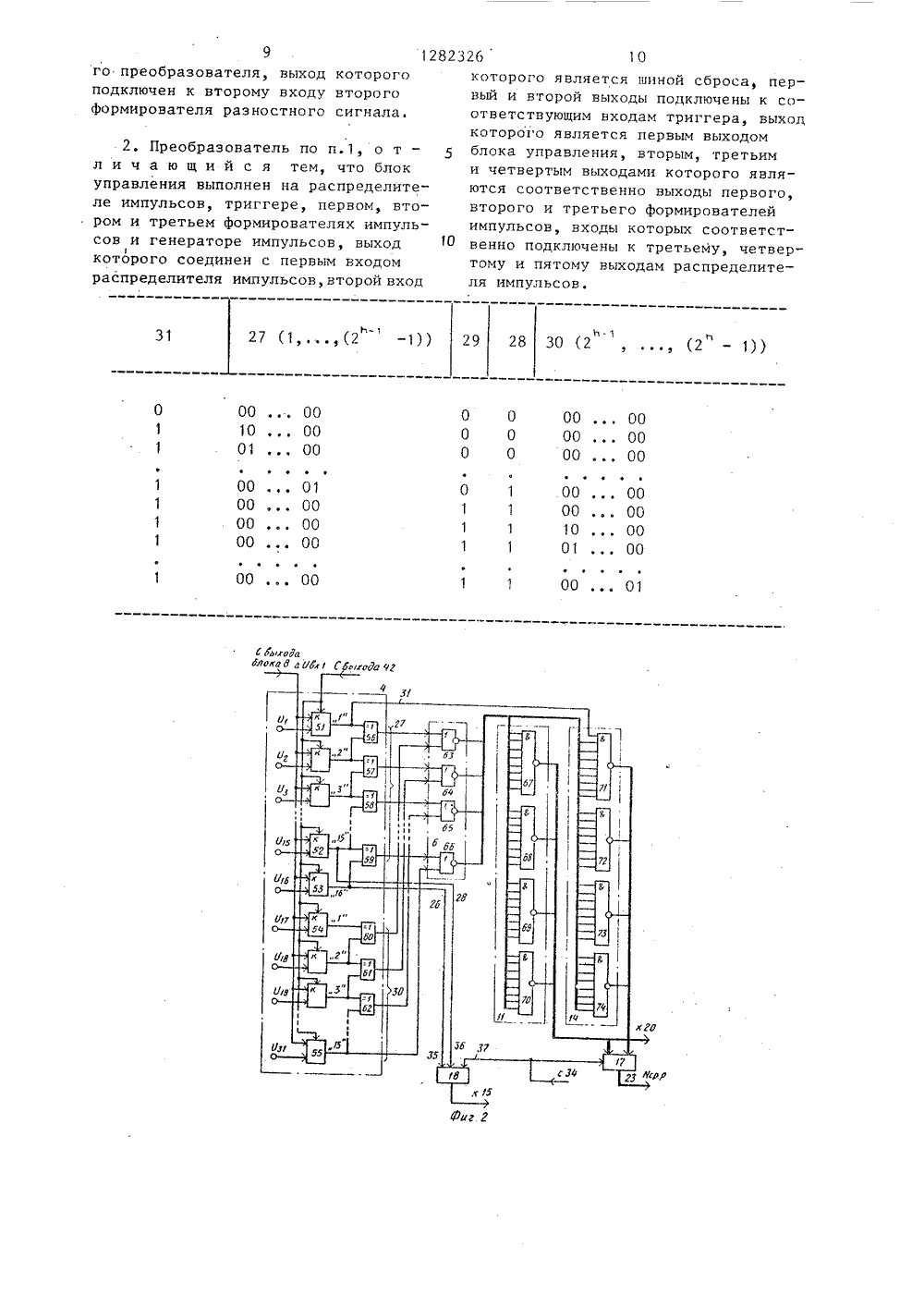

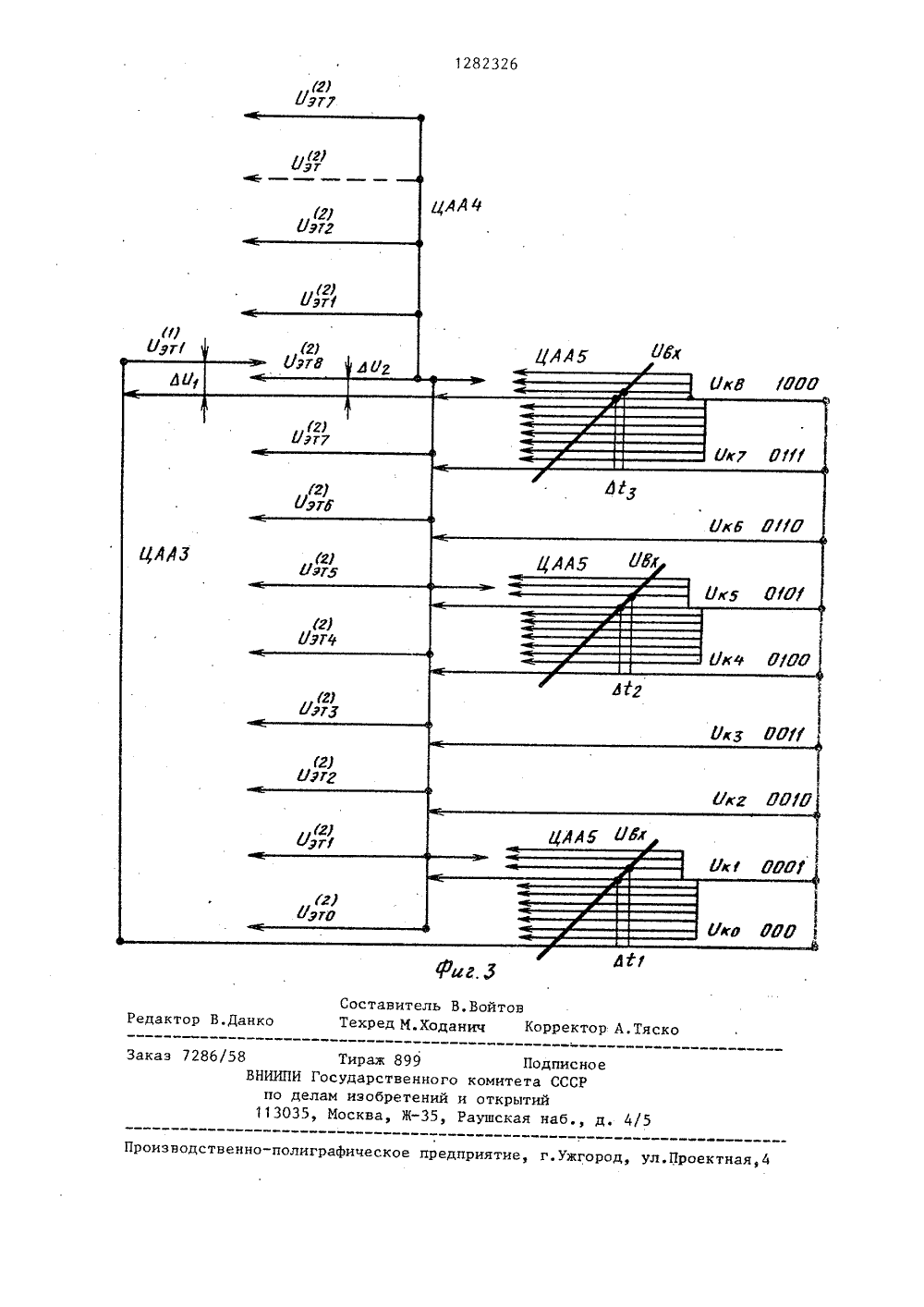

(5 3 М 1/34 ГОСУДАРСТВЕННЫЙ ПО ДЕЛАМ ИЗОБРЕ ОМИТЕТ С ИЙ ИОТН САНИЕ ИЗОБРЕТЕ роизмерительны(57) Изобретение относится к вычислительной и измерительной технике,Целью изобретения является повышение точности и упрощение преобразователя, Записанный в устройстве 2по сигналу блока 21 управления второй сигнал поступает на вход цифрового амплитудного анализатора (ЦАА)3 и через формирователи 8,9 разност1282326 ного сигнала - на входы ЦАА 4,5 соответственно. Выходной код старших разрядов формируется на шинах 22 с помощью цифраторов 10, 13 и коммута. - тора 15, который пропускает на выход коп, либо скорректированный с помощью блока 18 ввода поправки либо нескорректированный, Одновременно компенсирующий сигнал, формируемый ЦАП 19, поступает на формирователь 8, разностный сигнал которого анализируется в ЦАА 4 и через блок ИЛИ 6, шифраторы 11, 14 и коммутатор 17 поступает в скорректированном или неоизменном вице на выходные шины средних размеров 23, Код младших разрядов формируется путем анализа разно-.стного сигнала формирователя 9 вЦАА 5 с последующим кодированием вшифраторе 12. Разностный сигнал формирователя 9 образуется из входногосигнала и компенсирующего сигнала,образованного ЦАП 20, на выходы которого поступают коды с первого (через коммутатор 16) и второго (с шифратора 11) каскадов обработки. Принеобходимости корректировки выходныхкодов старших разрядов осуществляется сквозной перенос сигнала с выходаЦАА 5 с 1 зепе ф лыу 3 илеИзобретение относится к вычислительной и измерительной технике и может быть использовано при построении преобразователей аналогового сигнала в цифровой код,Цель изобретения - повышение точности и упрошение преобразователя за счет распараллеливания работы второго менее точного и третьего более точного каскадов преобразования приуменьшенном числе аналоговых блокови осуществления сквозного переносапри корректировке результата преобразования,На Фиг,1 приведена структурная15электрическая схема параллельно-последовательного аналого-цифровогопреобразователя (АЦП); на Фиг,2структурная электрическая схема узла,включающего второй цифровой амплитудный анализатор (ЦАА), блок ИЛИи второй и пятый шифраторы, и егоподключения к блоку ввода поправкии третьему коммутатору, на Фиг.Здиаграммы эталонных уровней трехразрядов преобразования.Обозначения, принятые на фиг,З:(1Ч - эталонный уровень первогоЦАА 9. Ч1 эталонные уров(ц) (0)то . этзнни второго ЦАА с разрядностью 2 ,где п=З ЧЧ, - расчетныеуровни, которые соответствуют компенсирующим напряжениям второго ЦАП;ЬЧ, - величина предварительного смещения эталонных уровней компараторовпервого ЦАА .ЛЧ - величина предварительного смещения эталонных уровней второго ЦАА относительно расчетных уровней ьй ьГ. и ьг - интерйвал времени, в котором входное напрят-жение Ч превышает 2 -й эталонныйвхуровень третьего ЦАА, где ш - . его разрядность.Параллельно-последовательный АЦПсодержит входную шину 1, аналоговоезапоминающее устройство (АЗУ) 2,первый 3, второй 4 и третий 5 ЦАА первый и второй блоки ИЛИ 6 и 7, первыйи второй формирователи 8 и 9 разностного сигнала (ФРС), первьц) 10,второй 11, третий 12, четвертый 13 ипятый 14 шифраторы, первый 15, второй 16 и третий 17 коммутаторы, блок18 ввода поправки, первьп и второйЦАП 19 и 20, блок 21 управления (БУ),выходные шины 22 старших разрядов,выходные шины 23 разрядов, выходныешины 24 младших разрядов,11 ервый ЦАА 3 включает выходы 25 и 26, второй ЦАА 4 включает выходы 27-31, третий ЦАА 5 включает выходы 32-34, блок 18 включает входы 35-37, а также содержит элемент ИЛИ 38 и элемент И 39. БУ 21 включает выходы 40-43 и шину 44 сброса, а также содержит генератор 45 импульсов, распределитель 46 импульсов, триггер 47 и Формирователи 48-50 импульсов. Второй ЦАА 4 содержит (фиг, 2) компараторы (К) 51-55, элементы ИСКЛЮЧА 10 щЕЕ ИЛИ 56-62, Блок ИЛИ 6 содер 3 12823 жит элементы ИЛИ-НЕ 63-66. Иифраторы 11 и 15 содержат элементы И-НЕ 67-74,Работа параллельно-последовательного АЦП заключается в следующем.При подаче импульса сброса на 5 шину 44 сброса распределитель 46 устанавливается в исходное состояние, при котором на его первом выходе устанавливается логический "0", что приводит к установлению на выходе триггера 47 и, следовательно, на первом выходе 40 блока 21 логической "1". АЗУ 2 осуществляет запоминание входного сигнала Ч(1), поступающего на входную шину"1 в течение вре мени действия сигнала логической "1" на выходе 40, т.е. до тех пор, пока под действием тактовых импульсов, которые поступают с выхода генератора 45 на вход сдвига, сигнал логического 0 не поступитна второй вход распределителя 46, что приведет к перебросу триггера 47 в другое состоянием. При этом логический "Оп в распределителе 46 под действием генератора 45 будет последовательно поступать (с соответствующими промежутками времени, которые зависят от числа промежуточных переходов внутри распределителя 46) на входы формирователей 48-50, которые, в свою очередь, будут Формировать на выходах 41-43 БУ 21 короткие импульсы высокого уровня, тем самым осуществляя временную синхронизацию работы 35 ЦАА 3-5.После записи входного сигнала Ч (1;) в АЗУ 2 этот сигнал поступает ьхна первые входы формирователей 8 и 9, а также на анологовый вход перво го ЦАА 3, где происходит сравнение его с эталонными напряжениями и после подачи стробирующего сигнала с выхода 41 БУ 21 на выходах 26 сформируется позиционный код вида 45 1110111, где "0" соответствует последнему из сработавших компараторов, а на инверсном выходе первого компаратора устанавливается логическая "1" или логический "0", 50Логическая "1" устанавливается на выходе 25 всегда, когда информационный логический 0" присутствует на выходах 26. Это позволяет, учитывая смещенное на один вход подклю чение четвертого шифратора 13 к выходам 26, сформировать на выходах .первого шифратора 10 двоичный код,который пропорционален позиционному коду первого ЦАА 3, а на выходе чет-, вертого шифратора 13 - двоичный код, увеличенный на единицу младшего разряда, Тем самым обеспечивается возможность последующего выбора выходного кода, соответствующего коду старших разрядов преобразователя, в зависимости от наличия ошибки прианализе выходного сигнала АЗУ 2 первым ЦАА 3. При этом наличие ошибкивыявляется при последующем анализевыходного сигнала АЗУ 2 с учетомрезультата преобразования первогоЦАА 3,Следует заметить, что вероятностьошибки существует практически в любых анализаторах, и для однозначности выделения этих ошибок каждый изэталонных уровней Ч (фиг.3) перво(1)этго ЦАА 3 смещается на величину д 71относительно расчетных уровней ЧКЯтем самым конкретизируется знакошибки, а корректировка ошибки осуществляется первым коммутатором 15,который в зависимости от логического уровня на его управляющем входепропускает на выходные шины 22 либовыходной код первого шифратора 10,либо увеличенный на единицу младшегоразряда выходной код четвертого шифратора 13. Одновременно двоичный кодпервого шифратора 10 поступает навход первого ЦАП 19, на выходе которого Формируется компенсирующий сигнал, пропорциональный результатупреобразования первого ЦАА 3. Этоткомпенсирующий сигнал поступает навторой вход первого формирователя8, на выходе которого формируетсяпервый разностный сигнал 67который поступает на аналоговыи входвторого ЦАА 4. При подаче с выхода42 блока 21 импульса на стробирующий вход второго ЦАА 4 на его выходах 27 и 30 формируются позиционныекоды вида 00001000, где информационным сигналом является логическая "1", а на выходах 28, 29 и 31формируются логические уровни в соответствии с таблицей 1 (и-разрядность ЦАА). Позиционные коды высокого уровня с выходов второго ЦАА 4, проходя первый блок ИЛИ 6 и инвертируясь в нем, поступают на входы второго шифратора 11, где преобразуются в дво 1282326ичный код, и на входы пятого шифратора 14, где также преобразуются в двоичный код, но при этом увеличенный на единицу младшего разряда.Рассмотрим более подробно процесс преобразования первого разностного сигнала дЧ , С выхода первогобхтФормирователя 8 разностный сигнал дЧ поступает (фиг.2) на первыебхтвходы компараторов 51-55, на вторые входы которых поданы эталонные напряжения Ч - Ч (Ч "на Фиг,З),5 т тсмещенные на величину ьЧ относительно расчетных уровней Ч, Чодля устранения неоднозначности ошибки анализа второго ЦАА 4. При подаче с третьего выхода 42 блока 21 стробирующего сигнала на выходах компараторов 51-53 и на выходах компараторов 54 и 55 формируются унитарные коды, которые посредством элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 56-62 преобразуются в позиционные коды высокого уровня, поступающие на выходы 27 и 30 второго ЦАА 4. Затем с выходов 27 и ЗО позиционные коды высокого уровня поступают на соответствующие входы элементов ИЛИ-НЕ 63-66 блока ИЛИ 6, где информационный пбзиционный код высокого уровня преобразует,ся в позиционный код низкого уровня, Далее код поступает на входы второго шифратора 11, в котором посредством элементов И-НЕ 67-70 преобразуется в двоичный код, а также на входы пятого шифратора 14, в котором посредством элементов И-НЕ 71-74 преобразуется в увеличенный на единицу младшего разряда двоичный код.Увеличенный на единицу младшего разряда двоичный код формируется за счет того, что входы элементов И-НЕ 71-74 пятого шифратора 14 в соответствии с двоичной системой подключены к выходам элементов ИЛИ-НЕ 63-66 блока ИЛИ 6, например, если первый вход элемента И-НЕ 67 был подключен к выходу элемента ИЛИ-НЕ (код "0001") то для смещения к выходу этого элемента подключают первый вход элемента И-НЕ 72, формируя тем самым код "0010", и т.д.В случае, если первый разностный сигнал дЧ , (фиг.2) не превышает эталонный уровень Ч компаратора1552, то это означает, что ошибки в определении кода первым ЦАА 3 не было и на выходе 28 будет присутствовать логический, 0, который не вызывает появления логической "1" навыходе блока 18.В случае, если разностный сигнал 5 попадает в диапазон Ч с д Ч с Чт 5 ьх тбто на выходе 28 компаратора 52 Формируется логическая "1", которая поступает на второй вход 36 блока 18,не обеспечивая при этом срабатывания элемента И 39, что необходимодля осуществления сквозного переноса, если величина ошибки первогоЦАА 3 не превышает по уровню величины предварительного смещения дЧ(Фиг.3).В случае, если дЧЧ ,то навыходе 29 компаратора 53 появляетсялогическая "1", которая поступаетна первый вход 35 блока 18, проходит элемент ИЛИ 38 (Фиг,1) и подаетна выходные шины код с выхода четвертого шифратора 13, а также подает на входы старших разрядов второго ЦАП 20 увеличенный на единицумладшего разряда выходной код четвертого шифратора 13,В процессе преобразования код свыхода второго шифратора 11 черезтретий коммутатор 17 поступает навыходные шины 23 средних разрядовпреобразователя, а также на входымладших разрядов второго ЦАП 20. Врезультате этого на выходе второгоЦАП 20 формируется второй компенси 35 рующий сигнал, который поступает навторой вход второго Формирователя,что приводит к формированию второгоразностного сигнала дЧ х,поступающего на аналоговый вход третьего40ЦАА 5. При подаче стробирующего импульса с четвертого выхода 43 БУ 21на стробирующий вход третьего ЦАА 5на выходах 32 и 33 формируются унитарные коды, которые, проходя второй блок ИЛИ 7 и третий шифратор12, поступают в виде двоичного кода на выходные шины 24 младших разрядов преобразователя.В случае, если разностный сигналдЧне превысил эталонный уровень2"-го компаратора третьего ЦАА 5,то корректировка результата преобразования первого и второго ЦАА непроизводится.В случае, если розностный сигналдЧпревысил эталонный уровень2" -го компаратора третьего ПАА 51. Параллельно-последовательный аналого-цифровой преобразователь, содержащий аналоговое запоминающее устройство, информационный вход которого является входной шиной, а выход соединен с первым входом первого цифрового амплитудного анали-затора, первые входы которого подключены через первый шифратор к соответствующим входам первого цифроаналогового преобразователя, выход которого подключен к первому входу первого формирователя разностного сигнала, выход которого соединен с первым входом второго цифрового амплитудного анализатора,а второй вход объединен с первым входом второго формирователя разностного сигнала и подключен к выходу аналогового запоминающего устройства, третий цифровой амплитудный анализатор, первый вход которого соединен с выходом второго формирователя разностного сигнала, второй шифратор, выходы которого соединены с соответствующими входами младших разрядов второго цифроаналогового преобразователя, блок ввода поправки и третий шифратор, выходы которого являются соответствующими выходными шинами младших разрядов, о т л и ч а ю щ и й с я тем, что, с целью повышения точности в работе, в него введены четвертый и пятый шифраторы, первый и второй блоки элементов ИЛИ, первый, второй и третий коммутаторы и блок управления, первый выход которого соединен с управляющим входом аналогового запоминающего устройства, а второй выход под 45 50 55"1." с выхода 34 (фиг.1) поступает на управляющий вход третьего коммутатора 17, подавая на выходные шины 23 увеличенный код с выхода пятого шифратора 14В случае (фиг.3, ьС), когда необходимо осуществить сквозной перенос (он всегда необходим, если на втором входе 36 блока 18 присутствует логическая "1"), по сигналу с выхода 34 третьего ЦАА 5 срабатывает элемент И 39 и с выхода блока 18 сигнал поступает на управляющий вход первого коммутатора 15, а на выходных шинах 22 устанавливается увеличенный код. Формула изобретения 5 10 15 20 25 30 35 40 ключен к второму входу первого цифрового амплитуцного анализатора,второй выход которого соединен с первым входом четвертого шифратора, остальные входы которого подключенык соответствующим первым выходампервого цифрового амплитудного анализатора, при этом первые входы первого коммутатора объединены с соответствующими первыми входами второго коммутатора и соответственно подключены к выходам четвертого шифратора, выходы первого коммутатора являются соответствующими выходными шинами старших разрядов, вторые входы первого коммутатора объединены с соответствующими вторыми входами второго коммутатора и соответственно подключены к выходам первого шифратора, третий вход первого коммутатора подключен к выходу блока ввода поправ-. ки, первый вход которого объединен с третьим входом второго коммутатора и подключен к первому выходу второго цифрового амплитудного анализатора, второй выход которого соединен с вторым входом блока ввода поправки, третий вход которого объединен с первым входом третьего коммутатора и подключен к первому выходу третьего цифрового амплитудного анализатора, вторые и третьи выходы которого через второй блок элементов ИЛИ соответственно подключены к входам третьего шифратора, а второй вход соединен с третьим выходом блока управления, четвертый выход которого соединен с вторым входом второго цифрового амплитудного анализатора, третьи и четвертые выходы которого подключены к соответствующим входам первого блока элементовИЛИ, а пятый выход соединен с первым входом пятого шифратора, вторые входы которого соответственно объединены с входами второго шифратораи подключены к соответствующим выходам первого блока элементов ИЛИ, а выходы пятого шифратора соответственно соединены с вторыми входамитретьего коммутатора, выходы которого являются соответствующими выходными шинами средних разрядов, атретьи входы подключены к соответствующим выходам второго шифратора, причем выходы второго коммутатора соответственно соединены с входами старших разрядов второго цифроаналогово2 б 10 которого является шиной сброса, первый и второй выходы подключены к соответствующим входам триггера, выходкоторого является первым выходомблока управления, вторым, третьими четвертым выходами которого являются соответственно выходы первого,второго и третьего формирователейимпульсов, входы которых соответственно подключены к третьему, четвертому и пятому выходам распределителя импульсов,27 (1(2 -1 29 31 28 0 0000 1000 0100 0 0 0 0 0 0 0000 0000 000001000000 0 1 1 1Ф00 00 00 00000001 00ЬчоРаооогод ои,иг 9 12823 го преобразователя, выход которого подключен к второму входу второго формирователя разностного сигнала. 2, Преобразователь по п.1, о т л и ч а ю щ и й с я тем, что блок управления выполнен на распределителе импульсов, триггере, первом, втором и третьем формирователях импульсов и генераторе импульсов, выход 10которого соединен с первым входом распределителя импульсов, второй вход 30 (2 , , (2 - 1

СмотретьЗаявка

3782613, 10.08.1984

ПРЕДПРИЯТИЕ ПЯ В-2201

ПЕТРЕНКО ЛЕВ ПЕТРОВИЧ

МПК / Метки

МПК: H03M 1/34

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 07.01.1987

Код ссылки

<a href="https://patents.su/7-1282326-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Фотоэлектрический датчик положения

Следующий патент: Аналого-цифровой преобразователь

Случайный патент: Мозаичная печатающая головка