Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1259262

Автор: Потоков

Текст

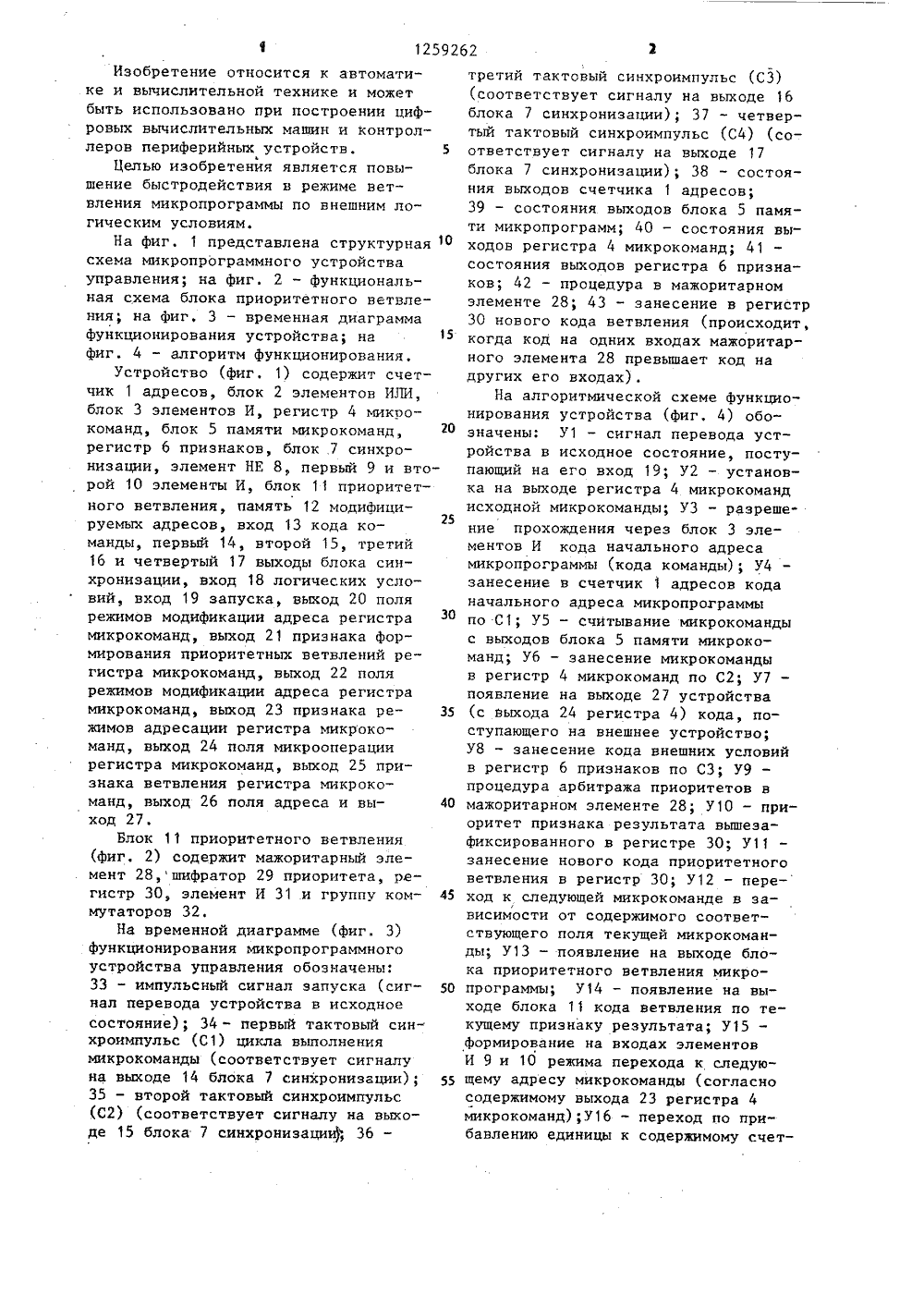

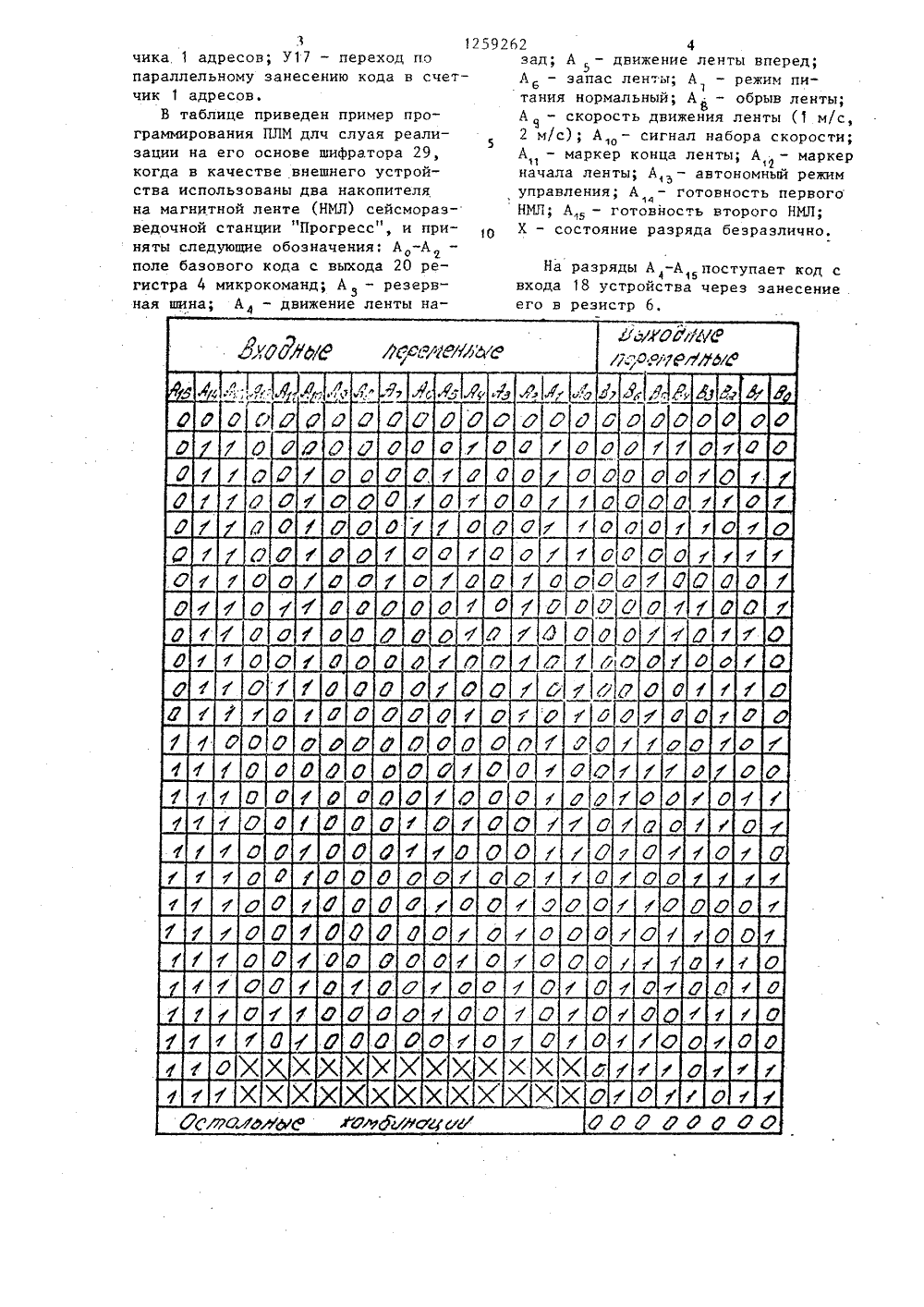

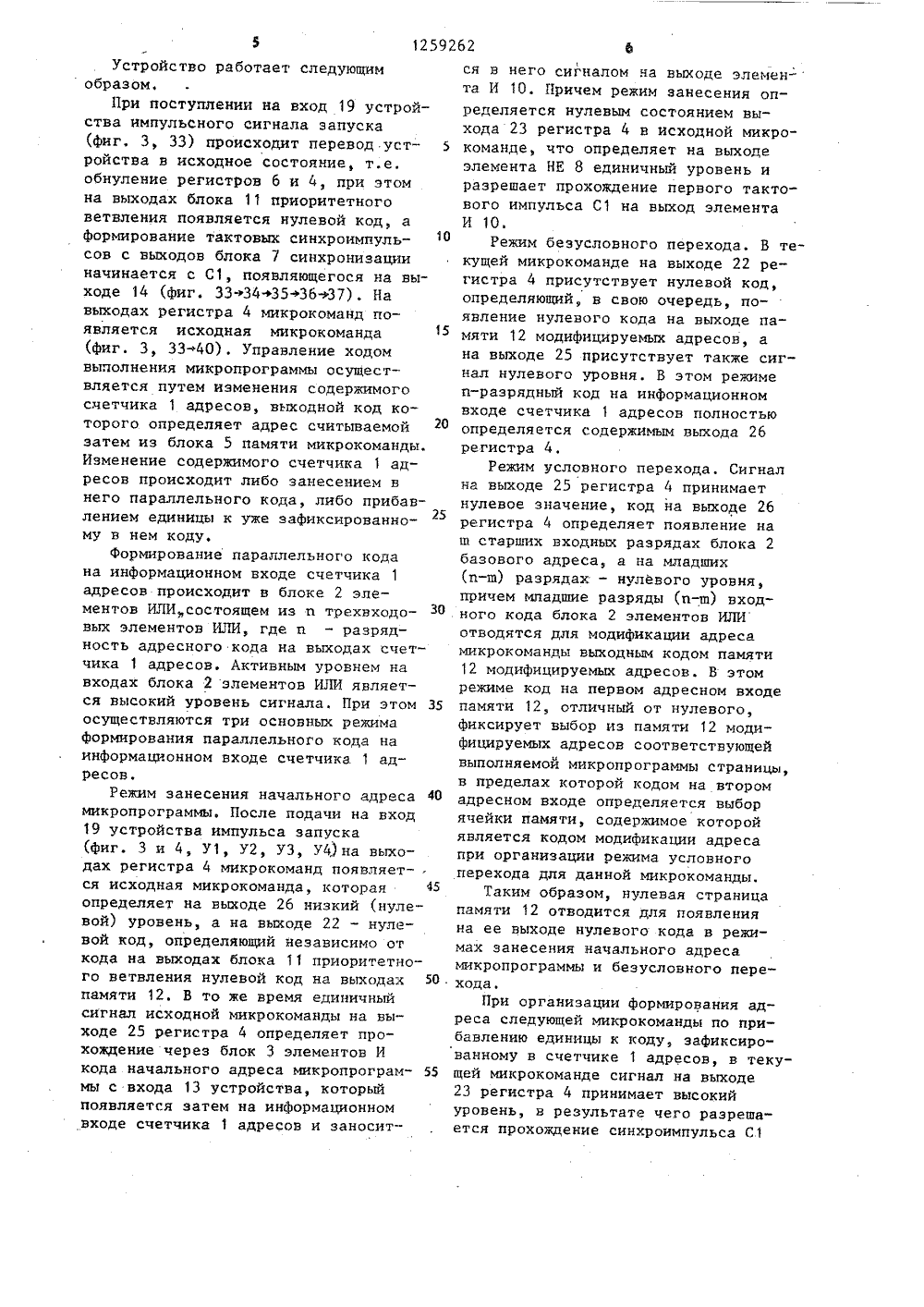

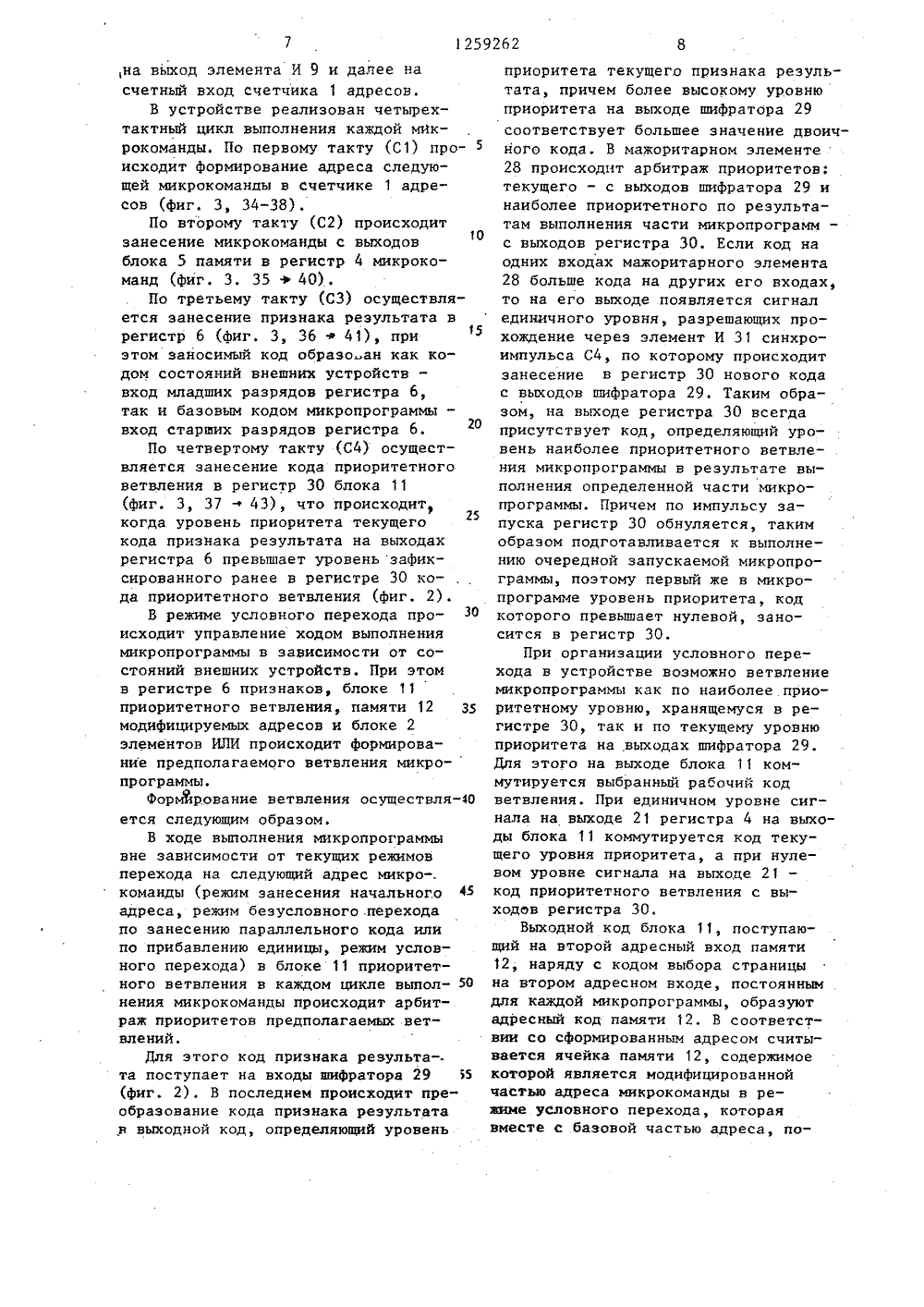

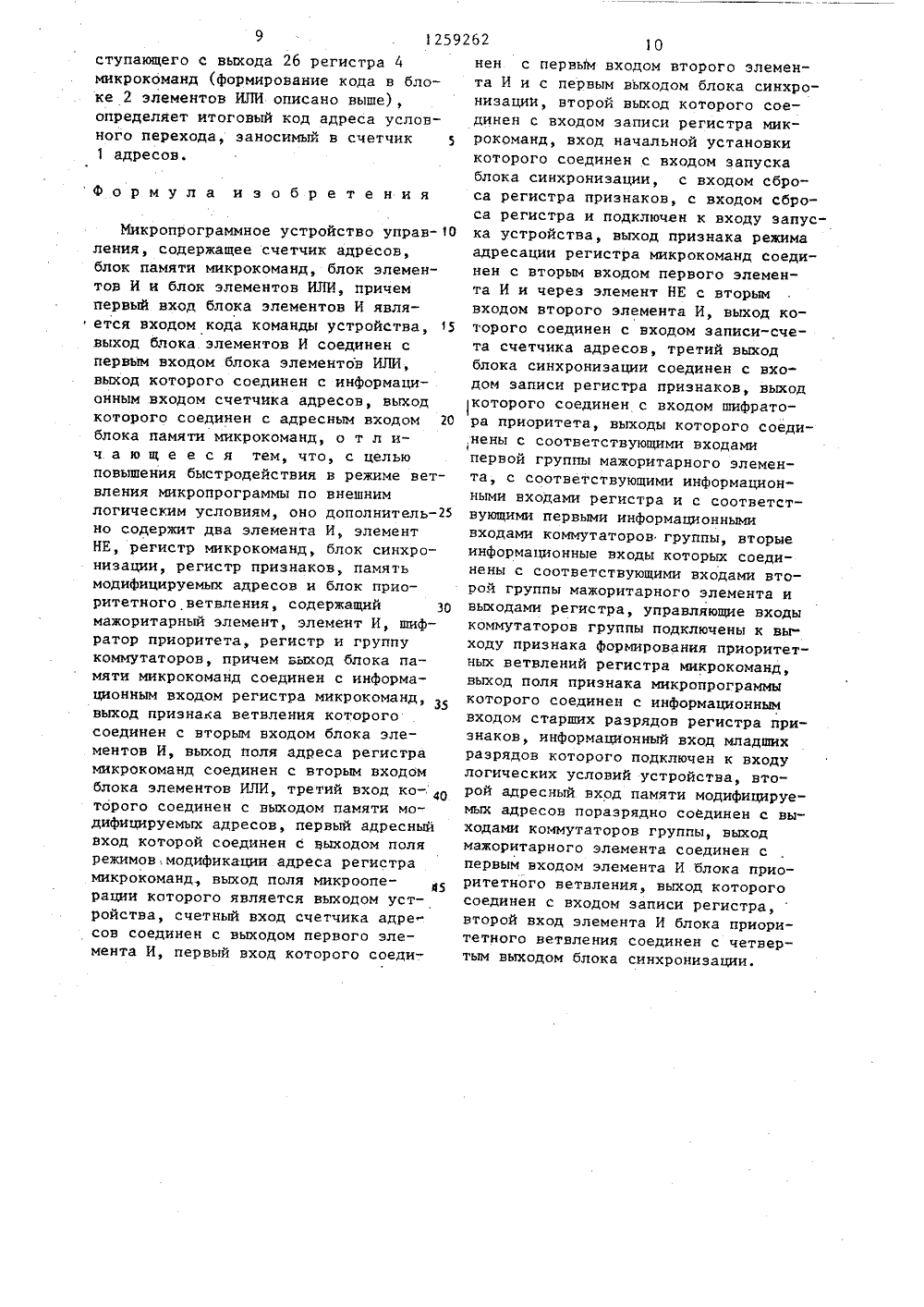

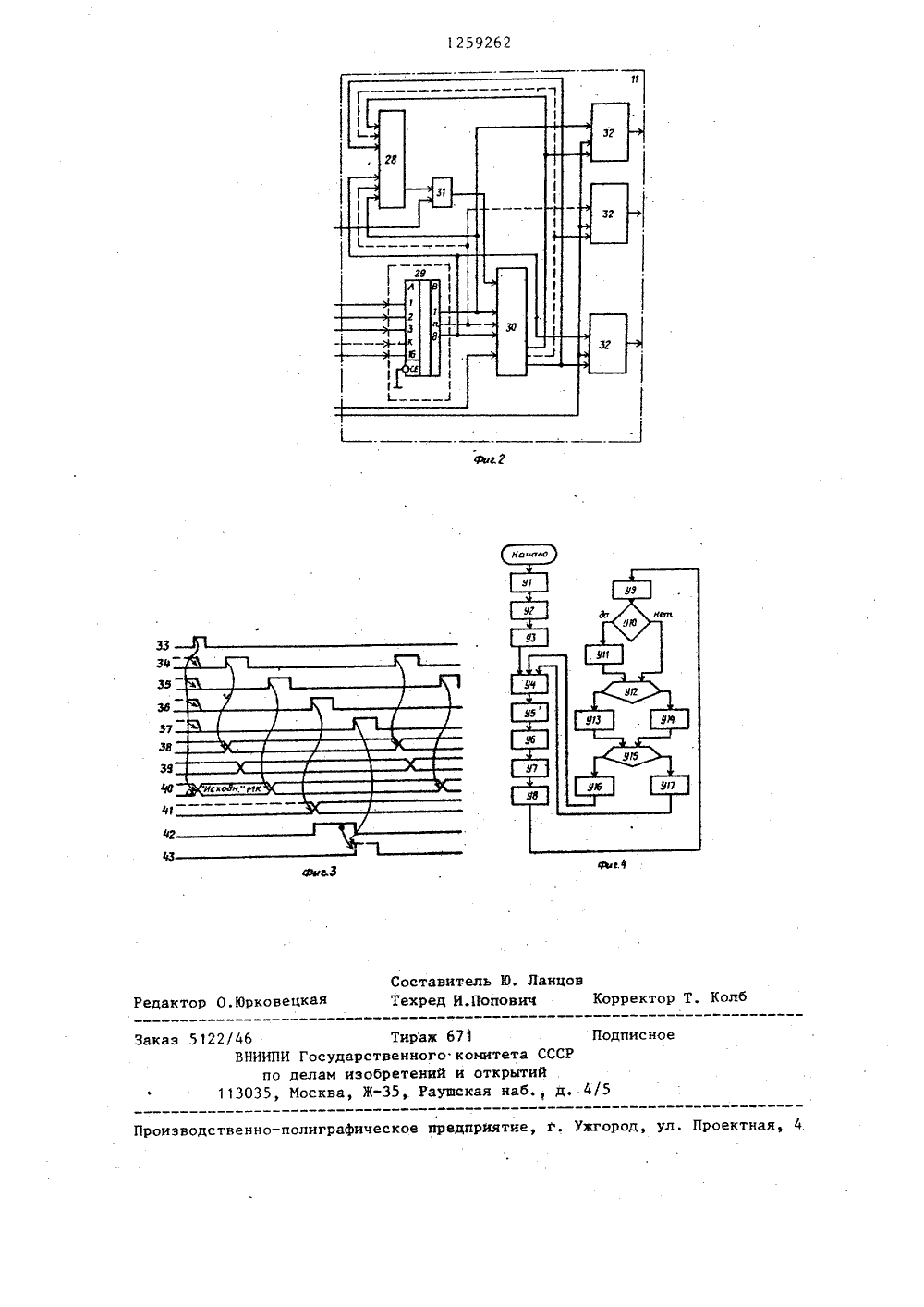

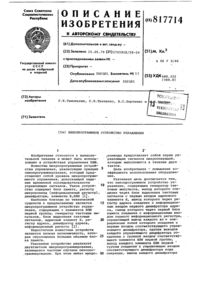

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 125. 22 СССРКРЫТ ИИ ОБРЕТ 8.84 ГОСУДАРСТВЕННЫЙ НОМИТЕ ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОПИСАНИЕ ИЗ Н АВТОРСКОМУ СВИДЕТЕ(56) Авторское свидетельство СССУ 934473, кл. С 06 Р 9/22, 1980..Авторское свидетельство СССРУ 1179337, кл, С 06 Р 9/22, 29.0 юл. У 35ое специальное конологическое бюрой электронной тех(54) ИИКРОПРОГРАМИНОЕ УСТРОЙСТВОУПРАВЛЕНИЯ(57) Изобретение относится к областиавтоматики и вычислительной техникии может быть использовано при построении цифровых вычислительных машин и контроллеров периферийных устройств. Целью изобретения являетсяповышение быстродействия в режимеветвления микропрограммы по внешнимлогическим условиям, Устройство содержит счетчик 1 адресов, блок 2элементов ИПИ, блок 3 элементов И,регистр 4 мнкрокоманд, блок 5 памяти микрокоманд, регистр 6 признаков,блок 7 синхронизации, элемент НЕ 8,два элемента И 9, 10, блок 11 приоритетного ветвления и памяти 12 модифицируемых адресов, входы и выходы устройства, 4 ил 1 табл,2 О Изобретение относится к автоматике и вычислительной технике и можетбыть использовано при построении цифровых вычислительных машин и контроллеров периферийных устройств. 5Целью изобретения является повышение быстродействия в режиме ветвления микропрограммы по внешним логическим условиям.На Фиг. 1 представлена структурная 1 Осхема микропрограммного устройствауправления; на фиг. 2 - функциональная схема блока приоритетного ветвления; на Фиг, 3 - временная диаграммафункционирования устройства; на15фиг. 4 - алгоритм функционирования,Устройство (Фиг. 1) содержит счетчик 1 адресов, блок 2 элементов ИЛИ,блок 3 элементов И, регистр 4 микрокоманд, блок 5 памяти микрокоманд,регистр б признаков, блок 7 синхронизации, элемент НЕ 8, первый 9 и второй 10 элементы И, блок 11 приоритетного ветвления, память 12 модифицируемых адресов, вход 13 кода ко 25манды, первый 14, второй 15, третий16 и четвертый 17 выхоцы блока синхронизации, вход 18 логических условий, вход 19 запуска, выход 20 полярежимов модификации адреса регистрамикрокоманд, выход 21 признака Формирования приоритетных ветвлений регистра микрокоманд, выход 22 полярежимов модификации адреса регистрамикрокоманд, выход 23 признака режимов адресации регистра микрокоманд, выход 24 поля микрооперациирегистра микрокоманд, выход 25 признака ветвления регистра микрокоманд, выход 26 поля адреса и выход 27.Блок 11 приоритетного ветвления(фиг. 2) содержит мажоритарный элемент 28,шифратор 29 приоритета, регистр 30, элемент И 31 и группу коммутаторов 32,На временной диаграмме (Фиг. 3)функционирования микропрограммногоустройства управления обозначены;33 - импульсный сигнал запуска (сигнал перевода устройства в исходноесостояние); 34 - первый тактовый синхроимпульс (С 1) цикла выполнениямикрокоманды (соответствует сигналуна выходе 14 блока 7 синхронизации); 5535 - второй тактовый синхроимпульс(С 2) (соответствует сигналу на выходе 15 блока 7 синхронизациьф 36 -третий тактовый синхроимпульс (СЗ) (соответствует сигналу на выходе 16 блока 7 синхронизации); 37 - четвертый тактовый синхроимпульс (С 4) (соответствует сигналу на выходе 17 блока 7 синхронизации)", 38 - состояния выходов счетчика 1 адресов;39 - состояния выходов блока 5 памяти микропрограмм; 40 - состояния выходов регистра 4 микрокоманд; 4 1 состояния выходов регистра 6 признаков; 42 - процедура в мажоритарном элементе 28; 43 - занесение в регистр 30 нового кода ветвления (происходит, когда код на одних входах мажоритарного элемента 28 превьппает код на других его входах).На алгоритмической схеме функционирования устройства (Фиг. 4) обозначены: У 1 - сигнал перевода устройства в исходное состояние, поступающий на его вход 19; У 2 - установка на выходе регистра 4 микрокоманд исходной микрокоманды; УЗ - разрешение прохождения через блок 3 элементов И кода начального адреса микропрограммы (кода команды); У 4 занесение в счетчик 1 адресов кода начального адреса микропрограммы по С 1; У 5 - считывание микрокоманды с выходов блока 5 памяти микрокоманд; У 6 - занесение микрокоманды в регистр 4 микрокоманд по С 2; У 7 появление на выходе 27 устройства (с выхода 24 регистра 4) кода, поступающего на внешнее устройство; У 8 - занесение кода внешних условий в регистр 6 признаков по СЗ; У 9 процедура арбитража приоритетов в мажоритарном элементе 28; У 10 - приоритет признака результата вьппезафиксированного в регистре 30; У 11 занесение нового кода приоритетного ветвления в регистр 30; У 12 - пере- ход к следующей микрокоманде в зависимости от содержимого соответствующего поля текущей микрокоманды; У 13 - появление на выходе блока приоритетного ветвления микропрограммы; У 14 - появление на выходе блока 11 кода ветвления по текущему признаку результата; У 15 - Формирование на входах элементов И 9 и 10 режима перехода к следующему адресу микрокоманды (согласно содержимому выхода 23 регистра 4 микрокоманд);У 16 - переход по прибавлению единицы к содержимому счет1ся в него сигналом на выходе элемента И 10. Причем режим занесения определяется нулевым состоянием выхода 23 регистра 4 в исходной микрокоманде, что определяет на выходе элемента НЕ 8 единичный уровень и разрешает прохождение первого тактового импульса С 1 на выход элемента И 10Режим безусловного перехода. В текущей микрокоманде на выходе 22 регистра 4 присутствует нулевой код, определяющий, в свою очередь, появление нулевого кода на выходе памяти 12 модифицируемых адресов, а на выходе 25 присутствует также сигнал нулевого уровня. В этом режиме и-разрядный код на информационном входе счетчика 1 адресов полностью определяется содержимым выхода 26 регистра 4.Режим условного перехода, Сигнал на выходе 25 регистра 4 принимает нулевое значение, код на выходе 26 регистра 4 определяет появление на ш старших входных разрядах блока 2 базового адреса, а на младших (и-ш) разрядах - нулевого уровня, причем младшие разряды (и-ш) входного кода блока 2 элементов ИЛИ отводятся для модификации адреса микрокоманды выходным кодом памяти 12 модифицируемых адресов. В этом режиме код на первом адресном входе памяти 12, отличный от нулевого, фиксирует выбор из памяти 12 модифицируемых адресов соответствующей выполняемой микропрограммы страниць, в пределах которой кодом на втором адресном входе определяется выбор ячейки памяти, содержимое которой является кодом модификации адреса при организации режима условного перехода для данной микрокоманды.Таким образом, нулевая страница памяти 12 отводится для появления на ее выходе нулевого кода в режимах занесения начального адреса ьщкропрограммы и безусловного перехода.При организации формирования адреса следующей микрокоманды по прибавлению единицы к коду, зафиксированному в счетчике 1 адресов, в текущей микрокоманде сигнал на выходе 23 регистра 4 принимает высокий уровень, в результате чего разрешается прохождение синхроимпульса С 1 3 1259262Устройство работает следующимобразом.При поступлении на вход 19 устройства импульсного сигнала запуска(фиг. 3, 33) происходит перевод устройства в исходное состояние, т.е.обнуление регистров 6 и 4, при этомна выходах блока 11 приоритетноговетвления появляется нулевой код, аформирование тактовых синхроимнульсов с выходов блока 7 синхронизацииначинается с С 1, появляющегося на выходе 14 (Фиг. 33+34.+35+36-ю 37). Навыходах регистра 4 микрокоманд появляется исходная микрокоманда15(фиг, 3, 3340). Управление ходомвыполнения микропрограммы осуществляется путем изменения содержимогосчетчика 1 адресов, выходной код которого определяет адрес считываемойзатем из блока 5 памяти микрокоманды.Изменение содержимого счетчика 1 адресов происходит либо занесением внего параллельного кода, либо прибавлением единицы к уже зафиксированно 25му в нем коду,Формирование параллельного кодана информационном входе счетчика 1адресов происходит в блоке 2 элементов ИЛИсостоящем из и трехвходовых элементов ИЛИ, где и - разрядность адресного кода на выходах счетчика 1 адресов. Активным уровнем навходах блока 2 элементов ИЛИ является высокий уровень сигнала. При этом 35осуществляются три основных режимаФормирования параллельного кода наинформационном входе счетчика. 1 адресов,Режим занесения начального адреса 40микропрограммы. После подачи на вход19 устройства импульса запуска(фиг. 3 и 4, У 1, У 2, УЗ, У 4) на выходах регистра 4 микрокоманд появляет- .ся исходная микрокоманда, которая 45определяет на выходе 26 низкий (нулевой) уровень, а на выходе 22 - нулевой код, определяющий независимо откода на выходах блока 11 приоритетного ветвления нулевой код на выходах 5 Опамяти 12, В то же время единичныйсигнал исходной микрокоманды на выходе 25 регистра 4 определяет прохождение через блок 3 элементов Икода начального адреса микропрограммы с входа 13 устройства, которыйпоявляется затем на информационномвходе счетчика 1 адресов и заносит 259262,на вйход элемента И 9 и далее насчетный вход счетчика 1 адресов.В устройстве реализован четырехтактный цикл выполнения каждой микрокоманды. По первому такту (С 1) происходит Формирование адреса следующей микрокоманды в счетчике 1 адресов (фиг, 3, 34-38).По второму такту (С 2) происходитзанесение микрокоманды с выходов10блока 5 памяти в регистр 4 микрокоманд (фиг. 3. 35 + 40),По третьему такту (СЗ) осуществляется занесение признака результата врегистр 6 (фиг. 3, 364 1), приэтом заносимый код образо ан как ко"дом состояний внешних устройств -вход младших разрядов регистра 6,так и базовым кодом микропрограммы -вход старших разрядов регистра 6.По четвертому такту (С 4) осуществляется занесение кода приоритетноговетвления в регистр 30 блока 11(фиг. 3, 37 - 43), что происходит,когда уровень приоритета текущего25кода признака результата на выходахрегистра 6 превышает уровень зафиксированного ранее в регистре 30 кода приоритетного ветвления (фиг. 2).В режиме условного перехода происходит управление ходом выполнениямикропрограммы в зависимости от состояний внешних устройств. При этомв регистре 6 признаков, блоке 11приоритетного ветвления, памяти 12 35модифицируемых адресов и блоке 2элементов ИЛИ происходит формирование предполагаемого ветвления микро-программы.Формйрование ветвления осуществля ется следующим образом.В ходе выполнения микропрограммывне зависимости от текущих режимовперехода на следующий адрес микро-.команды (режим занесения начального 45адреса, режим безусловного .переходапо занесению параллельного кода илипо прибавлению единицы, режим условного перехода) в блоке 11 приоритетного ветвления в каждом цикле выполнения микрокоманды происходит арбитраж приоритетов предполагаемых ветвлений.Для этого код признака результа та поступает на входы шифратора 29 55(фиг. 2). В последнем происходит преобразование кода признака результатав выходной код, определяющий уровень приоритета текущего признака результата, причем более высокому уровню приоритета на выходе шифратора 29 соответствует большее значение двоичного кода. В мажоритарном элементе 28 происходит арбитраж приоритетов: текущего - с выходов шифратора 29 и наиболее приоритетного по результатам выполнения части микропрограмм - с выходов регистра 30. Если код на одних входах мажоритарного элемента 28 больше кода на других его входах, то на его выходе появляется сигнал единичного уровня, разрешающих прохождение через элемент И 31 синхроимпульса С 4, по которому происходит занесение в регистр 30 нового кода с выходов шифратора 29, Таким образом, на выходе регистра 30 всегда присутствует код, определяющий уровень наиболее приоритетного ветвления микропрограммы в результате выполнения определенной части микропрограммы. Причем по импульсу запуска регистр 30 обнуляется, таким образом подготавливается к выполнению очередной запускаемой микропрограммы, поэтому первый же в микропрограмме уровень приоритета, код которого превьппает нулевой, заносится в регистр 30.При организации условного перехода в устройстве возможно ветвление микропрограммы как по наиболее приоритетному уровню, хранящемуся в регистре 30, так и по текущему уровню приоритета на выходах шифратора 29. Для этого на выходе блока 11 коммутируется выбранный рабочий код ветвления. При единичном уровне сигнала на выходе 21 регистра 4 на выходы блока 11 коммутируется код текущего уровня приоритета, а при нулевом уровне сигнала на выходе 21 код приоритетного ветвления с выходов регистра 30.Выходной код блока 11, поступающий на второй адресный вход памяти 12, наряду с кодом выбора страницы на втором адресном входе, постоянным для каждой микропрограммы, образуют адресный код памяти 12. В соответствии со сформированным адресом считывается ячейка памяти 12, содержимое которой является модифицированной частью адреса микрокоманды в режиме условного перехода, которая вместе с базовой частью адреса, по259262 10 ступающего с выхода 2 б регистра 4микрокоманд (формирование кода в блоке 2 элементов ИЛИ описано выше),определяет итоговый код адреса условного перехода, заносимый в счетчик1 адресов. Ф о р м у л а и э о б р е т е н и я Микропрограммное устройство управ пения, содержащее счетчик адресов, блок памяти микрокоманд, блок элементов И и блок элементов ИЛИ, причем первый вход блока элементов И является входом кода команды устройства, 15 выход блока элементов И соединен с первым входом блока элементов ИЛИ, выход которого соединен с информационным входом счетчика адресов, выход которого соединен с адресным входом 30 блока памяти микрокоманд, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия в режиме ветвления микропрограммы по внешним логическим условиям, оно дополнительно содержит два элемента И, элемент НЕ, регистр микрокоманд, блок синхронизации, регистр признаков, память модифицируемых адресов и блок приоритетного ветвления, содержащий 30 мажоритарный элемент, элемент И, шифратор приоритета, регистр и группу коммутаторов, причем Выход блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, З выход признака ветвления которого соединен с вторым входом блока элементов И, выход поля адреса регистра микрокоманд соединен с вторым входом блока элементов ИЛИ, третий Вход ко торого соединен с выходом памяти модифицируемых адресов, первый адресный вход которой соединен с выходом поля режимов, модификации адреса регистра микрокОманд ВыхОд поля микроопе д рации которого является выходом устройства, счетный вход счетчика адре сов соединен с выходом первого элемента И, первый вход которого соединен с первыМ входом второго элемента И и с первым выходом блока синхронизации, второй выход которого соединен с входом записи регистра микрокоманд, вход начальной установки которого соединен с входом запуска блока синхронизации, с входом сброса регистра признаков, с входом сброса регистра и подключен к входу запуска устройства, выход признака режима адресации регистра микрокоманд соединен с вторым входом первого элемента И и через элемент НЕ с вторым входом второго элемента И, выход которого соединен с входом записи-счета счетчика адресов, третий выход блока синхронизации соединен с входом записи регистра признаков, выход которого соединен с входом шифратора приоритета, выходы которого соеди,нены с соответствующими входами первой группы мажоритарного элемента, с соответствующими информацион" ными входами регистра и с соответствующими первыми информационными входами коммутаторов группы, вторые информационные входы которых соединены с соответствующими входами второй группы мажоритарного элемента и выходами регистра, управляющие входы коммутаторов группы подключены к вы" ходу признака Формирования приоритетных ветвлений регистра микрокоманд, выход поля признака микропрограммы которого соединен с информационным входом старших разрядов регистра при" знаков, информационный вход младших разрядов которого подключен к входу логических условий устройства, второй адресный вход памяти модифицируемых адресов поразрядно соЕдинен с выходами коммутаторов группы, выход мажоритарного элемента соединен с первым входом элемента И блока приоритетного ветвления, выход которого соединен с входом записи регистра, второй вход элемента И блока приоритетного ветвления соединен с четвертым выходом блока синхронизации.12592 б 2 Составитель Ю, Ланедактор О.Юрковецкая Техред И.Попович ектор Т ПодписСР о-полиграфическое предприят город, у о 5122/46 ВНИИПИ Госуд по делам 113035, ИоскваТирахственногообретенийЖ, Рауш митета открыт ая наб

СмотретьЗаявка

3744026, 23.05.1984

КРАСНОДАРСКОЕ СПЕЦИАЛЬНОЕ КОНСТРУКТОРСКО-ТЕХНОЛОГИЧЕСКОЕ БЮРО СЕЙСМОРАЗВЕДОЧНОЙ ЭЛЕКТРОННОЙ ТЕХНИКИ

ПОТОКОВ ВАЛЕРИЙ НУРБИЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 23.09.1986

Код ссылки

<a href="https://patents.su/7-1259262-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Устройство для централизованного управления вычислительной системой

Следующий патент: Устройство для выборки команд

Случайный патент: Дробеметная установка