Аналого-цифровой интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

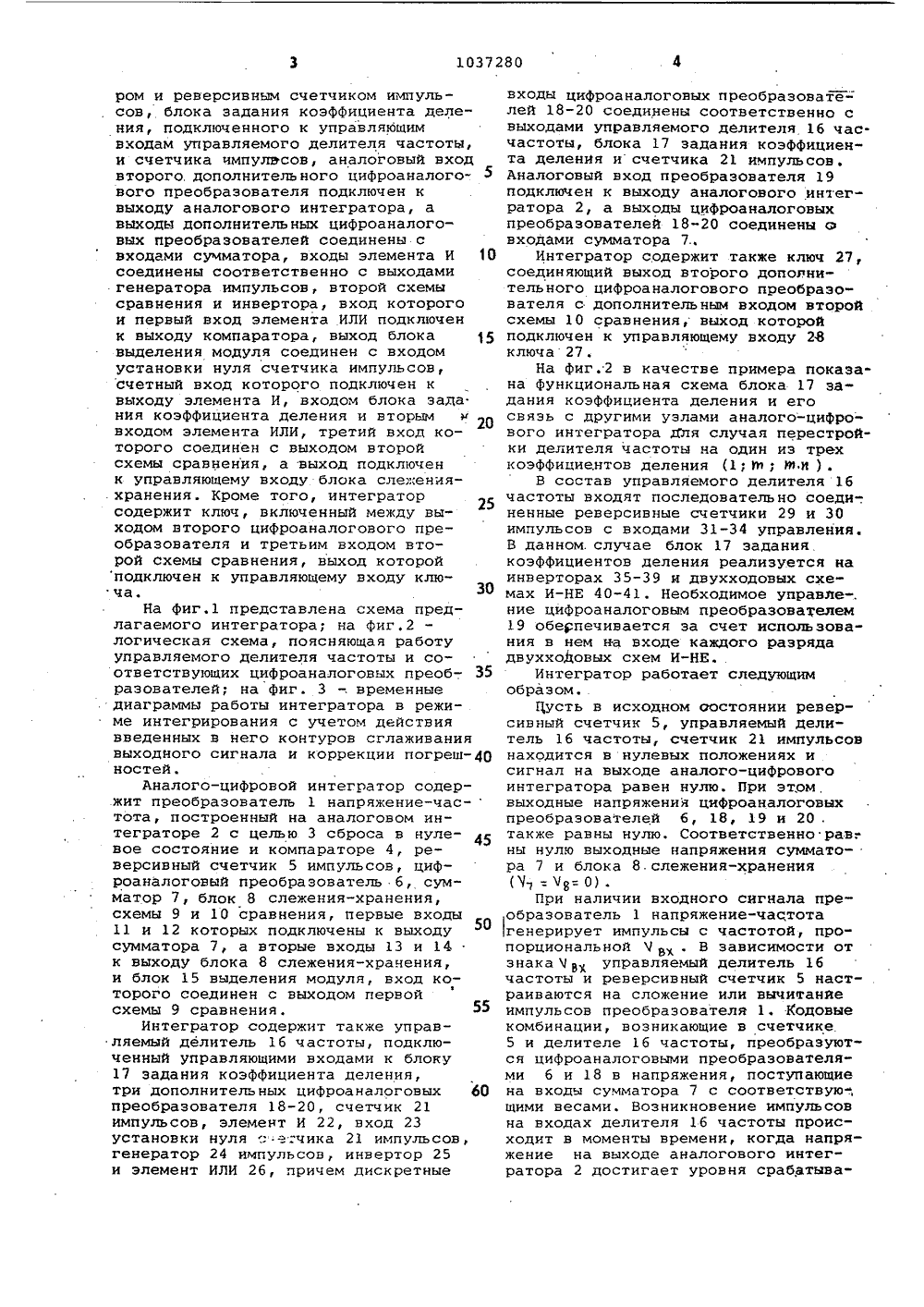

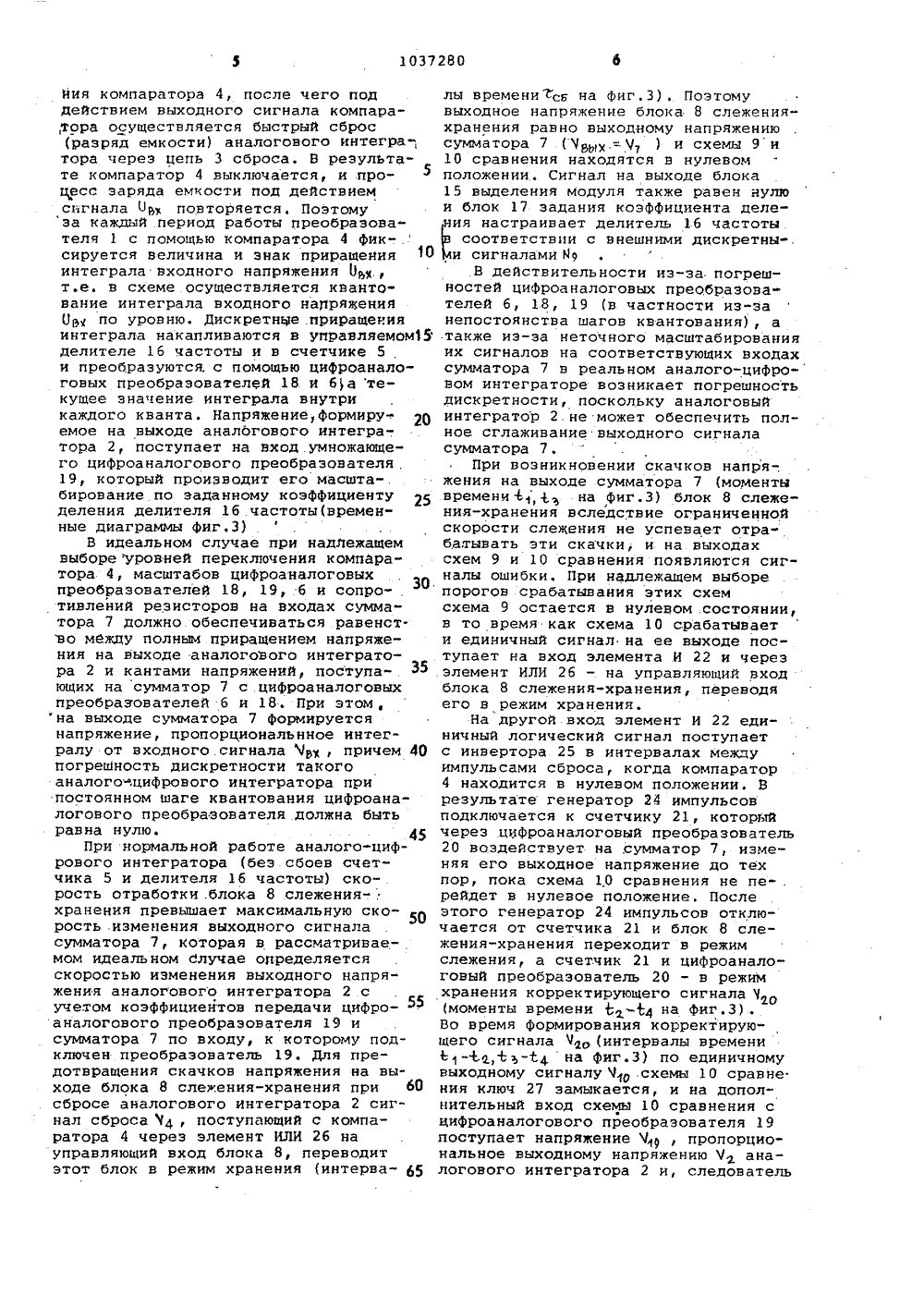

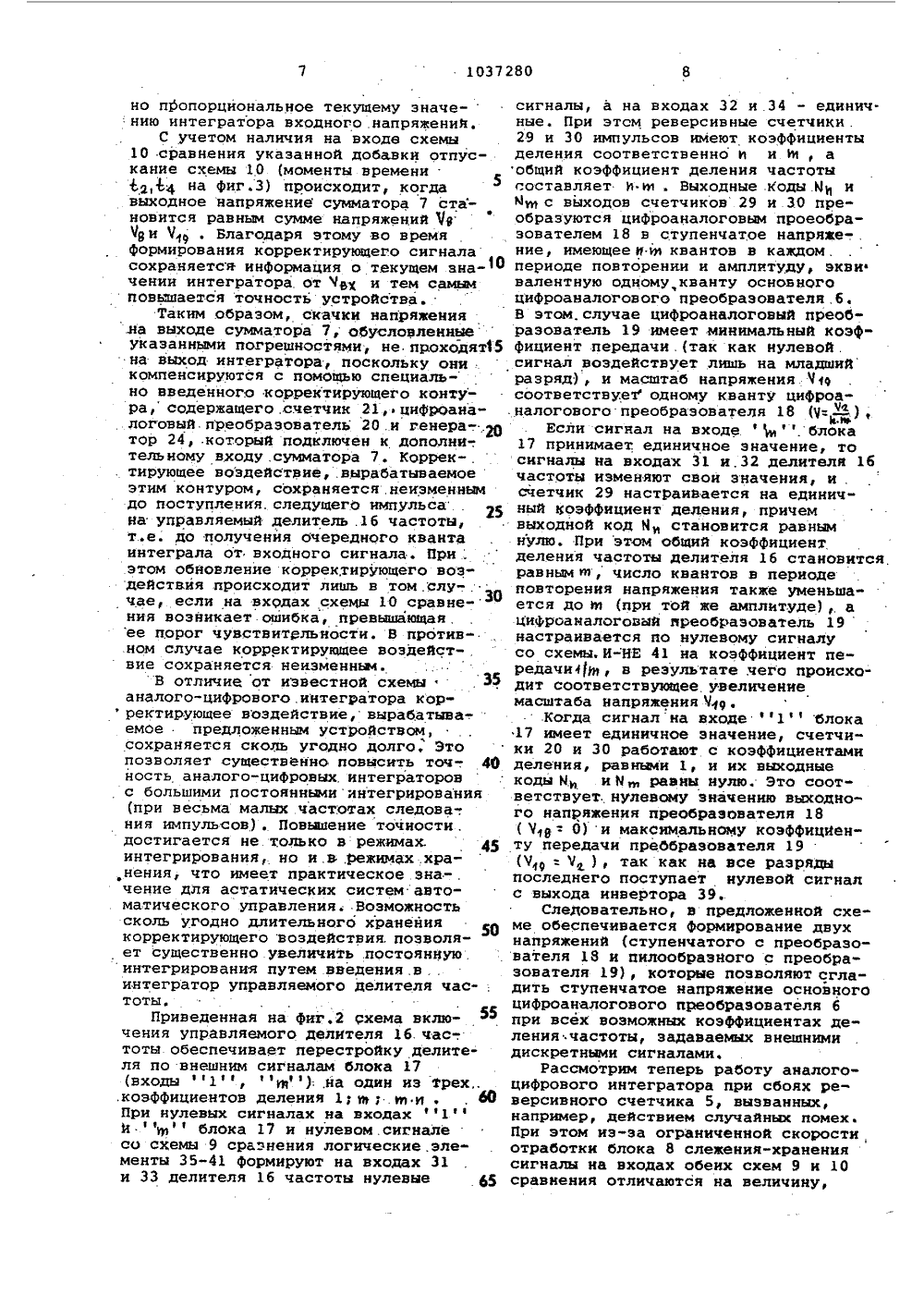

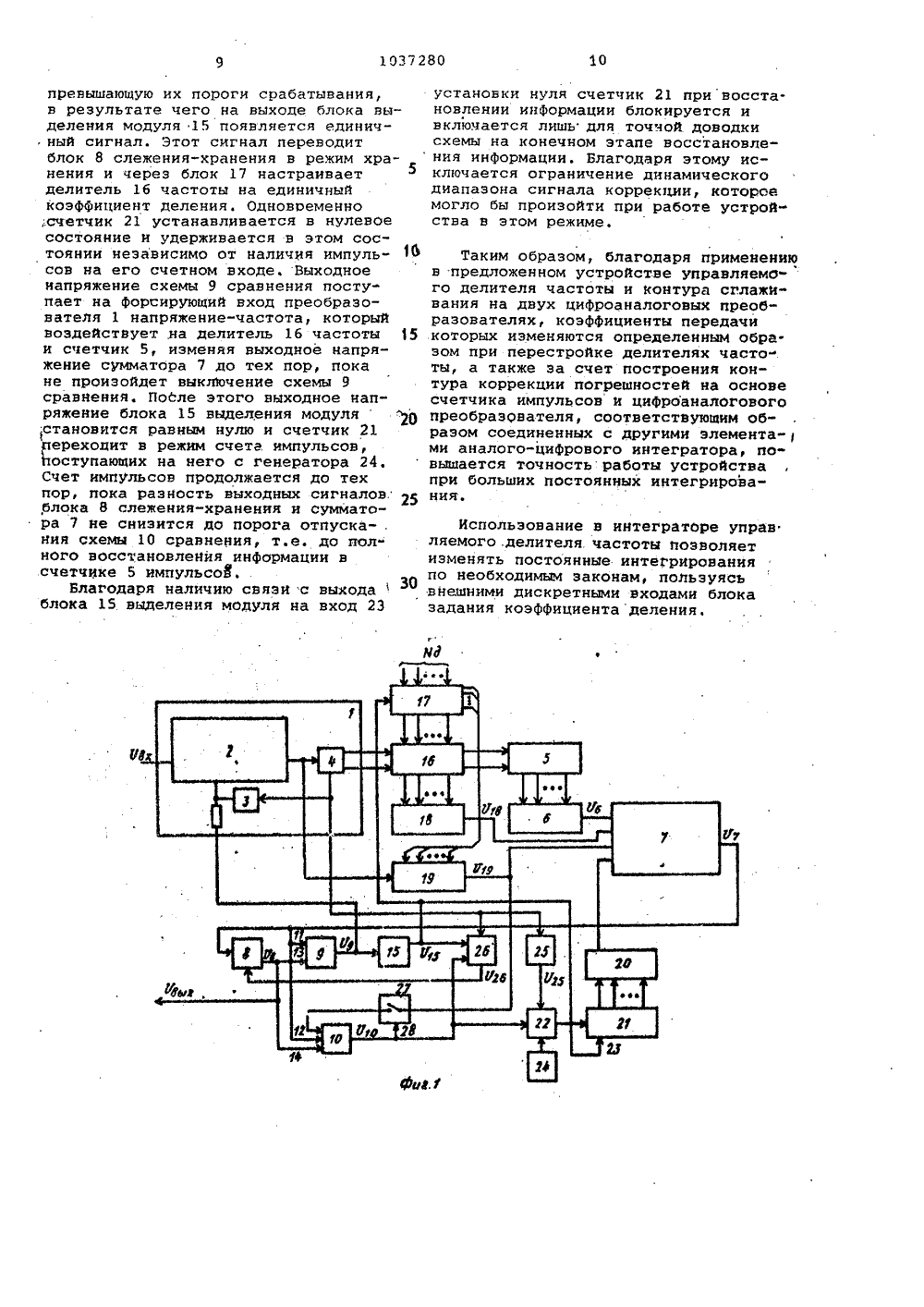

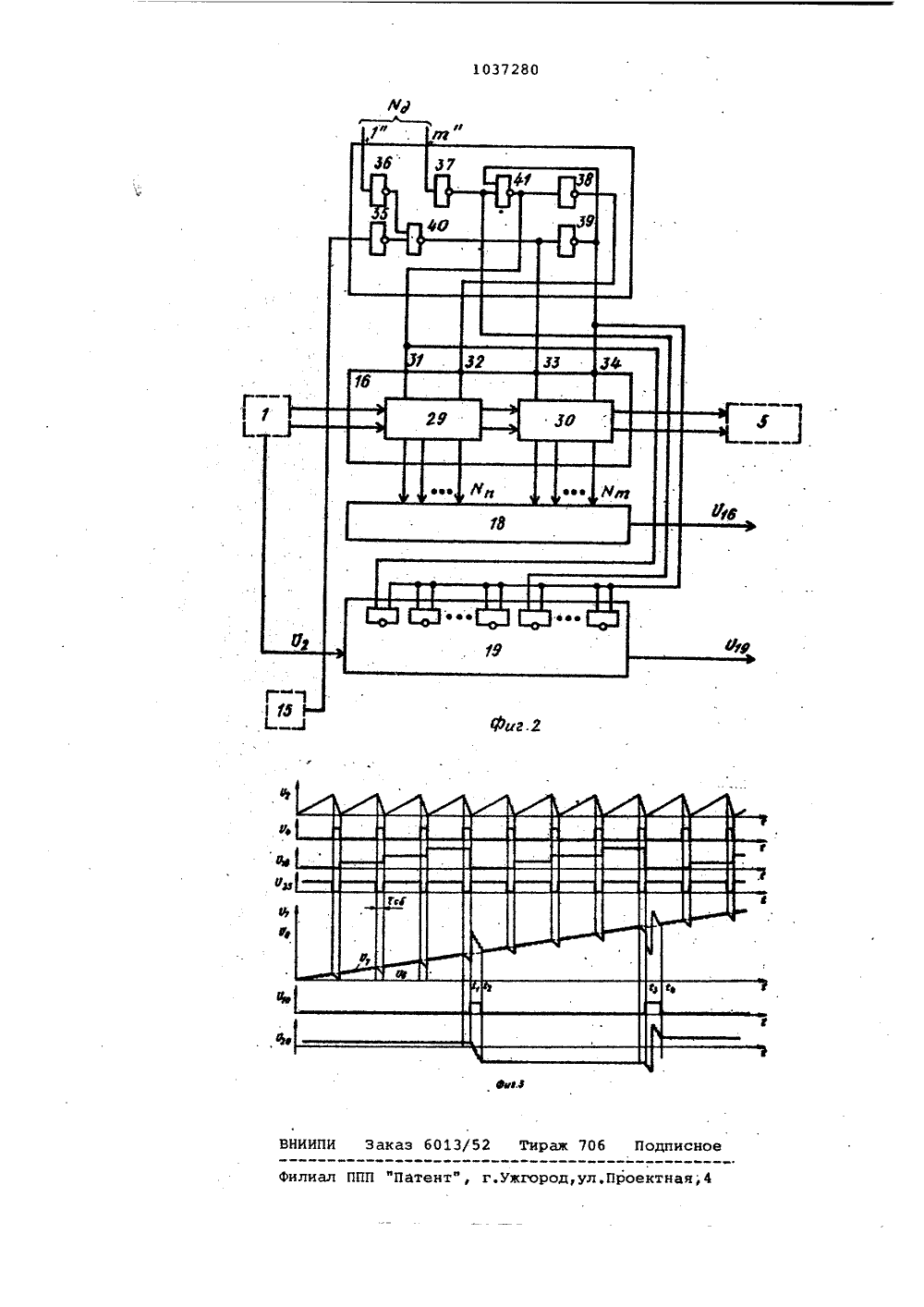

СООЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 9) (1 И ЯО,ГОСУДАРСТВЕННЫЙ НО ПО ДЕЛАМ ИЗОБРЕТЕНИ ИТЕТ СССР И ОТКРЫТИИ РЕТЕНИ ЕП:ЛЬСТВУ нт ов 73/18(прототи ША 9 3288627,опублик. 1975.свидетельство СССРОб 6 7/18, 1973свидетельство СССР06(3 7/18, 1981 атент 5 7/18 орское кл, 6 орское тонивча ОПИСАНИЕ К ДВТОРСКОМЪ Св п).(54)(57) 1. АНАЛОГО-ЦИФРОВОЙ ИНТЕГРА ТОР, содержащий последовательно соединенные аналоговый интегратор, вход которого является входом аналого-цифрового интегратора, и компаратор, выход которого через цепв сбро са подключен квходу обнуления анало гового интегратора, а также реверсивный счетчик импульсов, выход которого через цифроаналоговый преобразователь соединен с первым входом сумматора, две схемы сравнения, .первые входы которых соединены с вы ходом сумматора, а вторые входы - с выходом блока слежения-хранения, вход которого подключен к выходу сумматора, а выход является выходом аналого"цифрового интегратора, и блок выделения модуля, вход которого соединен с выходом первой схемы сравнения, о т л и ч а ю щ и й с я тем, что, с целью повышения точности интегрирования, увеличения посянной времени и диапазона измене" я постоянной времени интегрированы него введены управляемый делитель стоты, блок задания коэффициента деления, счетчик импульсов, элеме И, элемент ИЛИ, генератор импульс инвертор и первый, второй и третий дополнительные цифроаналоговые преобразователи, дискретные входы ко" торых соединены соответственно с выходами управляемого делителя частоты, включенного между компаратором и реверсивным счетчиком импульсов, блока задания коэффициента деления, подключенного к управляющим входам управляемого делителя частоты,и счетчика импульсов, аналоговый вход второго дополнитель" ного цифроаналогового преобразОвателя подключен к выходу аналогового интегратора, а выходы дополнительныхцифроаналоговых преобразователей соединены с входами сумматора, входы. элемента И соединены соответственно .с выходами генератора импульсов, С: второй схемы сравнения и инвертора, вход которого и первый вход элемен- Я та ИЛИ подключен к выходу компара" тора, выход блока выделения модуля 1 соединен с входом установки нуля ,счетчика импульсов, счетный вход которого подключен к выходу элемента Ивходом блока задани,1 коэффициента де", ,ления и вторым входом элемента ИЛИ, ) третий вход которого соединен с выхо дом второй схемы сравнения, а выход подключен к управляющему входу блока слежения-хранения,2. Интегратор но п.1, о т л и ч. а- ю щ и й с я тем, что, с целью повышения точности,он содержит ключ, включенный между выходом второго цифроаналогового преобразователя и третьим входом второй схемы сравнения выход которой подключен к управляюще" му входу ключа, 1037280Изобретение относится к автоматике, предназначено для формирования напряжения, пропорционального интегралу от входного сигнала, и может ис- пользоваться в системах автоматического управления различными технологическими процессами и объемами, когда требуются большие постоянные интегрирования.Известны устройства для интегрирования,содержащие реверсивный счетчик 10 импульсов, цифроаналоговый преобразователь и преобразователь напряжение частота, выполненный на основе ана; логового интегратора и компаратора 13. 35Недостатком таких устройств является то, что вследствие сбоев счетчика под действием случайных помех н перерывов и подаче питания происходит разрушение информации накоп- щ ленной интегратором, что может при" водить к аварийным последствиям, а потому во многих случаях совершенно недопустимо.Известен аналого-цифровой интегра" 25 тор, в котором наряду с указанными элементами и цифроаналоговым преобра" зователем с выходным сумматором, второй вход которого подключен к выходу аналогового интегратора, приме" нен контурносстановления информации, содержащий последовательно включенные блоки слежения-хранения, выявления модуля, сравнения и логическую схему управления режимами работы блока слежения-хранения 1.23.35Недостатком этого интегратора является погрешность интегрирования, /связанная с неравенством квантов напряжения на выходах аналогового интегратора и циФроаналогового преоб разователя. Это обусловлено как погрешностями цифроаналогового преобра" зователя, в частности непостоянством его шага квантования, так и неточностью релейных элементов в преобра зователе напряжение-частота, осуществ ляющих квантование интеграла входного сигнала, В результате в моменты сброса аналогового интегратора (в точках квантования) возникают скачки напряжения на выходе интегратора, что снижает точность интегрирования. Это затрудняет использование интегра" тора н особенности в устройствахифференцирования медленно меняющихя сигналов, когда интегратор включается и обратную связь усилителя с большим коэффициентом усиления.Наиболее близким к изобретению по технической сущности является аналого-цифроной интегратор, содер жащий последОвательно соединенные аналоговый интегратор, компаратор, ренерсивный счетчик импульсон, цифроаналоговый преобразователь, сумматор и блок слежения-хранения, две 65 схемы сравнення, первые входы которых соединены с выходом сумматора, а вторые входы - с выходом блока сле" жения-хранения, два блока выделения модуля, второй блок слежения-хране-": нияа также логические элементы И, И-НЕ и сложения по модулю два,соответствующим образом соединенные между собой и с другими элементами схемы. Благодаря введению в данное устройство контура сглажинания выходного напряжения обеспечивается повышение точности работы устройства за счет уменьшения составляющей погрешности, обусловленной непостоянством шага квантования цифроаналогового преобразователя 1 3 .Недостатком известного интегратора является наличие погрешности в режиме хранения и при интегрировании малых напряжений, когда в промежутках между импульсами на входе счетчика блок слежения-хранения в контуре формирования сигнала коррекции изменяет свое выходное напряжение из-эа дрейФа используемого в нем операционного усилителя, утечек, конденсатора и других дестабилизирующих факторов. Наряду со снижением точности это не позволяет использовать принцип деления частоты импульсов на входе счетчика, обеспечивающий получение достаточно больших и легко перестраиваемых по необходимым законам постоянных интегрирования.Целью изобретения является повышение точности интегрирования, увеличение постоянной времени и диапазона изменения постоянной времени интегрирования.Для достижения постанленной цели в аналого-циФровой интегратор, содержащий последовательно соединенные аналоговый интегратор, вход которого является входом аналого-цифрового интегратора, и компаратор, выход ко" торого через цепь сброса подключен к входу обНуления аналогового интегратора, а также реверсинный счетчик импульсов, выход которого через цифроаналоговый преобразователь соединен с первым входом сумматора, а вторые входы - с выходом блока слежения-хранения, вход которого подключен к выходу сумматора, а выход является выходом аналого-циФрового интегратора, и блок выделения модуля, вход которого соединен с выходом первой схемы сравнения, введены управляемый делитель частоты, блок задания коэффициента деления, счетчик импульсов, элемент И, элемент ИЛИ, генератор импульсов, инвертор и первый, второй и третий дополнительные цифроаналоговые преобразователи, дискретныевходы которых соединены соответственнос выходами управляемого делителячастоты, включенного между компаратором и реверсивным счетчиком импульсов, блока задания коэффициента деления, подключенного к управляющим входам управляемого делителя частоты, и счетчика импульсов, аналоговый вход второго. дополнительного цифроаналого вого преобразователя подключен к выходу аналогового интегратора, а выходы дополнительных цифроаналоговых преобразователей соединены с входами сумматора, входы элемента И 10 соединены соответственно с выходами генератора импульсов, второй схемы сравнения и инвертора, вход которого и первый вход элемента ИЛИ подключен к выходу компаратора, выход блока 15 выделения модуля соединен с входом установки нуля счетчика импульсов, счетный вход которого подключен к выходу элемента И, входом блока зада ния коэффициента деления и вторым м 20 входом элемента ИЛИ, третий вход которого соединен с выходом второй схемы сравнения, а выход подключен к управляющему входу блока слежения- .хранения. Кроме того, интегратор содержит ключ, включенный между выходом второго цифроаналогового преобразователя и третьим входом второй схемы сравнения, выход которой подключен к управляющему входу ключа.30На фиг.1 представлена схема предлагаемого интегратора; на фиг.2 логическая схема, поясняющая работу управляемого делителя частоты и соответствующих цифроаналоговых преоб разователей; на фиг. 3 в . временные диаграммы работы интегратора в режиме интегрирования с учетом действия введенных в него контуров сглаживания выходного сигнала и коррекции погрешностей.Аналого-цифровой интегратор содержит преобразователь 1 напряжение-час-тота, построенный на аналоговом интеграторе 2 с целью 3 сброса в нуле вое состояние и компараторе 4, реверсивный счетчик 5 импульсов, цифроаналоговый преобразователь 6, сумматор 7, блок 8 слежения-хранения, схемы 9 и 10 сравнения, первые входы 11 и 12 которых подключены к выходу сумматора 7, а вторые входы 13 и 14 к выходу блока 8 слежения-хранения, и блок 15 выделения модуля, вход которого соединен с выходом первой схемы 9 сравнения. 55Интегратор содержит также управляемый делитель 16 частоты, подключенный управляющими входами к блоку 17 задания коэффициента деления, три дополнительных цифроаналоговых 60 преобразователя 18-20, счетчик 21 импульсов, элемент И 22, вход 23 установки нуля с е."чика 21 импульсов, генератор 24 импульсов, инвертор 25 и элемент ИЛИ 26, причем дискретные входы цифроаналоговых преобразователей 18-20 соединены соответственно с выходами управляемого делителя 16 часчастоты, блока 17 задания коэффициента деления исчетчика 21 импульсов. Аналоговый вход преобразователя 19 подключен к выходу аналогового интегратора 2, а выходы цифроаналоговых преобразователей 18-20 соединены э входами сумматора 7Интегратор содержит также ключ 27, соединяющий выход второго дополнительного цифроаналогового преобразователя с дополнительным входом второй схемы 10 сравнения, выход которой подключен к управляющему входу 28 ключа 27.На фиг.2 в качестве примера показана функциональная схема блока 17 задания коэффициента деления и его связь с другими узлами аналого-цифрового интегратора ЕРя случая перестройки делителя частоты на один из трех коэффициентов деления (1;Ф; Ю И )В состав управляемого делителя 16 частоты входят последовательно соеди-. ненные реверсивные счетчики 29 и 30 импульсов с входами 31-34 управления. В данном. случае блок 17 задания коэффициентов деления реализуется на инверторах 35-39 и двухходовых схемах И-НЕ 40-41. Необходимое управле-. ние цифроаналоговым преобразователем 19 обеспечивается за счет использования в нем на входе каждого разряда двуххойовых схем И-НЕ.Интегратор работает следующим образом.пусть в исходном оостоянии реверсивный счетчик 5, управляемый делитель 16 частоты, счетчик 21 импульсов находится в нулевых положениях и сигнал на выходе аналого-цифрового интегратора равен нулю. При этом, выходные напряжения цифроаналоговых преобразователей 6, 18, 19 и 20 . также равны нулю. Соответственно рав.- ны нулю выходные напряжения сумматора 7 и блока 8.слежения-хранения (Ч: Чв= О) .При наличии входного сигнала преобразователь 1 напряжение-частота генерирует импульсы с частотой, пропорциональной Ч з . В зависимости от знака Чуправляемый делитель 16 частоты и реверсивный счетчик 5 настраиваются на сложение или вычитанйе импульсов преобразователя 1. Кодовые комбинации, возникающие в счетчике 5 и делителе 16 частоты, преобразуются цифроаналоговыми преобразователями 6 и 18 в напряжения, поступающие на входы сумматора 7 с соответствую-., щими весами. Возникновение импульсов на входах делителя 16 частоты происходит в моменты времени, когда напряжение на выходе аналогового интегратора 2 достигает уровня срабатыва 1037280йия компаратора 4, после чего под действием выходного сигнала компара,тора осуществляется быстрый сброс (разряд емкости) аналогового интегра-, тора через цепь 3 сброса. В результате компаратор 4 выключается, и процесс заряда емкости под действием сигнала Оь повторяется. Поэтому за каждый .период работы преобразова" теля 1 с помощью компаратора 4 фик-. сируется величина и знак приращения 10 интеграла входного напряжения ь., т.е. в схеме осуществляется квантование интеграла входного на)1 ряжений э по уровню. Дискретные .приращения интеграла накапливаются в управляемом 15 делителе 16 частоты и в счетчике 5, и преобразуются. с помощью цифроаналоговых преобразователЕй 18 и 6)а текущее значение интеграла внутри каждого кванта. Напряжение,формиру- рО емое на выходе аналогового интегра-. тора 2, поступает на вход умножающего цифроаналогового преобразователя 19, который производит его масшта-. бирование по заданному коэффициенту 25 деления делителя 16 частоты(времен" ные диаграммы Фиг.З)В идеальном случае при надлежащем выборе уровней переключения компаратора 4, масштабов цифроаналоговых преобразователей 18, 19, б и сопро" тивлений резисторов на входах сумматора 7 должно обеспечиваться равенство между полным приращением напряжения на выходе аналогового интегратора 2 и кантами напряжений, поступа-. ющих на сумматор 7 с цифроаналоговых преобразователей б и 18. При этом, "на выходе сумматора 7 формируется напряжение, пропорциональнное интегралу от входного. сигнала Ч, причем 40 погрешность дискретности такого аналого, цифрового интегратора при постоянном шаге квантования цифроаналогового преобразователя должна быть равна нулю. 45При нормальной работе аналого-цифрового интегратора (беэ сбоев счет" чика 5 и делителя 16 частоты) скорость отработки .блока 8 слежения-: хранения превышает максимальную ско рость .изменения выходного сигнала сумматора 7, которая в рассматриваемом идеальном случае определяется скоростью изменения выходного напряжения аналогового интегратора 2 с учетом коэффициентов передачи цифроаналогового преобразователя 19 и сумматора 7 по входу, к которому подключен преобразователь 19. Для предотвращения скачков напряжения на выходе блока 8 слежения-хранения при бО сбросе аналогового интегратора 2 сигнал сброса Ч 4, поступающий с компаратора 4 через элемент ИЛИ 26 на управляющий вход блока 8, переводит этот блок в режим хранения (интерва лы временис на фиг.3)Поэтому выходное напряжение блока 8 слежения- хранения равно выходному напряжению сумматора 7 (Чх,Ч ) и схемы 9 и 10 сравнения находятся в нулевом положении. Сигнал на выходе блока 15 выделения модуля также равен нулю и блок 17 задания коэффициента деле" ия настраивает делитель 16 частотысоответствии с внешними дискретны-. и сигналами ЙВ действительности из-за погрешностей цифроаналоговых преобразователей б, 18, 19 (в частности из-за непостоянства шагов квантования), а также из-за неточного масштабирования их сигналов на соответствующих входах сумматора 7 в реальном аналого-цифро- вом интеграторе возникает погрешность дискретности, поскольку аналоговый интегратор 2 не может обеспечить полное сглаживание выходного сигнала сумматора 7.При возникновении скачков напря-. жения на выходе сумматора 7 (моменты времени ь 1,(, на Фиг.З) блок 8 слежения-хранения вследствие ограниченной скорости слежения не успевает отрабатывать эти скачки, и на выходах схем 9 и 10 сравнения появляются сигналы ошибки. При надлежащем выборе порогов срабатывания этих схем схема 9 остается в нулевом состоянии, в то время как схема 10 срабатывает и единичный сигнал на ее выходе поступает на вход элемента И 22 и через элемент ИЛИ 26 - на управляющий вход блока 8 слежения-хранения, переводя его в режим хранения.На другой вход элемент И 22 единичный логический сигнал поступает с инвертора 25 в интервалах между импульсами сброса, когда компаратор 4 находится в нулевом положении. В результате генератор 24 импульсов подключается к счетчику 21, который через цифроаналоговый преобразователь 20 воздействует на сумматор 7, изменяя его выходное напряжение до тех пор, пока схема 1,0 сравнения не пе- . рейдет в нулевое положение. После этого генератор 24 импульсов отключается от счетчика 21 и блок 8 слежения-хранения переходит в режим слежения, а счетчик 21 и цифроаналоговый преобразователь 20 - в режим хранения корректирующего сигнала 1 (моменты времени -4 на фиг,З). Во время формирования корректирую" щего сигнала Чо (интервалы времени 1-Ь,1 -14 на Фиг3) по единичному выходному сигналу Ч 1 О .схемы 10 сравне. ния ключ 27 замыкается, и на дополнительный вход схемы 10 сравнения с цифроаналогового преобразователя 19 поступает напряжение Ч, пропорциональное выходному напряжению Ч аналогового интегратора 2 и, следовательно пропорциональное текущему значе-нию интегратора входного .напряжений.С учетом наличия на входе схемы10 сравнения указанной добавки отпускание схемы 10 (моменты времени .на фиг.3) происходит, когдавыходное напряжение сумматора 7 ста"новится равным сумме напряжений МуЧри У . Благодаря этому во времяформирования корректирующего сигналасохраняетса информация о текущем знаОчении интегратора.от Чэ и тем самыеповыпается точность устройства.Таким образом, скачки напряжения.на выходе сумматора 7, обусловленныеукаэанными погрешностями, не.проходят 15на выход интегратора, поскольку оникомпенсируются с помощью специально введенного корректйрующего контура,содержащего,счетчик 21, цифроаналоговый преобразователь 20.и генера-.,;Отор 24, .который подключен к дополни-.тельному входу, сумматора 7. Коррек-.. тирующее воздействие,.вырабатываемоеэтим контуром, сохраняется.неизменнымдо поступления. следущего импульсаНа уПравляемый делитель .16 частоты,т.е. до получения очередного квантаинтеграла от входного сигнала, При.;этом обновление корректирующего воздействия происходит лишь в том .слу-.,чае, если на вхрдах схемы 10 сравне-ния возникает ошибка, превышающая .ее порог чувствительйости. В противном случае корректирующее воздейст- .вие сохраняется некзменнью.В отличие от известной схемы . З 5аналого-циФрового .интегратора кор ректирующее воздействие,вырабатыва-.емое предложенным устройством,сохраняется сколь угодно долго, Этопозволяет существенно повысить точ-. 40ность аналого-циФровых, интеграторовс большими Постоянныки интегрирования(при весьма малых частотах следова-,ния импульсов) . Повышение точности .достигается не.только в Режимах. 45интегрирования, но и.в .Режимах .хра,нения, что имеет практическое зна- .чение для астатических системавтоматического управления. Возможностьсколь угодно длительного хранениякорректирующего воздействия. позволяет существенно увеличить постоянную .интегрирования путем введения.винтегратор управляемого делителя час-,тоты,Приведенная на Фиг.2 схема включения управляемого делителя 16. час-.тоты обеспечивает перестройку делителя по внешним сигналам блока 17.коэффициентов деления 11 е 1 е и . , 66При нулевых сигналах на входах 11 фй уп блока 17 и нулевом .сигналесо схемы 9 сравнения логические .элементы 35-41 формируют на входах 31и 33 делителя 16 частоты нулевые 5 сигналы, а на входах 32 и .34 - единич. ные. При этом реверсивные счетчики .29 и 30 импульсов имеют коэффициенты деления соответственно и и и, а общий коэффициент деления частоты составляет И в . Выходные .Коды .Ц и Йи с выходов счетчиков 29 и 30 преобразуются цифроаналоговым проеобразователем 18 в ступенчатое напряже- ние, имеющее ив квантов в каждом . периоде повторении и амплитуду, экви валентную одному, кванту основного цифроаналогового преобразователя .6, В этом, случае цифроаналоговый преобразователь 19 имеет минимальный коэфФициент передачи .(так как нулевой . сигнал воздействует лишь на младший разряд), и масштаб напряжения М(р соответствуечф одному кванту цифроаналогового преобразователя 18 (Ч:Ж),м фЕсли сигнал на входе. ф и фф. блока 17 принимает. единичное значение, то сигналы на входах 31 и,32 делителя 16 частоты изменяют свои значения, и . счетчик 29 настраивается на единичный коэффициент деления, причем выходной код Й становится равным нулю. При этом общий коэффициент деления частоты делителя 16 становится. равным щ, число квантов в периоде повторения напряжения также уменьшается до м (при той же амплитуде) а цифроаналоговый преобразователь 19 настраивается по нулевому сигналу со схемы, И-НЕ 41 на коэффициент передачн 4 И, в результате чего происходит соответствующее увеличение масштаба напряжения Чд.Когда сигнал на входе ф 1 блока17 имеет единичное значение, счетчики 20 и 30 работают с коэффициентами деления, равнъааи 1, и их выходные коды И и М равны нулю. Это соответствует. нулевому значению выходного напряжения преобразователя 18 ( Ч,8 = О) и максимальному коэффицйенту передачи преббразователя 19 (Ч - Ч ), так как иа все разряды последнего поступает нулевой сигнал с выхода инвертора 39.Следовательно, в предложенной схеме обеспечивается Формирование двух напряжений (ступенчатого с преобразо вателя 18 и пилообразного с преобразователя 19), которые позволяют сгладить ступенчатое напряжение основного цифроаналогового преобразователя 6 при всех возможных коэффициентах делениячастоты, задаваемых внешними дискретными сигналами.Рассмотрим теперь работу аналогоциФрового интегратора при сбоях реверсивного счетчика 5, вызванных, например, действием случайных помех. При этом из-за ограниченной скорости отработки блока 8 слежения-хранения сигналы на входах обеих схем 9 и 10 сравнения отличаются на величину,1937280 и 3 превышающую их пороги срабатывания, в результате чего на выходе блока выделения модуля 15 появляется единичный сигнал. Этот сигнал переводит блок 8 слежения-хранения в режим хранения и через блок 17 настраивает делитель 16 частоты на единичный коэффициент деления, Одновременно ,.счетчик 21 устанавливается в нулевое состояние н удерживается в этом состоянии независимо от наличия импульсов на его счетном входе. Выходное напряжение схемы 9 сравнения поступает на Форсирующий вход преобразователя 1 напряжение-частота, который воздействует яа делитель 16 частоты 15 и счетчик 5, изменяя выходное напряжение сумматора 7 до тех пор, пока не произойдет выключение схемы 9 сравнения. После этого выходное напряжение блока 15 выделения модулястановится равным нулю и счетчик 21 ереходит в режим счета импульсов, оступающих на него с генератора 24. Счет импульсов продолжается до тех пор, пока разность выходных сигналов. 25 ,блока 8 слежения-хранения и сумматора 7 не снизится до порога отпуска- . ния схемы 10 сравнения, т.е. до вол" ного восстановления информации в счетчике 5 импульсовБлагодаря наличию связи с выходаЗО блока 15 выделения модуля на вход 23 установки нуля счетчик 21 при восста.новлении информации блокируется ивключается лишь для точной. доводкисхемы на конечном этапе восстановле"ния информации. Благодаря этому исключается ограничение динамическогодиапазона сигнала коррекции, котороемогло бы произойти при работе устройства в этом режиме. Таким образом, благодаря применению в предложенном устройстве управляемого делителя частоты и контура сглажи" вания на двух цифроаналоговых преобразователях, коэффициенты передачи которых изменяются определенным образом при перестройке делителях часто" ты, а также за счет построения контура коррекции погрешностей на основе счетчика импульсов и цифроаналогового преобразсвателя, соответствующим образом соединенных с другими элемента-ми аналого-цифрового интегратора, по вышается точность работы устройства при больших постоянных интегрирования. Использование в интеграторе управляемого .делителя частоты позволяетизменять постоянные интегрированияпо необходимым законам, попьзуясьвнешними дискретными входами блоказадания коэффициента деления.

СмотретьЗаявка

3432573, 28.04.1982

ОРГАНИЗАЦИЯ ПЯ А-3500

ГЛАЗОВ МИХАИЛ НОСОНОВИЧ, КОЛМЫКОВ ЕВГЕНИЙ ВИКТОРОВИЧ, НИКУЛИН ЭДУАРД СЕРГЕЕВИЧ

МПК / Метки

МПК: G06G 7/18

Метки: аналого-цифровой, интегратор

Опубликовано: 23.08.1983

Код ссылки

<a href="https://patents.su/7-1037280-analogo-cifrovojj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой интегратор</a>

Предыдущий патент: Дифференцирующее устройство

Следующий патент: Корреляционное устройство

Случайный патент: Способ получения молочной кислоты