Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 991445

Автор: Борзых

Текст

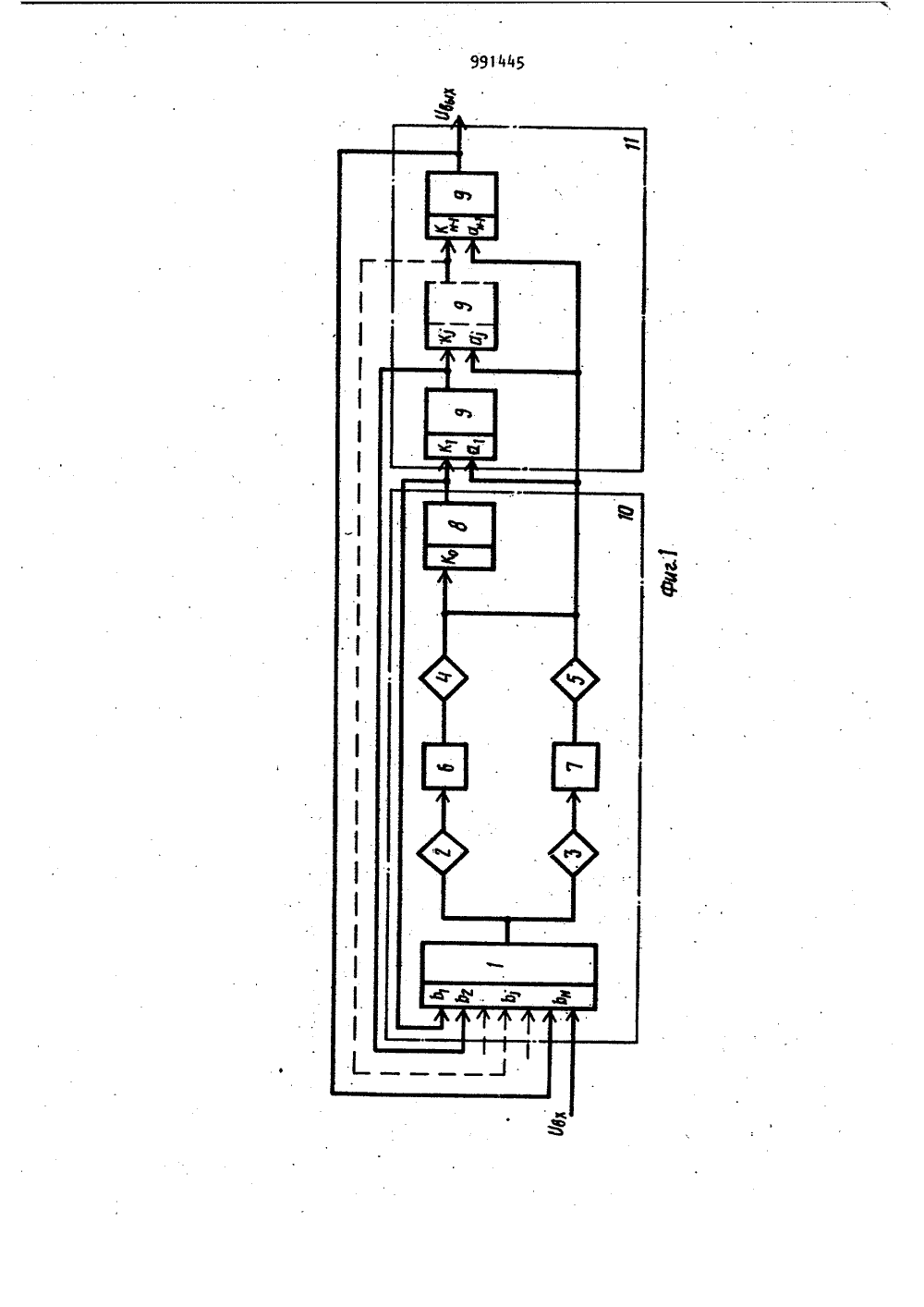

(71) Заяви 4) ИНТЕРПОЛЯТОР тем,наИзобретени вателям дискр налов в непре пользовано в томатического вах обработки измерений. о ных вны о и пр ис о устроиства явешности восстаосится к преобраэо(по времени) сиге и может быть исьсных системах аввления и устройстретных результатов Известен интерного порядка, исп тельную обратную ции на каждом пос рументальных ошиб накопленных на пр держащий цепочки,выполнена в виде единенныхсуммато вого запоминающег тегратора, а межд интеграторов кажд первой, установле ключи 1) Недостатком эт ляется наличие поолятор проиэволь- . льзующий отрицавязь для компенсаедующем шаге инстк интегрирования, дыдущем шаге, сокаждая из которых оследовательно соа, ключа, аналогоустройства и инвходами и выходами и цепочки, крометоы дополнительные новления функции, обусловленночто процесс фиксации приращеникладывается на процесс интегриния этих приращений. Наиболее близким по технической сущности к изобретению является ин" терполятор, содержащий блок повышения порядка интерполяции, выполненный на (М) -м интеграторе, выход каждого иэ которых соединен с первым входом последующего интегратора, и блок интерполяции первого порядка, состоящий иэ сумматора и интегратора, выход которого соединен с первым входом сумматора, второй вход сумматора является входом устройства, а выход соединен с входом интегратора блока интерполяции первого порядка через две соединенные параллельно цепочки, каждая из которых состоит иэ последовательно соединенных первого ключа запоминающего элемента и второго ключа 2,)Э 99144Йедостатком этого устройства является его сложность, обусловленнаянеобходимостью использования двухблоков нелинейной интерполяции, двухдополнительнительных сумматоров идвух дополнительных ключей.Целью изобретения является упрощение устройства.Поставленная цель достигается тем,что в интерполяторе, содержащем блок 1 Оповышения порядка интерполяции, выполненный на (М)-м интеграторе, выход каждого иэ которых соединен спервым входом последующего интегратора, и блок. интерполяции первого 1порядка, состоящий из сумматора и интегратора, выход которого соединен спервым входом сумматора, второй входсумматора, второй вход сумматораявляется входом устройства, а выходсоединен с входом интегратора блокаинтерполяции первого порядка черездве соединенные параллельно цепочки, .1каждая из которых состоит из последовательно соединенных первого ключа, фзапоминающего элемента и второго ключа, сумматор дополнительно содержит(М) входов, каждый из которых соединен с выходом соответствующегоинтегратора блока повышения порядка ЗОинтерполяции, вторые входы интеграторов блока повышения порядка интерполяции соединены с входом интегратора блока интерполяции первого порядка, а выход (М)-го интегратора ззблока повышения порядка интерполяцииявляется выходом устройства,На фиг.1 представлена блок-схемаустройства; на фиг.2 - графики сигналов, поясняющие принцип работы интер 40полятора.Блок-схема устройства содержитсумматор 1, ключи 2-5, запоминающиеэлементы 6 и 7, интегратор 8 блокаинтерполяции первого порядка, интег 4раторы 9 блока повышения порядка ин-,терполяции, блок 10 интерполяции первого порядка, блок 11 повышения порядка интерполяции.Интерполятор работает следующим Эобразом.Пусть порядок интерполяции М=2, Вэтом случае блок 11 повышения порядка интерполяции содержит только одининтегратор 9, на один вход которогопоступает сигнал с выхода интегратора 8, Коэффициент передачи этой цепи К 1 должен быть равен 1. На другой 5 4вход интегратора 9 поступает сигнал с выходов ключей ч и 5, Коэффициент передачи по этой цепи а 4 должен быть равен 0,5, Сигналы обратных связей подаются с выходов интеграторов 8 и 9, на входы сумматора 1 с коэффициентами Ь =-1, Ь=-1.На вход интерполятооа в момент временис периодом Т, равным постоянной времени интеграторов 8 и 9, поступает ступенчатое напряжение, величина каждой ступени которого соответствует значению интерполируемой Функции в укаэанный момент времени,Работа интерполятора различна для четных и нечетных периодов интерполирования. В нечетные интервалы времени замкнуты ключи 2 и 5, остальные ключи - 3 и 1 - разомкнуты, в четные - наоборот.В нечетные интервалы времени осуществляется запоминание на элементе 6 значения напряжения, поступающего с выхода сумматора 1, и интегрирование выходного сигнала запоминающего элемента 7 с целью формирования сигналов обратных связей и выходного сигнала интерполятора.В четные интервалы времени происходит запоминание на элементе 7 значения напряжения, поступающего с выхода сумматора 1, и интегрирование выходного сигнала запоминающего элемента 6 с целью формирования сигналов обратных связей и выходного сигнала интерполятора.Таким образом осуществляется разделение во времени процессов запоминания приращений и их интерполирования.Более подробно принцип действия интерполятора поясняет пример Формирования его реакции на одиночный импульс.В исходном состоянии выходные напряжения запоминающих элементов 6 и 7 и интеграторов 8 и 9 равны нулю, При поступлении в момент времени входного импульса с амплитудой 0(1 л) (фиг.2 а) ключи 2 и 5 открываются, а на выходе сумматора 1 появляется импульс прямоугольной формы (фиг,2 б). На отрезке с,(, й производится запоминание амплитуды этого импульса в элементе 6 (Фиг.2 в). Сигналы на выходах интеграторов 8 и 9 не изменяются (Фиг.2 д и е) потому, что через открытый ключ 5 на входы интеграторов45 6Выходное напряжение сумматора на отрезке 1 1+, С 1 подается через откры.тый ключ 3 на вход запоминающего эле.мента 7, на выходе которого в момент времени 1 Фиксируется напряжение, равное нулю.В момент времени с ключи 3 и 4 закрцваются, а ключи 2 и 5 открываются. Через открытый ключ 5 выходное напряжение запоминающего элемента равное нулю, подается иа входы интеграторов 8 и 9 Выходные сигналы интеграторов не изменяются, поэтому напряже" ния на выходах интеграторов 8 и 9 и сумматора 1 на отрезке С , 16 равны нулю, Через открытый ключ 2 выходное напряжение сумматора подается на вход запоминающего элемента 6 и фиксиру- ется.Таким образом, после момента времени с амплитуда выходных напряже, ний запоминающих элементов и интеграторов становится равной нулю, т,е. восстанавливаются нулевые начальные условияБсли на вход интерполятора поступает ступенчатое напряжение показанное на фиг.2 а пунктиром, выходной сигнал интерполятора можно представить ввиде интерполяционного многа- члена в Форме Лагранжа. )ля произвольного момента времени йкб= с-с 5 .9914 поступает сигнал нулевой амплитуды (Фиг,2 г). В момент. времениамплитуда входного сигнала уменьшается до нуля. Ключи 2 и 5 закрываются, а ключи 3 и 4 открываются. Через открытый ключ 4 напряжение, амплитуда которого постоянна и равна 0(т., ), подается с выхода запоминающего элемента 6 на входы интеграторов 3 и 9.Принимая во внимение, что К =1, 10 К 1=1, а =0,5, аналитические выражеФ 1 Ф Вния сигналов на выходе интеграторов 8 и 9 можно. записать в виде0 (,6)=ВТАлЯ ОМУ-Т, (1)0 (6) =0,5(бт)+0,5(бЧт)длЯ 0-б т, Р) й:Ис.,) Юк-) ,Г выражения сигналов на выходах интеграторов на отрезке й, 4 имеют ззвидО (О)=1-2 ЮТ)дл% 06 Т (,Ч0 Ж)=1-(61 Т )ч 0(7 т И)где О = й - ел .40Выходное напряжение сумматора наотрезке й, С, подается через открытый ключ 2 на вход запоминающего элемента 6, на выходе которого в моментвремени й 4 Фиксируется напряжение0(с ) .При С=1 ключи 2 и 5 закрываются,а ключи 3 и 4 открываются. Через открытый ключ 4 выходное напряжениезапоминающего элемента б величиной0(й ) подается на входы интеграторов8 и" 9.Аналитические выражения для сигналов на выходах интеграторов на отрезке й, 15 имеют вид5ОцО)=-1+(бП) . Алч О-Т, (В)О (О=о,ВФП)-о,5 И(т),аи о-бт, (ь)где СЪГ - С,где (ъ" = й.- .Начиная с момента времени й , на выходе сумматора 1 Формируется сигнал, соответствующий инверсной сумме на- фО пряжений, которые Формируются на интеграторах 8 и 9. Выходное напряжение сумматора на отрезке й, й 1 подается . через открытый ключ 3 на вход запоминающего элемента.7, на выходе которо-го в момент времениФиксируется напряжение с амплитудой -20( ).В момент времени г ключи 3 и 4 . закрываются, а ключи 2 и 5 открываются, Через открытый. ключ 5 выходное Зф .напряжение запоминающего элемента 7, равное -20(т ), подается на входы интеграторов 8 и 9, Аналитические 05 ЯР(т )-05 ЩТ 1цЬ.(5 - 0 - .О Таким образом, если блок повышения порядка интерполяции содержит один интегратор, интерполятор решает за" дачу интерполяции входного сигнала многочленом второй степени. В том случае, когда блок повышения порядка интерполяции содержит (М) интегратор. устройство осуществляет интерпо-. ляцию входного сигнала многочленом степени й,В процессе преобразования ступенчатого напряжения, поступающего на вход интерполятора, в,непрерывный сигнал, возникает задержка, равная периоду замыкания ключей 2-5.Упрощение интерполятора достигнуто за счет использования одного блока повышения порядка интерполяции вместо двух блоков нелинейной интерполяции. Кроме того, блок повышенияпорядка интерполяции по сравнению с блоком нелинейной интерполяции, не содержитразрядных ключей, сумматоров, блоков выборки и хранения,Таким образом, данный интерполятор . позволяет осуществлять интерполюцию сигналов без методической погрешнос" ти, причем для его построения требуется меньше элементов. формула изобретенияИнтерполятор, содержащий блок по- ф выйения. порядка интерполяции, выполненный на (й) -ом интеграторе, выход каждого из которых соединен с первым входом последующего интегратора, и блок интерполяции первого порядка, фВ состоящий из сумматора и интегратора, выход которого соединен с первым входом сумматора, второй вход сумматора является входом устройства, а выход . соединен с входом интегратора блока фз. интерполяции первого порядка черездве соединенные параллельно цепочки,каждая из которых состоит из последовательно соединенных первого ключа,запоминающего элемента и второго ключа, о т л и ч а ю щ и й с я тем, что,с целью упрощения конструкции., сумматор дополнительно содержит (й) входов, каждый из которых соединен свыходом соответствующего интегратораблока повышения порядка интерполяции,вторые входы интеграторов блока повышения порядка интерполяции соединеныс входом интегратора блока интерполяции первого порядка, а выход (Й)го интегратора блока повышения порядкаинтерполяции является выходом устройства.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРЮ 480094, кл, О 06 К 7/1 О, 1975.2. Авторское свидетельство СССРИ 765821, кл. 6 06 6 7/30, 1980

СмотретьЗаявка

3300954, 12.06.1981

РЯЗАНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

БОРЗЫХ ВЛАДИМИР ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор

Опубликовано: 23.01.1983

Код ссылки

<a href="https://patents.su/6-991445-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Устройство для воспроизведения функций

Следующий патент: Устройство для задания граничных условий

Случайный патент: Способ испытания гидропривода ведущих колес транспортного средства