Сумматор-интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

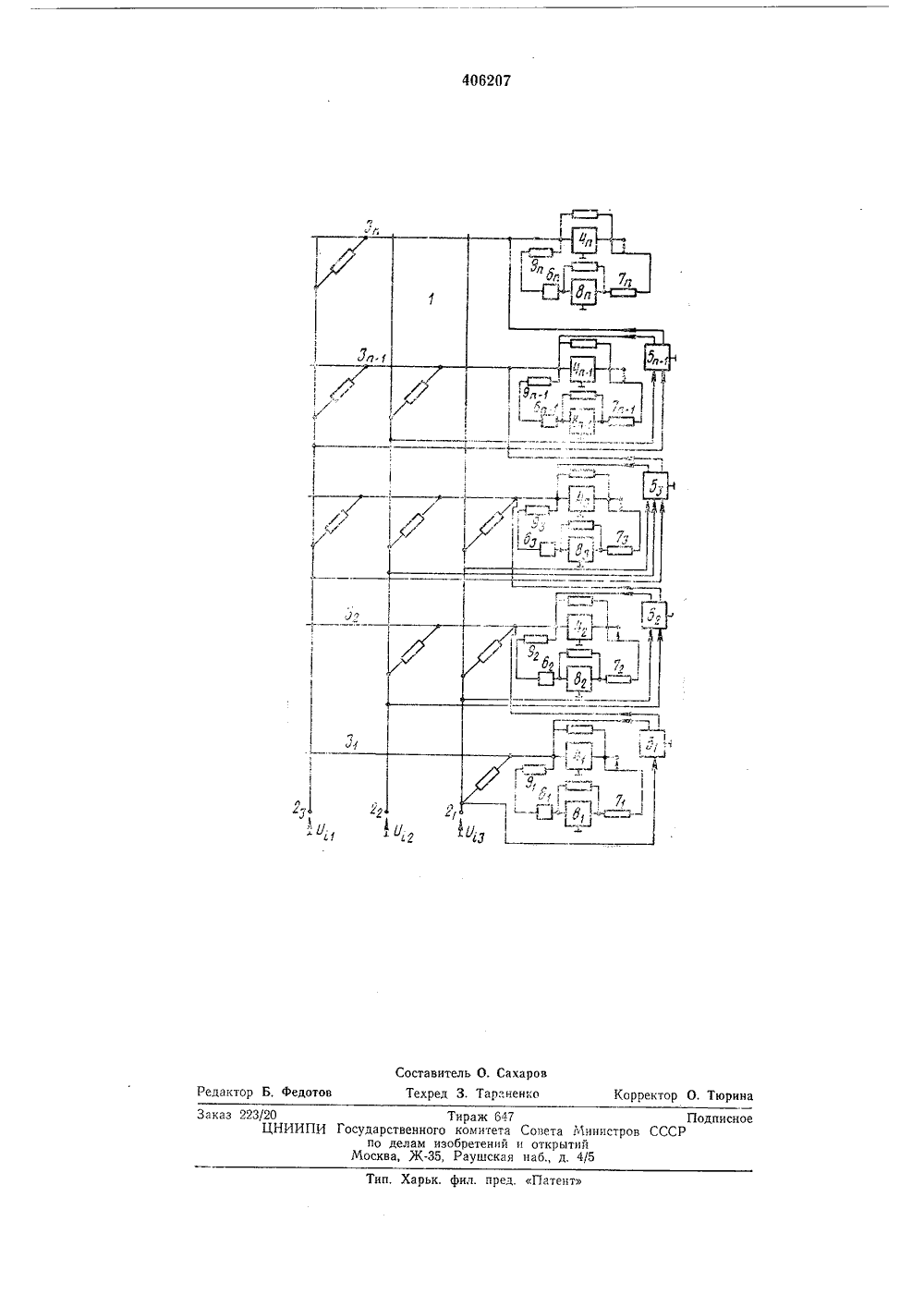

ОП ИСАНИ Е ИЗОБРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советских Социалистиц.ескит 1 Республик406207 Зависимое от авт, свидетельства-Заявлено 09.Х 11.1971 ( 1723282/18-24 Кл, Ь Обд 7/18 присоединением заявк осударстаенный комитетСовета Министрое СССРпо делам изооретенийи открытий и орите Опубликовано 05.Х 1.1973. Бюллетень45Дата оп)убликования описания 22.11.1974 К 681.335.8Авторыизобретения Е. Пухов, В. ф. Евдокимов, Л, А. Казакевич, А. С. Огир, Н. П. Тимошенко и Б, К, Крыжный Институт электродинамики А инской ССР аявител УММАТОР-И НТЕГРАТ2) соот на первом устройства 1+ 2+ (. 3.) 32( 33) ) Сумматор-интеграющую резистивную мми шинами 2, - 2, исумматоры с резистими 4, - 4, блоки пердержки б - б на7 - 7, инверторы сми связями 8, - 81 п тор содержит суммируатрицу 1 с )вертикальны- горизонтальными 81 - 8 вными обратными связяеноса б - 51, линии заодин такт, резисторы ,резистивными обратныи входные резисторы 30 ии задержки ются на вхоение вектора значение инфункций на ды устройства У 2 У 22, С,23одных функ Изобретение относится к гибридной вычислительной технике.Известны сумматоры-интеграторы, содержащие суммирующую резистивную матрицу,вертикальные шины которой соединены с основными входами, а горизонтальные подключены ко входам соответствующих сумматоров,блоки переноса, линии задержки, резисторыи инверторы с резистивными обратнымисвязями.С Оделью повышения точности выполненияматематических операций в каждом разрядепредлагаемого устройства выход сумматорачерез резистор соединен со входом соответ 15ствующего инвертора, выход которого черезпоследовательно соединенные линию задерж 1 си и входной резистор подключен ко входусумматора,Принципиальная схема устройства приве.дена на чертеже. Интегрируемые функции временив каждый момент представляются ветственно векторами напряжений) = -)111-)1213 ).)2 21 22 233 ( ). 31)-)32) 33)Компоненты векторов пропорциональны значениям соответствующих разрядов чисел (для рассмотрения принципа работы предлапаемого устройства интегрируемые функции представлены тремя разрядами).В момент времени 1 = О, т, е. шаге интепрированияна входы поступают векторы напряжений1 - ( 11)-) 12 13) ) ) 2 = -) 21)22)-) 23) ).) 3 = (.) 31 32) 33)На выходах устройства образуется вектор напряжений0 (0102 03)+ ) 31 компоненты ,которого через лин б - б на один такт опять пода ды сумматоров 4 - 4,. Умнож .,0 на М дает приближенное теграла суммы иинтегрируемых первом шаге. При 1 = 1 на вхо поступают векторы .напряжений соответствующие значениям вхций на втором шаге интегрирования, которые, складываясь с вектором Го -- Г+ Гз+ Гз, поступающим на входы сумматоров 4 - 4 в начале второго такта из линий задержки 6 - б, образуют вектор напряжений СО = = Го+ И+Рз+ СРз Умножение векторами/" на ,дает приближенное значение интеграла суммы функций,на первом и втором шагах интегрирования. Таким образом, интеграл суммы трех функций на т шагах интегрирования определяется выражением где т - количество шагов интегрирования;11 - шаг интегрирования, который в общем случае может быть многоразрядным. 20Выбор числа разряда шага интегрировая определяется, с оджой стороны, разрядностью представления чисел входных функций, с другой стороны - удобствами тактирования работы устройства и упрощения его 25 схемы, Для случая представления интегрируемых функций тремя разрядами он может достигать только трехразрядного числа, т. е. Л = ЛЛ,Лз. Лучше всего шаг интегрирования выбирать таким, чтобы знача щая цифра была в одном из разрядов, например А 1, а Лз=1 з = О. Это упрощает схему устройства, так как резистивная матрица 1 становится при этом квадратной и диагональной. 35Если проводимости матриц 1 - 3 удовлетворяют соотношениямЬ ) Дгз2, Дз(где- номер матрицы), работа устройства в точности описывается выражением (1), т, е. 40 устройство интегрирует сумму трех функций по методу прямоугольников и умножает их на единичные коэффициенты. Чтобы получить устройство, интегрирующее сумму функций и умножающее их на постоянные коэффициенты, отличные от единицы, необходимо предварительно умножить величины этих коэффициентов на шаг интегрирования и параметры, матриц подбирать пропорциональными разрядам этого произведения. Работа устройства в этом случае описывается выражен,иеми 3Ы = У,(М а) й,/= й - 1где т - количество шагов интегрирования;1 - шаг интегрирования;а - величина постоянного коэффициента, на которую умножается п-,ная функция.Блоки переноса б - б выполняют меж. разрядный перенос с одновременной компенсацией напряжения в усилителе, из которого возник перенос.Предм ет изобретенияСумматор-,интегратор, содержащий суммирующую резистивную матрицу, вертикальные шины которой соединены со входами сумматора-интегратора, а горизонтальные подключены ко входам соответствующих и сумматоров с резистивными обратными связями, и - 1 блоков переноса, входы которых соединены с вертикальными шинами суммирующей резистивной матрицы, а выходы подключены ко входам сумматоров данного и следующего разрядов, п линий задержки, резисторы и и инверторов с резистивными обратными связями, отличающийся тем, что, с целью повышения точностями, в каждом его разряде выход сумматора через резистор соединен со входом соответствующего инвертора, выход которого через последовательно соединенные линию задержки и входной резистор подключен ко входу сумматора., с 71 Составитель О. Сахароведактор Б. Федотов Техред 3. Тарененко Корректор О, Тюрина аказ 223/20 Подписно ЦНИИПИ Г ров СССР Тираж 647 осударственного комитета Совета Минист по делам изобретений и открытий Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

1723282

Институт электродинамики Украинской ССР

Г. Е. Пухов, В. Ф. Евдокимов, Л. А. Казакевич, А. С. Огир, Н. П. Тимошенко, Б. К. Крыжный

МПК / Метки

Метки: сумматор-интегратор

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-406207-summator-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Сумматор-интегратор</a>

Предыдущий патент: Л

Следующий патент: Устройство для проверки и настройки функциональных преобразователей двух переменных

Случайный патент: Способ автоматического регулирования цикла