Интегральная микросхема и микропроцессора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

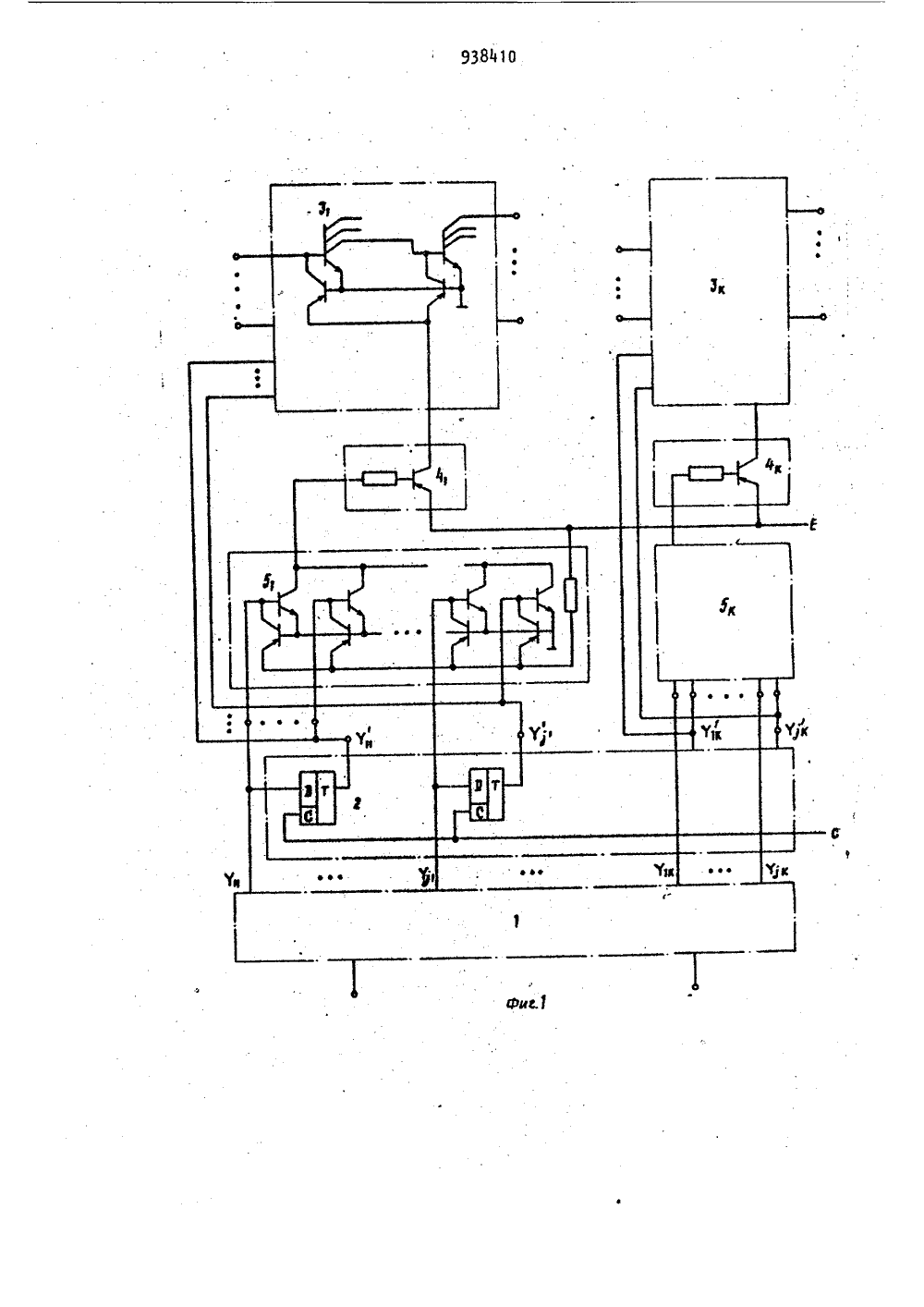

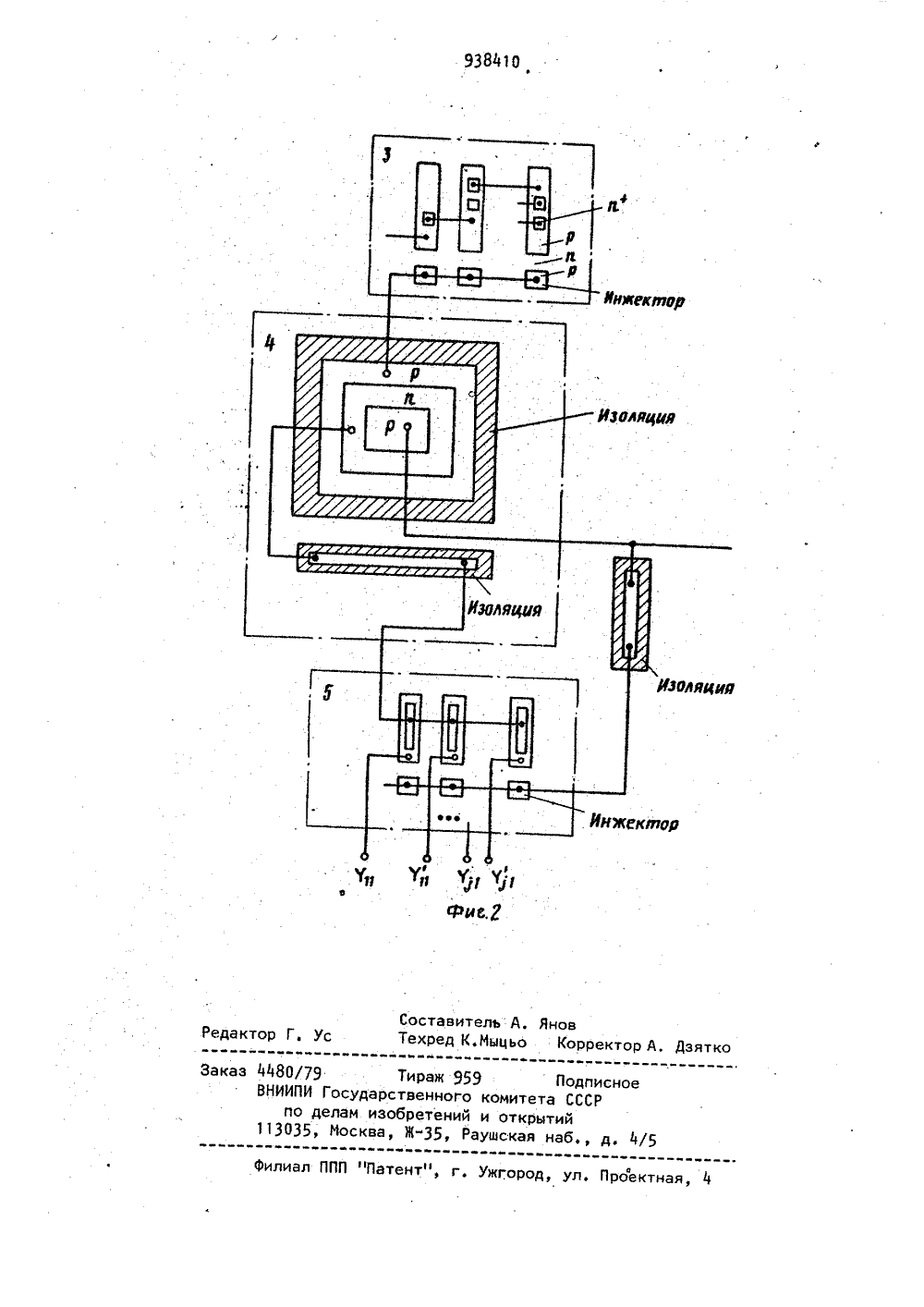

Союз СоветсиикСоциалистическихРеспублик ОЛ ИСАНИЕ ИЗОБРЕТЕН ИЯ и 1 93841 О К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(51)М. Кл. Н 03 К 19/091 Ьеударстааанцй комитет СССР дю делам кзобретений н еткрцткйс присоединением заявки РЙ -,083(088.8) Дата опубликования описания 23. 06. 82(72) Авторы изобретени М. К. Бушуев и И, И. Московский ордена Трудового Крас инженерно-физический институт Заявител 5 Й) ИНТЕГРАЛЬНАЯ МИКРОСХЕМА И Л МИКРОПРОЦЕССОРА 2 ны с уп вующего ов 2. извест я потреавляющими вхо"1-го узла опенцх устройствбляемая мощ" торого соедине дами соответст ,рационных блокНедостаткам является больш ность. Изобретение относится к микроэлектронике и может быть использовано при построении больших интегральных микросхем микропроцессоров на основе интенционной логики.Известно устройство, построенное на элементах .изопланарной интенционной логики и содержащее оперативные блоки, узел управления и операционный регистр 1,тоИзвестно такие устройство, построенное на элементах интенционной логики И Л , содержащее К узлов оперативных блоков, узел управления, имеющий К групп управляющих выходов, операционный регистр, имеющий К групп разрядов для хранения сигналов, управляющих узлами опера" тивных блоков, управляющие выходц каждой -й группы узла управления 2 о соединены с управляющими входами соответствующей 1-й группы разрядов операционного регистра, управляющие выходы каждой 1-й группы разрядов коЦель изобретения - уменьшение потребляемой мощности.Поставленная цель достигается тем, что в устройство, содержащее К узлов оперативных блоков, узел управления, имеющий К групп управля" ющих выходов, операционный регистр, имеющий К групп разрядов для хранения сигналов, управляющих узлами оперативных блоков, управляющие выходы каж дой 1-й группы узла управления сое" динены с управляющими входами сост ветствующей 1-й группы разрядов операционного регистра, управляющие выходы каждой 1-й группы разрядов котороГо соединены с управляющими входами соответствующего 1-го узла операционных блоков, введены К клюПрименение микросхем микропроцессоров. с отключением узлов оператив" ных блоков в сложных цифровых системах позволяет значительно уменьшить общую потребляемую мощность систем. Формула изобретения 1. Интегральная микросхема И Л мик" ропроцессора, содержащая К узлов оперативных блоков, узел управления, имеющий К групп управляющих выходов, операционный регистр, имеющий К групп разрядов для хранения сигналов, управляющих узлами оперативных блоков, управляющие выходы каждой 1-й группы узла управления соединены с управляющими входами соответствующей 1-й группы разрядов операционного регистра, управляющие выходы каждой 1-группы разрядов ко" 5 93841Реализация элемента ИЛИ-НЕ 5, ключа 4 коммутации тока питания и частьэлементов И Л узла оперативных бло"кв 3,показана на фиг.2. ИнверторыИ Л,образующие элемент ИЛИ-НЕ имеют такую же физическую структуру,как элементы И Л, используемые в узлах 1-3. Транзисторы ключей 4 ком"мутации тока питания располагаютсяв изолированных областях полупроводника, которые размещаются на пери"ферии кристалла микросхемы, Так какК-число узлов оперативных блоков 3относительно невелико (обычно на двапорядка меньше общего числа элементов в микропроцессоре, то возрастание площади кристалла из"эа введе"ния дополнительных элементов и ключей не превышает нескольких процентов. 20Иикросхема И В микропроцессораработает следующим образом,При поступлении команды на управляющие входы микропроцессораузел управления 1 вырабатывает управляющие сигналы (У, У,.); (УуаУ.),. (У, У;) каждая группа которых управляет работой соответствующего 1-го узла оперативныхблоков 3. Для узлов оперативных блоков 3, не участвующих в выполненииданной команды, все управляющие сиги нналы имеют значение логического 0(низкий потенциал нземли"): (у,У)=00 При поступлении тактового сигнала С значения всех управляющих сигналов У записываются в со-.ответствующие разряды операционногорегистра 2, и хранятся там в течение всего цикла обработки информации,Управляющие сигналы У с выходов операционного регистра 2 поступают науправляющие входы узлов оперативныхблоков 3, которые в соответствии сэтими сигналами производят необходимые операции для выполнения данной команды. При этом на управляющие входы микропроцессора поступает новая ( последующая) команда56выполняемой программы, и на выходахузла управления 1 образуются новыезначения управляющих сигналов У 1,определяющие выполнение этой коман"Дыэ55Таким образом, сигналы Уи Уна выходах операционного регистра иузла управления определяют, соответ-ственно, выполнение текущей и последу 0 6уЬ ющей команды программы. Эти сигналы поступают на входы элементов ИЛИ-НЕ 5, Если яизъюнкция сигналов У и Ур ф поступающих на входы 1"го элемен та ИЛИ-НЕ не равна нулю, то это значит, что 1-й узел оперативных блоков .3 участвуетв выполнении текущей или последующей команды программы. В этом случае протекает базовый ток р"и"р-транзистора в 1"м ключе 4 коммутации тока питания. Этот транзистор открывается и подает ток питайния для элементов И Л 1-го узуа опе ративных блоков 3. Если же (т+ У) О, то все выходные транзисторы ин" , верторов ИП в 1-м элементе ИЛИ"НЕ 5 закрыты, р"и-р-транзистор 1-го ключа 4 коммутации тока питания также зак" рыт, и в 1-й узел оперативных бло-, ков 3 не поступает ток питания. Таким образом, узлы оперативных блоков 3, .не участвующие в выполнении текущей и последующей команды, отключаются от источника питания и не потребляют мощность.Переключение элементов ИЛИ-НЕ 5 и ключей 4 коммутации тока питания в состояние, необходимое для выполне-, ния последующей команды производит" ся в течение цикла выполнения теку" щей команды. Таким образом, в микро" схеме реализуется предварительное включение тока питания узлов оперативных блоков , благодаря чему бы" стродействие Иф Й микропроцессора сохраняется на прежнем уровне.торога соединены с управляющими входами соответствующего 1-го узла операционных блоков, о т л и ч а ющ а я с я тем, что, с целью уменьаения потребляемой мощности, в нее 5 введены К ключей коммутации тока питания и К элементов ИЛИ-НЕ, причем входы каждого 1-го элемента ИЛИ"НГ соединены с управляющими выходами 1-й группы узла управления и с вы" ф ходами -й группы разрядов операционного регистра, выходы каждого 1"го элемента ИЛИ-НЕ соединены с управляющим входом 1-го ключа коммутации тока питания, токовый выход каждого О "го ключа коммутации тока питания соединен с входом питания 1-го узла оперативных блоков, токовый вход всех К ключей коммутации тока питания соединен с входом питания уст ройства2,Микросхема по п,1, о т л и ч а ющ а я с я тем, что в качестве элементов ИЛИ-НЕ используются инверторы И,Л, входы которых соединены 25 с соответствующими выходами 1-й груп пы узла управления и операционного регистра, выходы инверторов И Л подй ключены к выходу элемента ИЛИ-НЕ, в качестве ключей коммутации тока питания используется р-и-р-транзисто" ры, база каждого из которых через резисторы соединена с управляющими, входами соответствующего ключа коммутации тока питания, коллектор и эмиттер каждого транзистора соединены соответственно с токовым выходом и токовым входом соответствующего ключа коммутации тока питания. Источники информации,принятые во внимание при экспертизе1. Вильнаи, Верхофштадт. Однокристальная БИС центрального процессорадля универсальных миникомпьютеров,"Электроника", 1977, 8 13, т.50,с, 36, рис. 2,2. Хортон Энглейд, Иакж, Интегральная интекционная логика - важное достижение технологии биполярных ИС.-Электроника", 1975, У 3,т. 18, с, 32, рис. 11 (прототип),938410 Ур Ъ оставитель А. Яновехред К.Мыцьо Корректор А, Дзят с дакто аз 4480/79 Тираж 959 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж"35, РаПодписноеомитета СССРоткрытийшская наб д. 4/т ещтная, 4 лиал ППП "Патент", г. Ужгород, ул.

СмотретьЗаявка

3008123, 17.11.1980

МОСКОВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНЖЕНЕРНО ФИЗИЧЕСКИЙ ИНСТИТУТ

БУШУЕВ МИХАИЛ КОНСТАНТИНОВИЧ, ШАГУРИН ИГОРЬ ИВАНОВИЧ

МПК / Метки

МПК: H03K 19/091

Метки: интегральная, микропроцессора, микросхема

Опубликовано: 23.06.1982

Код ссылки

<a href="https://patents.su/6-938410-integralnaya-mikroskhema-i-mikroprocessora.html" target="_blank" rel="follow" title="База патентов СССР">Интегральная микросхема и микропроцессора</a>

Предыдущий патент: Устройство защиты от помех

Следующий патент: Мажоритарное резервированное счетное устройство

Случайный патент: Способ измерения толщины стенки труб