Способ параллельно-последовательногоаналого-цифрового преобразования

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

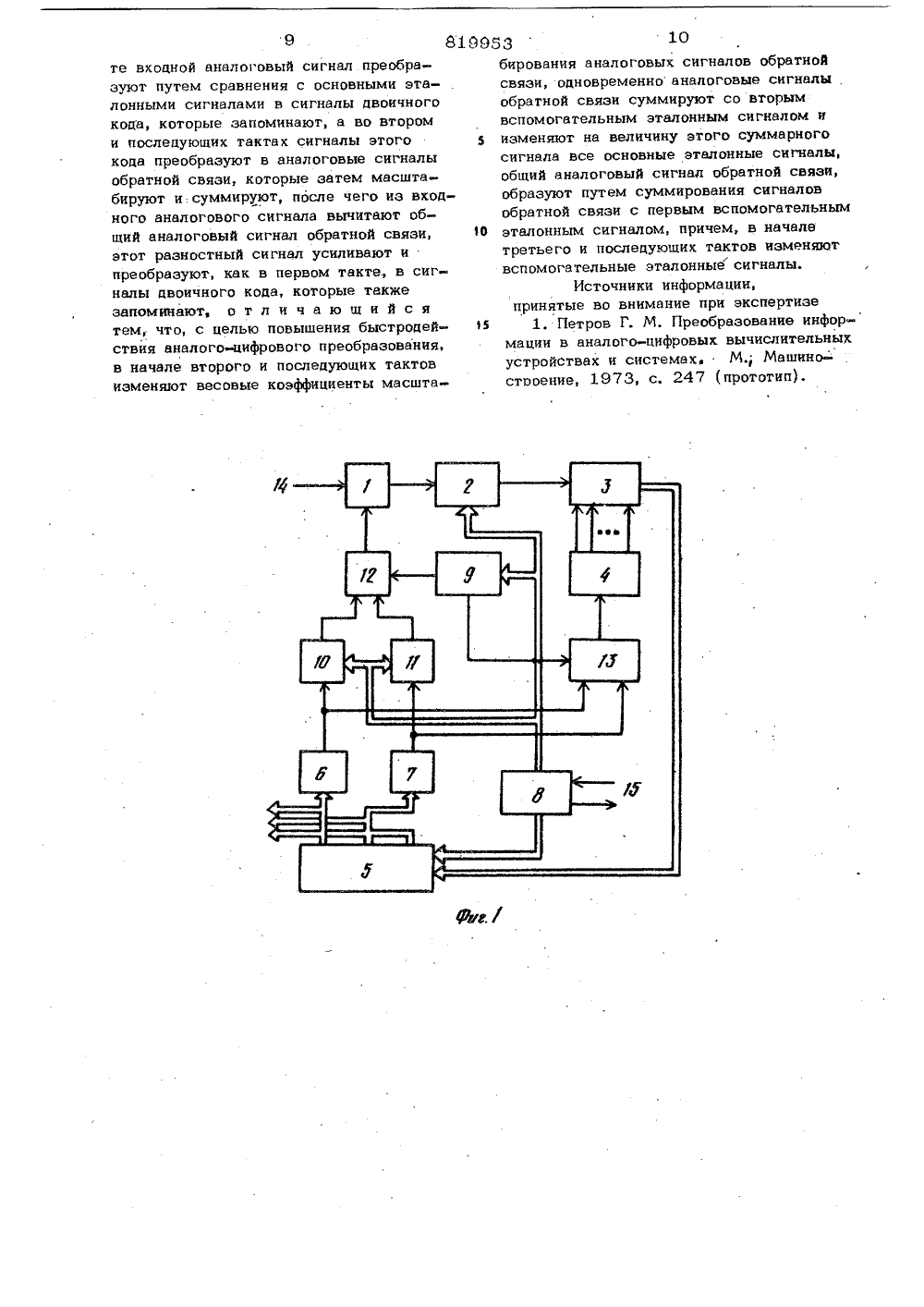

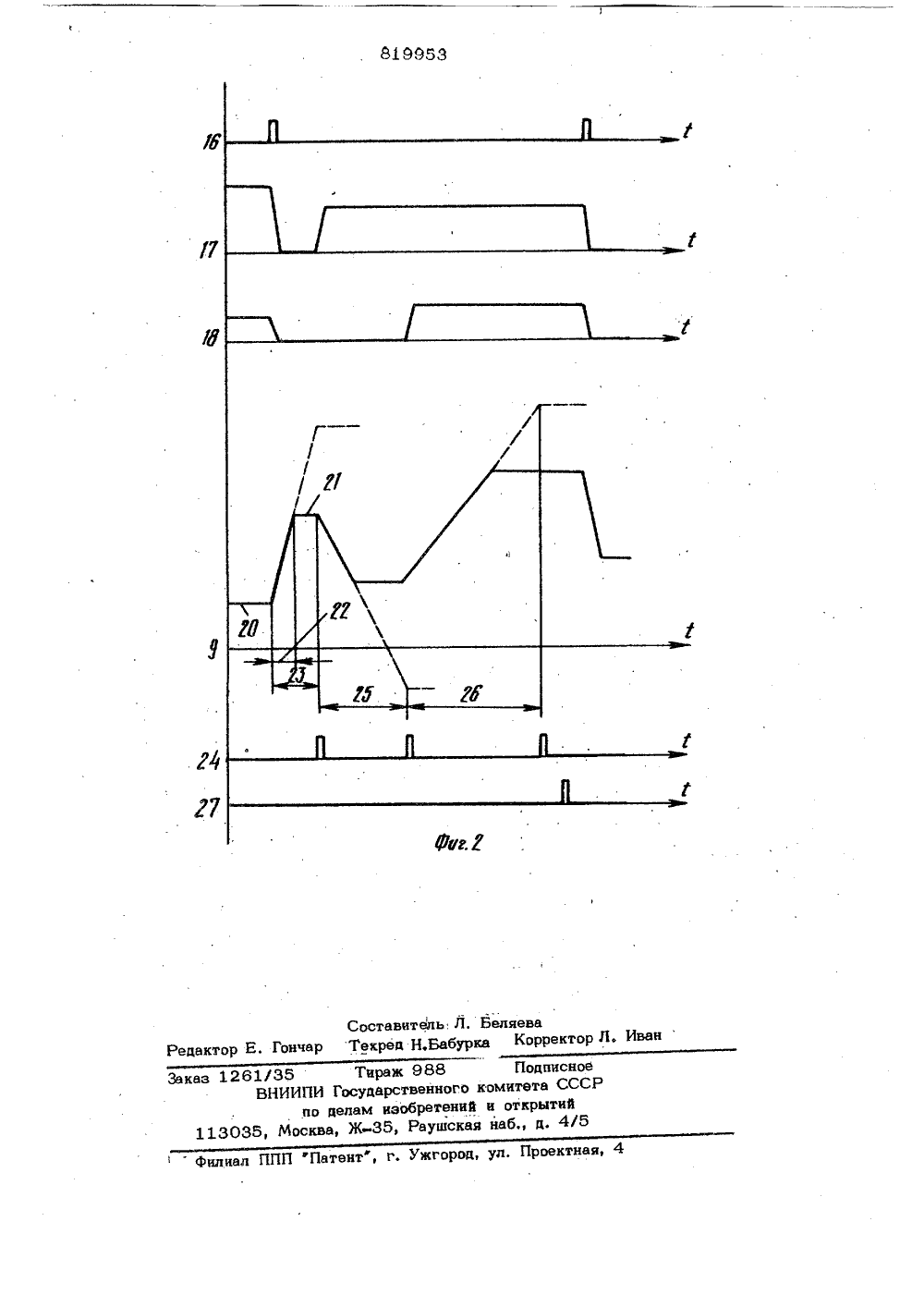

ОПИСАНИЕИЗОБРЕТЕНИЯХ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическмкреспублик и 819953. свид-ву 21) 2761246/18-21 5.79 2)Заявлено 03 К 13/03 ксоединением заявки Гввудврстввнный квинтет СССР нв делам нзввретвннй н вткрмтнй) СПОСОБ ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ сной в этом способе вре кажцом такте опре Изобретение относится к импуль технике и может быть использовано для создания аналого-цифровых преобразовате лей параллельно-последовательного типа с повышенным быстродействием.Известен способ параллельно-последовательного аналого-цифрового преобразования, заключающийся в том, что в первом такте входной аналоговый сигнал преобразуют путем сравнения с основны,ми эталонными сигналами в сигналы двоичного кода, которые запоминают, а во втором и последующих тактах сигналы этого коца преобразуют в аналоговые сигналы обратной связи, которые затем масштабируют и суммируют, после чего из входного аналогового сигнала вычитают общий аналоговый сигнал обратной ,связи, этот разностный сигнал усиливают и преобразуют, как в первом такте, в сигналы двоичного кода, которые также запоминают, 1 .Однако мя преобра; зования на деляетсямаксимально-возможным, :диа пазоном изменения усиленного сигнала разности межцу преобразуемым сигналом и сигна.- лом обратной связи, что приводит к уве.- личению среднего времени преобразования.Целью изобретения является повышение быстродействия аналого-цифрового преобразования.Достигается это тем, что в способе параллельно-последовательного преобразования, заключающемся в том, что в первом такте входной аналоговый сигнал преобразуют путем сравнения с основными эталонными сигналами в сигналы цвоичного кода, которые запоминают, а во втором и последующих тактах этого кода преобразуют в аналоговые сигналы обратной связи, которые затем масштабируют суммируют, после чего из вхоцного аналогового сигнала вычитают общий аналоговый сигнал обратной связи, этот раз 1- костный сигнал усиливают и преобразуют как в первом такте, в сигналы двоичного81995 15 55 кода, которые также запоминают, в начале второго и последующих тактов, изменяют весовые коэффициенты масштабирования аналоговых сигналов обратной связи, одновременно аналоговые сигналыобратной связи суммируют со вторымвспомогательным эталонным сигналом иизменяют на величину этого суммарногосигнала все основные эталонные сигналы,общий аналоговый сигнал обратной связиобразуют путем суммирования сигналовобратной связи с первым вспомогательным эталонным сигналом, причем в начале третьего и последующих тактов изменяют вспомогательные эталонные сигналы,В этом способе параллельно-последовательного аналого цифрового преобразования за счет введения операций изменения весовых коэффициентов масштабиро 20 вания аналоговых сигналов обратной связи и добавления вспомогательного сигнала, который суммируют с входным сигна- лом, причем одновременно смещают шкалы эталонных сигналов, уровень выходно 25 го сигнала после усиления раэностного сигнала остается неизменным, если значение последнего пропорционально половине кванта шкалы данного такта нреобразования, Для остальных значений разностэо ного сигнала уровень усиленного сигнала может изменяться в пределах только половины возможного диапазона изменения. Таким образом, изменение усиленного сигнала при переходе к очередному такту преобразования в два раза меньше анало гичного изменения усиленного сигнала в указанном известном способе.При реализации этого способа такое , техническое рещение приводит к пропорци 4 о ональному уменьшению времени выполнения в каждом такте аналого-цифрового преобразования, т. е. к повышению его быстродействия, причем последнее достигается без изменения коэффициентов уси45 ления аналоговых сигналов и без повышения точности выполнения операции сравнения аналоговых сигналов с эталонными.На фиг. 1 дана блок-схема трехтактного аналого-цифрового преобразователя; на фиг. 2 - временная диаграмма его работы.Блок-схема содержит аналоговый вы читатель 1, усилитель 2 с управляемым коэффициентом усиления, преобразователь считывания 3, блок эталонных сигналов 4, секционный регистр-счетчик 5, первый и второй цифроаналоговые преобразователи (ЮП) 6 и 7, блок управления 8,34блок. 9 формирования вспомогательных эталонных сигналов, первый и второй блоки масштабирования 10 и 11, первый и второй аналоговые сумматоры 12 и 13, шину аналогового входа 14, интерфейсные входы-выходы 15 блока управления 8.На фиг. 2 приняты следующие обозначения: 16 - импульс исходного состояния, формируемый на одном иэ выходов блока управления, по которому начинает" ся преобразование; 17 и 18 - сигналы на выходах первого и второго ЦАП 6 и 7; 18 - сигнал на выходе усилителя 2;20 и 21 - начальный и конечный уровни выходного сигнала усилителя 2 на первом такте преобразования; 22 и 23- конкретный и максимально-возможный интервалы времени, в течение которых происходит изменение сигнала на выходе усилителя 2; 24 - выходные импульсы блока 8, по которым выполняется считывание кода с выхода преобразователя 3 в регистр-счетчик 5; 25 и 26- максимально-возможные интервалы времени, в течение которых могут происходить изменения выходного сигнала уси лителя во втором и третьем тактах преобразования; 27 - импульсы на интерфейсном выходе 15 блока 8, по которым разрешается, передача кода результата преобразования Аналого-цифровое преобразование в этом преобразователе выполняется следующим образом. Сначала блок управления 8 вырабатывает импульс исходного состояния 16, которым гасятся счетчик б и блок формирования вспомогательных эталонных сигналов 9, а в усилителе 2 устанавливается наименьший коэффициент усиления К,( д 1. Так как выходные сиг-. налы ЦАП 6 и 7 в этот момент равны нулю и отсутствует сигнал на выходе блока 9, то входной, сигнал усилителя 2, поступающий с выхода аналогового вычйтателя 1, равен входному аналоговому сигналу, подаваемому на первый вход вычитателя 1 по входной аналоговой шине 14. В результате этого на выходе усилителя 2 выходной сигнал начинает изменяться от предыдущего значения (уровень 20) и устанавливается через интервал времени 22 на уровне 21, который соответствует входному аналоговому сигналу.Выходной сигнал усилителя 2 подается на вход преобразователя считывания 3, в котором преобразуется в сигналы парад. - /лельного двоичного кода. После истечения интервала времени 23 с момента появления сигнала 16, по сигналу 24, поступаюшему из блока 8, производитсясчитывание этого двоичного кода и записьего в старшие разряды регистра-счетчика 5.Если значение кода, считанного с выкодов преобразователя 3, отличается отнулевого, то начинает изменяться выходной сигнал 17 первого ЦАП 6, которыйчерез некоторый момент времени устанавливается на уровне, соответствующем сточностью данного такта преобразования,входному аналоговому сигналу,Одновременно со считыванием К-разрядного кода в регистр-счетчик 5 блок 8начинает подготавливать второй такт преобразования. При этом в усилителе 2 ус.танавливается коэффициент усиления в2 раэ больший, чем в первом такте,открываются входы для считывания кодас выходов преобразователя 3 в средниеразряды регистра-счетчика 5, коэффициентмасштабирования в блоке 10 устанавливается равным (1 - 1/2" ), а в блоке 9устанавливаются следующие значениявспомогательных сигналов: первого (длясмещения выходного сигнала усилителя 2)О =ад (-г") 1 2ивторого (для смешения шкалы блока 4):А-;к 2где д А = Ас/2" - квант вкодногоаналогового сиг"нала,А - диапазон изменения входного аналогового сигналаНачинает изменяться сигнал на выходе преобразователя 6, а за ним начинает из меняться и сигнал на выходе усилителя 2,- При указанных выше значениях коэффици ента масштабирования и первого дополнительного эталонного сигнала максимально-возможное изменение сигнала на выходе усилителя 2 сокращается вдвое по сравнению с изменением аналогичного сигнала в преобразователе, выполненном на основе известного способа и содержа" шем аналоговый вычитатель, соединенный выходом через усилитель с управляемым коэффициентом усиления и преобразователь считывания с входами регистра, выходы которого через цифроаналоговый пре30 35 40 45 50 повышается быстродействие преобразователя.Через интервал времени 25, определяемый временем установления сигнала на выходе усилителя 2 при переходе к вто,рому такту при его максимально возможном изменении на Аф /2, производится считывание кода с выходов преобразова 5 1 О 15 20 25образователь соединены с первым входоманалогового вычитателя, второй вход которого соединен с шиной аналогового входа, причем выходы блока управления соединены с управляюшими входами упомянутого усилителя и регистра,Действительно, предположим, что вкод-ной сигнал имеет значение ЬА(81+1/2),где К,1 ко, полученный в первом тактепреобразования. Выходной сигнал блока о10 Ацап.1 с учетом масштадированиябудет равен Д А И.1 (1 - 1/2 ). Тогдакдля установившегося значения Ау (1,П) сигнала на выкоде усилителя 2 припереходе от первого к второму тактупреобразования и наличии сигнала обратной связи АС - А п 2 - И можно написать следующее выражение:А(1)-(А -А )2"фАЙФ Я 1)ДАЙ(-2 К)щЬАИ2: (нТаким образом, при указанных значениях входного аналогового сигнала и общего сигнала обратнвй связи изменениясигнала на выходе усилителя 2 не происходит.В том случае, когда входной аналоговый сигнал отличается от значения А А"(й,1+1/2), т. е, находится в пределах от М,1 йА до ( И,( +1/2 ) ЬА или от(Й,1+1/2) дА до (й, +1) ЬА, то изменение выходного сигнала при переходе отпервого к второму такту не будет превышать Ау /2.При входном сигнале М,1 дА или(Й 1,+1) ф ЬА будет наибольшее изменениевыходного сигнала усилителя 2. Это изменение для Абхаз( Й 1+1)Ь,А будет равноЬ А(Т,П)макс= А(1,П)макс-(й+1)аА"АА.2. : 2 Фк.-.ьА= -Ай - ьА2т е, практически в два раза меньше, чем в указанном преобразователе, осноФванном на известном способе. Уменьше 1- ние диапазона изменения выходного сигнала приводит к эквивалентному уменьше-нию максимально-возможного времени установления сигнала на выходе усилителя такту преобразования, следовательно7 81995теля 3 в средние % разрядов регистраСледует заметить, что этот интервалвремени несколько больше аналогичногоинтервала 23 первого такта, так как5при изменении коэффициента усиленияусилителя 2 в 2" раэ изменяется такжеи скорость изменения сигнала на выходе усилителя. Объясняется это тем, чтореальные усилители эквиваленты РС-эве Ону, в котором одновременно с увеличением коэффициента усиления увеличивается значение сопротивления Р , что приводит к увеличению постоянной временитакого звена. 15При подготовке третьего такте преобразования блок 8 устанавливает коэффи 2 Кциент усиления усилителя 2 равным 2а также формирует сигналы, управляющиеизменением коэффициента масштабирова ния в блоках 10 и 1 1 и изменением виходных сигналов блока 9,Для.сохранения изменения выходногосигнала усилителя 2, не превышающеговеличины А /2, также и при переходе 5к третьему такту, значение первого вспомогательного эталонного сигнала устанав.ливается равным 1/2 (1 1/2 к )ьА,коэффициенты масштабирования в блоках10 и 11 устанавливаются равными соот-ветственно (1 - 1/2 ) и (1 1/2 К),в значении второго вспомогательного эталонного сигнала устанавливается равным, дА " +1)В случае, если входной сигнал имеетзначение В этих выражениях ЬА - квант напервом такте преобразования; й - значение кодов преобразования на каждом-м такте; 1 = 1, 2, ( 4 - 1);К - число параллельно получаемым разрядов кода в каждом такте преобразования,Таким образом, в и -тактном параллельно-последовательном преобразователе,выполненном на основе рассмотренногоспособа, в котором обеспечивается формирование сигналов Аос и Асм в соответствии с вышепривеценными формулами,достигается уменьшение максимально-возможного изменения выходного сигналаусилителя 2 на каждом такте преобразования в два раза по сравнению с вышеуказанным преобразователем, основаннымна известном способе преобразования.Это эквивалентно почти такому же сокрашению времени выполнения каждого тактапреобразования, т е. практически двухкратному повышению быстродействия преобразования.При этом реализация вновь введенныхопераций не требует использования болеебыстродействуюших элементов и узлов,чем те, на которых выполняется указанный известный преобразователь.формула изобретенияСпособ параллельно-последовательного аналого-цифрового преобразованиязаключающийся в том, что в первом так. ВА Ам (йд+ )к 3,где Й - код, полученный во втором такте преобразования,то выходной сигнал. усилителя 2 при переходе к третьему такту не будет.изменяться, аналогично тому, как это имеет место при переходе ко второму такту при значении входного сигнала, равногоЬ А(4+1/2) .Через интервал времени 26, равный максимальному времени установления сигнала на выходе усилителя 2, которое определяется новым значением постоянной времени, изменившейся (увеличившейся) с с изменением коэффициента усиления при переходе от второго к третьему такту преобразования, выполняется запись кода с выхоцов преобразователя 3 в младшие К - разряды регистра 5. На этом процесс трехтактового аналого-цифрового преобразования заканчивается, и код реЭО Э 5 40 45 59 Я 3зультата преобразования с выходов р- гистра 5 может быть передан в микропроцессор по соответствующему сигналу готовности результата преобразования, перецаваемого иэ блока 8 по одному из выходов 15.В общем случае цля И;-тактового преобразования по предложенному способу справедливо следующее выражение для сигнала обратной связи Аос -го преобразования , тф =ДА 1-1 фа(1-1)к-)кЗдесь коэффициенты при И определяют значение масштабирующих коэффициентов блоков масштабирования, а послецний член выражения - значение сигнала смещения на каждом такте преобразования,Сигнал смещения эталонных уровней сравнения Ас, , формируемый блоком 13, в рассмотренном преобразователе определяется следующим выражением:те входной аналоговый сигнал преобразуют путем сравнения с основными эталонными сигналами в сигналы двоичногокода, которые запоминают, а во второми последующих тактах сигналы этогокода преобразуют в аналоговые сигналыобратной связи, которые затем масштабируют и:суммируют, после чего из входного аналогового сигнала вычитают общий аналоговый сигнал обратной связи,этот разностный сигнал усиливают ипреобразуют, как в первом такте., в сигналы двоичного кода, которые такжезапоминают, о т л и ч а ю щ и й с ятем, что, с целью повышения быстродействия аналого-цифрового преобразования,в начале второго и последующих тактовизменяют весовые коэффициенты масшта 0053 10бирования аналоговых сигналов обратнойсвязи, одновременно аналоговые сигналыобратной связи суммируют со вторымвспомогательным эталонным сигналом иЗ изменяют на величину этого суммарногосигнала все основные эталонные сигналы,общий аналоговый сигнал обратной связи,образуют путем суммирования сигналовобратной связи с первым вспомогательнымО эталонным сигналом, причем, в началетретьего и последующих тактов изменяютвспомогательные эталонные сигналы.Источники информации,принятые во внимание при экспертизе15 1. Петров Г. М. Преобразование инфор-мации в аналого-цифровых вычислительныхустройствах и системах, М.; Машино-строение, 1973, с. 247 (прототип).М 9953 г 7 Составитыь. Л. БеляеваЧехред Н.Бабурка Корректор Л. ИванГон 61/35 Тираж 988ВНИИПИ Государственного компо делам изобретений и сква, Ж 35, Раушская н Подписноетета СССткрытийд. 4/5 аз 035, Мо филиал ППП Патент", г. Ужгород, ул. Проектная

СмотретьЗаявка

2761246, 04.05.1979

ПРЕДПРИЯТИЕ ПЯ Г-4128

ВОИТЕЛЕВ АЛЕКСАНДР ИЛЬИЧ, ЛУКЬЯНОВ ЛЕВ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03K 13/03

Метки: параллельно-последовательногоаналого-цифрового, преобразования

Опубликовано: 07.04.1981

Код ссылки

<a href="https://patents.su/6-819953-sposob-parallelno-posledovatelnogoanalogo-cifrovogo-preobrazovaniya.html" target="_blank" rel="follow" title="База патентов СССР">Способ параллельно-последовательногоаналого-цифрового преобразования</a>

Предыдущий патент: Параллельно-последовательныйаналого-цифровой преобразователь

Следующий патент: Способ параллельно-последовательногопреобразования напряжения b код

Случайный патент: Способ балансировки роторов