Цифровой демодулятор сигналов фазоразностной модуляции второго порядка

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1716616

Авторы: Горляковский, Крутов, Тримайлов

Текст

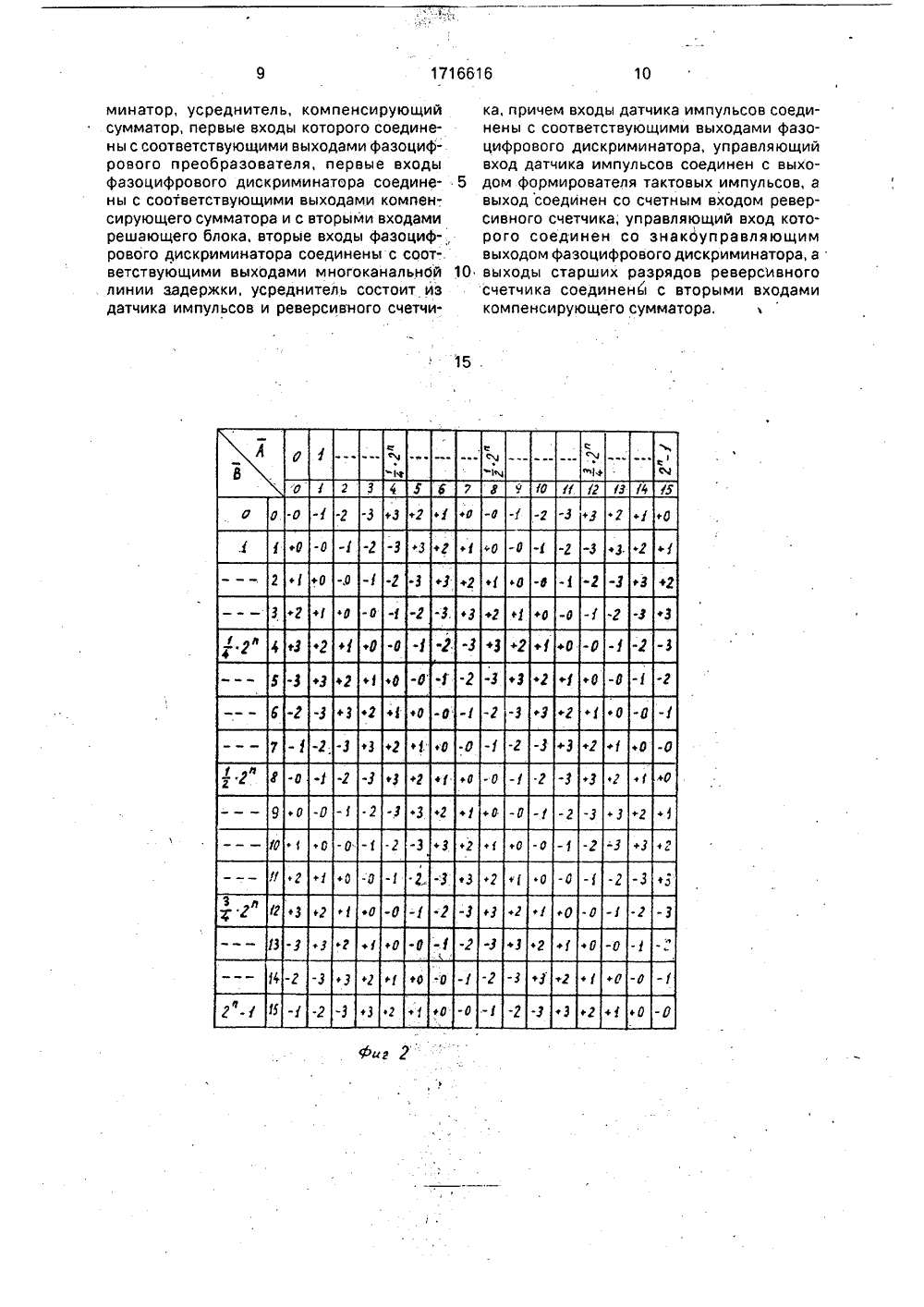

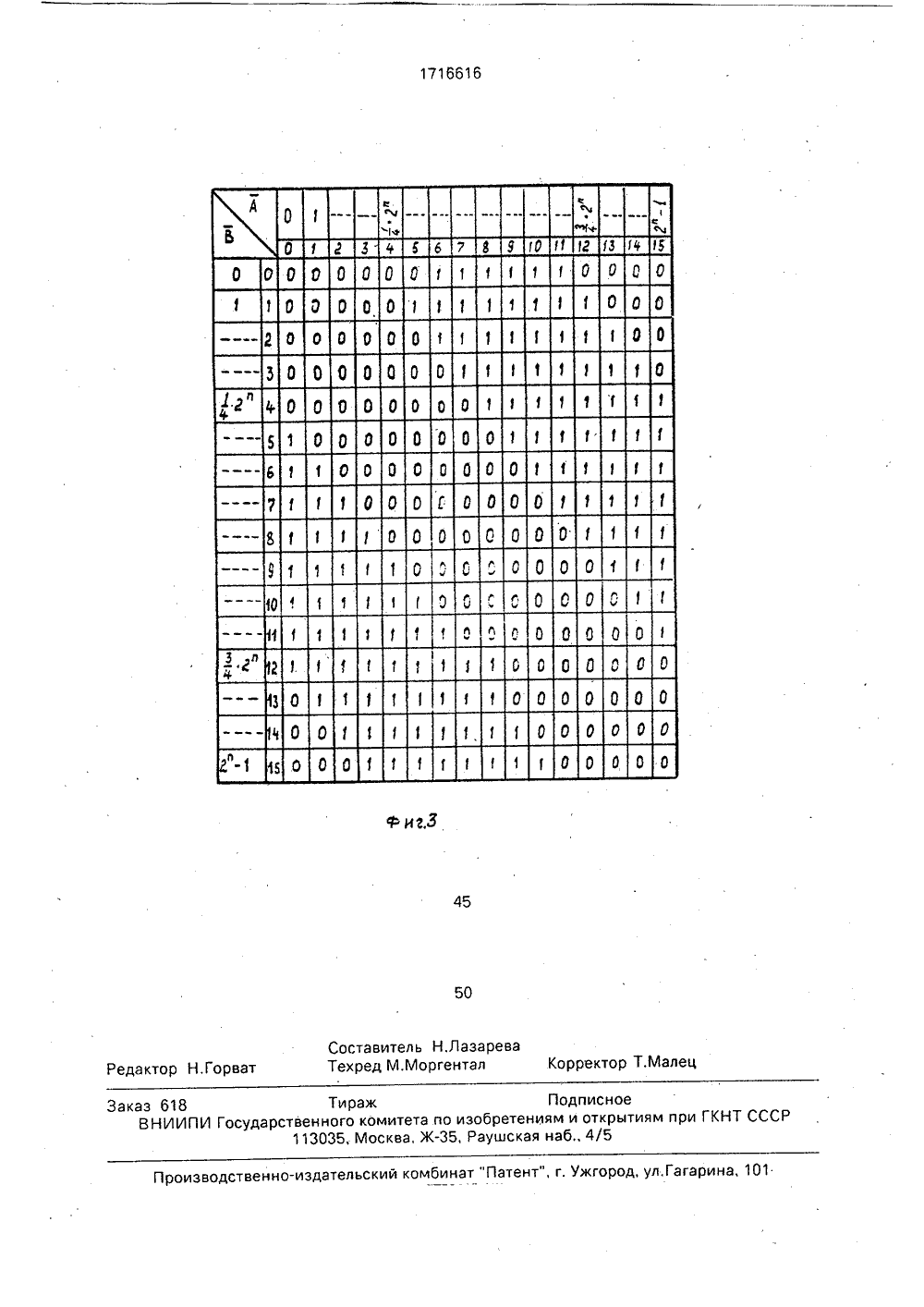

(19 51)5 Н 04 1 27/ ИЗОБРЕТЕНИЯТЕЛ ЬСТВУ ПИСАНИ ВТОРСКОМУ СВ й инс 88.ИГНАЯЦИИ . ехнике.омехоты сигГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССРМ 1570021, кл. Н 04 1 27/22, 07,00,19(54) ЦИФРОВОЙ ДЕМОДУЛЯТОР СЛОВ ФАЗОРАЗНОСТНОЙ МОДУЛВТОРОГО ПОРЯДКА(57) Изобретение относится к радиотЦель изобретения - повышение иустойчивости при отклонении часто нала от номинального значения. Цифровой демодулятор содержит ограничитель-формирователь 1, генератор 2, фазоцифровой преобразователь 3, формирователь 4 тактовых импульсов, компенсирующий сумматор 5, многоканальную линию 6 задержки, фазоцифровой дискриминатор 7, решающий блок 8, усреднитель 9, состоящий из датчика 10 импульсов и реверсивного счетчика 11, фильтр 12 нижних частот и блок 13 вычисления второй разности фаз. Цель достигается за счет осуществления автоматической компенсации паразитного фазового сдвига с помощью кольца фазовой автоподстройки, содержащего сумматор 5, дискриминатор 7 и усреднитель 9. 3 ил,360и 092-у - ,Изобретение относится к радиотехнике Максимальному значению двоичногои может использоваться в выходныхходныхустрой- числа, равному 2", соответствует максиствах для демодуляции сигналов. мальное значение фазы сигнала, равное 2 лЦель изобретения - повышение поме- (3600). Следовательно, точность Ьо измехоустойчивости при отклоненионении частоты 5 нения мгновенного значения фазы сигналасигнала от номинального значения, равнаНа фиг. 1 изображена структурная электрическая сХема предложенного цифровогодемодулятора; на фиг, 2 и 3 - таблицы, по"ясняющие работу цифрового дискриминатора и компенсирующего сумматора, Количество и разрядов двоичного числа, выбранное из. условия необходимойраничитель-формирователь 1, генератор 2, гнфазоцифровой преобразователь 3, форми- значения фазы сигнала, Определяется сорователь 4 тактовых импульсов, компенсирующий сумматор 5, многоканальнуюлинию задержки 6, фазоцифровой дискриминатор 7, решающий блок 8, усреднитель9, состоящий из датчика 10 импульсов иреверсивного счетчика 11, фильтР 12 ниж 20 где дп - необходимая точность измеренияних частот, блок 13 вычисления второи Раз новенного значения фазы сигнала, выраности фаз.л женная в градусах.Цифровой демодулятор работает следуЧастота 1 о генератора 2 определяетсяющим Образом,из соотношенияВходной синусоидальный сигнал с фазоразностной модуляцией второго порядка 10 = 2" ясном,(ФРМ) поступает на вход ограничителягде ю - номинальная частота сигнала,НИЧЕние и формированиЕ импульСнОйпоследовательности. Во время положителожительВыбор тактовой частоты т определяетных полупериодов сигнала амплитуда им- опустимыми телеграфными искаженипульсов становится равнои логичес ями, которь 1 е вносит демодулятор, иединице, а во вРемя Отрицательных - ло- вел ичиной номинальной частоты 1 сигнагическому нулю. С выхода ограничителялаформирователя 1 ограниченный и 35сформированный сигнал поступает на один1001 уснОнвход фазоцифрового преобразователя 3, на Едругой вход этого же фазоцифрового преобразователя 3 поступают импульсы с генератора 2 с частотой 10, а на управляющий 40вход поступают тактовые импульсы с форь ов. На вымирователя 4 тактовых импульсов.При номинальной частоте сигнала и отходах фазоцифрового преобразователя утствии фазовой манипуляции мгновенноемомент действия переднего фроа каж значение текущей фазы сигнала на выходедого тактового импульса Устаналиваетс фаз цифрового преобразователя принимаопределенное двоичное число, численно лучайную величину, которая не изменяравное количеству периодов частотьется отодноготакта кдругому.поступивших на фазоцифровой преоора Текущее мгновенное значение фазызователь 3 в течение интервала времени игнала поступает на входы многоканальначавшегося в момент устан ной линии 6 задержки, в каждом из каналовновления за сигиднего фронта предыдущего тактового им котороЙ осуществляется задержка соответпульса и закончившегос в моме вующего разряда двоичного числа на веустановления ближайшего переднего лич у, равную длительности Т однойфронта импульса сигнала элементарной посылки.Это двоичное число на выходе фазоциф При номинальной частоте 1 н 0 м сигналарового преобразователя 3 буде пропорци и аенстве фаз колебаний сравниваемыхонально текущему мгновенному значению (соседних) посылок паразитный фазовыйфазы ограниченного и сформированного виг ду, равный разности мгновенныхсигнала, измеренному в моме деиствия значений текущих и задержанных фаз сигтактового импульса.нала, равен нулю, а мгновенные значения этих фаз одинаковы и неизменны. Если отклонение Ьчастоты сигнала от номинального значения отличается от нуля, то 5 10 мгновенные значение текущих и задержанных фаз сигнала начнут медленно изменяться с частотой повторения, равной Ь Ю, а паразитныйфазовый сдвиг Ьд) будетоставаться неизменным и определяться соотно- шением Ьр =2 к Ь Т,где Л 1 - отклонение частоты сигнала от номинального значения, Гц;Т - длительность элементарной посылки.Наличие паразитного фазового сдвига Л р между текущими и задержанными значениями фаз сигнала приводит к значитель 15 20 ному ухудшению помехоустойчивости автокорреля цион ного демодулятора,Поэтому с целью повышения помехоустойчивости цифрового демодулятора сиг-налов фазоразностной модуляции второго 25 порядка в нем осуществляется автоматическая компенсации паразитного фазового Текущее значение фазы сигнала с выхода фазоцифрового преобразователя 3 поступает на первые входы компенсирующего 40 сумматора 5, На вторые входы этого же сумматора 5 поступает корректирующий код, вы рабаты ваем ый посл едовател ьно включенными фазоцифровым дискриминатором 7 и усреднителем 9. При сложении двоично го числа, соответствующего текущему значению фазы сигнала и двоичного числа, соответствующего корректирующему коду, текущее значение фазы сигнала получаеттакое приращение фазы, при котором про исходит компенсация паразитного фазово-" го сдвига Ьр.Скорректированное значение А текущей фазы сигнала с выходов компенсирующего сумматора 5 поступает на одни входы 55 фазоцифрового дискриминатора 7 и решающего блока 8, на другие входы фазоцифрового дискриминатора 7 и решающего блока 8 подается задержанное значение В фазы сдвига АО,с помощью кольца фазовой автоподстройки, содержащего компенсирующий сумматор 5, фазоцифровой ЗО дискриминатор 7 и усреднитель 9, состоящий из последовательно соединенных датчика 10 импульсов и реверсивного счетчика 11,Кольцо фазовой автоподстройки рабо- З 5 тает следующим образом. сигнала с выходов многоканальной линии 6 задержки.Фазоцифровой дискриминатор 7 представляет собой устройство, в котором каждой паре двоичных п-разрядных чисел А и В, поступающих на его входы, соответствует определенное (и)-разрядное двоичное число Е на его выходе. Это число Е остается неизменным в течение промежутка времени, равного периоду тактовой частоты Ет, и может изменяться только в момент действия тактовых импульсов. Старший(и) разряд этого числа 2 является знакоуправляющим разрядом, показывающим необходимость увеличения или уменьшения корректирующего кода. Остальные разряды (01, 020 СЬ-г) определяют величину фазового рассогласования Ь 2 в виде (и)- разрядного двоичного числа. Схемная реализация фазоцифрового дискриминатора 7 может быть представлена в виде программируемого запоминающего устройства или в виде комбинационной схемы,Принцип работы фазоцифрового дискриминатора 7 можно пояснить с помощью таблицы 1, расположенной на фиг. 2, где показано состояние выходов фазоцифрового дискриминатора 7 в зависимости от величины четырехразрядных (и= 4) двоичных чисел А и В. Состояние старшего (и) разряда обозначено знаками "+" или "-", причем знаку "+" соответствует состояние "0", а знаку "-" "1". Величина фазового рассогласования Ьт представлена в десятичном коде.Выход фазоцифрового дискриминатора 7 соединен с входом усреднителя 9, состоящего из датчика 10 импульсов и реверсивного счетчика 11, Датчик 10 импульсов в момент прихода каждого тактового импульса формирует импульсную последовательность (" пачку" ), состоящую из импульсов, количество которых численно равно величине фазового рассогласования ЬЕ. При этом частота повторения импульсов должна быть такой, чтобы максимальное количество импульсов в "пачке", равное (2" -1) могло сформироваться и поступить на счетный вход реверсивного счетчика 11 в течение промежутка времени, равного длительности одного периода частоты Г тактовых импульсов.С выхода знакоуправляющего (и) разряда фазоцифрового дискриминатора 7 на управляющий вход реверсивного счетчика 11 поступает сигнал ("0" или "1"), определяющий направление счета в реверсивном счетчике 11. При сигнале "0", который соответствует знаку "+", записанное в реверсивном счетчике 11 число будет складываться с числом импульсов, поступивших на его счетный вход, а при "1", соответствующей знаку "-", из числа, записанного в реверсивном счетчике 11, будет вычитаться число импульсов, поступивших на счетный вход реверсивного счетчика 11. Следовательно, число, записанное в реверсивном счетчике 11, будет увеличиваться или уменьшаться в зависимости от того, требуется ли увеличение или уменьшение корректирующего кода, чтобы скомпенсировать паразитный фазоВый СДВиг. Старшие разряды многоразрядного выхода реверсивного счетчика 11, на которых формируется корректирующий код, соединены соответственно со вторыми входами компенсирующего сумматора 5. Чем больше разрядов в реверсивном счетчике 11, тем большее двоичное число можно записать на его выходе, реже будут меняться потенциалы старших разрядов, а следовательно, большее усреднение можно получить при формировании корректирующего кода, но при этом кольцо фазовой автоподстройки будет более инерционным. Следовательно, количество разрядов реверсивного счетчика 11 определяется предельно допустимым временем вхождения в синхронизм кольца фазовой автоподстройки.При работе кольца фазовой автоподстройки на одних входах компенсирующего сумматора 5 автоматически устанавливается такой корректирующий код, при котором фазовый сдвиг Ьф между значениями фазы А и В стремится к 0 или 7 г. При достижении одной из этих двух точек устойчивого равновесия фазоцифровой дискриминатор 7 начнет выдавать нулевые значения фазового рассогласования Ь Е, а корректирующий код будет оставаться неизменным, следовательно, кольцо фазовой автоподстройки войдет в синхронизм.На одни входы решающего блока 8 поступает скорректированное значение А текущей фазы сигнала, на другие входы - задержанное значение В фазы этого же сигнала.Решающий блок 8 производит действия над двоичными и-разрядными числами А и В, в результате которых каждой паре двоичных чисел соответствует определенное состояние "0" или "1" выхода. решающего блока 8. Принципы работы решающего блока 8 можно пояснить с помощью таблицы 2, расположенной на фиг. 3, где показано со. стояние его выхода в зависимости от величин четырехразрядных двоичных чисел А иВ, поступающих на его входы.Схемная реализация решающего блока8 может быть представлена в виде програм-5 мируемого запоминающего устройства илив виде комбинационной схемы.Выход решающего блока 8 через фильтр12 нижних частот, обеспечивающий фильтрацию высокочастотнных составляющих,10 соединен со входом блока 13 вычисленияВторой разности фаз, которая устраняет неоднозначность решений в выходном предмодулированном сигнале и обеспечиваетформирование выходных импульсов,15 Применение кольца фазовой автоподстройки, содержащего компенсирующий сумматор 5, фазоцифровой дискриминатор 7 иусреднитель 9, состоящий из последовательно соединенных датчика 10 импульсов20 и реверсивного счетчика 11, обеспечивает.повышение помехоустойчивости цифровогодемодулятора сигналов фазоразностной модуляции второго порядка при отклонениичастоты сигнала от номинального значения25 и снижает требование к стабильности длительности задержки сигнала за счет автоматической компенсации паразитногофазового сдвига Лр, возникающего междутекущими и задержанными значениями фа 30 зы сигнала,Формула изобретения Цифровой демодулятор сигналов фазоразностной модуляции второго порядка, со держащий ограничитель-формирователь,генератор, формирователь тактовых импульсов, вход которого подключен к выходу генератора, фазоцифровой преобразователь, первый вход которого соединен с вы ходом ограничителя-формирователя,второй вход соединен с выходом генератора, а управляющий вход соединен с выходом формирователя тактовых импульсов,многоканальная линия задержки, входы ко торой соединены с соответствующими выходами фазоцифрового преобразователя, а управляющий вход соединен с выходом формирователя тактовых импульсов, решающий блок, первые входы которо го соединены с соответствующими выходами многоканальной линии задержки, блок вычисления второй разности фаз, вход которой соединен с выходом фильтра нижних частот, вход ко торого соединен с выходом решающегоблока, о т л и ч а ю щ и й с я тем, что, с целью повышения помехоустойчивости при отклонении частоты сигнала от номинального значения, введены фазоцифровой дискри1716616 10 15 минатор, усреднитель, компенсирующий сумматор, первые входы которого соединены с соответствующими выходами фазоцифрового преобразователя, первые входы фазоцифрового дискриминатора соедине ны с соответствующими выходами компенсирующего сумматора и с вторыми входами решающего блока, вторые входы фазоциф-, рового дискриминатора соединены с соответствующими выходами многоканальной 10 линии задержки, усреднитель состоит из датчика импульсов и реверсивного счетчика, причем входы датчика импульсов соединены с соответствующими выходами фазоцифрового дискриминатора, управляющий вход датчика импульсов соединен с выходом формирователя тактовых импульсов, а выход соединен со счетным входом реверсивного счетчика; управляющий вход которого соединен со знакОуправляющим выходом фазоцифрового дискриминатора, а . выходы старших разрядов реверсивного счетчика соединенй с вторыми входами компенсирующего сумматора,1716616 иг.З 4 0 Корректор Т.М едактор Н,Горват и ГКНТ СССР Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 каз 618 ВНИИПИ Г Составитель НЛазаревТехред М.Моргентал Тираж Подписноерственного комитета по изобретениям и открытиям 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4721830, 19.07.1989

ОМСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ПРИБОРОСТРОЕНИЯ

ТРИМАЙЛОВ АЛЕКСАНДР ЕВГЕНЬЕВИЧ, КРУТОВ МИХАИЛ ИВАНОВИЧ, ГОРЛЯКОВСКИЙ ВЛАДИМИР АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: второго, демодулятор, модуляции, порядка, сигналов, фазоразностной, цифровой

Опубликовано: 28.02.1992

Код ссылки

<a href="https://patents.su/6-1716616-cifrovojj-demodulyator-signalov-fazoraznostnojj-modulyacii-vtorogo-poryadka.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор сигналов фазоразностной модуляции второго порядка</a>

Предыдущий патент: Когерентный приемник частотно-манипулированных радиосигналов с непрерывной фазой

Следующий патент: Переговорно замочное устройство

Случайный патент: Способ очистки углеводородов с 4 с 7 от примесей циклопентадиена и кислородсодержащих соединений