Цифровой синтезатор сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

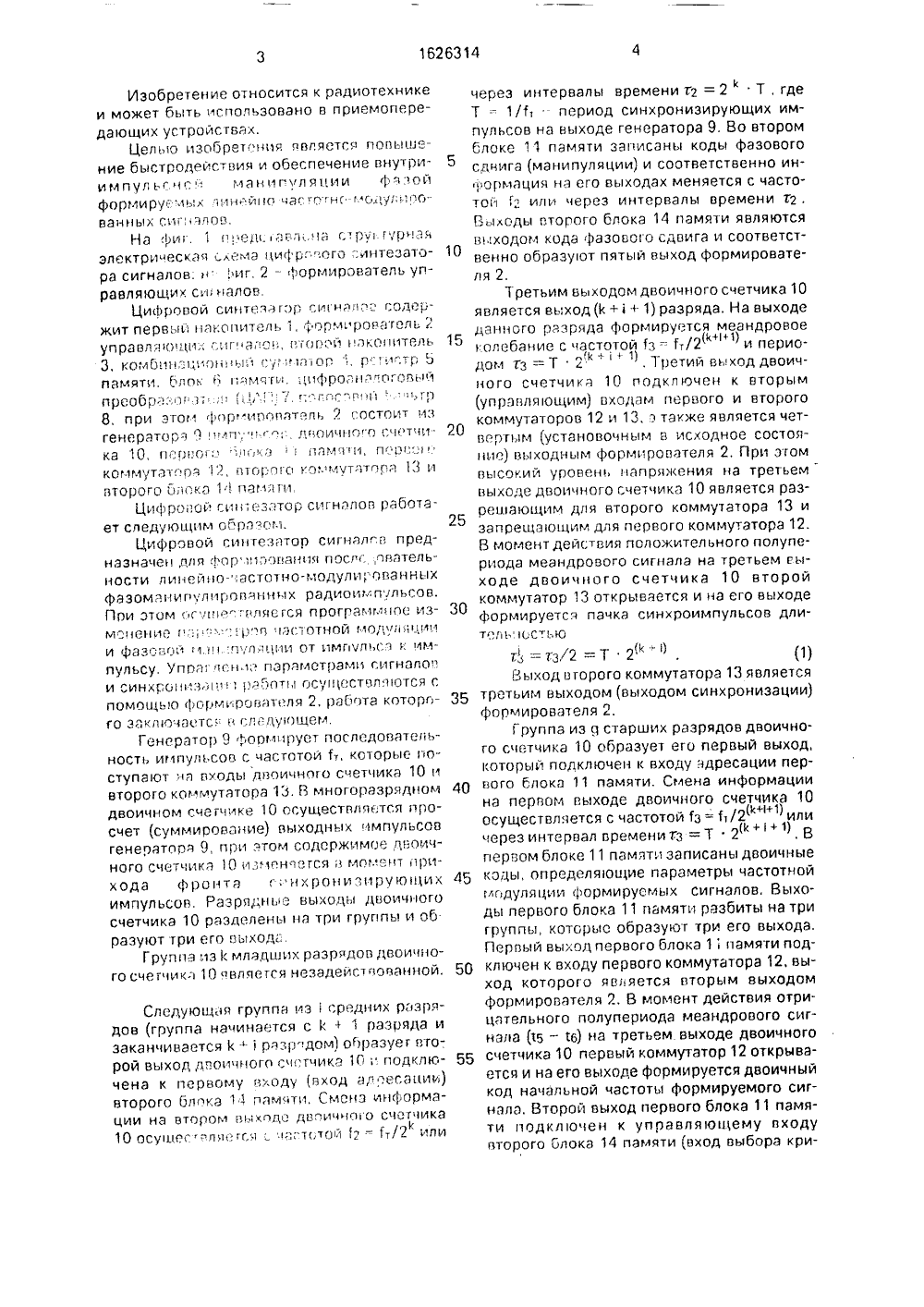

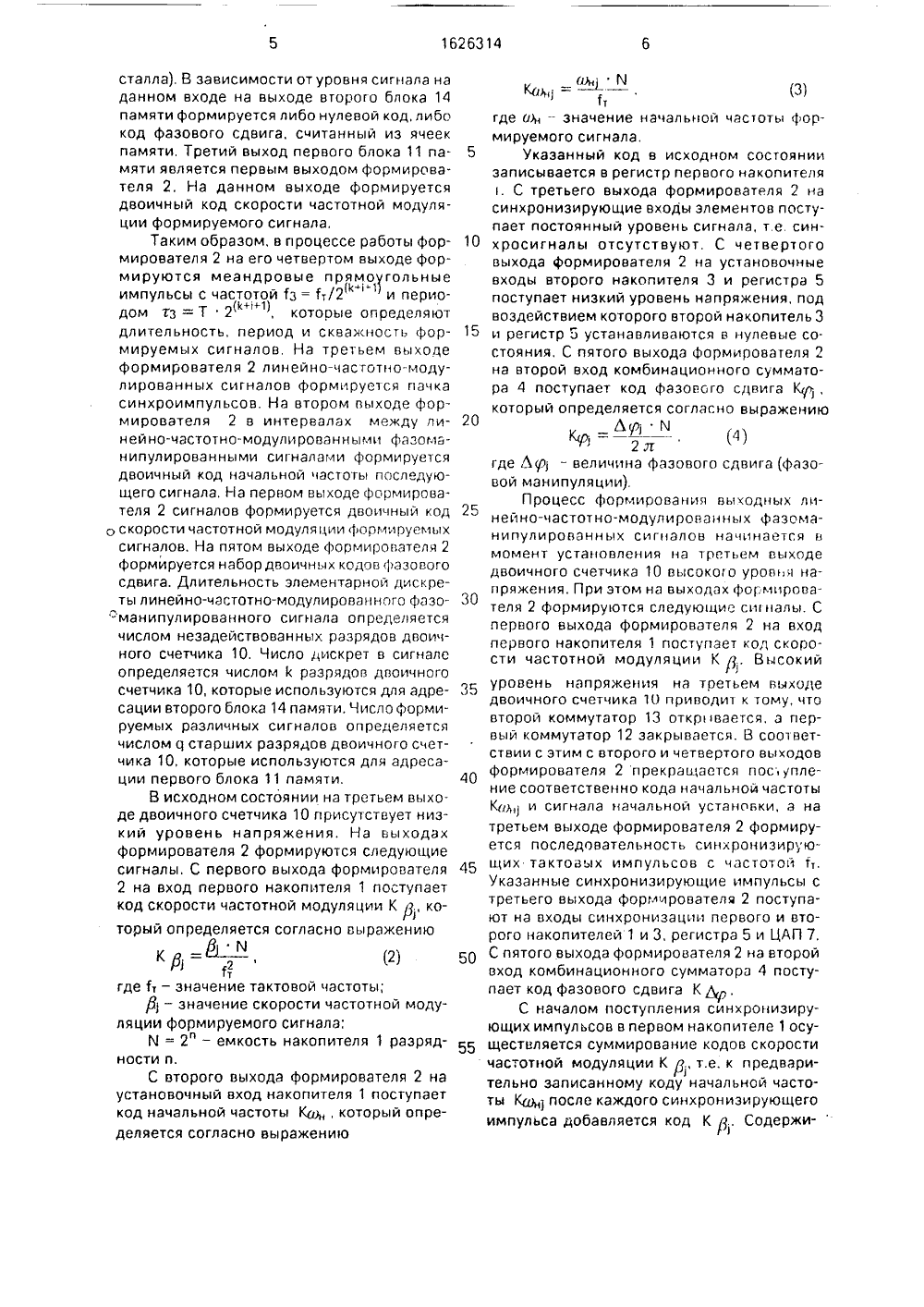

(5)5 Н 03 В 19/00 БРЕТЕНИ ся к радиотехнике. шение быстродейвнутриимпульсной мируемых линейноых сигналов. Цифналов содержит)ЬЭ) ОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАН И К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Кочемасов В,Н, и др, Формирование сигналов с линейной частотной модуляцией. - М,: Радио и связь, 1983, с. 55-58.Алешин В.Г. и др, Конспект лекций по курсу Радиопередгющие устройства, Синтезаторы частоты. - М.: Московский энергетический ин-т, 1978, с. 34 - 37.(54) ЦИФРОВОЙ СИНТЕЗАТОР СИГНА(57) Изобретение относиЦель изобретения - повыствия и обеспечениеманипуляции фазой форчастотно-модулированнровой синтезатор си первыи накопитель 1, формирователь э улравляющих сигналов, второй накопитель 3, комбинационный сумматор 4, регистр 5 па.мяти, блок 6 памяти, цифроаналооль й р . - образователь (ЦАП) 7, паласовой филь;р Я Формирователь 2 сос 1 оит из ге ерагора г 1.пульсов, двоичного с;етчйка, первого 61 о памяти, первого ко) мутатора, второго,ом мутатора и второго блока памяти. На выходе первого накопителя 1 фопмируются кПРИРаЩЕНИй фаЗЫ ФОРМИРУЕМЫХ СйгН:.ЛОВ за один такт работы устройства, Н,1 выходе второго накопителя 3 формир,ются кодь фазы синтезируемого сигнала в,г,;скре 1 н ые моменты времени. Результирующий код фазы фиксируется в регистре 5 и поступает на входы блока 6 памяти, где хранится тддли ьэ преобразования в функцию синуса, К. л,амплитудных выборок преобразуютс". л ЦАП 7 в аналоговую величину, 1 з,п ф-л 1., 2 ил,Изобретение относится к радиотехнике и может быть спользовано в приемопередающих устройствах,Целло изобретг.ния является повышение быстродействия и обеспечение внутриимпульгноманип)ляции азой фОРМИРУ 1 ЫХ И.-.йО часто гНС С,УЛРО- ванных сиг ллооНэ фиг, 1 е. Эол,.,л сто.Гургас ЭЛЕКТР ЕСКЭЯ СЕМЭ ИфРг ОГО СинтЕЗЭтО- ра сигналов., иг, 2 - формирователь управляющих с. паловЦиФрооой синтеза Гор сигнл 00 со;ержит первый лкопитель 1, фзрмрооатель 2 упраоляощи;НГ лло:, огоппй лксчитель 3, КОМб 1;.Г;10 Ь;.1 Су; ЛОГ 1, р: :г.рпамяти, блок 6 пят.14 рогКлсгоо 1 8, при зтол 1 фр"ИГгллтель 2 состоит из ГЕНЕратОра 9 .1 г.гоггГИгГггС Т 1- ка 10, пегоог; ,.Гг;, плми, пор КО 1 МутатоОЛ ,), ЛТОргГС 0.1 утатгрЛ 13 И второГО блока 14 па 1;тиЦифровой Ги",езлтор сигналов работает следующим обрэзсЦифровой си Гезлтор сигнллпо преднэзначе для г).ор" Оогэн 1 л после Ооательности линейно-;астотно-модули; ооаннцх фэзомлнип л 1 с 0 олннцх рэдиоил 1 пГльГоо. ПОИ Зтам ГГП.-ГляСГСя ПООГраМГОЕ ИЗ- моение г". : " рв астотной мод)7 яц 1 и и фазооой 1,:и,глии От 1 мгулэсл к им. пульсу, апов сн,1 пэрлметрал 1 И сигнало . и синхро ;за;работОсу 1 Г стеллотся Г ПОМОцЬО фОрмроватЛя 2, рабгта КотОрг- го заключэетсв о слегуощем,Генератор 9 гоол 1 рует последооатеьность импульсоо с частотои Ьт, которые поступают нл входы двоичного счетчика 10 и второго коллмутлтора 13, В многоразрядном двоичном счетчике 10 осуществляется просчет (суммирооаие) выходных импульсов генератпрл 9, при этом содержимое двоич- НОГО сг"тчикл 10 из 1 енетсямпент 13 ИХОДа фРОНТЭ Г: НХРОНИЗИРУОЩИХ ИМПУЛЬСОВ, РЭЗРЯНЬ 8 ВЫХОДЫ ДООИЧНОГО счетчика 10 разделенц на три группы и об разуют три его выход,".Группа из ); младших разрядоо двоичного сче Гчик: 10 является незадействованной. Следующая группа из 1 средних разрядов (группа наинается с Е + 1 разряда и заканчивается )с 1 рлзр дом) огразует второй выход дооичногп счетчика 10 г, подключена к первому ходу (вход ар;есации) второго блг ка 11 плмт 1, Сменэ информации нэ отогол 1 выходе допично 0 счепикэ 10 Осувес гл.Гслгтто 1 = 1 т/2 иличерез интервалы времени т 2 =2 Т, где блоке 11 памяти записаны коды фазового сдвига манипуляции) и соответственно ин- ОГмлция на его выходах меняется с частотой )или через интервалы времени т 2, В коды ОтОрОГО бЛОКЭ 14 ПЭМятИ яВЛяЮтСя выходом кода фазового сдвига и соответственно образуот пятый выход формирователя 2.Третьим вьходом двоичного счетчика 10 является вь;ход ++ 1) разряда, На выходе 5 10 15 20 25 30 35 40 45 50 55 данного разряда формируется меандровое :олебание с частоой 1 з =- И 2 + ) и периодом тз = Т, Третий вьход двоичгк 1)НОГО счетчикл 10 подключен к вторы (управляощим) входам первого и второго коммутаторов 12 и 13, з также является четвертьм (установочным о исходное состояГие) выходным формирователя 2, При этом высокий уровень лпряжения на третьем выходе двоичного счетчика 10 является разрешающим для второго коммутатора 13 и запрещающим для первого коммутатора 12.В момент действия положительного полупериода меэндрооого сигнала на третьем выходе двоичного счетчика 10 второй комл 1 утатор 13 открывается и на его выходе формируетсл пачка синхроимпульсов длител;ос. ьют. = 73/2 = Т2 (1) Выход второго коммутатора 13 является третьим выходом (выходом синхронизации) формирователя 2.Группа из 9 старших разрядов двоичного счетчика 10 образует его первый выход, который подключен к входу адресации первого блока 11 памяти, Смена информации на первом выходе двоичного счетчика 10 осуществляется с частотой з = 1,/2+) или через интервал времени тз = Т2 ), В первом блоке 11 памяти записаны двоичные коды, определяощие параметры частотной мгдуляции формируемых сигналов, Выходы первого блока 11 памяти разбиты на три группы, которые образуют три его выхода, Первый выход первого блока 1 1 памяти подключен к входу первого коммутатора 12, выход которого является вторым выходом формирователя 2, В момент действия отрицательного полупериода меандрового сигнала (ю 5 - тб) на третьем выходе двоичного счетчика 10 первый коммутатор 12 открывается и на его выходе формируется двоичный код начальной частоты формируемого сигнала, Второй выход первого блока 11 памяти подключен к управляющему входу оторого блока 14 памяти (вход оыбора криТ = 1/ттпериод синхронизирующих импульсов на выходе генератора 9, Во второмсталла). В зависимости от уровня сигнала наданном входе на выходе второго блока 14памяти формируется либо нулевой код, либокод фазового сдвига, считанный из ячеекпамяти, Третий выход первого блока 11 памяти является первым выходом формирователя 2. На данном выходе формируетсядвоичный код скорости частотной модуляции формируемого сигнала,Таким образом, в процессе работы формирователя 2 на его четвертом выходе формируются меандровые прямогольныеимпульсы с частотой 1 з = 1/2 и перио(И 1(11)дом тз = Т 2 , которые определяютдлительность, период и скважность формируемых сигналов, На третьем выходеформирователя 2 линейно-частотно-модулированных сигналов формируется пачкасинхроимпульсов. На втором выходе формирователя 2 в интервалах между линейно-частотно-модулированными фазоманипулированными сигналами формируетсядвоичный код начальной частоты последующего сигнала. На первом выходе формирователя 2 сигналов формируется двоичный кодо скорости частотной модуляции 1 ормируемыхсигналов. На пятом выходе формирователя 2формируется набор двоичных кодов фазовогосдвига. Длительность элементарной дискреты линейно-частотно-модулированного фазо-манипулированного сигнала определяетсячислом незадействованных разрядов двоичного счетчика 10, Число дискрет в сигналеопределяется числом ) разрядов двоичногосчетчика 10, которые используются для адресации второго блока 14 памяти. Число формируемых различных сигналов определяетсячислом ц старших разрядов двоичного счетчика 10, которые используются для адресации первого блока 11 памяти,В исходном состоянии на третьем выходе двоичного счетчика 10 присутствует низкий уровень напряжения. На выходахформирователя 2 формируются следующиесигналы, С первого выхода формирователя2 на вход первого накопителя 1 поступаеткод скорости частотной модуляции К и., который определяется согласно выражениюК д - , (2)где 1 т - значение тактовой частоты;Р) - значение скорости частотной модуляции формируемого сигнала;И = 2" - емкость накопителя 1 разрядности п.С второго выхода формирователя 2 наустановочный вход накопителя 1 поступаеткод начальной частоты Ксо, который определяется согласно выражению 5 10 15 20 25 30 35 40 45 50 55 Кдл) = - )- -иь М(3)Фтгде аЪ - значение начальной частоты формируемого сигнала,Укаэанный код в исходном состояниизаписывается в регистр первого накопителя. С третьего выхода формирователя 2 насинхронизирующие входы элементов поступает постоянный уровень сигнала, т е синхросигналы отсутствуют, С четвертоговыхода формирователя 2 на установочныевходы второго накопителя 3 и регистра 5поступает низкий уровень напряжения, подвоздействием которого второй накопитель 3и регистр 5 устанавливаются в нулевые состояния, С пятого выхода формирователя 2на второй вход комбинационного сумматора 4 поступает код фазового сдвига Кд,который определяется согласно выражениюКр = --Л р) (х)2 л(4)где Лр - величина фазового сдвига (фазовой манипуляции).Процесс формирования выходных линейно-частотно-модулированных фазоманипулированных сигналов начинаетгя вмомент установления на третьем выходедвоичного счетчика 10 высокоо уровня напряжения, При этом на выходах формирователя 2 формируются следующие си налы. Спервого выхода формирователя 2 на входпервого накопителя 1 поступает код скорости частотной модуляции К а. ВысокийЙуровень напряжения на третьем выходедвоичного счетчика 10 приводит к тому, чтовторой коммутатор 13 открзовется, а первый коммутатор 12 закрывается, В соо 1 ветствии с этим с второго и четвертого выходовформирователя 2 прекращается пос упление соответственно кода начальной частотыКгц,) и сигнала начальной установки, а натретьем выходе формирователя 2 формируется последовательность синхронизирую ющих тактовых импульсов с частотойУказанные синхронизирующие импульсы стретьего выхода формирователя 2 поступают на входы синхронизации первого и второго накопителей 1 и 3, регистра 5 и ЦАП 7,С пятого выхода формирователя 2 на второйвход комбинационного сумматора 4 поступает код фазового сдвига Кд.С началом поступления синхронизирующих импульсов в первом накопителе 1 осуществляется суммирование кодов скоростичастотной модуляции К л., т.е. к предварительно записанному коду начальной частоты Ксд,) после каждого синхронизирующегоимпульса добавляется код К л., Содержи-(5) мое первого накопителя 1 для г-го тактаработы устройства определяется соотношением К К(р(г) =,;, (Ка;+, К р) + г=1 г =1где К; (г) - ыходной код первого накопителя 1 в за,)симости от такта работы устройства. Таким образом, на выходе первого накопителя 1 формируются коды приращеий фазы формируемых сигналов эа один такт работы устройства. Указанные коды поступают на вход второго накопителя 3, где осущесгг/)яется их суглмирование, На выходе второго накопителя 3 формируются коды фазы синтезируемого сигнала в дискретные моменты времени, численное значение которых определяется соотношением в В,в я- / еп 1- , (кодХ к /1. (Б)г - 1 г=1 При это(л второе слагаемое в правой части выражения (б) реализуется автоматически путем переполнения второго накопителя 3, емкость которого эквивалента 2 , Таким образом на выходе второго накопителя 3 формируется последовательность кодов фазы, численные значения которых изменяются в соответствии с законом полинома второй степени, что соответствует синтезу линейно-частотно-модулированного сигнала В комбинационном сумматоре 4 выходные коды второго накопителя 3 суммируются с кодом фазового сдвига КЬр, который поступает с пятого выхода формирователя 2, В течение длительности формируемого сигнала код фазового сдвига КЬр на пятом выходе формирователя 2 несколько раз изменяется. Количество манипуляций фазы и элементарных частей в формируемом сигнале определяется числом двоичных разрядов, которые используются для адресации второго блока 14 памяти в формирователе 2. Таким образом, на выходе комбинационного сумматора 4 формируется последовательность кодов фазы, которая соответствует закону изменения фазы сложного линейно-частотно-модулированного фазоманипулированного сигнала и описывается выражением 10 15 20 25 30 35 40 45 50 55 где 1 р (г) - кодообразующая последовательность.Результирующий код фазы К(р (г) формируемого сигнала фиксируется синхронизирующими импульсами в регистре 5, Сформированные коды фазы Кр(г) формируемого сигнала с выхода регистра 5 поступают на входы адресации блока б памяти, в котором записана таблица преобразования, соответствующая функции синуса. Таким образом в блоке б памяти осуществляется преобразование фаза-синус и на его выходе формируются коды амплитудных выборок синтезируамого линейно-частотно- модулированного фазоманипулированного сигнала. Указанные коды поступают на вход ЦАП 7, где преобразуются в соответствующую аналоговую вели ину, В результате этого на выходе ЦАП 7 формируется дискретный сигнал. Переход от дискретного к непрерывному сигналу осуществляется с помощью полосового фильтра 8, полоса пропускания которого согласована с полосой частот формируемого сигнала,Процесс формирования линейно-частотно-модулированного фазоманипулированного сигнала заканчивается в момент установления на третьем выходе двоичного счетчика 10 низкого уровня напряжения. При этом содержимое старших о разрядов двоичного счетчика 10 изменяется на единицу и соотве 1 ственно изменяется код адресации первого блока 11 памяти. Последнее приводит к тому, что на первом и втором выходах формирователя 2 формируются новые коды скорости частотной модуляции К л. и начальной частоты Кг) последующего формируемого сигнала. Далее процесс установки цифрового синтезатора сигналов в исходное состояние и формирования выходного сигнала аналогичен описанному. Можно формировать линейно-частотно-модулированные сигналы без внутриимпульсной фазовой манипуляции. Это достигается в том случае, если с второго выхода первого блока 11 памяти на управляющий вход второго блока 14 памяти поступает запрещающий сигнал, под действием которого в течение всей длительности линейно-частот 1626314 10но-модулированного сигнала на выходахвторого блока 11 памяти формируется нулевой код фазового сдвига,Использование "конвейерного" метода вычислений позволяет добиться максимального быстродействия устройства в целом. 45 Минимальный период импульсов синхронизации в данном случае определяется максимальным временем выполнения одной иэ необходимых операций. В предлагаемом устройстве наибольшее время необходимо 50 для выполнения операции суммирования в первом или втором накопителях 1 и 3, разрядность которых не менее двадцати двоичных разрядов, Поэтому минимальное значение периода синхронизирующих им пульсов предлагаемого устройства определяется соотношением(8) Т Ъ =т +тэ,Е Таким образом, цифровой синтезатор 5 сигналов обладает широкими функциональными воэможностями и позволяет осуществлять внутриимпульсную фазовую манипуляцию в формируемом сигнале, Кроме того, цифровой синтезатор сигналов об падает быстродействием, так как реализована минимальная по аппаратурным затратам структура вычислителя кодов фазы формируемого линейно-частотно-модулированного сигнала, В данном случае 15 вычислитель кодов фазы состоит из двух последовательно включенных первого и второго накопителей 1 и 3, синхронизация которых осуществляется одновременно от одного формирователя 2, т.е. при вычисле нии кодов фазы формируемого сигнала, преобразования кодов фазы в коды амплитуды и цифроаналоговым преобразовании используется "конвейерный" метод вычислений. Повышение быстродействия 25 устройства достигается путел соответствующего разделения необходимых вычислительных операций по различным тактам работы устройства, Например, если передним фронтом очередного синхронизирую щего импульса в регистр ЦАП 7 записывается код амплитуды для момента времени тг, то этим же синхроимпульсом в регистр 5 записывается код фазы сигнала для момента времени (тг+ Т), в регистр вто рого накопителя 3 записывается код фазы формируемою сигнала для момента времени (тг+ 2 Т), а в регистр первого накопителя 1 записывается код приращения фазы формируемого сигнала для момен га времени 40 (т, + ЗТ). где 1 сп - время выполнения операции сложения в накапливающем сумматоре(накопителе);1 - время сложения в комбинационном сумматоре;тз - время задержки в буферном регистре, входящем в состав первого или второго накопителя 1.3.Формула изобретения 1. Цифровой синтезатор сигналов, содержащий последовательно соединенные первый накопитель и второй накопитель, последовательно соединенные блок памяти, цифроаналоговый преобразователь и полосовой фильтр, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия и обеспечения внутриимпульсной манипуляции фазой формируемых линеино-частотно- модулированных сигналов, введен формирователь управляющих сигналов. а между выходом второго накопителя и входом блока памяти введены последовательно соединенные комбинационный сумматор и регистр памяти, первый и второй выходы формирователя управляющих сигналов подключены соответственно к первому и второму входам первого накопителя, вход синхронизации которого обьединен с входами синхронизации второго накопителя, регистра памяти и цифроаналогового преобразователя и подключен к третьему выходу формирователя управляющих сигналов, четвертый выход которого соединен с установочным входом второго накопителя и с установочным входом регистра памяти, а второй вход комбинационного сумматора подключен к пятому выходу формирователя управляющих сигналов.2, Синтезатор поп.1.отл ичающийс я тем, что формирователь управляющих сигналов содержит последовательно соединенные генератор импульсов, двоичный счетчик, первый блок памяти и первый коммутатор, второй коммутатор, первый вход которого подключен к выходу генератора импульсов, второй блок памяти, первый и второй входы которого соединены соответственно с вторым выходом двоичного счетчика и вторым выходом первого блока памяти, второй вход первого коммутатора обьединен с вторым входом второго коммутатора и подключен к третьему выходу двоичного счетчика, третий выход первого блока памяти, выход первого коммутатора, выход второго коммутатора, третий выход двоичного счетчика и выход второго блока памяти являются соответственно первым, вторым, третьим, четвертым и пятым выходами формирователя управляющих сигналов.1626314 едактор С,Пекарь ственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 Пр аказ 282 ВНИИПИ Госуда Составитель Ю.КовалевТехред М.Моргентал Корректор Н.Король Тираж 446 Подписноеенного комитета по изобретениям и открытиям при ГКНТ ССС 13035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4445186, 20.06.1988

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯ АКАДЕМИЯ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА ГОВОРОВА Л. А

БАТУРИН НИКОЛАЙ ГАВРИЛОВИЧ, БОНДАРЬ ЛЕОНИД ВЛАДИМИРОВИЧ, ГОРШКОВ НИКОЛАЙ ВИКТОРОВИЧ, РОМАНОВ ЮРИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03B 19/00

Метки: сигналов, синтезатор, цифровой

Опубликовано: 07.02.1991

Код ссылки

<a href="https://patents.su/6-1626314-cifrovojj-sintezator-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой синтезатор сигналов</a>

Предыдущий патент: Управляемый кварцевый генератор

Следующий патент: Умножитель частоты

Случайный патент: Устройство для отладки программ