Преобразователь амплитудно-модулированного сигнала в код, пропорциональный коэффициенту модуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1575132

Автор: Максимов

Текст

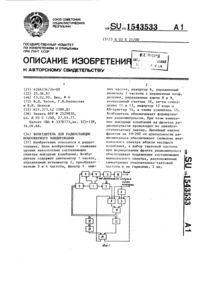

(5) 55 где К 15 ,57513из блоков 13 и 12 соответственно,и - число разрядов кодовМ, И задаваемых регистрами 29 блоков 13 и12 соответственно. Напряжение К,Бь(М) 2 -Ц вх постотупает на входы демодулятора 2 и фор мирователя 3, На выходе формирователя 3 образуются .прямоугольные импульсы частоты (о с фронтами, соответствующими моментам перехода через ноль напряжения несушей частоты (см.фиг.3.3), поступающие на управляющий вход ключа 21 демодулятора 2 и на вход делителя 23 частоты задатчика 20. В результате с выхода дешифратора 26 на управляющий вход интерполирующего20 фильтра 22 поступают прямоугольные импульсы, следующие с периодом где К - коэффициент деления, задаваемый формирователем 28.Импульсы с частотой м (см. Фиг.3,3), поступающие с выхода формирователя 3 на управляющий вход ключа 21 демодулятора 2, открывают его в интервалы времени, соответствующие, например, положительным полуволнам напряжения, поступающего на его сигнальный вход, 35В результате низкочастотной фильт рации выпрямленного ключом 21 напряжения интерполирующим фильтром 22 на втором выходе демодулятора 2 рбразуется сигнал, содержащий постоянную 40 составляющую, определяемую уровнем несущей, и огибающую входного АМ-напряжения (Фиг. 3, 4). 11, (С)= К(МЧз 2.пй С+Ч), (4) 45 где К- коэффициент передачи трактавход ключа 21 - выход демодулятора 2,Причем в данном случае М, =250Одновременно на первом выходе демодулятора 2 образуется первая производная сигнала (4) (фиг, 3.5)- коэффициент передачи трактавход ключа 21 - выход демодулятора 2,2 6В данном случае М, 2Минимальная частота дискретизации2/(Я = ; - выбирается исходя из условияЭполучения необходимой среднеквадратической погрешности восстановления непрерывного сигнала (4) и его производной (5).Напряжение (5) усилителем-ограничителем 25 преобразуется в прямоугольныеимпульсы (фиг. 3.6), через делитель 24частоты поступающие на вход дешифратора 27,Импульсы с третьего выхода задатчика 20 (Фиг, 3,7) поступают на входыобнуления интеграторов 8 и 9 и черезэлемент ИЛИ 18 на первые входы блоков12 и 13, с второго выхода (Фиг. 3.8)на управляющие входы ключей 6 и 7, счетвертого выхода (фиг. 3.9) на управляющие входы ключей 15 и 16, с пятоговыхода (см, фиг. 3.10) - на управляющие входы ключей 14 и 17. В результате в моменты Сз, 1 ь и т.д.(фиг, 3.8) на выходах интеграторов 8и 9 образуются средневыпрямленное Би среднее 11 . напряжения соответственно:,т где , Г - постоянные времени интеграторов 6 и 7 соответственно; Т = 1/,Коэффициент передачи выпрямителя 5приняли ранним единице.Преобразование напряжения Б,т, вкод И, пропорциональный уровню несущей Ч, и напряжения У СЬ в код И1пропорциональный коэфФициенту модуляции М производится путем сравнения винтервалах С С С, и т,д.(Фиг. 3.9) напряженцй Б ср; и Г,компаратором 11, а также У Ь и 0 с1 1компаратором 10.При этом процесс уравновешиванияпроизводится в направлении от старшихразрядов блоков 13 и 12 к младшим,аналогично аналого-цифровым преобразователям поразрядного уравновешиваниякомпенсирующие напряжения изменяютсяпо закону: ПйсЬ д К М ( " 2 о -2 ) 11, (8сЬ, д. о((9) где п " число разрядов регистров 29,блоков 12 и 13;5 ав Ь,- состояния 1 3-х разрядов регистра 29 блоков 12 и 13 соответственно.В первом цикле в интервале с, е на выхбдах интеграторов 8 и 9 образу ются данряжения: Компаратором 11 производится сравнение напряжений Уср,и У.аа а компа-, ратором 10 - напряженйй Ос и У,рср 1 ф Выходные сигналы компараторов 10 и 11 через ключи 15 и 16 соответственно в Интервалей поступают в блоки 12 и 13 управления усилителями 4 и 1. 25 В зависимости от знака разности между О,р, и Б и между .Б сд, и Бср, первые разряды регистра 29 блоков 12 и 13 соответственно остаются включенными (а =1, Ь 1 =1) либо сбрасываются (а =О, Ъ, = О; а, = О, Ь, = 1; а =1,=О) .Во втором цикле в интервале С С сигналом с третьего выхода задатчика 19 (фиг, 3.7) происходит обнуление интеграторов 8 и 9 и включение через35 элемент ИЛИ 18 вторых разрядов регистра 29 блоков 12 и 13 с весом 2 " . В момент й на выходах интеграторов 8 и 9 образуются соответственно напряжения: 11 свК Мха/(2 а+2 а )(2 Ь +2 Ь ); Ъ С Куело/(2а,+2 а 2) сР 2 0 По результатам сравнения Цр иОа компаратором 11, а также Б иУ ср компаратором 10 в интервале(фиг. 3.9), определяемымоткрытым состоянием ключей 15 и 16,вторые разряды регистров 29 блоков13 и 12 остаются либо включенными(а =О, Ь 2=0; а 2=0, Ь 2=1, а 2=1,Ь 2 =0) и т,д.В конце уравновешивания в и-м так 11 рл Оаа е, 11 сэл 11 ер Время преобразования коэффициента модуляции в код пропорционально числу разрядов регистров 29 блоков 12 и 13. Формула изобретения Преобразователь амплитудно-модулированного сигнала в код, пропорциональный коэффициенту модуляции, содержащий усилитель входного сигнала, выходом подключенный к первому входу синхронного демодулятора и через формирователь управляющего напряжения - к его второму входу и к первому входу эадагчика режима измерения, первым выходом соединенного с третьим входом синхронного демодулятора, первый выход которого подключен к второму входу эадатчика режима измерения, выход выпрямителя через последовательно соединенные первый ключ и первый интегратор подключен к первому входу первого компаратора, второй выход синхронного демодулятора через последовательно соединенные второй ключ и второй интегратор соединен с первым входом второго компаратора и вторым входом первого компаратора, второй вход второго компаратора подключен к шине опорного напряжения, управляющие, входы первого и второго ключей соеди 157иены с вторым выходом задатчика режима измерения, управляющие входы первого и второго интеграторов - с третьим выходом задатчика, выход третьего ключа - с выходной шиной кода модуляции, о т л и ч а ю щ и й с я тем, что, с целью расширения динамического диапазона, в него введены второй усилитель, два блока управления усилителями,три ключа, элемент ИЛИ и одновибратор, при этом выходы первого и второго компараторов через четвертый и пятый ключи подключены соответственно к первым входам первого и второго блоков управления усилителями, вторые входы которых через элемент ИЛИ соединены с третьим выходом задатчика режима измерения, второй вход элемента ИЛИ 5132 1 Оподключен к выходу одновибратора,вход которого соединен с шиной питания, выход первого блока управленияусилителем подключен к управляющемувходу второго усилителя и к сигнальному входу третьего ключа, вход вто. рого усилителя подключен к первомувыходу синхронного демодулятора, а 1 Овыход - к входу выпрямителя, выходвторого блока управления подключен куправляющему входу первого усилителяи через шестой ключ - к шиве кода несущей, управляющие входы четвертого ипятого ключей соединены с четвертымвыходом задатчика режима измерения,а управляющие входы третьего и шестого ключей - с его пятым выходом.,Стройко едиевор Л. Веселовская Те еРдюкова КоРРектоР Т, Малец твенног 113 О 35 енно-издательский комбинат Патент , г, Ужгород, ул.на, 10)ЗНЮВ;9 Щ Зажав 1783ВНИИПИ Госуд ставитель хред Л.С Тираж 558 Подписноемитета по изобретениям и открытиям при ГКНТ СССР сква, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

4485913, 20.09.1988

ПРЕДПРИЯТИЕ ПЯ М-5156

МАКСИМОВ ГЕОРГИЙ ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G01R 23/06

Метки: амплитудно-модулированного, код, коэффициенту, модуляции, пропорциональный, сигнала

Опубликовано: 30.06.1990

Код ссылки

<a href="https://patents.su/6-1575132-preobrazovatel-amplitudno-modulirovannogo-signala-v-kod-proporcionalnyjj-koehfficientu-modulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь амплитудно-модулированного сигнала в код, пропорциональный коэффициенту модуляции</a>

Предыдущий патент: Устройство для формирования частотной метки

Следующий патент: Способ регистрации формы импульсных сигналов и устройство регистрации формы импульсных сигналов

Случайный патент: Устройство для защиты фар транспортного средства