Устройство для вычисления систем логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

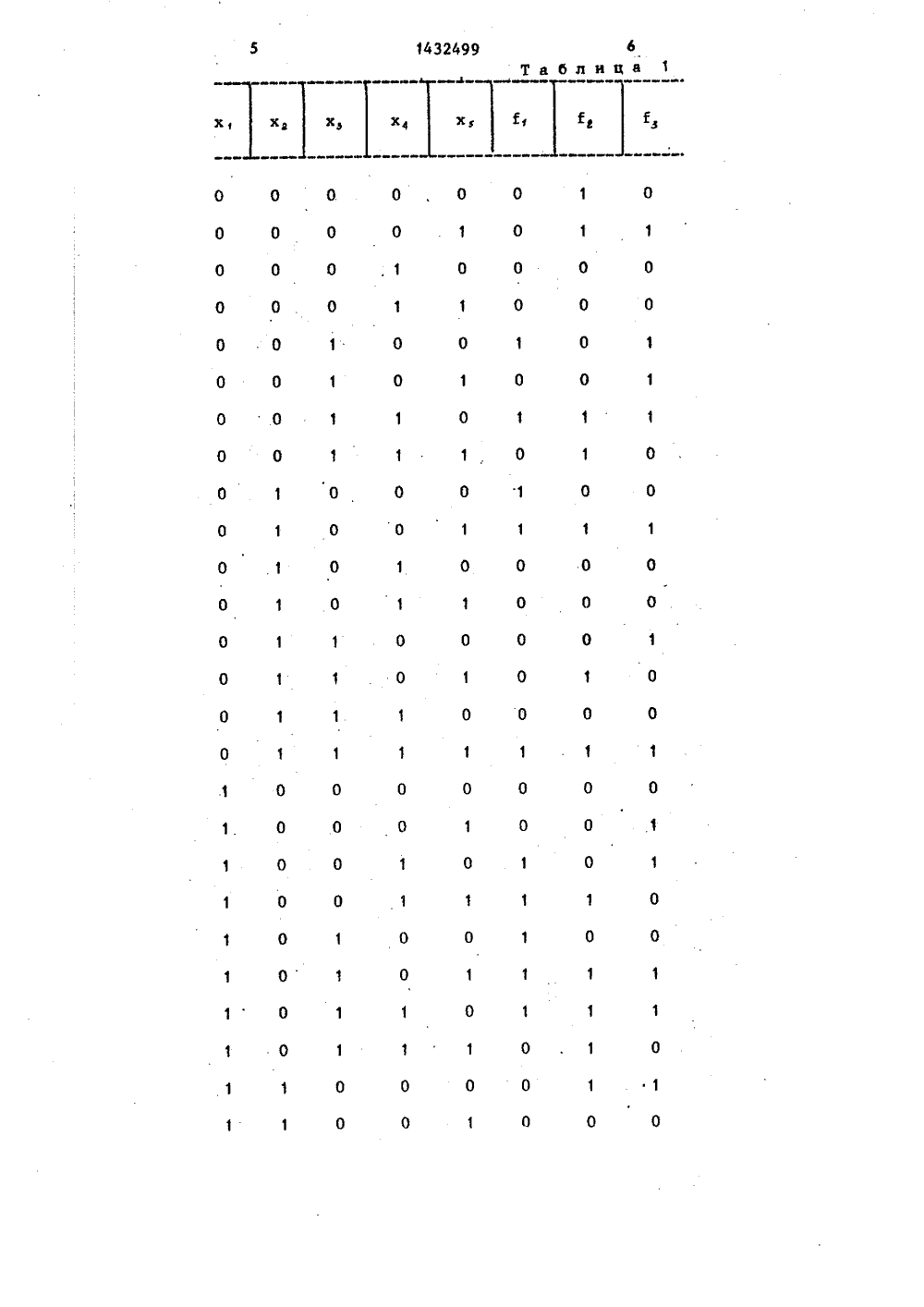

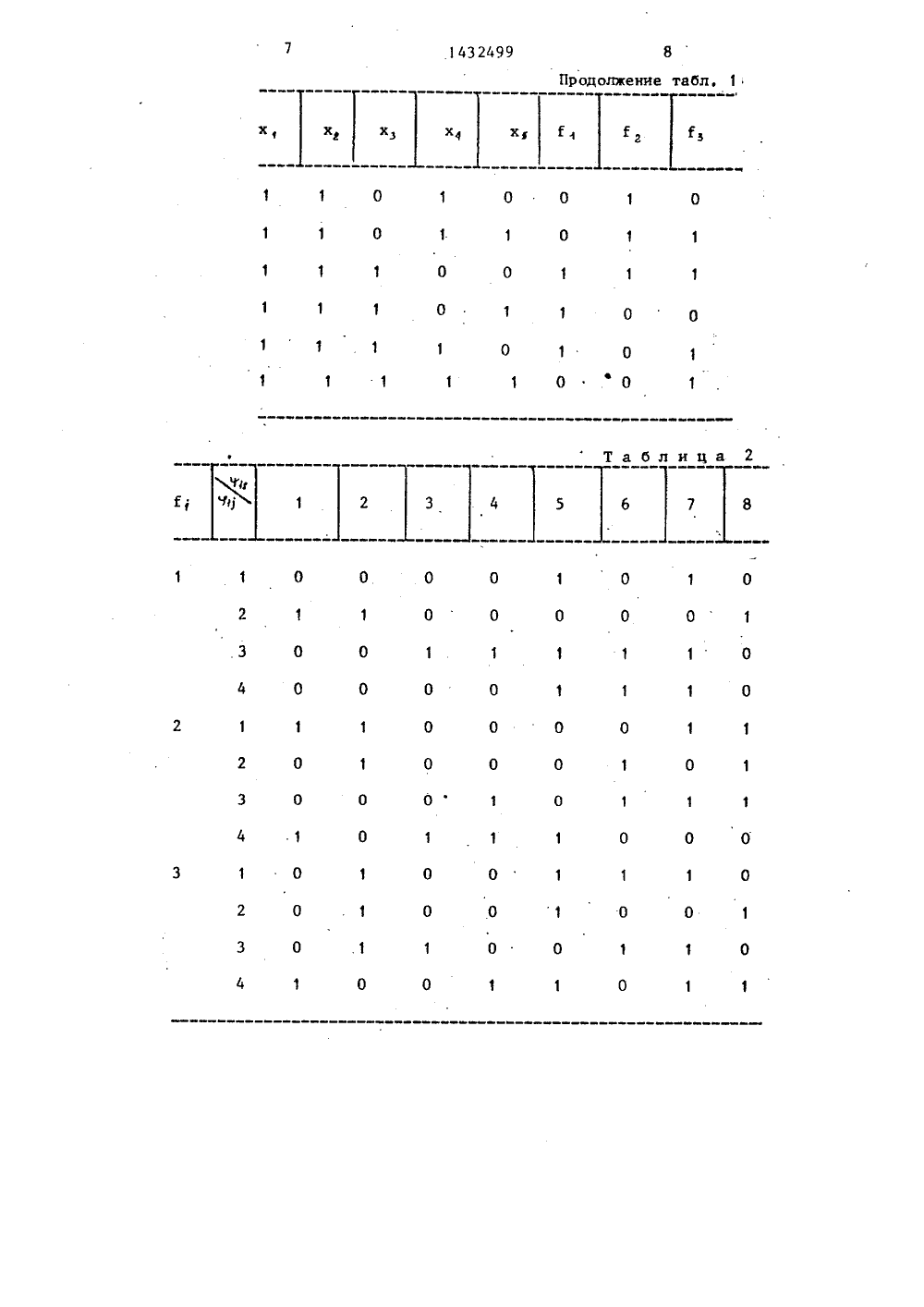

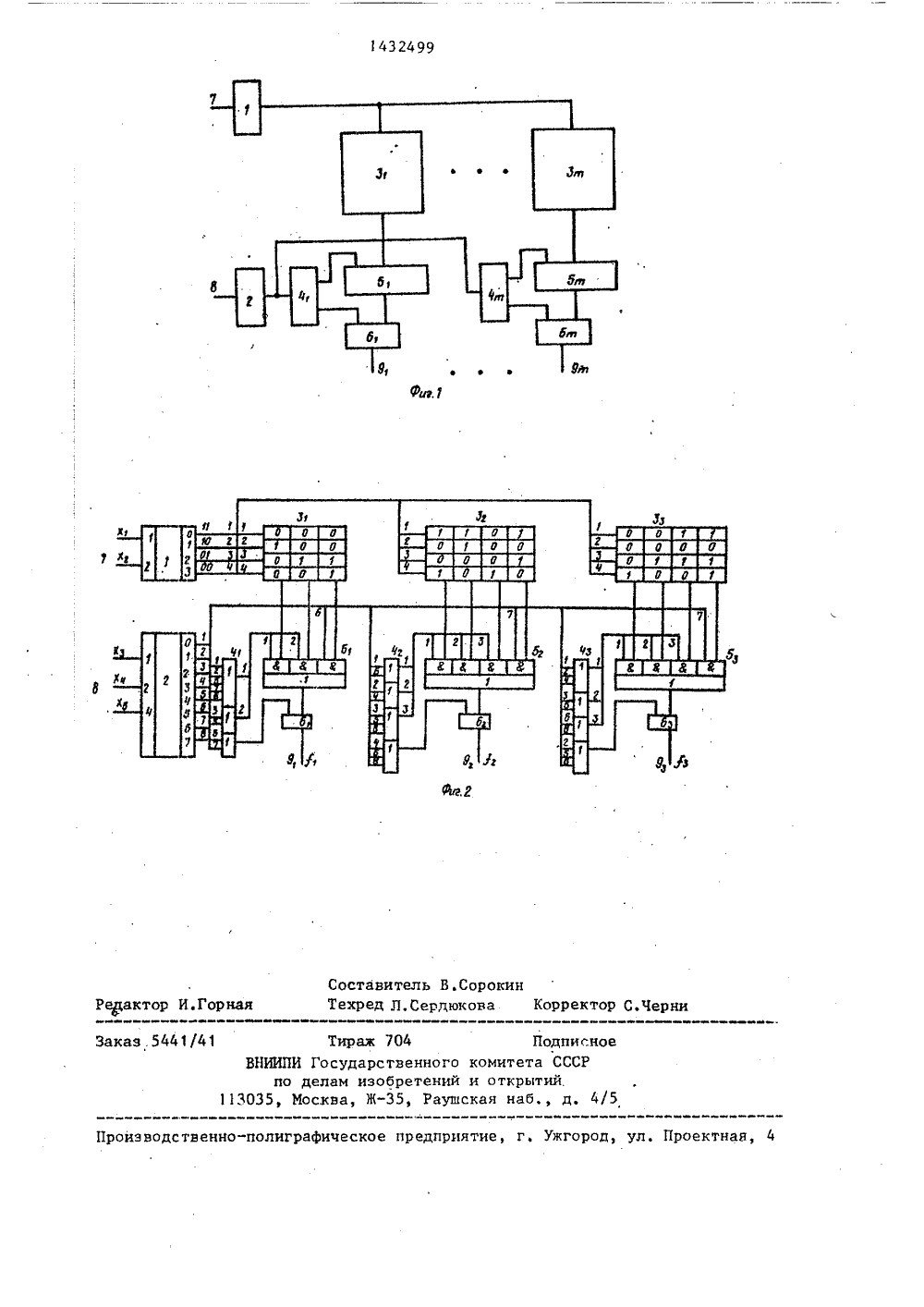

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИН А И 9) (и) (51)4 С 06 Р 7 00Л с Ф с"1 Ф; м ОПИСАНИЕ ИЗОБРЕТЕНИ АВТОРСКОМ 24-24(54) УСТЛОГИЧЕСКИ ИСТВО ДЛЯФУНКЦИет ениетехнике ВЫЧИСЛЕНИЯ(57) Изо лительно осится к вычиспредназначено СУДАРСТВЕННЫЙ КОМИТЕТ ССС.10.88. Бюп.Б.Авгуль, В.ПМаценко и В.П.Як1.3(0888)торское свиде04, кл, С 06рское свидетел60, кл. С 06 для реапизации систем логических фун ций. Цель изобретения - упрощение устройства за счет уменьшения количества элементов памяти. Цель дЬстигается тем, что устройство содержит ш матриц памяти, два дешнфратора, ш групп элементов ИЛИ, ш коммутаторов и ш элементов СЛОЖЕНИЕ ПО МОДУЛЮ 2, две группы информационных входов, выходов. При подаче переменных х хх 1 на первую группу Входов и переменных х, , хна вторую группу входов на выходах устройства реализуются логические функции ГЕ зависящие от и переменных х, х, , х. 2 ил., 2 табл.Изобретение относится к вычислительной технике и предназначено дляреализации систем логических функций,ойисывающих работу цифровых преобра 5зователей.Цель изобретения - упрощение устройства за счет уменьшения количества элементов памяти.На фиг, 1 приведена структурнаясхема предлагаемого устройства; нафиг. 2 - пример функциональной схемыустройства,Устройство (фиг. 1) содержит дешифратор 1 и 2, щ (по числу реализуех устройством логических йункций)Иоков 31-3.щ памяти, щ групп 4. 14 щ элементов ИЛИ, щ коммутаторов5 1-5.тп, элементов СЛОЖЕНИЕ ПО ИОДУ 2 6,1-б.тп первую 7 и вторую 8 20г уппы информационных входов, щ выходов 9. 1-9,щ,Устройство работает следующим обр эом.На вход 7 первого дешифратора 1 25пбдаются двоичные переменные х тх , на вход 8 второго дешифратора 2 д оичные переменные х . х.Ь 1Н выходах 9. 1-9,щ устройства реалиэ тся логические функции Е, (х 30хп) е фГщ(х 1 хе фхп)сответственно.Система щ логических функций(ххе , х ), где= 1 2,щ, разлагается по Шеннону по1 с(1 с ( п) переменным х 1 х , х 1,на функции р,. (х , х), где1,2,2 Таким образом, каждойфункции т, соответствует 2 функций40Логические йункции ср, размещаются в памяти так что каждая иэ нихзанимает одно слово (строку) в 1-йматрице (блоке) памяти. Очевидно одноименным разрядам Б (Б = 12" ) йыцтти ср (х,, и)где 1 = 1, 2, , 2, соответствуютлОгические функции ; (х 1, х,х 1,) кащая иэ которых занимаетБ"й столбец в 3.-й матрице памяти.Следовательно переменные х ,50хопределяют функцию /; В х Й матрйце а переменные х х , х 1, -значение выбранной функции (т;экоторое совпадает со значением функцпи К;(х , хх) на данном55набоРе пеРеменньтх х Х ,х и.Если переменные х х,т, х 1подают на первый дешийратор, выход которого подключает к адресным шинам матриц памяти, переменные х с,х подают на второй дешифраторвыход которого подключают к управляющим входам коммутаторов, информационные входы которых соединяют соответственно с выходами матриц памяти, на выходе коммутаторов реализуются функции Г (х , х, х ),где= 1 2.щ.С целью уменьшения аппаратурныхзатрат все попарно тождественные ивзаимоинверсные функции у, =( М р еу;р те е 31 Б 1 21 = 1, 2, , 2, Я Ф 1), которым соответствуют сигналы на Я-м и1-м выходам второго дешифратора, размещаются в памяти так, чтобы они занимали один столбец. Тогда соответствующий управляющий вход коммутатора подключается к выходу элементаИЛИ, входы которого соединяются сБ-м и 1-м выходам второго дешифратора 2. Таким образом, в результатетакого объединения в -ю матрицу 3памяти заносятся Р; логических функций 1 с переменных.,(хх.1 тх. ) 1 е трххее х) (/, (х 1ех., х 1) где= 1 2,и-Б = 1, 2, , 2 . При этом г-евыходы второго дешифратора 2, длякоторых р,. = у,. , объединяютсяна входе одного из элементов ИЛИ -йгруппы 4;, выход которого подключается к первому входу -го элементаСЛОЖЕНИЕ ПО МОДУЛЮ 2 бх второй входкоторого подключен к выходу 1-го коммутатора 5, а выход соединяется сФ1-м выходом 9 устройства, на котором и реализуется заданная логическая.функция Е;(х , х ,., хп)Работу предлагаемого устройства рассматривают на примере реализации трех логических функций памяти переменных (табл. 1).Разлагают функции К;(х т х х х, х), гдето=1 2, 3, по 1 с= переменным х и х (табл. 2):т(х х хп хт х) =х хп ср ч Ч хх сР. Ч х,. х ср, ЧххитрРассматривают, например, реализации функции Г(х, х, х х 4, х).Иэ табл. 2 следуетГ 2(х, х)1К(х х)Следовательно, в первую матрицу 3.1 памяти заносят три функции (Р, =3)5 10 15 20 25 30 35 40 45 50 55 ф,= Г,(х х)ф у К (хх) Ф ), = Гз(х х).Причем первая группа 4.1 элементовИЛИ содержит три элемента, входы первого из которых соединяются с первым,вторым, пятым, седьмым и восьмым выходами второго дешифратора 2, входывторого элемента ИЛИ соединяются стретьим и четвертым выходами второгодешифратора 2, входы третьего элемента ИЛИ соединяются с пятым и седьмымвыходами второго дешифратора 2. Выход первого элемента ИЛИ подключается к управляющему входу первого коммутатора 5. 1, соответствующий.информационный вход которого подключаетсяк выходу первого столбца матрицы 3.1памяти, в котором размещена таблицаистинности Функции фи ч 11 112= М= У 1= М. Выход второго элементаИЛИ подключают к следующему управляющему входу первого коммутатора 5.1соответствующий информационный входкоторого подключается к выходу второго столбца матрицы 3.1 памяти, в котором размещена таблица истинностифункции "; = /1 = /1 . Функцияб( )1 1 б ) не имеет тождественной или взаимоинверсной функции, Поэ.тому соответствующий ей управляющийвход коммутатора 5.1 непосредственно соединен с шестым выходом второгодешифратора 2,Выход третьего элемента ИЛИ подключен к одному из входов первогоэлемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 6. 1,второй вход которого соединен с выходом первого коммутатора 5.1. Этимобеспечивается инвертирование функции ъ для получения прямых знаЬчений функций ( и у 7 . В общемслучае инверсные функции могут размещаться в нескольких столбцах матрицы памяти, но для получения их прямых значений достаточно одного элемента ИЛИ, выход которого подключается к входу элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2, а входы соединяются с выходами второго дешифратора 2, соответствующими всем функциям, инверсные значения которых занесены в данную матрицу памяти.Логические функции Е, и Е реализуются аналогично.Таким образом, при подаче переменных х хх 1, на входы 7 первого дешифратора 1 и переменных х+ , х на входы 8 второго де. шиФратора 2 на выходах 9.1-9.ш устройства реализуются логические функции Г 1 , 1, соответственно.Формула изобретенияУстройство для вычисления систем логических функций, содержащее первый и второй дешифраторы, ш групп элементов ИЛИ (ш - количество реализуемых устройством логических функций), ш коммутаторов и ш блоков памяти, выходы каждого 1-го (х = 1, ш) из которых соединены с информационными входами 1-го коммутатора, информационные входы первой группы устройства соединены с входами первого дешифратора, выходы которого соединены с адресными входами ш блоков памяти, информационные входы второй группы устройства соединены свхода- . ми второго дешифратора, выходы которого соединены с входами элементов ИЛИ групп с первой по ш-ую, выходы первой группы элементов ИЛИ х-й группы соединены с управляющими входами -го коммутатора, о т л и ч аю щ е е с я тем, что, с целью упрощения за счет уменьшения количества элементов памяти; содержит ш элементов СЛОЖЕНИЕ ПО МОДУЛЮ 2, причем выход -го ( = 1, ш) из которых сое динен с -м выходом устройства, а первый вход х-го элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 соединен с выходом -го коммутатора, второй вход х-го элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 соединен с второй группой выходов элемента ИЛИ х-й группы.143 2499 Составитель Б . С орокинТехред Л. Сердюкова фактор И.Гое Мат ректор С.че аказ,544 енно-полиграфическое предприятие, г. Ужгород, ул. Проектная роизв Тираж ВНИИПИ Государ по делаи из 113035, Москва, Ж

СмотретьЗаявка

4225483, 07.04.1987

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ, БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, СУПРУН ВАЛЕРИЙ ПАВЛОВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, ЯКУШ ВИКТОР ПАВЛОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: вычисления, логических, систем, функций

Опубликовано: 23.10.1988

Код ссылки

<a href="https://patents.su/6-1432499-ustrojjstvo-dlya-vychisleniya-sistem-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления систем логических функций</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Устройство для вычисления симметрических булевых функций

Случайный патент: Трамбовочная машина для получения уплотненного угольного пирога, предназначенного для коксования